PMC-Sierra,Inc.

Octal E1 Framer

Preliminary

PM6388

EOCTL

FEATURES

• Monolithic single-chip device that

integrates eight datacom E1 framers

and transmitters for term inatin g duple x

E1 signals.

• Frames to ITU-T G.704 basic and

CRC-4 multiframe formatted E1

signals and is consist ent with ITU -T

G.706 specifications.

• Extracts/inserts up to three HDLC links

from/to arbitrary time slots to support

the D-channel for ISDN Primary Rate

Interfaces, the datalink in the National

Use Bits and the C-channels for V5.1/

V5.2 interfaces as per ITU-T G.964,

ITU-T G.965, ETS 300-324-1, and

ETS 300-347-1.

• Provides an optional backplane

interface which is com patible wit h Mitel

®

-bus, AT&T CHI

ST

backplanes, supporting data rates of

2.048 Mbit/s and 8.192 Mbit/s.

• Supports transfer of PCM data to and

from 2.048 Mbit/s backplane buses.

• Supports fractional E1 backplan e

interface.

• Provides jitter attenuation in both the

receive and transmit directions.

• Provides per-timeslot line loopback

and per-link diagnostic and line

loopbacks.

• Provides signaling extraction and

insertion on a per-channel basis.

• Provides a Pseudo Random Binary

Sequence (PRBS) generator and

detector wh ich may be configured for

insertion/detection on a per-timeslot or

multiple timeslot basis.

• Software-compatible with the PM6341

E1XC Single E1 Transceiver, the

PM6344 EQUAD Quad E1 Framer, the

PM4388 TOCTL Octal T1 Framer, and

PM4351 COMET Combined E1/T1

Transceiver.

• Pin-compatible with the PM4388

TOCTL with a seamless interface to

the PM4314 QDSX quad line interface

unit.

• Provides an 8-bit microprocessor bus

interface for config uration , contro l, a nd

status monitoring.

• Low power 3.3 V CMOS technology

with 5 V tolerant inputs.

• Supports standard 5-signal P1149.1

JTAG boundary scan.

®

and MVIP PCM

• Provides a -40 to +85° industrial

temperature operating rang e.

• Available in a rectangular 128-pin

PQFP (14 by 20 mm) package.

RECEIVE SECTION

• Red and AIS alarm detection and

integration are done according to

ITU-T Q.516 specifications.

• Can be programmed to generate an

interrupt on change of signaling state.

• Provides performance monitoring

counters sufficiently large as to allow

performance monito r counter pol ling at

a minimum rate of once per second.

Accumulators are provided for

counting ESF CRC-6 errors, framing

bit errors, Far-End Block Errors

(FEBEs) and PRBS bit errors.

• Provides a 2-frame buffer for jitter and

wander attenuation.

TRANSMIT SECTION

• Transmits G.704 basic and CRC-4

multiframe formatted signals with

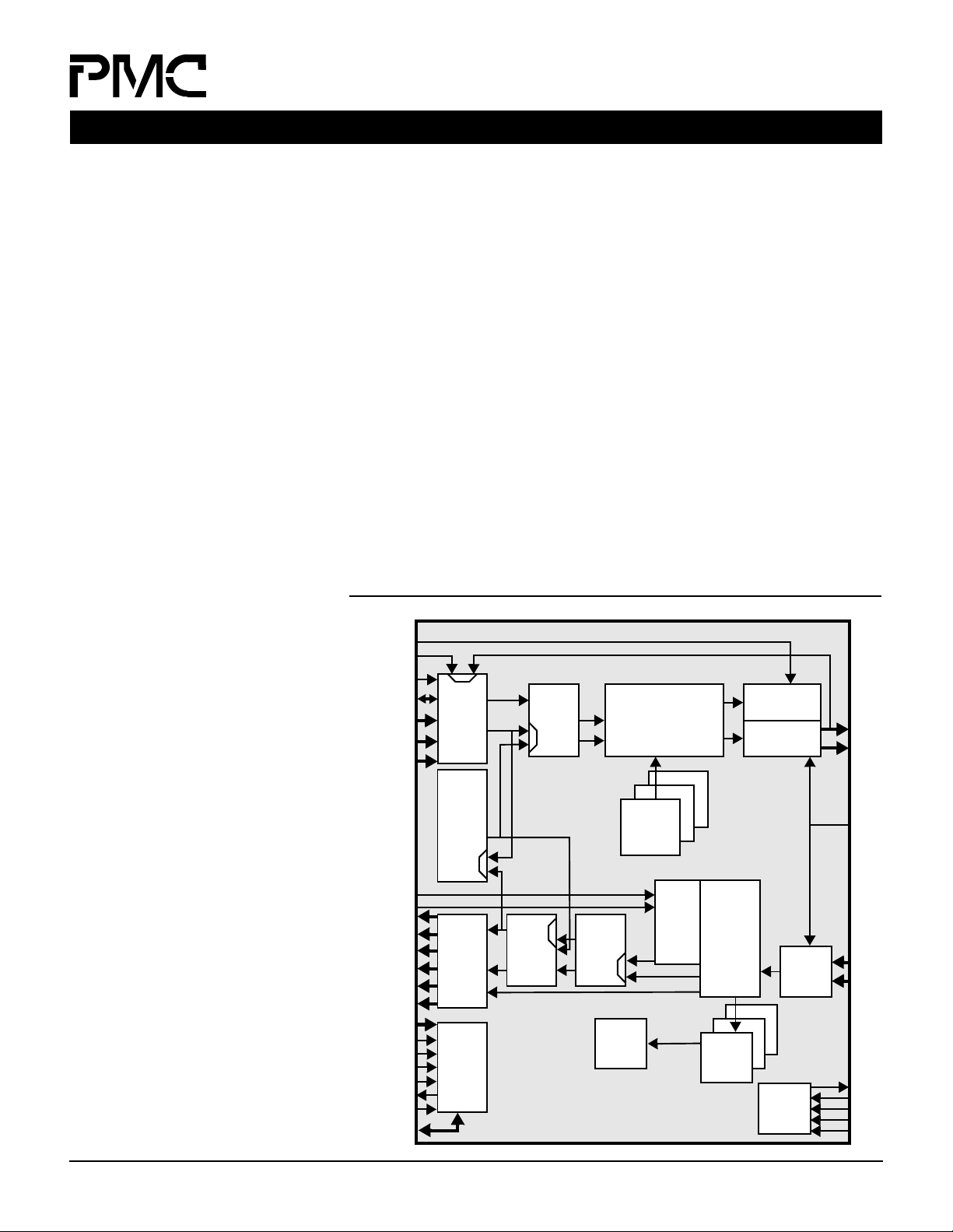

BLOCK DIAGRAM

CTCLK1*

CECLK/MCECLK*

CEFP/MCEFP*

ESIG[1:2]/ECLK[1:2]/

EFP[1:2]/MESIG[1:2]

ED[1:2]/MED[1:2]

ESIG[3:8]/ECLK[3:8]/

EFP[3:8]

ED[3:8]

CICLK/MCICLK*

CIFP/MCIFP*

ID[1:2]/MID[1:2]

ICLK[1:2]/ISIG[1:2]/

MISIG[1:2]

IFP[1:2]/MIFP[1:2]

ID[3:8]

ICLK[3:8]/ISIG[3:8]

IFP[1:8]

A[10:0]*

RDB*

WRB*

CSB*

ALE*

INTB*

RSTB*

D[7:0]*

BTIF

Backplane

Egress

Interface

PRGD

Pattern

Generator/

Detector

BRIF

Ingress

Backplane

Interface

MPIF

Micro-

processor

Interface

TPSC

Per-

channel

Controller

RPSC

Per-DS0

Controller

* These signals are shared between all eight framers.

support for unframed mode.

• May be timed to its associated receive

clock (loop timing) or may derive its

timing from a common egress clock or

a common transmit clock; the tr ans mi t

line clock may be synthesized from an

n × 8kHz reference.

• Provides a digital PL L for generat ion of

a low jitter transmit clock.

• Provides a FIFO buffer for jitter

attenuation and transmit rate

conversion.

APPLICATIONS

• High density Internet E1 interfaces for

multiplexers, switches, routers, and

digital modems

• Frame Relay Switches and Access

Devices (FRADS)

• Digital Access and Cross-Connect

Systems (DACS)

• SDH Add/Drop Multiplexers (ADMs)

Transmitter

Basic Transmitter:

Frame Generation,

Alarm Insertion,

Signalling Insertion,

Trunk Conditioning

TDPR

HDLC

Transmitter

Receiver

SIGX

Signalling

Extractor

PMON

Performance

Monitor

Counters

XBAS

1

ELST

Elastic

Store

TOPS

Timing

Options

TJAT

Digital Jitter

Attenuator

3

2

FRMR

Framer:

Frame

Alignment,

Alarm

Extraction

RDLC

HDLC

Receiver

1

3

2

JTAG

Test Access

Port

RJAT

Digital Jitter

Attenuator

TLCLK[1:8]

TLD[1:8]

XCLK*

RCLK[1:8]

RLD[1:8]

TDO

TDI

TCLK

TMS

TRSTB

PMC-980271 (P1) 1998 PMC-Sierra, Inc. September, 1998

Preliminary PM6388 EOCTL

Octal E1 Framer

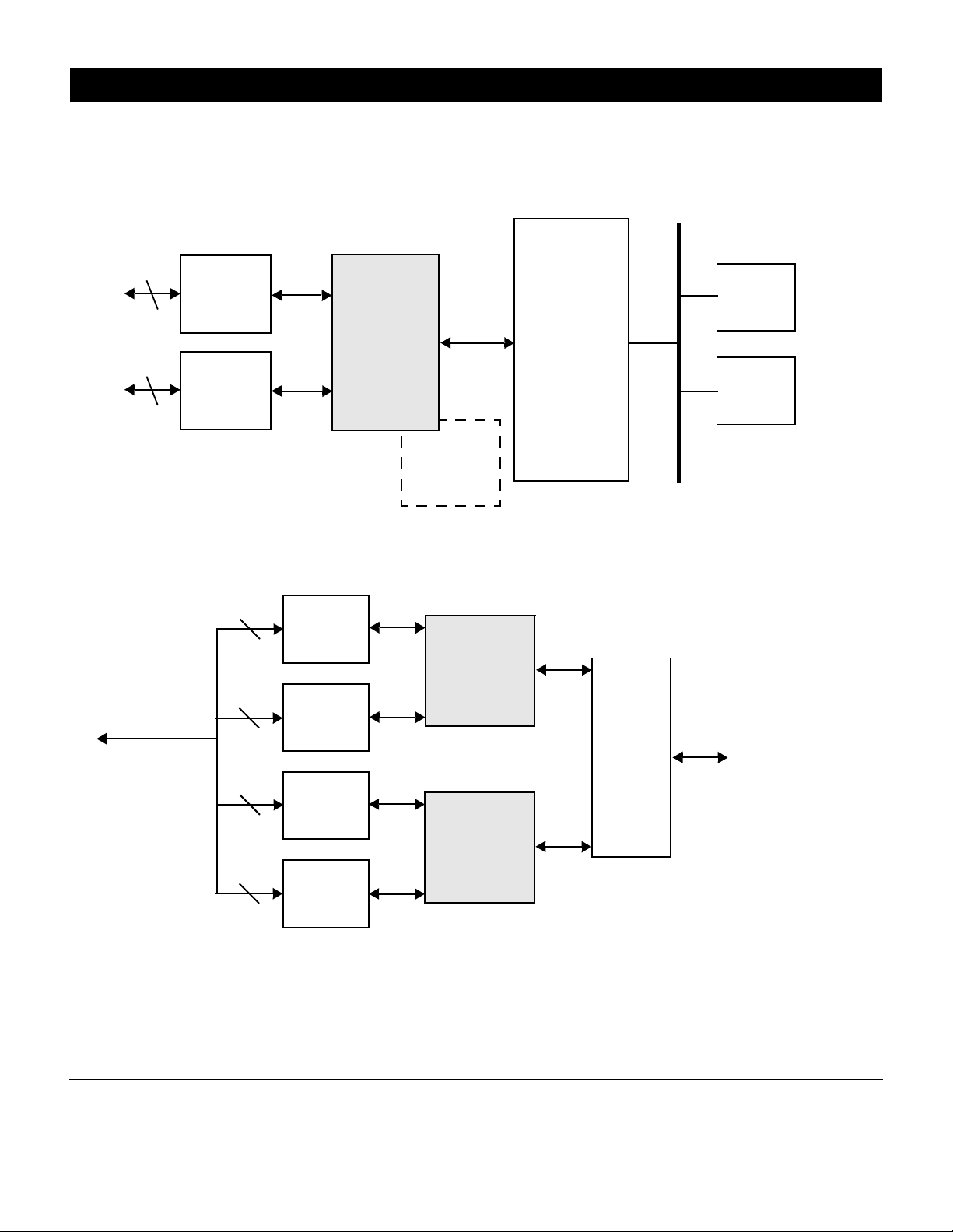

TYPICAL APPLICATIONS

EIGHT-CHANNEL T1/E1 PORT CARD ADAPTER USING PIN-COMPATIBLE TOCTL AND EOCTL

4

4

PM4314

QDSX

Quad LIU

PM4314

QDSX

Quad LIU

PM6388

EOCTL

Octal E1 Framer

Octal T1 Framer

PM388

TOCTL

SIXTEEN-PORT V5.2 INTERFACE USING TWO EOCTLS

PM4314

QDSX

Quad LIU

PM4314

QDSX

Quad LIU

PM6388

EOCTL

Octal E1 Framer

16 Link

V5.2 Interface

4

4

PM7366

FREEDM-8™

HDLC Controller

TDM Switch

Fabric

PCI Bus

Processor

Packet

Memory

User Port

Interface

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

4

4

PM4314

QDSX

Quad LIU

PM4314

QDSX

Quad LIU

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PM6388

EOCTL

Octal E1 Framer

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

PMC-980271 (P1)

1998 PMC-Sierra, Inc.

September, 1998

FREEDM-8 is a trademark

of PMC-Sierra, Inc.

CHI and ST are registered trademarks

of AT&T.

Loading...

Loading...