PMC PM6341 Datasheet

E1 TRANSCEIVER

FEATURES

• Monolithic single chip device which

integrates a full-featured E1 framer

with on-chip analog line interface.

• Provides frame synchronization and

frame generation for a G.704/G.706

2.048 Mbit/s signal with capability to

support the optional signalling and

CRC multiframes.

• Supports HDB3 or AMI line coding

and accepts gapped data streams to

support higher rate demultiplexing.

• Supports both 75 Ohm and 120 Ohm

G.703 line interfaces.

• Provides Channel Associated

Signalling extraction/insertion,

programmable idle code substitution,

digital milliwatt code substitution,

data inversion and up to 3

multiframes of signalling debounce

on a per channel basis.

• Optionally extracts/inserts the

datalink from/to timeslot 16 to

receive/transmit Common Channel

Signalling.

• Pin compatible with the PM4341A

T1XC T1 Transceiver.

• Software compatible with the

PM6344 EQUAD E1 Framer, and

PM6388 EOCTL E1 Framer.

• Provides an 8-bit microprocessor bus

interface for configuration, control

and status monitoring.

• Low-power 5V CMOS technology.

• Available in a high density 80-pin (14

by 14mm) PQFP or in a 68-pin PLCC

package.

APPLICATIONS

• E1 & E3 Multiplexers

• Digital Loop Carriers

• E1 Frame Relay Interfaces

• E1 ATM UNI Interfaces

• E1 Channel Service Units (CSUs)

and Data Service Units (DSUs)

• Digital Access and Cross-Connect

Systems (DACS) and Electronic

Digital Cross-Connect Systems

(EDSX)

• SDH Add/Drop Multiplexers (ADM)

• ISDN Primary Rate Interfaces (PRI)

• Digital Private Branch Exchanges

(PBX)

• E1 & E3 Test Equipment

PMC

-920109(R6)

Summary Information

RECEIVE SECTION

• Provides indications of loss of

signal, loss of frame alignment

(OOF), loss of signalling multiframe

alignment and loss of CRC

multiframe alignment.

• Declares red and AIS alarms using

Q.516 recommended integration

periods

• Supports line and path performance

monitoring according to ITU-T

recommendations. Accumulators

are provided for CRC-4 errors, Far

End Block Errors, Frame sync errors,

and Line Code Violations.

• Provides an integral HDLC/LAPD

interface which may be used for

terminating a CCS or National Bits

datalink.

• Provides a two frame elastic store for

jitter and wander attenuation.

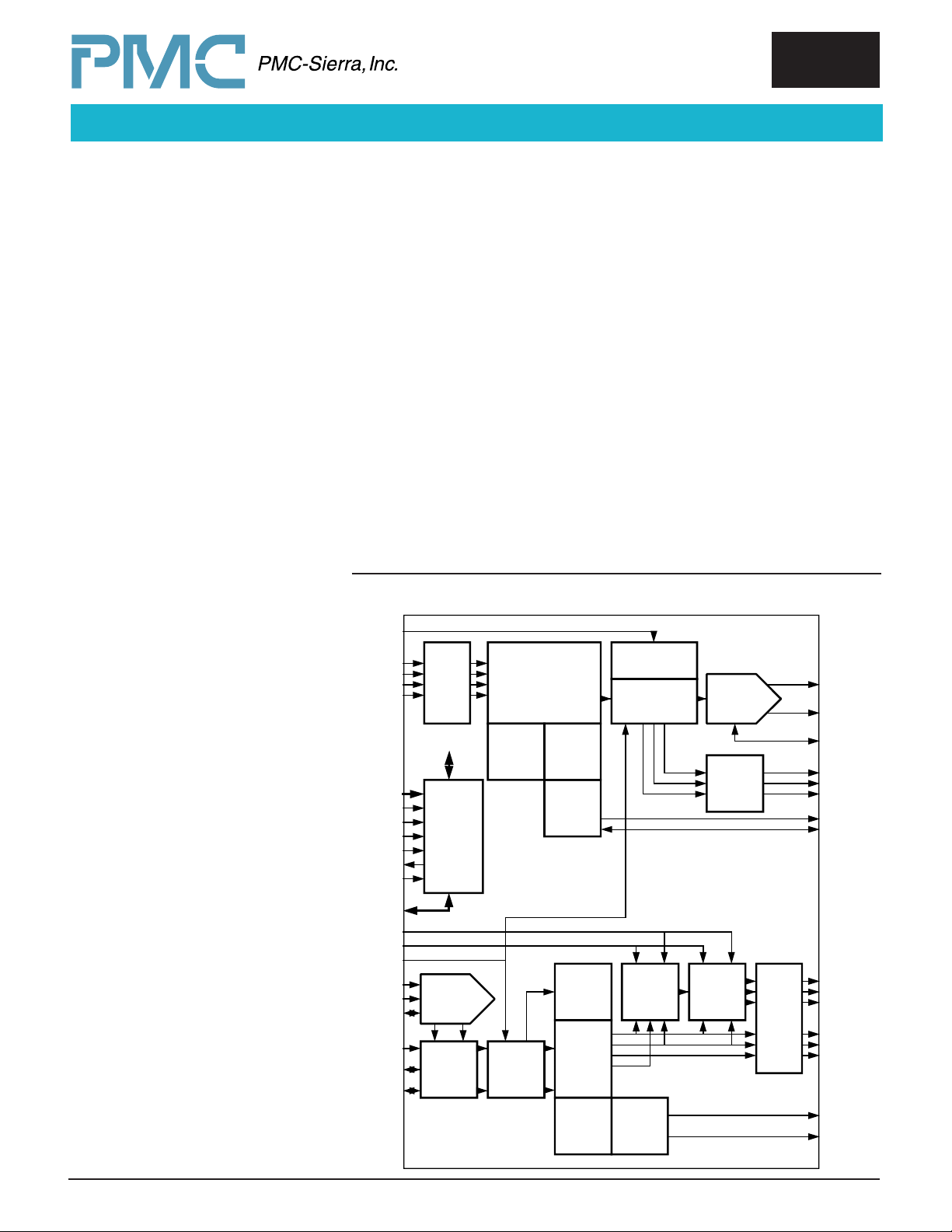

BLOCK DIAGRAM

TCLKI

BTPCM/BTDP

BTSIG/BTDN

BTFP

BTCLK

A(7-0)

RDB

WRB

CSB

ALE

INTB

RSTB

D(7-0)

BRCLK

BRFPI

XCLK/VCLK

RAS

REF

RRC

RCLKI

RDP/RDD/

SDP

RDN/RLCV/

SDN

BTIF

BACK-

PLANE

TRANS-

MIT

INTER-

FACE

INTERNAL

BUS

MPIF

MICRO-

PROCESSOR

INTERFACE

RSLC

ANALOG

PULSE

SLICER

DRIF

DIGITAL

RECEIVE

INTERFACE

TRAN

TRANSMITTER:

FRAME GENERATION,

ALARM INSERTION,

TRUNK CONDITIONING

LINE CODING

PCSC

PER-CHAN

CONTR:

SIGNAL,

IDLE CONT

CDRC

CLOCK AND

DATA

RECOVERY

XBOC

BIT-

ORIENTED

CODE

TRANS

XFDL

HDLC

TRANSMITTER

MONITOR

COUNTERS

FRAMER:

ALIGNMENT,

DETECTION

ORIENTED

DETECTOR

FRAME

ALARM

PMON

PERF

FRMR

RBOC

BIT

CODE

PM6341

E1XC

• Provides programmable trunk

conditioning on a per channel basis.

TRANSMIT SECTION

• Supports transmission of AIS,

timeslot 16 AIS, remote alarm signal

or remote multiframe alarm signal.

• Provides an integral HDLC/LAPD

interface which may be used for

generating a CCS or National Bits

datalink.

• Provides an integrated digital phase

locked loop for generation of a low

jitter transmit clock.

• Provides a FIFO buffer for jitter

attenuation and rate conversion.

• Provides programmable trunk

conditioning which forces trouble

code substitution and signalling

conditioning on a per channel basis.

TOPS

TIMING OPTIONS

DJAT

DIGITAL JITT E R

ATTENUATOR

ELST

ELASTIC

STORE

RFDL

HDLC

RECEIVER

TRAN SMITTER

XPLS

ANALOG

PULSE

GENERATOR

DTIF

DIGITAL

TRANSMIT

INTERFACE

TAP

TAN

TC

TCLKO

TDP/TDD

TDN/TFLG

TDLCLK/

TDLUDR

TDLSIG/

TDLINT

RECEIVER

SIGX

SIGNALLING

EXTRACT,

TRUNK

CONDITION

BRIF

BACK-

PLANE

RECEIVE

INTER-

FACE

BRPCM/BRDP

BRSIG/BRDN

BRFPO

RDPCM/RPCM

RCLKO

RFP

RDLSIG/

RDLINT

RDLCLK/

RDLEOM

© 1998 PMC-Sierra, Inc. March, 1998

E1 TRANSCEIVER

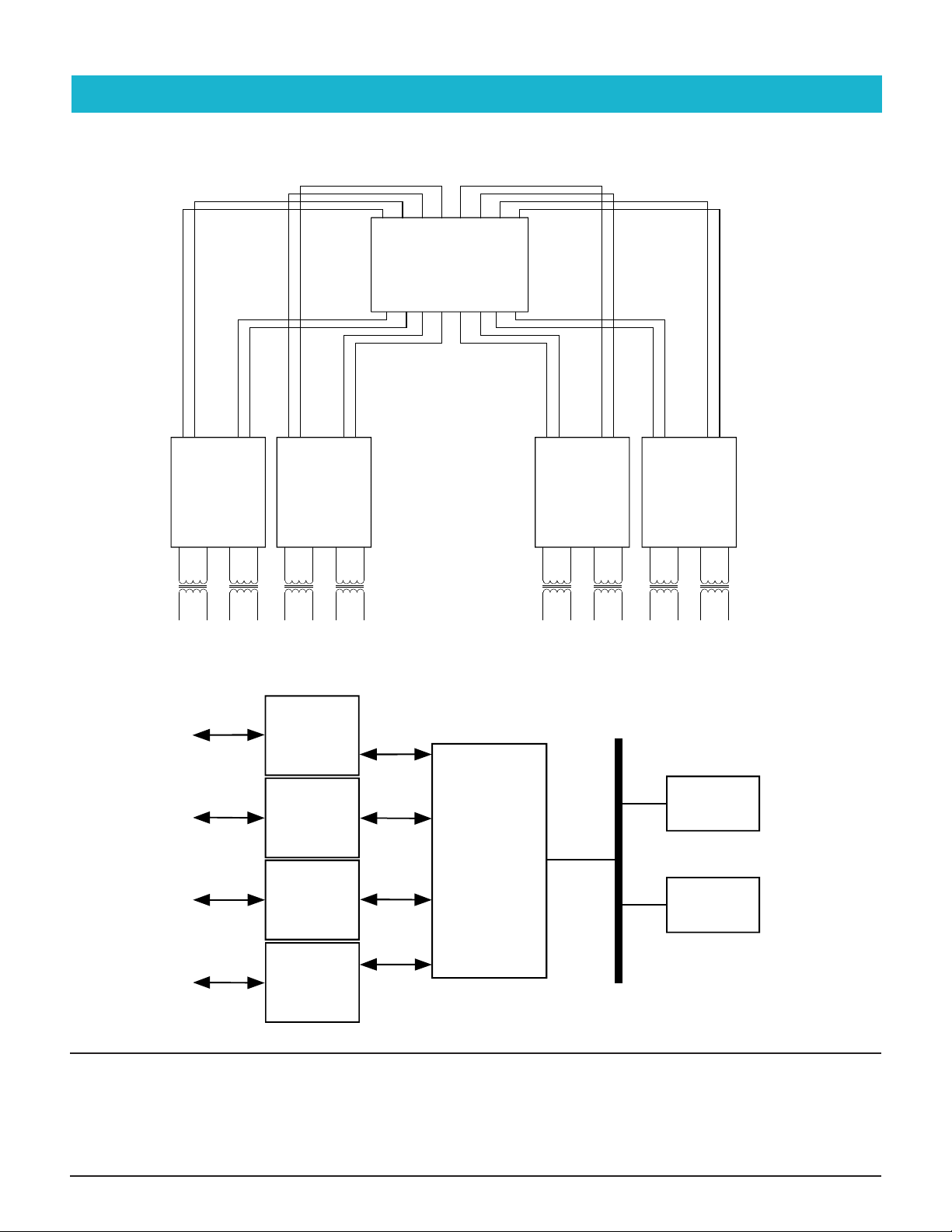

TYPICAL APPLICATIONS:

1/0 CROSS-CONNECT WITH E1 INTERFACE:

PM6341 E1XC

Summary Information

STo1

STi1

BTPCM

TAP

E1

BTSIG

PMC

PM6341

E1XC

TAN

Transmit

BRSIG

BRPCM

RAS

E1

Receive

BTSIG

BTPCM

PMC

PM6341

E1XC

TAP

REF

E1

Transmit

TAN

BRSIG

BRPCM

REF

RAS

E1

Receive

FULLY CHANNELIZED QUAD E1 HDLC CARD:

STo4

STo2

Digital Crosspoint

STi2

STo3

Switch

STi3

STo5

STi4

STi5

STo6

STi6

STo7

STi7

STo8

STi8

BTPCM

TAP

E1

BTSIG

PMC

PM6341

E1XC

TAN

Transmit

BRSIG

BRPCM

RAS

E1

Receive

BTSIG

BTPCM

PMC

PM6341

E1XC

TAP

REF

E1

Transmit

TAN

BRSIG

BRPCM

REF

RAS

E1

Receive

E1

E1

E1

E1

Head Office:

PMC-Sierra, Inc.

Suite 105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

PMC

PM6341

E1XC

PMC

PM6341

E1XC

PMC

PM6341

E1XC

PMC

PM6341

E1XC

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn:Document Coordinator

PMC

PM7366

FREEDM-8

HDLC

Controller

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

Processor

Packet

Memory

PCI Bu s

PMC-920109(R6)

© 1998

PMC-Sierra, Inc.

March, 1998

Loading...

Loading...