PRELIMINARY

/

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

PM5381

ââââ

S

UNI-

2488

S/UNI-2488

SATURN

USER NETWORK INTERFACE

FOR 2488 MBIT/S

DATASHEET

PROPRIET A RY AND CONFIDENTIAL

PRELIMINARY

ISSUE 1: MARCH 2000

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

CONTENTS

1 FEATURES ............................................................................................................................................1

1.1 G

1.2 SONET S

1.3 SONET P

1.4 T

1.5 T

1.6 T

1.7 T

ENERAL..........................................................................................................................................1

ECTION AND LINE / SDH REGENERA T OR AND MULTIPLEXER SECTION...................................2

ATH / SDH HIGH ORDER PATH ...........................................................................................3

HE RECEIVE ATM PROCESSOR........................................................................................................3

HE RECEIVE POS PROCESSOR........................................................................................................4

HE TRANSMIT ATM PROCESSOR......................................................................................................4

HE TRANSMIT POS PROCESSOR......................................................................................................4

2 APPLICATIONS.....................................................................................................................................6

3 REFERENCES.......................................................................................................................................7

4 DEFINITIONS.........................................................................................................................................9

5 APPLICATION EXAMPLES ................................................................................................................10

6 BLOCK DIAGRAM ..............................................................................................................................13

7 DESCRIPTION.....................................................................................................................................17

8 PIN DIAGRAMS...................................................................................................................................19

9 SDPIN DESCRIPTION.........................................................................................................................20

9.1 S

9.2 C

9.3 R

9.4 T

9.5 S

9.6 APS S

9.7 M

9.8 JTAG

9.9 A

9.10 A

9.11 D

ERIAL LINE SIDE INTERFACE SIGNALS (7) .......................................................................................20

LOCKS AND ALARMS (7).................................................................................................................21

ECEIVE SECTION/LINE/PATH OVERHEAD EXTRACTION SIGNALS (6) .................................................23

RANSMIT SECTION/LINE/PATH OVERHEAD INSERTION SIGNALS (7)...................................................24

YSTEM SIDE UTO PIA AND POS SIGNALS (84).................................................................................28

ERIAL DATA INTERFACE (20) ..................................................................................................37

ICROPROCESSOR INTERFACE SIGNALS (37)...................................................................................39

TEST ACCESS PORT (TAP) SIGNALS (5).................................................................................40

NALOG MISCELLANEOUS SIGNALS (10)...........................................................................................41

NALOG POWER AND GROUND (107)...............................................................................................42

IGITAL POWER AND GROUND..........................................................................................................44

10 FUNCTIONAL DESCRIPTION.........................................................................................................50

10.1 R

10.2 SONET/SDH R

10.3 R

10.4 R

10.5 R

10.6 SONET/SDH V

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use i

ECEIVE LINE INTERFACE ................................................................................................................50

ECEIVE LINE INTERFACE (SRLI)...............................................................................51

ECEIVE REGENER A TOR AND MULTIPLEXOR PROCESSOR (RRMP) ...................................................51

ECEIVE TAIL TRACE PROCESSOR (RTTP)......................................................................................53

ECEIVE HIGH ORDER PATH PROCESSOR (RHPP)...........................................................................54

IRTUAL CONTAINER ALIGNER (SVCA) ......................................................................62

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

10.7 RECEIVE CELL AND FRAME PROCESSOR (RCFP)..............................................................................65

10.8 R

10.9 R

10.10 T

10.1 1 SONET/SDH T

10.12 T

10.13 T

10.14 T

10.15 T

10.16 T

10.17 T

10.18 SONET/SDH B

10.19 SONET/SDH A

10.20 SONET/SDH I

10.21 APS S

10.22 JTAG T

10.23 M

ECEIVE SCALABLE DATA QUEUE (RXSDQ).....................................................................................70

ECEIVE PHY INTERFACE (RXPHY).................................................................................................71

RANSMIT LINE INTERFACE ..........................................................................................................71

RANSMIT LINE INTERFACE (STLI)..........................................................................72

RANSMIT REGENERATOR MULTIPLEXOR PROCESSOR (TRMP).....................................................72

RANSMIT TAIL TRACE PROCESSOR (TTTP).................................................................................75

RANSMIT HIGH ORDER PATH PROCESSOR (THPP)......................................................................76

RANSMIT CELL AND FRAME PROCESSOR (TCFP) ........................................................................76

RANSMIT SCALABLE DATA QUEUE (TXSDQ) ...............................................................................79

RANSMIT PHY INTERFACES (RXPHY AND TXPHY) .....................................................................79

IT ERROR RATE MONITOR (SBER).......................................................................80

LARM REPORTING CONTROLLER (SARC).............................................................80

NBAND ERROR REPORT PROCESSOR (SIRP).........................................................81

ERIAL DATA INTERFACE......................................................................................................82

EST ACCESS PORT INTERFACE .........................................................................................83

ICROPROCESSOR INTERFACE.....................................................................................................83

11 NORMAL MODE REGISTER DESCRIPTION.................................................................................97

12 OPERATION...................................................................................................................................430

12.2 SONET/SDH F

12.3 POS/HDLC D

12.4 S

12.5 S

12.6 B

12.7 C

12.8 L

12.9 B

12.10 P

12.11 I

ETTING ATM MODE OF OPERATION..............................................................................................439

ETTING PACKET OVER SONET/SDH MODE OF OPERATION .........................................................439

IT ERROR RATE MONITOR............................................................................................................439

LOCKING OPERATIONS ................................................................................................................439

OOPBACK OPERATION..................................................................................................................439

OARD DESIGN RECOMMENDATIONS..............................................................................................440

OWER SUPPLIES......................................................................................................................440

NTERFACING TO ECL OR PECL DEVICES...................................................................................440

RAME MAPPINGS AND OVERHEAD BYTE USAGE......................................................433

ATA STRUCTURE......................................................................................................438

13 FUNCTIONAL TIMING...................................................................................................................441

13.1 S

13.2 ATM U

13.3 P

13.4 S

13.5 S/UNI-2488 C

ERIAL LINE INTERFACE.................................................................................................................441

TOPIA LEVEL 3 SYSTEM INTERFACE.....................................................................................441

ACKET OVER SONET/SDH (POS) LEVEL 3 SYSTEM INTERFACE..................................................443

ECTION AND LINE DATA COMMUNICATION CHANNELS.....................................................................446

ONCEPTUAL REGIONS .............................................................................................446

14 TEST FEATURES DESCRIPTION.................................................................................................447

15 FUNCTIONAL TIMING...................................................................................................................448

16 ABSOLUTE MAXIMUM RATINGS................................................................................................449

17 D.C. CHARACTERISTICS .............................................................................................................450

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use ii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

18 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS..............................................453

19 A.C. TIMING CHARACTERISTICS ...............................................................................................457

19.1 APS P

ORT INTERFACE ..................................................................................................................461

20 ORDERING AND THERMAL INFORMATION...............................................................................463

21 MECHANICAL INFORMATION.....................................................................................................464

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use iii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

LIST OF REGISTERS

REGISTER 0000H: S/UNI-2488 IDENTITY, AND GLOBAL PERFORMANCE MONITOR UPDATE......98

REGISTER 0001H: S/UNI-2488 MASTER RESET, CONFIGURATION, AND LOOPBACK....................99

REGISTER 0003H: S/UNI-2488 CLOCK MONITORS............................................................................102

REGISTER 0004H: S/UNI-2488 MASTER INTERRUPT STATUS #1 ....................................................104

REGISTER 0005H: S/UNI-2488 MASTER INTERRUPT STATUS #2 ....................................................105

REGISTER 0006H: S/UNI-2488 MASTER INTERRUPT STATUS #3 ....................................................106

REGISTER 0007H: S/UNI-2488 MASTER INTERRUPT STATUS #4 ....................................................107

REGISTER 0008H: S/UNI-2488 MASTER INTERRUPT STATUS #5 ....................................................108

REGISTER 0009H: S/UNI-2488 MASTER INTERRUPT STATUS #6 ....................................................110

REGISTER 000AH: S/UNI-2488 MASTER INTERRUPT STATUS #7....................................................112

REGISTER 000BH: UNUSED...................................................................................................................113

REGISTER 000CH: APS INPUT TELECOMBUS SYNCHRONIZATION DELAY...................................114

REGISTER 000DH: APS OUTPUT TELECOMBUS SYNCHRONIZATION DELAY ...............................115

REGISTER 000EH: S/UNI-2488 DIAGNOST ICS....................................................................................116

REGISTER 000FH: S/UNI-2488 FREE REGISTER.................................................................................118

REGISTER 0010H: RX2488 ANALOG INTERRUPT CONTROL/STATUS.............................................119

REGISTER 0011H: RX2488 ANALOG CRU CONTROL .........................................................................122

REGISTER 0012H: RX2488 ANALOG CRU CLOCK TRAINING CONFIGURATION AND STATUS ....125

REGISTER 0013H: RX2488 ANALOG PRBS CONTROL.......................................................................127

REGISTER 0014H: RX2488 ANALOG PAT T ERN REGISTER................................................................ 129

REGISTER 0030H: SRLI CLOCK CONFIGURATION.............................................................................130

REGISTER 0031H: SRLI PGM CLOCK CONFIGURATION....................................................................132

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use iv

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0038H: STLI CLOCK CONFIGURATION .............................................................................134

REGISTER 0039H: STLI PGM CLOCK CONFIGURATION....................................................................135

THE PROGRAMMABLE TRANSMIT CLOCK FREQUENCY SELECTION (PGMTCLKSEL) BIT

SELECTS THE FREQUENCY OF THE PGMTCLK OUTPUT CLOCK. WHEN PGMTCLKSEL IS SET

HIGH, PGMTCLK IS A NOMINAL 8 KHZ CLOCK. WHEN PGMTCLKSEL IS SET TO LOGIC ZERO,

PGMTCLK IS A NOMINAL REGISTER 0040H: RRMP CONFIGURATION............................................136

REGISTER 0041H: RRMP STATUS.........................................................................................................138

REGISTER 0042H: RRMP INTERRUPT ENABLE..................................................................................140

REGISTER 0043H: RRMP INTERRUPT STATUS...................................................................................141

REGISTER 0044H: RRMP RECEIVE APS...............................................................................................143

REGISTER 0045H: RRMP RECEIVE SSM..............................................................................................144

REGISTER 0046H: RRMP AIS ENABLE.................................................................................................145

REGISTER 0047H: RRMP SECTION BIP ERROR COUNTER...............................................................147

REGISTER 0048H: RRMP LINE BIP ERROR COUNTER (LSB)............................................................148

REGISTER 0049H: RRMP LINE BIP ERROR COUNTER (MSB)...........................................................148

REGISTER 004AH: RRMP LINE REI ERROR COUNTER (LSB) ...........................................................149

REGISTER 004BH: RRMP LINE REI ERROR COUNTER (MSB) ..........................................................149

REGISTER 0080H: TRMP CONFIGURATION.........................................................................................150

REGISTER 0081H: TRMP REGISTER INSERTION................................................................................153

REGISTER 0082H: TRMP ERROR INSERTION .....................................................................................156

REGISTER 0083H: TRMP TRANSMIT J0 AND Z0 .................................................................................158

REGISTER 0084H: TRMP TRANSMIT E1 AND F1.................................................................................159

REGISTER 0085H: TRMP TRANSMIT D1D3 AND D4D12.....................................................................160

REGISTER 0086H: TRMP TRANSMIT K1 AND K2 ................................................................................161

REGISTER 0087H: TRMP TRANSMIT S1 AND Z1.................................................................................162

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use v

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0088H: TRMP TRANSMIT Z2 AND E2.................................................................................163

REGISTER 0089H: TRMP TRANSMIT H1 AND H2 MASK.....................................................................164

REGISTER 008A: TRMP TRANSMIT B1 AND B2 MASK.......................................................................165

REGISTER 00A0H: TRMP AUX2 CONFIGURATION..............................................................................166

REGISTER 00C0H: TRMP AUX3 CONFIGURATION..............................................................................166

REGISTER 00E0H: TRMP AUX4 CONFIGURATION..............................................................................166

REGISTER 00A2H: TRMP AUX2 ERROR INSERTION ..........................................................................167

REGISTER 00C2H: TRMP AUX3 ERROR INSERTION ..........................................................................167

REGISTER 00E2H: TRMP AUX4 ERROR INSERTION ..........................................................................167

REGISTER 0110H: SBER CONFIGURATION .........................................................................................168

REGISTER 0111H: SBER STATUS..........................................................................................................170

REGISTER 0112H: SBER INTERRUPT ENABLE...................................................................................171

REGISTER 0113H: SBER INTERRUPT STATUS....................................................................................172

REGISTER 0114H: SBER SF BERM ACCUMULAT ION P ERIOD (LSB) ...............................................173

REGISTER 0115H: SBER SF BERM ACCUMULATION PERIOD (MSB)...............................................173

REGISTER 0116H: SBER SF BERM SATURATION THRESHOLD (LSB).............................................174

REGISTER 0117H: SBER SF BERM SATURATION THRESHOLD (MSB)............................................174

REGISTER 0118H: SBER SF BERM DECLARING THRESHOLD (LSB) ..............................................175

REGISTER 0119H: SBER SF BERM DECLARING THRESHOLD (MSB)..............................................175

REGISTER 011AH: SBER SF BERM CLEARING THRESHOLD (LSB) ................................................176

REGISTER 011BH: SBER SF BERM CLEARING THRESHOLD (MSB)................................................176

REGISTER 011CH: SBER SD BERM ACCUMULATION PERIOD (LSB) ..............................................177

REGISTER 011DH: SBER SD BERM ACCUMULATION PERIOD (MSB)..............................................177

REGISTER 011EH: SBER SD BERM SATURATION THRESHOLD (LSB)............................................178

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use vi

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 011FH: SBER SD BERM SATURATION THRESHOLD (MSB) ...........................................178

REGISTER 0120H: SBER SD BERM DECLARATION THRESHOLD (LSB) .........................................179

REGISTER 0121H: SBER SD BERM DECLARATION THRESHOLD (MSB) ........................................179

REGISTER 0122H: SBER SD BERM CLEARING THRESHOLD (LSB) ................................................180

REGISTER 0123H: SBER SD BERM CLEARING THRESHOLD (MSB)................................................180

REGISTER 0130H: RTTP SECTION INDIRECT ADDRESS...................................................................181

REGISTER 0131H: RTTP SECTION INDIRECT DATA...........................................................................183

REGISTER 0132H: RTTP SECTION TRACE UNSTABLE STATUS.......................................................184

REGISTER 0133H: RTTP SECTION TRACE UNSTABLE INTERRUPT ENABLE ................................185

REGISTER 0134H: RTTP SECTION TRACE UNSTABLE INTERRUPT STATUS .................................186

REGISTER 0135H: RTTP SECTION TRACE MISMATCH STATUS.......................................................187

REGISTER 0136H: RTTP SECTION TRACE MISMATCH INTERRUPT ENABLE.................................188

REGISTER 0137H: RTTP SECTION TRACE MISMATCH INTERRUPT STATUS .................................189

INDIRECT REGISTER 00H: RTTP SECTION TRACE CONFIGURATION.............................................190

INDIRECT REGISTER 40H TO 7FH: RTTP SECTION CAPTURED TRACE .........................................192

INDIRECT REGISTER 80H TO BFH: RTTP SECTION ACCEPTED TRACE .........................................193

INDIRECT REGISTER C0H TO FFH: RTTP SECTION EXPECTED TRACE.........................................194

REGISTER 0138H: TTTP SECTION INDIRECT ADDRESS....................................................................195

REGISTER 0139H: TTTP SECTION INDIRECT DATA............................................................................197

INDIRECT REGISTER 0138H: TTTP SECTION TRACE CONFIGURATION .........................................198

INDIRECT REGISTER 40H TO 7FH: TTTP SECTION TRACE...............................................................199

REGISTER 0200H: RHPP STS-1/STM-0 #1 THROUGH #12 INDIRECT ADDRESS REGISTER 0280H:

RHPP STS-1/STM-0 #13 THROUGH #24 INDIRECT ADDRESS REGISTER 0300H: RHPP STS-1/STM0 #25 THROUGH #36 INDIRECT ADDRESS REGISTER 0380H: RHPP STS-1/STM-0 #37 THROUGH

#48 INDIRECT ADDRESS........................................................................................................................200

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use vii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0201H: RHPP STS-1/STM-0 #1 THROUGH #12 INDIRECT DATA REGISTER 0281H: RHPP

STS-1/STM-0 #13 THROUGH #24 INDIRECT DATA REGISTER 0301H: RHPP STS-1/STM-0 #25

THROUGH #36 INDIRECT DATA REGISTER 0381H: RHPP STS-1/STM-0 #37 THROUGH #48

INDIRECT DATA.......................................................................................................................................202

REGISTER 0208H, 0210H, 0218H, 0220H, 0228H, 0230H, 0238H, 0240H, 0248H, 0250H, 0258H,

0260H REGISTER 0288H, 0290H, 0298H, 02A0H, 02A8H, 02B0H, 02B8H, 02C0H, 02C8H, 02D0H,

02D8H, 02E0H REGISTER 0308H, 0310H, 0318H, 0320H, 0328H, 0330H, 0338H, 0340H, 0348H,

0350H, 0358H, 0360H REGISTER 0388H, 0390H, 0398H, 03A0H, 03A8H, 03B0H, 03B8H, 03C0H,

03C8H, 03D0H, 03D8H, 03E0H: RHPP

STS-1/STM-0 #N (WHERE N=1 TO 48) POINTER INTERPRETER STATUS 203

REGISTER 0209H, 0211H, 0219H, 0221H, 0229H, 0231H, 0239H, 0241H, 0249H, 0251H, 0259H,

0261H REGISTER 0289H, 0291H, 0299H, 02A1H, 02A9H, 02B1H, 02B9H, 02C1H, 02C9H, 02D1H,

02D9H, 02E1H REGISTER 0309H, 0311H, 0319H, 0321H, 0329H, 0331H, 0339H, 0341H, 0349H,

0351H, 0359H, 0361H REGISTER 0389H, 0391H, 0399H, 03A1H, 03A9H, 03B1H, 03B9H, 03C1H,

03C9H, 03D1H, 03D9H, 03E1H: RHPP

STS-1/STM-0 #N (WHERE N=1 TO 48) POINTER INTERPRETER INTERRUPT ENABLE 205

REGISTER 020AH, 0212H, 021AH, 0222H, 022AH, 0232H, 023AH, 0242H, 024AH, 0252H, 025AH,

0262H REGISTER 028AH, 0292H, 029AH, 02A2H, 02AAH, 02B2H, 02BAH, 02C2H, 02CAH, 02D2H,

02DAH, 02E2H REGISTER 030AH, 0312H, 031AH, 0322H, 032AH, 0332H, 033AH, 0342H, 034AH,

0352H, 035AH, 0362H REGISTER 038AH, 0392H, 039AH, 03A2H, 03AAH, 03B2H, 03BAH, 03C2H,

03CAH, 03D2H, 03DAH, 03E2H:

RHP

P STS-1/STM-0 #N (WHERE N=1 TO 48) POINTER INTERPRETER INTERRUPT STATUS 207

REGISTER 020B: RHPP STS-1/STM-0 #1 ERROR MONITOR STATUS ...............................................209

REGISTER 020C: RHPP STS-1/STM-0 #1 ERROR MONITOR INTERRUPT ENABLE ........................211

REGISTER 020D: RHPP STS-1/STM-0 #1 ERROR MONITOR INTERRUPT STATUS .........................213

REGISTER 020E: RHPP STS-1/STM-0 #1 PATH BIP ERROR COUNTER ............................................215

REGISTER 020F: RHPP STS-1/STM-0 #1 PATH REI ERROR COUNTER............................................216

INDIRECT REGISTER 00H: RHPP POINTER INTERPRETER CONFIGURATION ...............................217

INDIRECT REGISTER 01H: RHPP ERROR MONITOR CONFIGURATION...........................................219

INDIRECT REGISTER 02H: RHPP POINTER VALUE AND ERDI..........................................................222

INDIRECT REGISTER 03H: RHPP CAPTURED AND ACCEPTED PSL................................................223

INDIRECT REGISTER 04H: RHPP EXPECTED PSL AND PDI..............................................................224

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use viii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

INDIRECT REGISTER 05H: RHPP GPO AND OTHER STATUS............................................................225

REGISTER 0400H: THPP STS-1/STM-0 #1 THROUGH #12 INDIRECT ADDRESS REGISTER 0480H:

THPP STS-1/STM-0 #13 THROUGH #24 INDIRECT ADDRESS REGI STER 0500H: THPP STS-1/STM-0

#25 THROUGH #36 INDIRECT ADDRESS REGISTER 0580H: THPP STS-1/STM-0 #37 THROUGH #48

INDIRECT ADDRESS...............................................................................................................................227

REGISTER 0401H: THPP STS-1/STM-0 #1 THROUGH #12 INDIRECT DATA REGISTER 0481H: THPP

STS-1/STM-0 #13 THROUGH #24 INDIRECT DATA REGISTER 0501H: THPP STS-1/STM-0 #25

THROUGH #36 INDIRECT DATA REGISTER 0581H: THPP STS-1/STM-0 #37 THROUGH #48

INDIRECT DATA.......................................................................................................................................229

REGISTER 0402: THPP PAYLO AD CONFIGUR ATION.......................................................................... 230

INDIRECT REGISTER 00H: THPP CONTROL REGISTER ....................................................................231

INDIRECT REGISTER 01H: THPP SOURCE AND POINTER CONTROL REGISTER..........................233

INDIRECT REGISTER 02H: THPP CURRENT POINTER REGISTER ...................................................235

INDIRECT REGISTER 03H: THPP ARBITRARY POINTER REGISTER................................................236

INDIRECT REGISTER 05H: THPP B3 MASK AND FIXED STUFF BYTE..............................................238

INDIRECT REGISTER 06H: THPP TRANSMIT C2 AND J1....................................................................239

INDIRECT REGISTER 07H: THPP TRANSMIT H4 MASK AND G1.......................................................240

INDIRECT REGISTER 08H: THPP TRANSMIT F2 AND Z3....................................................................241

INDIRECT REGISTER 09H: THPP TRANSMIT Z4 AND Z5....................................................................242

REGISTER 0600H: RSVCA INDIRECT ADDRESS.................................................................................243

REGISTER 0601H: RSVCA INDIRECT DATA.........................................................................................245

REGISTER 0603H: RSVCA POSITIVE JUSTIFICATION INTERRUPT STATUS ...................................248

REGISTER 0604H: RSVCA NEGATIVE JUSTIFICATION INTERRUPT STATUS.................................. 249

REGISTER 0605H: RSVCA FIFO OVERFLOW INTERRUPT STATUS..................................................250

REGISTER 0606H: RSVCA FIFO UNDERFLOW INTERRUPT STATUS ...............................................251

INDIRECT REGISTER 00H: RSVCA POINTER JUSTIFICATION INTERRUPT ENABLE.....................252

INDIRECT REGISTER 01H: RSVCA FIFO INTERRUPT ENABLE.........................................................253

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use ix

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

INDIRECT REGISTER 02H: RSVCA POSITIVE JUSTIFICATIONS PERFORMANCE MONITOR........254

INDIRECT REGISTER 03H: RSVCA NEGATIVE JUSTIFICATIONS PERFORMANCE MONITOR ......255

INDIRECT REGISTER 04H: RSVCA DIAGNOSTIC/CONFIGURATION.................................................256

REGISTER 0680H: TSVCA INDIRECT ADDRESS..................................................................................258

REGISTER 0601H: TSVCA INDIRECT DATA..........................................................................................260

REGISTER 0603H: TSVCA POSITIVE JUSTIFICATION INTERRUPT STATUS....................................261

REGISTER 0604H: TSVCA NEGATIVE JUST IFICATION INTERRUPT STATUS ..................................262

REGISTER 0605H: TSVCA FIFO OVERFLOW INTERRUPT STATUS ..................................................263

REGISTER 0606H: TSVCA FIFO UNDERFLOW INTERRUPT STATUS................................................264

INDIRECT REGISTER 00H: TSVCA POINTER JUSTIFICATION INTERRUPT ENABLE .....................265

INDIRECT REGISTER 01H: TSVCA FIFO INTERRUPT ENABLE .........................................................266

INDIRECT REGISTER 02H: TSVCA POSITIVE JUSTIFICATIONS PERFORMANCE MONITOR ........267

INDIRECT REGISTER 03H: TSVCA NEGATIVE JUSTIFICATIONS PERFORMANCE MONITOR.......268

INDIRECT REGISTER 04H: TSVCA DIAGNOSTIC/CONFIGURATION.................................................269

REGISTER 0700H: RTTP PATH INDIRECT ADDRESS..........................................................................271

REGISTER 0701H: RTTP PATH INDIRECT DATA..................................................................................273

REGISTER 0702H: RTTP PATH TRACE UNSTABLE STATUS..............................................................274

REGISTER 0703H: RTTP PATH TRACE UNSTABLE INTERRUPT ENABLE.......................................275

REGISTER 0704H: RTTP PATH TRACE UNSTABLE INTERRUPT STATUS........................................276

REGISTER 0705H: RTTP PATH TRACE MISMATCH STATUS..............................................................277

REGISTER 0706H: RTTP PATH TRACE MISMATCH INTERRUPT ENABLE .......................................278

REGISTER 0707H: RTTP PATH TRACE MISMATCH INTERRUPT STATUS ........................................279

INDIRECT REGISTER 00H: RTTP PATH TRACE CONFIGURATION....................................................280

INDIRECT REGISTER 40H TO 7FH: RTTP PATH CAPTURED TRACE ................................................282

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use x

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

INDIRECT REGISTER 80H TO BFH: RTTP PATH ACCEPTED TRACE................................................283

INDIRECT REGISTER C0H TO FFH: RTTP PATH EXPECTED TRACE................................................284

REGISTER 0708H: TTTP PATH INDIRECT ADDRESS ..........................................................................285

REGISTER 0709H: TTTP PATH INDIRECT DATA ..................................................................................287

INDIRECT REGISTER 00H: TTTP PATH TRACE CONFIGURATION....................................................288

INDIRECT REGISTER 40H TO 7FH: TTTP PATH TRACE......................................................................289

REGISTER 0720H: SARC INDIRECT ADDRESS ...................................................................................290

REGISTER 0722H: SARC SECTION CONFIGURATION........................................................................291

REGISTER 0723H: SARC SECTION SALM ENABLE............................................................................292

REGISTER 0724H: SARC SECTION RLAISINS ENABLE .....................................................................295

REGISTER 0725H: SARC SECTION TLRDIINS ENABLE .....................................................................296

REGISTER 0728H: SARC PATH CONFIGURATION ..............................................................................297

REGISTER 0729H: SARC PATH RALM ENABLE ..................................................................................299

REGISTER 072A: SARC PATH RPAISINS ENABLE..............................................................................300

REGISTER 0730H: SARC LOP POINTER STATUS................................................................................301

REGISTER 0731H: SARC LOP POINTER INTERRUPT ENABLE.........................................................302

REGISTER 0732H: SARC LOP POINTER INTERRUPT STATUS..........................................................303

REGISTER 0733H: SARC AIS POINTER STATU S .................................................................................304

REGISTER 0734H: SARC AIS POINTER INTERRUPT ENABLE ..........................................................305

REGISTER 0735H: SARC AIS POINTER INTERRUPT STATUS ...........................................................306

REGISTER 0740H: RCFP CONFIGURATION .........................................................................................307

REGISTER 0741H: RCFP INTERRUPT ENABLE...................................................................................310

REGISTER 0742H: RCFP INTERRUPT INDICATION AND STATUS .....................................................312

REGISTER 0743H: RCFP MINIMUM PACKET LENGTH........................................................................314

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xi

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0744H: RCFP MAXIMUM PACKET LENGTH ......................................................................315

REGISTER 0745H: RCFP LCD COUNT THRESHOLD...........................................................................316

REGISTER 0746H: RCFP IDLE CELL HEADER AND MASK................................................................317

REGISTER 0747H: RCFP RECEIVE BYTE/IDLE CELL COUNTER (LSB)............................................319

REGISTER 0748H: RCFP RECEIVE BYTE/IDLE CELL COUNTER ......................................................319

REGISTER 0749H: RCFP RECEIVE BYTE/IDLE CELL COUNTER (MSB)...........................................319

REGISTER 074AH: RCFP PACKET/CELL COUNTER (LSB) ................................................................320

REGISTER 074BH: RCFP RECEIVE PACKET/ATM CELL COUNTER (MSB) ......................................320

REGISTER 074CH: RCFP RECEIVE ERRED FCS/HCS COUNTER......................................................321

REGISTER 074DH: RCFP RECEIVE ABORTED PACKET COUNTER..................................................322

REGISTER 074EH: RCFP RECEIVE MINIMUM LENGTH PACKET ERROR COUNTER .....................323

REGISTER 074FH: RCFP RECEIVE MAXIMUM LENGTH PACKET ERROR COUNTER ....................324

REGISTER 0750H: TCFP CONFIGURATION..........................................................................................325

REGISTER 0751H: TCFP INTERRUPT INDICATION .............................................................................328

REGISTER 0752H: TCFP IDLE/UNASSIGNED ATM CELL HEADER ...................................................329

REGISTER 0753H: TCFP DIAGNOSTICS...............................................................................................331

REGISTER 0754H: TCFP TRANSMIT CELL/PACKET COUNTER (LSB)..............................................333

REGISTER 0755H: TCFP TRANSMIT CELL/PACKET COUNTER (MSB).............................................333

REGISTER 0756H: TCFP TRANSMIT BYTE COUNTER (LSB).............................................................334

REGISTER 0757H: TCFP TRANSMIT BYTE COUNTER........................................................................334

REGISTER 0758H: TCFP TRANSMIT BYTE COUNTER (MSB)............................................................334

REGISTER 0759H: TCFP ABORTED PACKET COUNTER....................................................................335

REGISTER 0760H: RXSDQ FIFO RESET...............................................................................................336

REGISTER 0761H: RXSDQ FIFO INTERRUPT ENABLE......................................................................337

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0763H: RXSDQ FIFO OVERFLOW PORT AND INTERRUPT INDICATION......................338

REGISTER 0764H: RXSDQ FIFO SOP ERROR PORT AND INTERRUPT INDICATION .....................339

REGISTER 0765H: RXSDQ FIFO EOP ERROR PORT AND INTERRUPT INDICATION .....................340

REGISTER 0768H: RXSDQ FIFO INDIRECT ADDRESS.......................................................................341

REGISTER 0769H: RXSDQ FIFO INDIRECT CONFIGURATION..........................................................343

REGISTER 076AH: RXSDQ FIFO INDIRECT DATA AVAILABLE THRESHOLD..................................345

REGISTER 076BH: RXSDQ FIFO INDIRECT CELLS AND PACKETS COUNT....................................346

REGISTER 076CH: RXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (LSB)

...................................................................................................................................................................347

REGISTER 076DH: RXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (MSB)

...................................................................................................................................................................347

REGISTER 076EH: RXSDQ FIFO CELLS AND PACKETS DROPPED AGGREGATE COUNT ...........348

REGISTER 0770H: TXSDQ FIFO RESET................................................................................................349

REGISTER 0771H: TXSDQ FIFO INTERRUPT ENABLE......................................................................350

REGISTER 0773H: TXSDQ FIFO OVERFLOW PORT AND INTERRUPT INDICATION ......................351

REGISTER 0774H: TXSDQ FIFO SOP ERROR PORT AND INTERRUPT INDICATION......................352

REGISTER 0775H: TXSDQ FIFO EOP ERROR PORT AND INTERRUPT INDICATION......................353

REGISTER 0778H: TXSDQ FIFO INDIRECT ADDRESS.......................................................................354

REGISTER 0779H: TXSDQ FIFO INDIRECT CONFIGURATION..........................................................356

REGISTER 077AH: TXSDQ FIFO INDIRECT DATA AND BUFFER AVAILABLE THRESHOLDS .......358

REGISTER 077BH: TXSDQ FIFO INDIRECT CELLS AND PACKETS COUNT ....................................360

REGISTER 077CH: TXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (LSB)

...................................................................................................................................................................361

REGISTER 077DH: TXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (MSB)

...................................................................................................................................................................361

REGISTER 077EH: TXSDQ FIFO CELLS AND PACKETS DROPPED AGGREGATE COUNT............362

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xiii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0780H: RXPHY CONFIGURATION.......................................................................................363

REGISTER 0781H: RXPHY INTERRUPT STATUS .................................................................................364

REGISTER 0782H: RXPHY INTERRUPT ENABLE ................................................................................365

REGISTER 0783H: RXPHY INDIRECT BURST SIZE .............................................................................366

REGISTER 0784H: RXPHY CALENDAR LENGTH................................................................................. 368

REGISTER 0785H: RXPHY CALENDAR INDIRECT ADDRESS DATA.................................................369

REGISTER 0786H: RXPHY DATA TYPE FIELD......................................................................................371

REGISTER 0788H: TXPHY CONFIGURATION.......................................................................................372

REGISTER 0789H: TXPHY INTERRUPT STATUS..................................................................................374

REGISTER 078AH: TXPHY INTERRUPT ENABLE ................................................................................375

REGISTER 078BH: TXPHY DATA TYPE FIELD .....................................................................................376

REGISTER 0790H: SIRP CONFIGURATION TIMESLOT .......................................................................377

REGISTER 079CH: SIRP CONFIGURATION ..........................................................................................380

REGISTER 0800H: PRGM INDIRECT ADDRESS...................................................................................382

REGISTER 0810H: PRGM AUX 2 INDIRECT ADDRESS.......................................................................382

REGISTER 0820H: PRGM AUX 3 INDIRECT ADDRESS.......................................................................382

REGISTER 0830H: PRGM AUX 4 INDIRECT ADDRESS.......................................................................382

REGISTER 0801H: PRGM INDIRECT DATA...........................................................................................384

REGISTER 0811H: PRGM AUX 2 INDIRECT D ATA................................................................................384

REGISTER 0821H: PRGM AUX 3 INDIRECT DATA...............................................................................384

REGISTER 0831H: PRGM AUX 4 INDIRECT DATA...............................................................................384

REGISTER 0802H: PRGM GENERATOR PAYLOAD CONFIGURATION..............................................385

REGISTER 0812H: PRGM AUX 2 GENERATOR PAYLOAD CONFIGURATION...................................385

REGISTER 0822H: PRGM AUX 3 GENERATOR PAYLOAD CONFIGURATION...................................385

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xiv

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0832H: PRGM AUX 4 GENERATOR PAYLOAD CONFIGURATION...................................385

REGISTER 0803H: PRGM MONITOR PAYLOAD CONFIGURATION REGISTER ................................386

REGISTER 0813H: PRGM AUX 2 MONITOR PAYLOAD CONFIGURATION ........................................386

REGISTER 0823H: PRGM AUX 3 MONITOR PAYLOAD CONFIGURATION ........................................386

REGISTER 0833H: PRGM AUX 4 MONITOR PAYLOAD CONFIGURATION ........................................386

REGISTER 0804H: PRGM MONITOR BYTE ERROR INTERRUPT STATUS........................................387

REGISTER 0814H: PRGM AUX 2 MONITOR BYTE ERROR INTERRUPT STATUS ............................387

REGISTER 0824H: PRGM AUX 3 MONITOR BYTE ERROR INTERRUPT STATUS ............................387

REGISTER 0834H: PRGM AUX 4 MONITOR BYTE ERROR INTERRUPT STATUS.............................387

REGISTER 0805H: PRGM MONITOR BYTE ERROR INTERRUPT ENABLE.......................................388

REGISTER 0815H: PRGM AUX 2 MONITOR BYTE ERROR INTERRUPT ENABLE............................388

REGISTER 0825H: PRGM AUX 3 MONITOR BYTE ERROR INTERRUPT ENABLE............................388

REGISTER 0835H: PRGM AUX 4 MONITOR BYTE ERROR INTERRUPT ENABLE............................388

REGISTER 0806H: MONITOR B1/E1 BYTES INTERRUPT STATUS ....................................................389

REGISTER 0807H: MONITOR B1/E1 BYTES INTERRUPT ENABLE....................................................390

REGISTER 0808H: MONITOR B1/E1 BYTES STATUS ..........................................................................391

REGISTER 0809H: PRGM MONITOR SYNCHRONIZATION INTERRUPT STATUS.............................392

REGISTER 0819H: PRGM AUX 2 MONITOR SYNCHRONIZATION INTERRUPT STATUS .................392

REGISTER 0829H: PRGM AUX 3 MONITOR SYNCHRONIZATION INTERRUPT STATUS .................392

REGISTER 0839H: PRGM AUX 4 MONITOR SYNCHRONIZATION INTERRUPT STATUS .................392

REGISTER 080AH: PRGM MONITOR SYNCHRONIZATION INTERRUPT ENABLE...........................393

REGISTER 081AH: PRGM AUX 2 MONITOR SYNCHRONIZATION INTERRUPT ENABLE................393

REGISTER 082AH: PRGM AUX 3 MONITOR SYNCHRONIZATION INTERRUPT ENABLE................393

REGISTER 083AH: PRGM AUX 4 MONITOR SYNCHRONIZATION INTERRUPT ENABLE................393

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xv

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 080BH: PRGM MONITOR SYNCHRONIZATION STATUS..................................................394

REGISTER 081BH: PRGM AUX 2 MONITOR SYNCHRONIZATION STATUS ......................................394

REGISTER 082BH: PRGM AUX 3 MONITOR SYNCHRONIZATION STATUS ......................................394

REGISTER 083BH: PRGM AUX 4 MONITOR SYNCHRONIZATION STATUS ......................................394

INDIRECT REGISTER 0800H: PRGM MONITOR TIMESLOT CONFIGURATION PAGE......................395

INDIRECT REGISTER 0801H: PRGM MONITOR PRBS[22:7] ACCUMULATOR PAGE.......................397

INDIRECT REGISTER 0802H: PRGM MONITOR PRBS[6:0] ACCUMULATOR PAGE.........................397

INDIRECT REGISTER 0803H: PRGM MONITOR B1/E1 VALUE PAGE ................................................398

INDIRECT REGISTER 0804H: PRGM MONITOR ERROR COUNT PAGE ............................................399

INDIRECT REGISTER 0805H: PRGM MONITOR RECEIVED B1/E1 BYTES PAGE.............................400

INDIRECT REGISTER 0808H: PRGM GENERATOR TIMESLOT CONFIGURATION PAGE................401

INDIRECT REGISTER 0809H : PRGM GENERATOR PRBS[22:7] ACCUMULATOR PAGE................403

INDIRECT REGISTER 080AH: PRGM GENERATOR PRBS[6:0] ACCUMULATOR PAGE ..................403

INDIRECT REGISTER 080BH: PRGM GENERATOR B1/E1 VALUE PAGE..........................................404

REGISTER 0840H: R8TD APS1 CONTROL AND STATUS....................................................................405

REGISTER 0848H: R8TD APS2 CONTROL AND STATUS....................................................................405

REGISTER 0850H: R8TD APS3 CONTROL AND STATUS....................................................................405

REGISTER 0858H: R8TD APS4 CONTROL AND STATUS....................................................................405

REGISTER 0841H: R8TD APS1 INTERRUPT STATUS..........................................................................408

REGISTER 0849H: R8TD APS2 INTERRUPT STATUS..........................................................................408

REGISTER 0851H: R8TD APS3 INTERRUPT STATUS..........................................................................408

REGISTER 0859H: R8TD APS4 INTERRUPT STATUS..........................................................................408

REGISTER 0842H: R8TD APS1 LINE CODE VIOLATION COUNT .......................................................410

REGISTER 084AH: R8TD APS2 LINE CODE VIOLATION COUNT.......................................................410

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xvi

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0852H: R8TD APS3 LINE CODE VIOLATION COUNT .......................................................410

REGISTER 085AH: R8TD APS4 LINE CODE VIOLATION COUNT.......................................................410

REGISTER 0843H: R8TD APS1 ANALOG CONTROL 1........................................................................411

REGISTER 084BH: R8TD APS2 ANALOG CONTROL 1........................................................................411

REGISTER 0853H: R8TD APS3 ANALOG CONTROL 1........................................................................411

REGISTER 085BH: R8TD APS4 ANALOG CONTROL 1........................................................................411

REGISTER 0844H: R8TD APS1 ANALOG CONTROL 2........................................................................412

REGISTER 084CH: R8TD APS2 ANALOG CONTROL 2........................................................................412

REGISTER 0854H: R8TD APS3 ANALOG CONTROL 2........................................................................412

REGISTER 085CH: R8TD APS4 ANALOG CONTROL 2........................................................................412

REGISTER 0860H: T8TE APS1 CONTROL AND STATUS .....................................................................413

REGISTER 0868H: T8TE APS2 CONTROL AND STATUS .....................................................................413

REGISTER 0870H: T8TE APS3 CONTROL AND STATUS .....................................................................413

REGISTER 0878H: T8TE APS4 CONTROL AND STATUS .....................................................................413

REGISTER 0861H: T8TE APS1 INTERRUPT STATUS...........................................................................415

REGISTER 0869H: T8TE APS2 INTERRUPT STATUS...........................................................................415

REGISTER 0871H: T8TE APS3 INTERRUPT STATUS...........................................................................415

REGISTER 0879H: T8TE APS4 INTERRUPT STATUS...........................................................................415

REGISTER 0862H: T8TE APS1 TELECOMBUS MODE #1....................................................................416

REGISTER 086AH: T8TE APS2 TELECOMBUS MODE #1 ...................................................................416

REGISTER 0872H: T8TE APS3 TELECOMBUS MODE #1....................................................................416

REGISTER 087AH: T8TE APS4 TELECOMBUS MODE #1 ...................................................................416

REGISTER 0863H: T8TE APS1 TELECOMBUS MODE #2....................................................................417

REGISTER 086BH: T8TE APS2 TELECOMBUS MODE #2 ...................................................................417

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xvii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

REGISTER 0873H: T8TE APS3 TELECOMBUS MODE #2....................................................................417

REGISTER 087BH: T8TE APS4 TELECOMBUS MODE #2 ...................................................................417

REGISTER 0864H: T8TE APS1 TEST PATTERN ...................................................................................418

REGISTER 086CH: T8TE APS2 TEST PATTERN...................................................................................418

REGISTER 0874H: T8TE APS3 TEST PATTERN ...................................................................................418

REGISTER 087CH: T8TE APS4 TEST PATTERN...................................................................................418

REGISTER 0865H: T8TE APS1 ANALOG CONTROL............................................................................419

REGISTER 086DH: T8TE APS2 ANALOG CONTROL...........................................................................419

REGISTER 0875H: T8TE APS3 ANALOG CONTROL............................................................................419

REGISTER 087DH: T8TE APS4 ANALOG CONTROL...........................................................................419

REGISTER 0866H: T8TE APS1 DTB BUS..............................................................................................421

REGISTER 086EH: T8TE APS2 DTB BUS..............................................................................................421

REGISTER 0876H: T8TE APS3 DTB BUS..............................................................................................421

REGISTER 087EH: T8TE APS4 DTB BUS..............................................................................................421

REGISTER 0880H-0883H: RFCLK DLL RESERVED .............................................................................422

REGISTER 0884H-0887H: TFCLK DLL RESERVED..............................................................................423

REGISTER 0888H: CSTR CONTROL......................................................................................................424

REGISTER 0889H: CSTR INTERRUPT ENABLE AND CSU LOCK STATUS .......................................425

REGISTER 088AH: CSTR CSU LOCK INTERRUPT INDICATION ........................................................426

REGISTER 088BH: CSTR CSU LOCK INTERRUPT INDICATION ........................................................427

REGISTER 0890H-0897: S/UNI-2 488 RX STSI RESERVED ..................................................................428

REGISTER 0898H-089F: S/UNI-2488 TX STSI RESERVED ..................................................................429

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xviii

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

LIST OF TABLES

TABLE 1: PLM-P, UNEQ-P AND PDI-P DEFECTS DECLARATION ..........................................................60

TABLE 2: EXPECTED PDI DEFECT BASED ON PDI AND PDI RANGE VALUES ...................................61

TABLE 3: BYTE DESTUFFING..................................................................................................................69

TABLE 4: TOH INSERTION PRIORITY ......................................................................................................73

TABLE 5: Z0/NATIONAL GROWTH BYTES DEFINITION FOR ROW #1..................................................75

TABLE 6: BYTE STUFFING.......................................................................................................................78

TABLE 7: REGISTER MEMORY MAP........................................................................................................83

TABLE 8 CRU MODE CONTRO L .............................................................................................................123

TABLE 9: FUNCTIONALITY OF THE CRC_SEL[1:0] REGISTER BITS ..................................................308

TABLE 10: AVERAGE STS-X CELL PERIOD VERSUS LCD INTEGRATION PERIOD ..........................316

TABLE 11: SELECTION OF THE NUMBER OF FLAG BYTES...............................................................325

TABLE 12: CRC MODE SELECTION ......................................................................................................326

TABLE 13: SIRP RDI AND REI REPORTING MODES............................................................................378

TABLE 14: SIRP RDI SETTINGS.............................................................................................................378

TABLE 15: SIRP RDI MAINTENANCE.....................................................................................................379

TABLE 16: SIRP RDI PRIORITY SCHEMES...........................................................................................381

TABLE 17: ABSOLUTE MAXIMUM RATINGS.........................................................................................449

TABLE 18: D.C CHARACTERISTICS......................................................................................................450

TABLE 19: MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 26)......................................453

TABLE 20: MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 27) ....................................455

TABLE 21: RECEIVE SYSTEM INTERFACE TIMING (FIGURE 28).......................................................457

TABLE 22: TRANSMIT SYSTEM INTERFACE TIMING (FIGURE 29)....................................................459

TABLE 23: JTAG PORT INTERFACE (FIGURE 30)................................................................................461

TABLE 24: ORDERING INFORMATION..................................................................................................463

TABLE 25: THERMAL INFORMATION .....................................................................................................463

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xix

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

LIST OF FIGURES

FIGURE 1: STS-48 (STM-16-16C) ATM (UTOPIA LEVEL 3) SWITCH PORT APPLICATION 11

FIGURE 2: STS-48 (STM-16-16C) PACKET OVER SONET (POS-PHY LEVEL 3) ROUTER

APPLICATION 12

FIGURE 3:NORMAL OPERATION 13

FIGURE 4:LOOPBACK MODES 14

FIGURE 5: APS WORKING 15

FIGURE 6: APS PROTECT 16

FIGURE 7: TYPICAL STS-48C (STM-16C) JITTER TOLERANCE 50

FIGURE 8: STS-48C (STM-16-16C) ON RTOH 53

FIGURE 9: POINTER INTERPRETATION STATE DIAGRAM 55

FIGURE 10: CONCATENATION POINTER INTERPRETATION STATE DIAGRAM 58

FIGURE 11: POINTER GENERATION STATE DIAGRAM 64

FIGURE 12: CELL DELINEATION STATE DIAGRAM 66

FIGURE 13: PPP/HDLC OVER SONET FRAME FORMAT 68

FIGURE 14: CRC DECODER 69

FIGURE 15: STS-48C (STM-16-16C) ON TTOH 73

FIGURE 16: CRC GENERATOR 78

FIGURE 17: GENERIC LVDS LINK BLOCK DIAGRAM 430

FIGURE 18 ATM MAPPING 433

FIGURE 19 PACKET OVER SONET MAPPING 434

FIGURE 20: A 52 BYTE ATM DATA STRUCTURE 438

FIGURE 21: A 63 BYTE PACKET DATA STRUCTURE 438

FIGURE 22 SINGLE-PHY UTOPIA LEVEL 3 RECEIVE FUNCTIONAL TIMING 441

FIGURE 23 SINGLE-PHY UTOPIA LEVEL 3 TRANSMIT FUNCTIONAL TIMING 442

FIGURE 24 SINGLE PHY POS-PHY LEVEL 3 RECEIVE FUNCTIONAL TIMING 444

FIGURE 25 SINGLE PHY POS-PHY LEVEL 3 TRANSMIT FUNCTIONAL TIMING 445

FIGURE 26: INTEL MICROPROCESSOR INTERFACE READ TIMING 454

FIGURE 27: INTEL MICROPROCESSOR INTERFACE WRITE TIMING 455

FIGURE 28: RECEIVE SYSTEM INTERFACE TIMING DIAGRAM 458

FIGURE 29: TRANSMIT SYSTEM INTERFACE TIMING 460

FIGURE 30: JTAG PORT INTERFACE TIMING 462

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use xx

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

1 FEATURES

1.1 General

• Single chip ATM and POS User-Network Interface operating at 2488.32 Mbit/s.

• Implements the ATM Forum User Network Interface Specification and the ATM physical layer for

Broadband ISDN according to CCITT Recommendation I.432.

• Implements the Point-to-Point Protocol (PPP) over SONET/SDH specification according to RFC

2615(1619)/1662 of the PPP Working Group of the Internet Engineering Task Force (IETF).

• Processes bit-serial 2488.32 Mbit/s STS-48 (STM-16-16c) data streams with on-chip clock and data

recovery and clock synthesis.

• Complies with Bellcore GR-253-CORE jitter tolerance, jitter transfer and intrinsic jitter criteria.

• Provides termination for SONET Section, Line and Path overhead or SDH Regenerator Section,

Multiplexer Section and High Order Pat h over h ead.

• Provides UTOPIA Level 3 32-bit wide System Interface (clocked up to 104 MHz) with parity support

for ATM applications.

• Provides SATURN POS-PHY Level 3ä 32-bit System Interface (clocked up to 104 MHz) for Packet

over SONET (POS), or ATM applications.

• Supports line loopback from the line side receive stream to the transmit stream and diagnostic

loopback from the line side transmit stream to the line side receive stream interface.

• Provides support for automatic protection switching via a 4-bit LVDS 777.76 MHz port.

• Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

• Provides a generic 16-bit microprocessor bus interface for configuration, control, and status

monitoring.

• Low power 1.8V CMOS core logic with 3.3V CMOS/TTL compatible digital inputs and digital outputs.

PECL inputs and outputs are 3.3V compatible.

• Industrial temperature range (-40C to +85C).

• 416 pin UBGA package.

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 1

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

1.2 SONET Section and Line / SDH Regenerator and Multiplexer Section

• Frames to the SONET/SDH receive stream and inserts the framing bytes (A1, A2) and the section

trace byte (J0) into the transmit stream; descrambles the received stream and scrambles the transmit

stream.

• Calculates and compares the bit interleaved parity (BIP) error detection codes (B1, B2) for the receive

stream. Calculates and inserts B1 and B2 in the transmit stream. Accumulates near end errors (B1,

B2) and far end errors (M1) and inserts line remote error indications (REI) into the M1 byte based on

received B2 errors.

• Detects signal degrade (SD) and signal fail (SF) threshold crossing alarms based on received B1

errors.

• Extracted and optionally inserts on dedicated pins the SONET/SDH transport overhead for an STS-

48c/STM-16c frame.

• Extracts and serializes on dedicated pins the data communication channels (D1-D3, D4-D12) and

inserts the corresponding signals into the transmit stream.

• Extracts and filters the automatic protection switch (APS) channel (K1, K2) bytes into internal

registers. Inserts the APS channel into the transmit stream.

• Extracts and filters the synchronization status message (S1) byte into an internal register for the

receive stream. Inserts the synchronization status message (S1) byte into the transmit stream.

• Extracts a 64 byte (Bellcore compatible) or 16 byte (ITU compatible) section trace (J0) message using

an internal register bank for the receive stream. Detects an unstable message or mismatch message

with an expected message. Provides access to the accepted message via the microprocessor port.

Inserts a 64 byte or 16 byte section trace (J0) message using an internal register bank for the

transmit stream.

• Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line remote defect indication

(RDI-L), line alarm indication signal (AIS-L), and protection switching byte failure alarms on the

receive stream.

• Configurable to force Line AIS in the transmit stream.

• Provides automatic transmit line RDI insertion following detection of various received alarms (LOS,

LOF, LAIS, SD, SF, STIM, STIU).

• Provides automatic DROP bus line AIS insertion following detection of various received alarms (LOS,

LOF, LAIS, SD, SF, STIM, STIU).

• Support Automatic Protection Switching (APS) via a serial 4x777.76 LVDS mate protection port.

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 2

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

1.3 SONET Path / SDH High Order Path

• Interprets the received payload pointer (H1, H2) and extracts the STS-48c/STM-16c synchronous

payload envelope and path overhead.

• Detects loss of pointer (LOP), path alarm indication signal (PAIS) and path (normal and enhanced)

remote defect indication (RDI) for the receive stream. Optionally inserts path alarm indication signal

(PAIS) and path remote defect indication (RDI) in the transmit stream.

• Extracts and insert the entire SONET/SDH path overhead to and from dedicated pins. The path

overhead bytes may be sourced from internal registers or from bit serial path overhead input stream.

Path overhead insertion may also be disabled.

• Extracts the received path payload label (C2) byte into an internal register and detects for payload

label unstable (PLU), payload label mismatch (PLM), payload unequipped (UNEQ) and payload

defect indication (PDI). Inserts the path payload label (C2) byte from an internal register for the

transmit stream.

• Extracts a 64 byte or 16 byte path trace (J1) message using an internal register bank for the receive

stream. Detects an unstable message or mismatch message with an expected message. Provides

access to the captured, accepted and expected message via the microprocessor port. Inserts a 64

byte or 16 byte path trace (J1) message using an internal register bank for the transmit stream.

• Detects received path BIP-8 and counts received path BIP-8 errors for performance monitoring

purposes. BIP-8 errors are selectable to be treated on a bit basis or block basis. Optionally

calculates and inserts path BIP-8 error detection codes for the transmit stream.

• Counts received path remote error indications (REI’s) for performance monitoring purposes.

Optionally inserts the path REI count into the path status byte (G1) based on bit or block BIP-8 errors

detected in the receive path. Reporting of BIP-8 errors is on a bit or block basis independent of the

accumulation of BIP-8 errors.

• Provides automatic transmit path RDI and path Enhanced RDI insertion following detection of various

received alarms (LAIS, LOP, LOPCON, PAIS, PAISCON, PTIM, PTIU, PLM, PLU, UNEQ, PDI).

1.4 The Receive ATM Processor

• Extracts ATM cells from the received STS-48c/STM16-16c channel payloads using ATM cell

delineation.

• Provides ATM cell payload de-scrambling.

• Performs header check sequence (HCS) error detection and correction, and idle/unassigned cell

filtering.

• Detects out of cell delineation (OCD) and loss of cell delineation (LCD) alarms.

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 3

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

• Counts number of received cells, idle cells, erred cells and dropped cells.

• Provides UTOPIA Level 3 and POS-PHY Level 3 32-bit wide datapath interfaces (clocked up to 104

MHz) with parity support to read extracted cells from an internal 8 cell FIFO buffer.

1.5 The Receive POS Processor

• Supports packet based link layer protocols using byte synchronous HDLC framing.

• Performs self-synchronous POS data de-scrambling on the received STS-48c/STM16c-16c payloads

using the x

43

+1 polynomial.

• Performs flag sequence detection and terminates the received POS frames.

• Performs frame check sequence (FCS) validation for CRC-CCITT and CRC-32 polynomials.

• Performs control escape de-stuffing or byte de-stuffing of the POS stream.

• Detects packet abort sequence.

• Checks for minimum and maximum packet lengths. Optionally deletes short packets and marks

those exceeding the maximum length as erred.

• Permits FCS stripping on the POS-PHY output data stream.

• Provides a SATURN POS-PHY Level 3 compliant 32-bit datapath interface (clocked up to 104 MHz)

with parity support to read packet data from an internal 256 byte FIFO buffer.

1.6 The Transmit ATM Processor

• Provides idle/unassigned cell insertion.

• Optionally provides HCS generation/insertion, and ATM cell payload scrambling.

• Counts the number of transmitted cells.

• Provides UTOPIA Level 3 and POS-PHY Level 3 32-bit wide datapath interfaces (clocked up to 104

MHz) with parity support for writing cells into an internal channel FIFO.

1.7 The Transmit POS Processor

• Supports any packet based link layer protocol using byte synchronous and bit synchronous framing

like PPP, HDLC and Frame Relay.

43

• Performs self-synchronous POS data scrambling using the 1+X

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 4

polynomial.

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

• Encapsulates packets within a POS/HDLC frame.

• Performs flag sequence insertion.

• Performs byte stuffing for transparency processing.

• Optionally performs frame check sequence generation using the CRC-CCITT and CRC-32

polynomials.

• Aborts packets under the direction of the host or when the FIFO underflows.

• Provides a SATURN POS-PHY Level 3 compliant 32-bit wide datapath (clocked up to 104 MHz) with

parity support to an internal FIFO buffer.

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 5

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

2 APPLICATIONS

• ATM/ Multi-service Enterprise, Access, Edge and Core switches

• Packet Over Sonet interfaces for Access, Edge and Core routers

• SONET/SDH Add/Drop Multiplexers and Terminal Multiplexers with data processing capabilities

• DWDM Optical networking equipment requiring SONET/SDH capabilities

• Network Interface Cards and Uplinks

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 6

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

3 REFERENCES

• Bell Communications Research - GR-253-CORE “SONET Transport Systems: Common Generic

Criteria”, Issue 2 Revision 2, January 1999.

• Bell Communications Research - GR-436-CORE “Digital Network Synchronization Plan”, Issue 1

Revision 1, June 1996..

• ANSI - T1.105-1995, “Synchronous Optical Network (SONET) – Basic Description including Multiplex

Structure, Rates, and Formats”, 1995.

• ANSI T1.107 - 1995, "Digital Hierarchy - Formats Specifications".

• ANSI T1.107a - 1990, "Digital Hierarchy - Supplement to Formats Specifications (DS3 Format

Applications)".

• ANSI T1.627 - 1993, "Broadband ISDN - ATM Layer Functionality and Specification".

• ETS 300 417-1-1, "Generic Functional Requirements for Synchronous Digital Hierarchy (SDH)

Equipment", January, 1996.

• ITU-T Recommendation G.703 - "Physical/Electrical Characteristics of Hierarchical Digital Interfaces",

1991.

• ITU-T Recommendation G.704 - "General Aspects of Digital Transmission Systems; Terminal

Equipment - Synchronous Frame Structures Used At 1544, 6312, 2048, 8488 and 44 736 kbit/s

Hierarchical Levels", July 1995.

• ITU, Recommendation G.707 - "Network Node Interface For The Synchronous Digital Hierarchy",

1996.

• ITU Recommendation G781, “Structure of Recommendations on Equipment for the Synchronous

Design Hierarchy (SDH)”, January 1994.

• ITU, Recommendation G.783 - "Characteristics of Synchronous Digital Hierarchy (SDH) Equipment

Functional Blocks", 1996.

• ITU Recommendation I.432, “ISDN User Network Interfaces”, 1993.

• ITU Recommendation I.432, “ISDN User Network Interfaces”, March 93.

• ATM Forum - ATM User-Network Interface Specification, V3.1, October, 1995.

• ATM Forum – STR-PHY-UL3-01.00, “UTOPIA Level 3”, April, 1999.

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 7

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

• IETF Network Working Group – RFC-1619, “Point to Point Protocol (PPP) over SONET/SDH

Specification”, May 1994.

• IETF Network Working Group – RFC-1661, “The Point to Point Protocol (PPP)”, July, 1994.

• IETF Network Working Group – RFC-1662, “PPP in HDLC like framing”, July 1994.

• IETF Network Working Group – RFC-2615, “Point to Point Protocol (PPP) over SONET/SDH”, June

1999.

• PMC-980495, “SATURN Compatible Interface for Packet Over SONET Physical Layer and Link Layer

Devices (Level 3)”, Issue 3, Dec. 2, 1998.

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 8

PRELIMINARY

DATASHEET

PMC-2000489 ISSUE 1 SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PMC-Sierra, Inc.

PM5381 S/UNI-2488

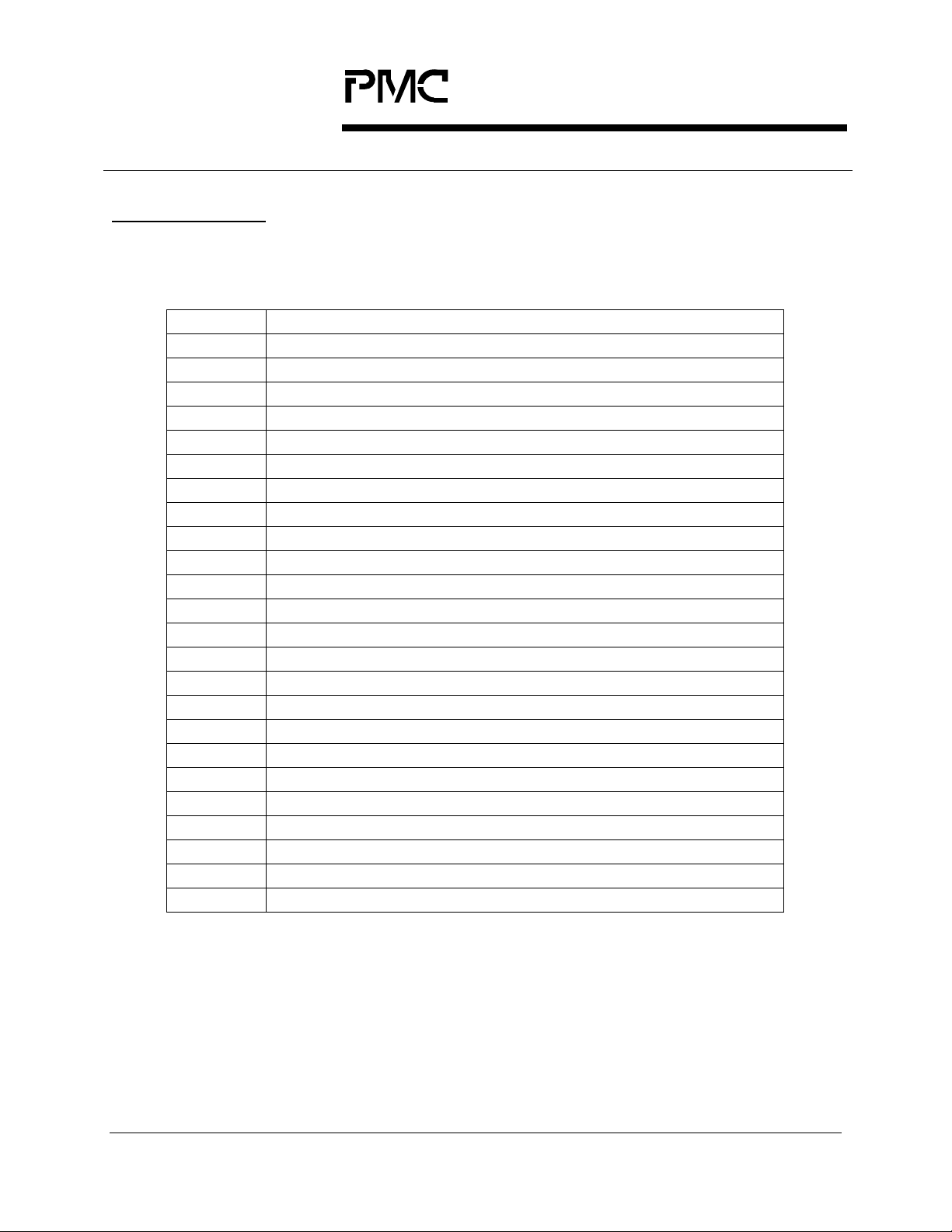

4 DEFINITIONS

The following table defines the abbreviations for the S/UNI-2488.

A TM Asynchronous Transfer Mode

CSU Clock Synthesis Unit

DRU Data Recovery Unit

FCS Frame Check Sequence

FIFO First-In-First-Out storage element

HCS Header Check Sequence

LVDS Low Voltage Differential Signaling

NNI Network-to-Network Interface

POS Packet Over SONET

PRGM PRBS Generator and Monitor

RCFP Receive Cell and Frame Processor Block

RHPP Receive High order Path Processor

RRMP Receive Regenerator Multiplexer Processor

RTTP Received Tail T race Processor

RXSDQ Receive Scalable Data Queue FIFO

RXSIF Receive Slave Interface (UL3 or POS L3)

SRLI SONET/SDH Receive Line Interface

STLI SONET/SDH Transmit Line Imterface

STSI SONET/SDH Time Slot Interchange

SVCA SONET/SDH Virtual Container Aligner

TCFP Transmit Cell and Frame Processor Block

THPP Transmit High order Path Processor

TRMP Transmit Regenerator Multiplexer Processor

TTTP Transmit T ail Trace Processor

TXSIF Transmit Slave Interface (UL3 or POS L3)

Proprietary and Confidentail to PMC-Sierra Inc., and for its Customer’s Internal Use 9

Loading...

Loading...