PMC-Sierra,Inc.

Preliminary

40 Gbit/s Transport Switching Element

PM5372

TSE

FEATURES

• Implements a Time-Space-Time fabric

with STS-1/AU-3 granularity.

• Provides 64 ingress STS-12 equivalent

ports for a total of 64*12 = 768 STS-1

flows.

• Supports non-blocking permutation

switching of 768 STS-1 flows at STS-1

granularity.

• Provides 64 egress STS-12 equivalent

ports consisting of 768 STS-1 flows.

• Interfaces to STS-48 and STS-192

devices by aggregating 4 and 16 STS12 equivalent flows respectively.

• Supports multicast and broadcast of

STS-1 streams.

• Supports STS-12 equivalent flows with

an extended 8B/10B protocol over

777.6 MHz LVDS links.

• Supports multi-plane (inverse

multiplexed) switch architectures in

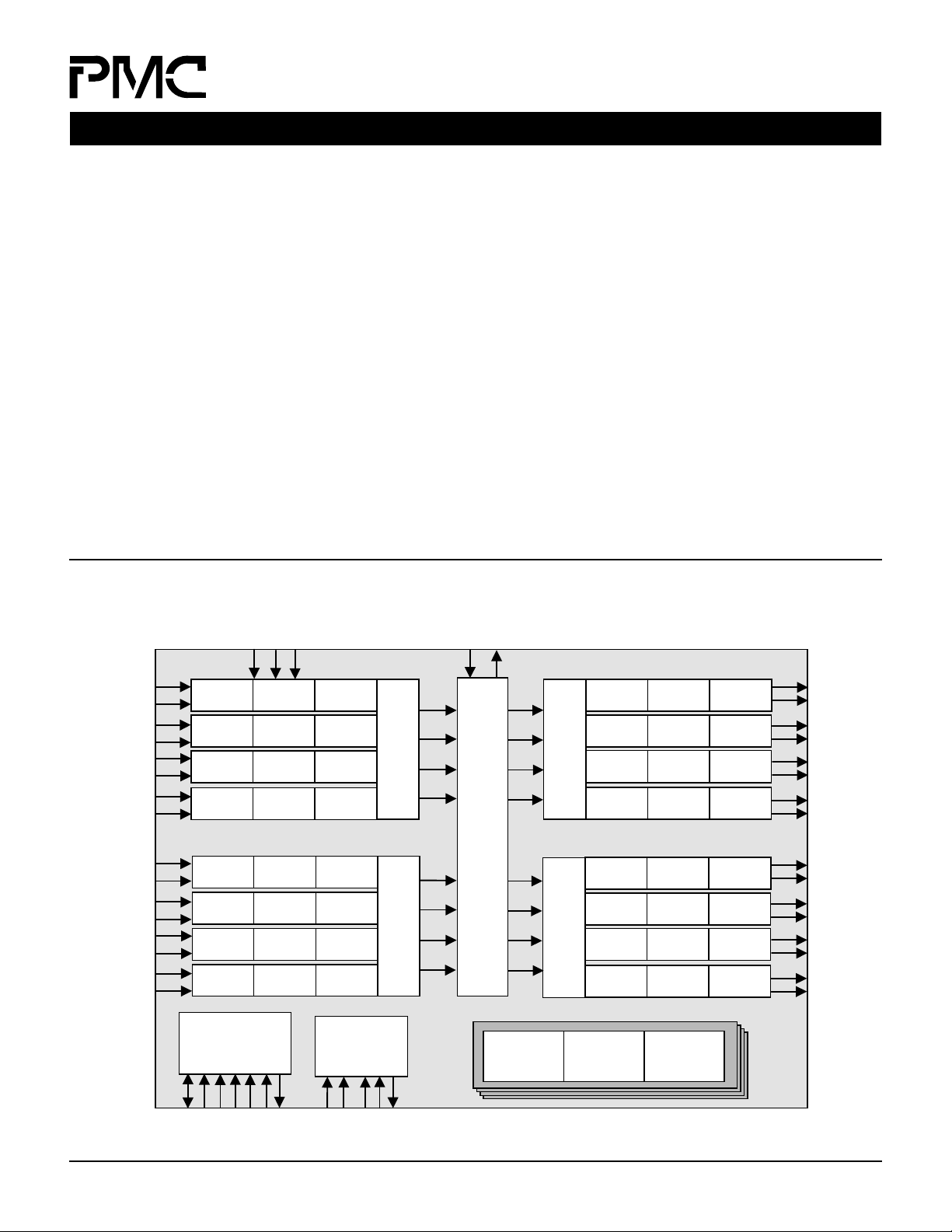

BLOCK DIAGRAM

conjunction with the PM5310 TBS

device and PM7390 S/UNI

®

-MACH48.

• Recovers clock and data at each

ingress port, synchronizes with an

internal 77.76 MHz clock, and

produces egress streams with a

common 777.6 MHz clock.

• Detects and reports inactive or erred

LVDS links via the microprocessor

interface.

• Supports two sets of switch settings

and a controlled method of changing

settings on STS-1 frame boundaries.

• Supports multiple fabric architectures

that range from 40 Gbit/s (1 TSE) to

160 Gbit/s (4 TSE devices) in a single

stage, and up to 2.5 Tbit/s using multistage fabrics.

• Ingress to egress STS-1 switching

latency of approximately 900 ns.

• Supported by an efficient algorithm to

compute control settings for all

permutation loads for all supported

fabric architectures. Algorithms are

also available for multicast/broadcast

allocation.

• 1.8 V CMOS core and 3.3 V

CMOS/LVDS input/output.

• Requires no external RAMs or logic

parts.

• Provides a standard IEEE 1149.1

JTAG port.

• Power Consumption of 13 W

(maximum).

• Packaged in a 520 pin 40mm by 40mm

UltraBGA.

• Supports a 16-bit microprocessor

interface which is used to initialize the

device, to write switch settings into onchip control tables, and to monitor

device performance.

RP[1]

RN[1]

RP[2]

RN[2]

RP[3]

RN[3]

RP[4]

RN[4]

RP[61]

RN[61]

RP[62]

RN[62]

RP[63]

RN[63]

RP[64]

RN[64]

RSTB

LVDS

Receiver

RXLV #1

LVDS

Receiver

RXLV #2

LVDS

Receiver

RXLV #3

LVDS

Receiver

RXLV #4

LVDS

Receiver

RXLV #61

LVDS

Receiver

RXLV #62

LVDS

Receiver

RXLV #63

LVDS

Receiver

RXLV #64

Microprocessor

Interface

Recovery Unit

Recovery Unit

Recovery Unit

Recovery Unit

Recovery Unit

DRU #61

Recovery Unit

DRU #62

Recovery Unit

DRU #63

Recovery Unit

DRU #64

SYSCLK

Data

DRU #1

Data

DRU #2

Data

DRU #3

Data

DRU #4

Data

Data

Data

Data

CMP

Frame Aligner

Frame Aligner

Frame Aligner

Frame Aligner

• • •

Frame Aligner

Frame Aligner

Frame Aligner

Frame Aligner

Rx 8b/10b

R8FA#1

Rx 8b/10b

R8FA#2

Rx 8b/10b

R8FA#3

Rx 8b/10b

R8FA#4

Rx 8b/10b

R8FA#61

Rx 8b/10b

R8FA#62

Rx 8b/10b

R8FA#63

Rx 8b/10b

R8FA#64

JTAG

Ingress

Time

Switch

Element

ITSE #1

Ingress

Time

Switch

Element

ITSE

#16

RJOFP

Cross-

bar

Space

Switch

Element

SSWT

TJOFP

CSTR

Egress

Time

Switch

Element

ETSE

#1

Egress

Time

Switch

Element

ETSE

#16

Tx 8b/10b

Disp. Encoder

T8DE#1

Tx 8b/10b

Disp. Encoder

T8DE#2

Tx 8b/10b

Disp. Encoder

T8DE#3

Tx 8b/10b

Disp. Encoder

T8DE#4

Tx 8b/10b

Disp. Encoder

T8DE#61

Tx 8b/10b

Disp. Encoder

T8DE#62

Tx 8b/10b

Disp. Encoder

T8DE#63

Tx 8b/10b

Disp. Encoder

T8DE#64

Clock

Synthesizer

CSU

Serializer

PISO #1

Serializer

PISO #2

Serializer

PISO #3

Serializer

PISO #4

• • •

Serializer

PISO #61

Serializer

PISO #62

Serializer

PISO #63

Serializer

PISO #64

LVDS Transmit

Reference

TXREF

LVDS

Transmitter

TXLV #1

LVDS

Transmitter

TXLV #2

LVDS

Transmitter

TXLV #3

LVDS

Transmitter

TXLV #4

LVDS

Transmitter

TXLV #61

LVDS

Transmitter

TXLV #62

LVDS

Transmitter

TXLV #63

LVDS

Transmitter

TXLV #64

TP[1]

TN[1]

TP[2]

TN[2]

TP[3]

TN[3]

TP[4]

TN[4]

TP[61]

TN[61]

TP[62]

TN[62]

TP[63]

TN[63]

TP[64]

TN[64]

ALE

CSB

RDB

INTB

A[12:0]

D[15:0]

PMC-2000328 (P1) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2000

WRB

TRSTB

TCK

TMS

TDI

TDO

40 Gbit/s Transport Switching Element

Preliminary

PM5372 TSE

APPLICATIONS

In combination with the PM5310 TBS

(TelecomBus Serializer and Time-Space

switching stage), the PM5315

SPECTRA-2488, the PM5316

SPECTRA-4X155, and the PM7390

S/UNI-MACH48, the PM5372 TSE

supports a variety of flexible Layer 1 /

Layer 2 architectures. These architectures can implement features commonly

found in DCS, ADM, and multi-service

switch/router equipment.

The PM5372 TSE provides the functionality that enables networking equipment

to:

• Connect to (multiple) SONET rings.

• Participate in mesh-connected

architectures.

• Serve as SONET-connected terminal

multiplexers.

• Groom traffic at STS-1/AU-3

granularity.

• Support channelization of OC3/12/48/192 line rates.

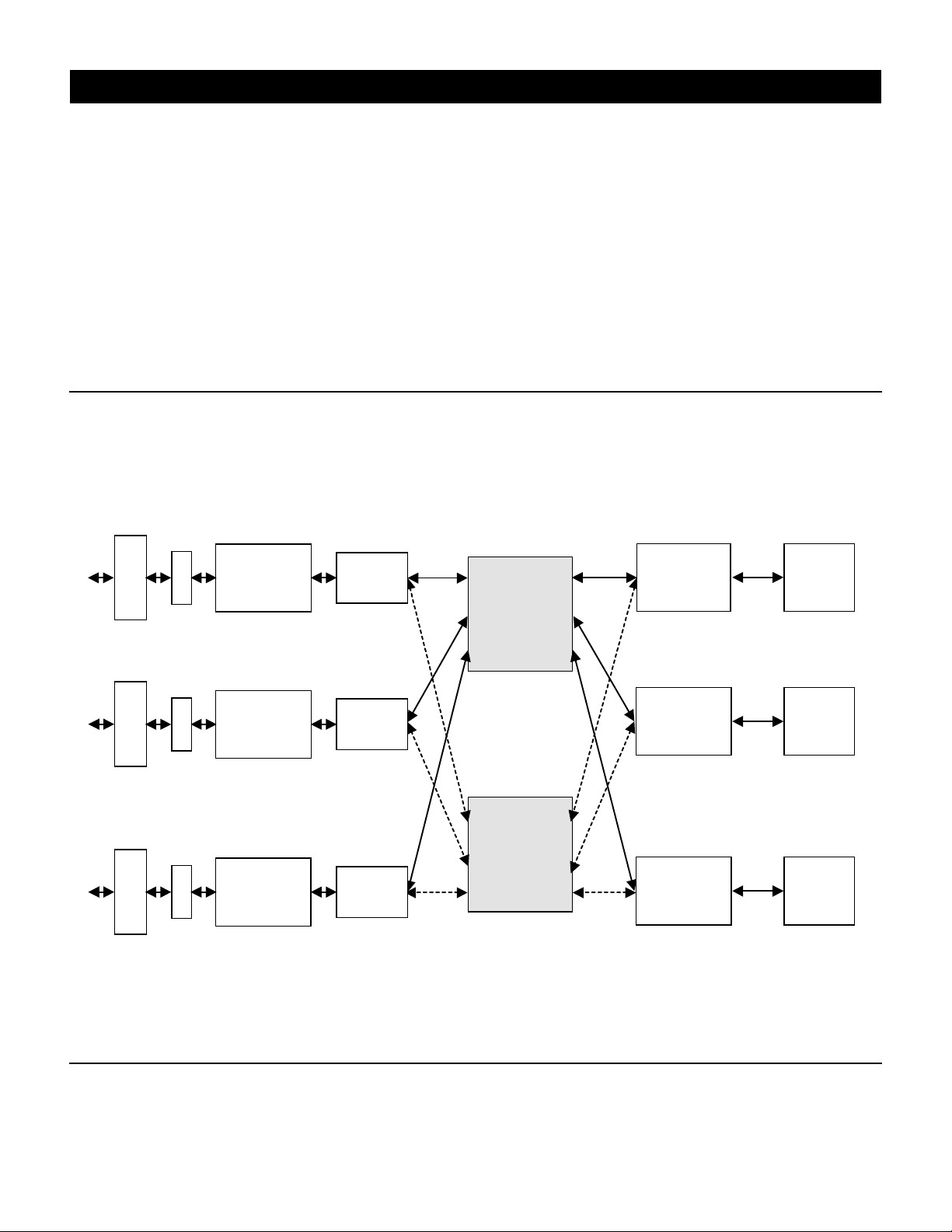

TYPICAL APPLICATIONS

MULTI-SERVICE ATM/POS SWITCH PORT APPLICATION

SONET Ring/PHY Layer 40 Gbit/s STS-1 Fabric Multi-Service Layer

1

OC-48

Optical

Transceiver

SPECTRA-2488

SERDES

PM5315

PM5310

TBS

4x777.6 MHz

LVDS Links

•

•

N

OC-48

Optical

Transceiver

SERDES

•

PM5315

SPECTRA-2488

PM5310

TBS

PM5372

TSE

(Working X-

Connect)

4x777.6 MHz

LVDS Links

• Support concatenated lines rates

including STS-1 (DS-3), STS-3c, STS12c, STS-48c and STS-192c.

• Support add, drop, and drop-andcontinue.

• Support UPSR, 2-BLSR, 4-BLSR, and

1+1 or 1:N APS.

• Support mesh-based APS systems.

1

PM7390

S/UNI-MACH48

POS-PHY

Level 3/

UTOPIA

Level 3

ATM Layer

Device

•

•

•

N

POS-PHY

PM7390

S/UNI-MACH48

Level 3

IP Layer

Device

8

OC-48

Optical

Transceiver

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

•

•

•

PM5315

SPECTRA-2488

SERDES

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5310

TBS

4x777.6 MHz

LVDS Links

PM5372

TSE

(Protection X-

Connect)

4x777.6 MHz

LVDS Links

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

PM7390

S/UNI-MACH48

•

•

•

8

POS-PHY

Level 3

PMC-2000328 (P1)

© Copyright PMC-Sierra,

Inc. 2000. All rights reserved.

March 2000

S/UNI is a registered

trademark of PMC-Sierra,

Inc.

ATM or

IP Layer

Device

Loading...

Loading...