PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

PM5371

TUDX

SONET/SDH TRIBUT ARY UNIT

CROSS CONNECT

DATA SHEET

ISSUE 6: SEPTEMBER 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

REVISION HISTORY

Issue No. Issue Date Details of Change

6 September

1998

1. Corrected some formatting problems.

2. Corrected documentation errata from TUDX

errata document (issue 1). Issue 1 errata is now

obsolete.

3. Issue 5 contained two different mechanical

diagrams. Incorrect diagram was removed.

4. All references to PQFP changed to MQFP which

is a more technically correct description of the

package.

5 July 1998 Data Sheet Reformatted — No Change in Technical

Content.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

CONTENTS

1 FEATURES....................................................................................1

2 APPLICATIONS.............................................................................2

3 REFERENCES..............................................................................3

4 APPLICATION EXAMPLES...........................................................4

5 BLOCK DIAGRAM.........................................................................7

6 DESCRIPTION..............................................................................9

7 PIN DIAGRAM.............................................................................10

8 PIN DESCRIPTION.....................................................................11

9 FUNCTIONAL DESCRIPTION....................................................23

9.1 INPUT BUS FORMATTER................................................23

9.2 OUTPUT BUS FORMATTER............................................23

9.3 SWITCHING ELEMENT ...................................................24

9.3.1 DATA MEMORIES..................................................25

9.3.2 CONNECTION MEMORY ......................................25

9.3.3 TIMING GENERATOR ...........................................26

9.3.4 OUTPUT MULTIPLEXER.......................................26

9.3.5 COMMON BUS INTERFACE.................................26

9.4 MICROPROCESSOR INTERFACE ..................................27

10 NORMAL MODE REGISTER DESCRIPTION.............................28

11 TEST FEATURES DESCRIPTION ..............................................47

11.1 I/O TEST MODE ...............................................................51

12 OPERATION................................................................................53

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

12.1 BASIC CONNECTION MEMORY ACCESS......................53

12.1.1CONNECTION MEMORY READ...........................53

12.1.2CONNECTION MEMORY WRITE..........................53

12.2 CONNECTION SET UP....................................................54

12.3 IDLE CODE INSERTION..................................................56

13 FUNCTIONAL TIMING ................................................................58

14 ABSOLUTE MAXIMUM RATINGS...............................................66

15 D.C. CHARACTERISTICS ...........................................................67

16 MICROPROCESSOR INTERFACE TIMING

CHARACTERISTICS...................................................................70

17 TUDX TIMING CHARACTERISTICS...........................................77

18 ORDERING AND THERMAL INFORMATION .............................82

19 MECHANICAL INFORMATION....................................................83

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

LIST OF REGISTERS

REGISTER 00H: MASTER CONFIGURATION......................................29

REGISTER 01H: CONNECTION MEMORY CONTROL ........................31

REGISTER 02H: CLOCK MONITOR...................................................... 32

REGISTER 03H: MASTER RESET/REVISION ID.................................34

REGISTER 04H: PARITY CONFIGURATION.........................................35

REGISTER 05H: PARITY ERROR INTERRUPT ENABLE.....................36

REGISTER 06H: PARITY ERROR INTERRUPT STATUS......................37

REGISTER 07H: SYSTOLIC DELAY CONTROL...................................38

REGISTER 08H,0CH: CONNECTION ADDRESS HIGH.......................40

REGISTER 09H,0DH: CONNECTION ADDRESS LOW........................42

REGISTER 0AH,0EH: CONNECTION DATA HIGH................................43

REGISTER 0BH,0FH: CONNECTION DATA LOW.................................46

REGISTER 10H: MASTER TEST...........................................................49

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

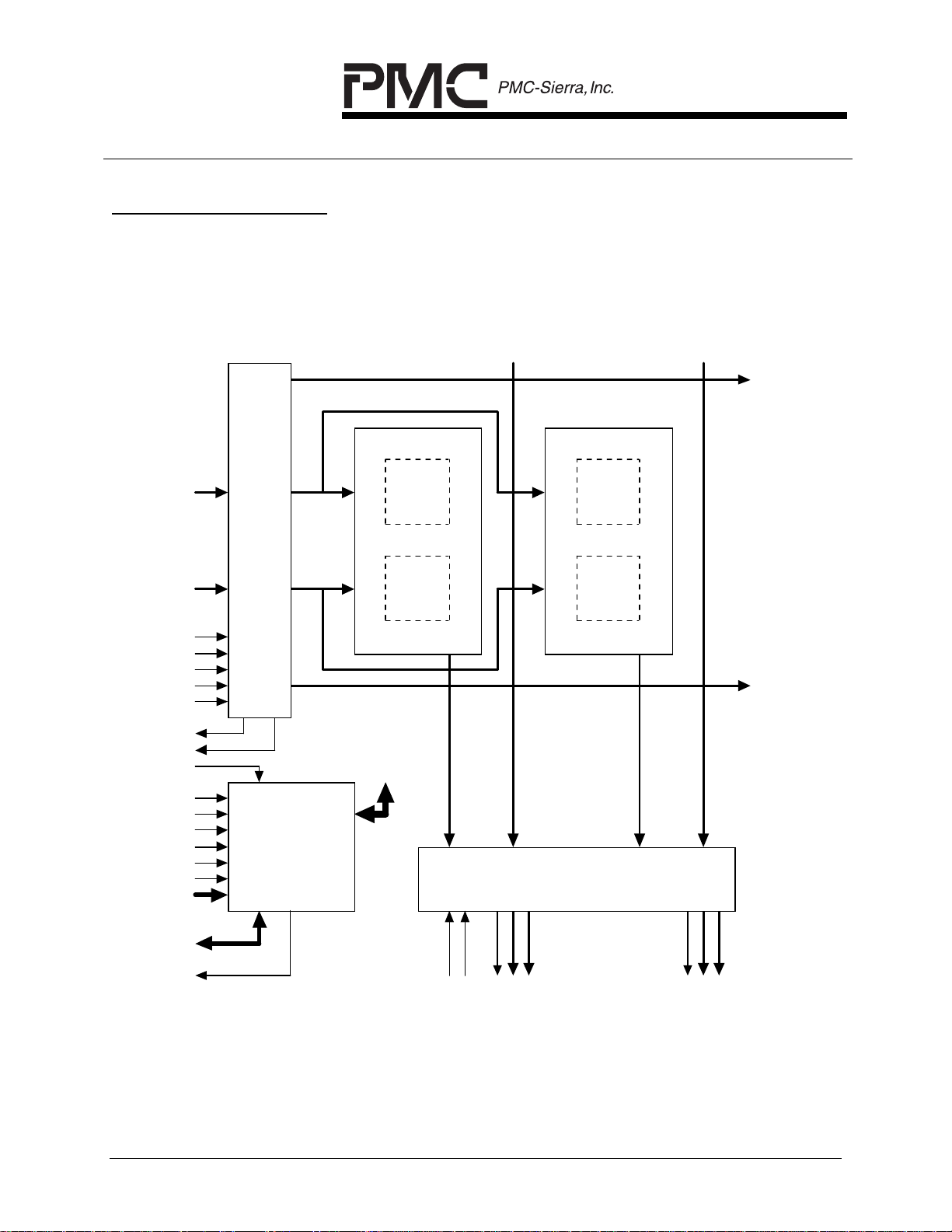

LIST OF FIGURES

FIGURE 1 - 2 X 2 TUDX SWITCH ARRAY USING SYSTOLIC

INTERCONNECT ..........................................................................4

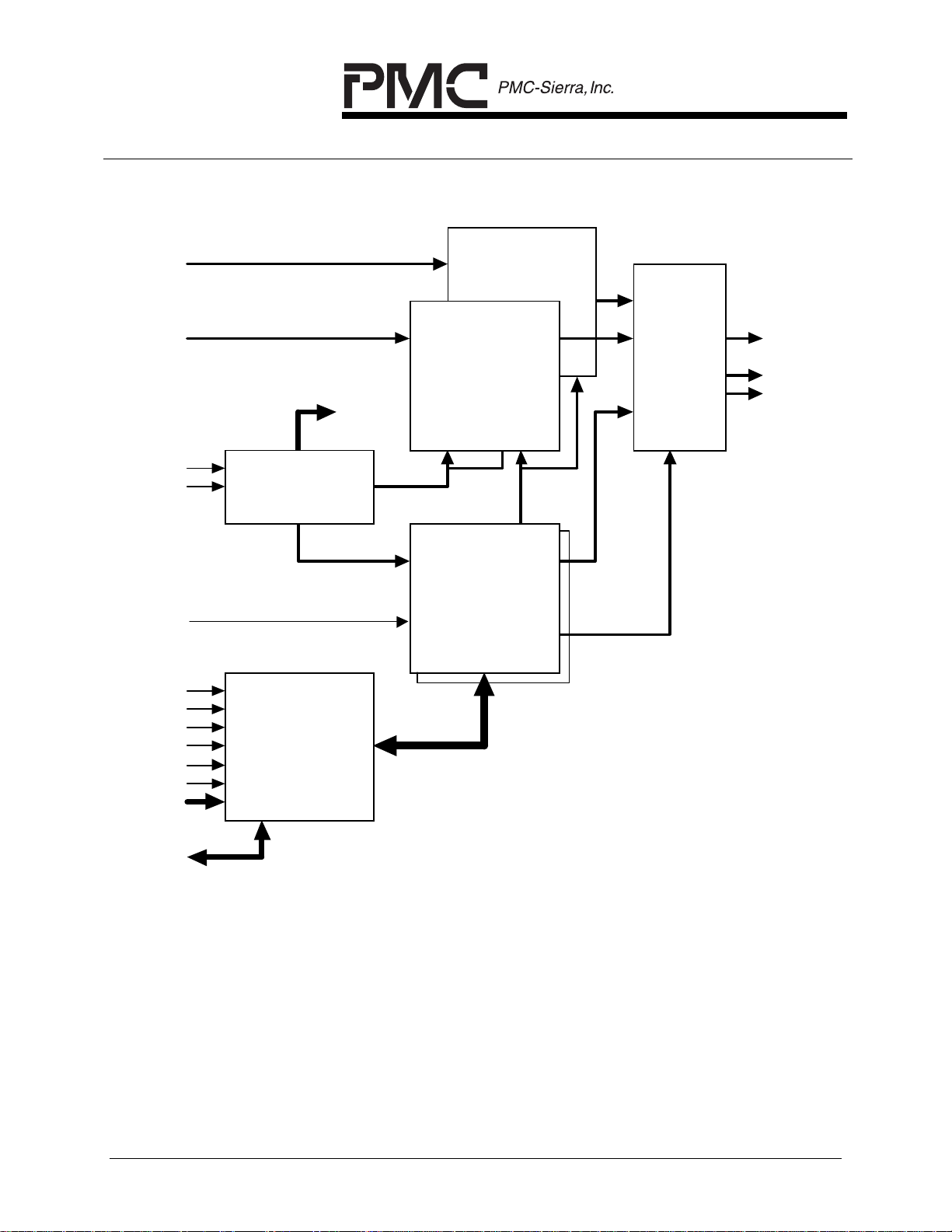

FIGURE 2 - 2 X 2 TUDX SWITCH ARRAY USING BUSED

INTERCONNECT ..........................................................................5

FIGURE 3 - 2 X 2 TUDX SWITCH ARRAY USING HYBRID

INTERCONNECT ..........................................................................6

FIGURE 4 - OVERALL DEVICE..............................................................7

FIGURE 5 - EACH SWITCHING ELEMENT...........................................8

FIGURE 6 - SONET STS-3 CARRYING VT1.5 WITHIN STS-1............55

FIGURE 7 - SDH STM-1 CARRYING TU12 WITHIN VC3/AU3.............56

FIGURE 8 - SDH STM-1 CARRYING TU12 WITHIN TUG3..................56

FIGURE 9 - INPUT/OUTPUT BUS TIMING (SYSTOLIC DELAY

DISABLED)..................................................................................59

FIGURE 10- INPUT/OUTPUT BUS TIMING (SYSTOLIC DELAY

APPLIED TO SINL/SINR) ............................................................60

FIGURE 11- INPUT/OUTPUT BUS TIMING (SYSTOLIC DELAY

APPLIED TO DINT/DINB)............................................................61

FIGURE 12- INPUT/OUTPUT BUS TIMING (SYSTOLIC DELAY

APPLIED TO DOUTL/DOUTR)....................................................62

FIGURE 13- INPUT/OUTPUT BUS TIMING (SYSTOLIC DELAY

APPLIED TO SOUTT/SOUTB).....................................................64

FIGURE 14- PAGE TIMING....................................................................65

FIGURE 15- MICROPROCESSOR INTERFACE READ ACCESS

TIMING FOR INTEL MODE.........................................................71

FIGURE 16- MICROPROCESSOR INTERFACE READ ACCESS

TIMING FOR MOTOROLA MODE...............................................72

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

FIGURE 17- MICROPROCESSOR INTERFACE WRITE ACCESS

TIMING FOR INTEL MODE.........................................................74

FIGURE 18- MICROPROCESSOR INTERFACE WRITE ACCESS

TIMING FOR MOTOROLA MODE...............................................75

FIGURE 19- INPUT TIMING..................................................................78

FIGURE 20- OUTPUT TIMING..............................................................80

FIGURE 21- METRIC QUAD FLAT PACK – MQFP (BODY

28X28X3.49MM)..........................................................................83

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

LIST OF TABLES

TABLE 1 - REGISTER MEMORY MAP ..............................................27

TABLE 2 - SYSTOLIC DELAY CONTROL..........................................38

TABLE 3 - SYSTOLIC ARRAY DELAY CONTROL.............................39

TABLE 4 - TEST MODE REGISTER MEMORY MAP.........................47

TABLE 5 - READING INPUT PIN VALUES.........................................51

TABLE 6 - FORCING OUPUT PIN VALUES.......................................51

TABLE 7 - CONNECTION SET UP ....................................................55

TABLE 8 - IDLE CODE INSERTION...................................................57

TABLE 9 - TUDX MAXIMUM RATINGS..............................................66

TABLE 10 - TUDX D.C. CHARACTERISTICS ......................................67

TABLE 11 - MICROPROCESSOR INTERFACE READ ACCESS

(FIGURE 15, FIGURE 16) ...........................................................70

TABLE 12 - MICROPROCESSOR INTERFACE WRITE ACCESS

(FIGURE 17, FIGURE 18) ...........................................................73

TABLE 13 - TUDX INPUT (FIGURE 19)...............................................77

TABLE 14 - TUDX OUTPUT (FIGURE 20)...........................................79

TABLE 15 - SYSTOLIC OUTPUT CONFIGURATION...........................79

TABLE 16 - BUSED OUTPUT CONFIGURATION................................79

TABLE 17 - PARALLEL BUSED OUTPUT CONFIGURATION .............79

TABLE 18 - ORDERING PM5372-RI....................................................82

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

1

FEATURES

•

A single stage, non-blocking array of time switches for cross-connecting

SONET virtual tributaries (VTs) or SDH tributary units (TUs).

•

Provides non-blocking switching between two STS-3 (STM-1) byte serial input

streams and two STS-3 (STM-1) byte serial output streams.

•

Operates from a single 19.44 MHz clock.

•

Provides parity checking on input data buses and parity generation on output

data buses.

•

Allows programmable idle code insertion on a per VT or per TU basis.

•

Permits switching of any combination of SONET VT1.5, VT2, VT3, VT6, or

STS-1 channels. Permits switching of any combination of SDH TU11, TU12,

TU2, or TU3 channels.

•

Operates in conjunction with the PM5361 TUDX SONET/SDH Tributary Unit

Payload Processor which aligns SONET VTs or SDH TUs such that they can

be switched by the TUDX.

•

Cascadable in a systolic or bused manner to allow larger switching arrays to

be implemented. Provides control outputs that are programmable on a per

timeslot basis to facilitate construction of larger switching arrays.

•

Provides programmable delay to match data skew in the systolic array

application.

•

Provides a generic 8-bit microprocessor bus interface for configuration,

control, and status monitoring.

•

Low power, +5 Volt, CMOS technology. Device has TTL compatible inputs

and outputs.

•

160 pin metric quad flat pack (MQFP) package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

2

APPLICATIONS

•

SONET and SDH Wideband Cross-Connects

•

SONET and SDH Add-Drop and Terminal Multiplexers

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

3

REFERENCES

1. American National Standard for Telecommunications - Digital Hierarchy -

Optical Interface Rates and Formats Specification, ANSI T1.105-1988.

2. Bell Communications Research - SONET Transport Systems: Common

Generic Criteria, TR-TSY-000253, Issue 1, September 1989.

3. CCITT Blue Book, Recommendation G.708 - "Netwo rk Node Interface For

The Synchronous Digital Hierarchy", Volume III, Fascicle III.4, 1988.

4. CCITT Blue Book, Recommendation G.709 - "Synchronous Multiplexing

Structure", Volume III, Fascicle III.4, 1988.

5. CCITT Study Group XVIII, Report R 33 - "Recommendations Drafted By

Working Party XVIII/7" (Digital Hierarchies) To Be Approved In 1990 Including

Revised Draft Recommendations G.708 and G.709", June 1990.

6. Bell Communications Research - SONET Transport Systems: Common

Generic Criteria, TA-NWT-000253, Issue 6, September 1990.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

4

APPLICATION EXAMPLES

Larger switching arrays can be constructed in a variety of manners using arrays

of TUDX devices. Systolic or bused interconnect methods can be used, or a

hybrid of the two approaches.

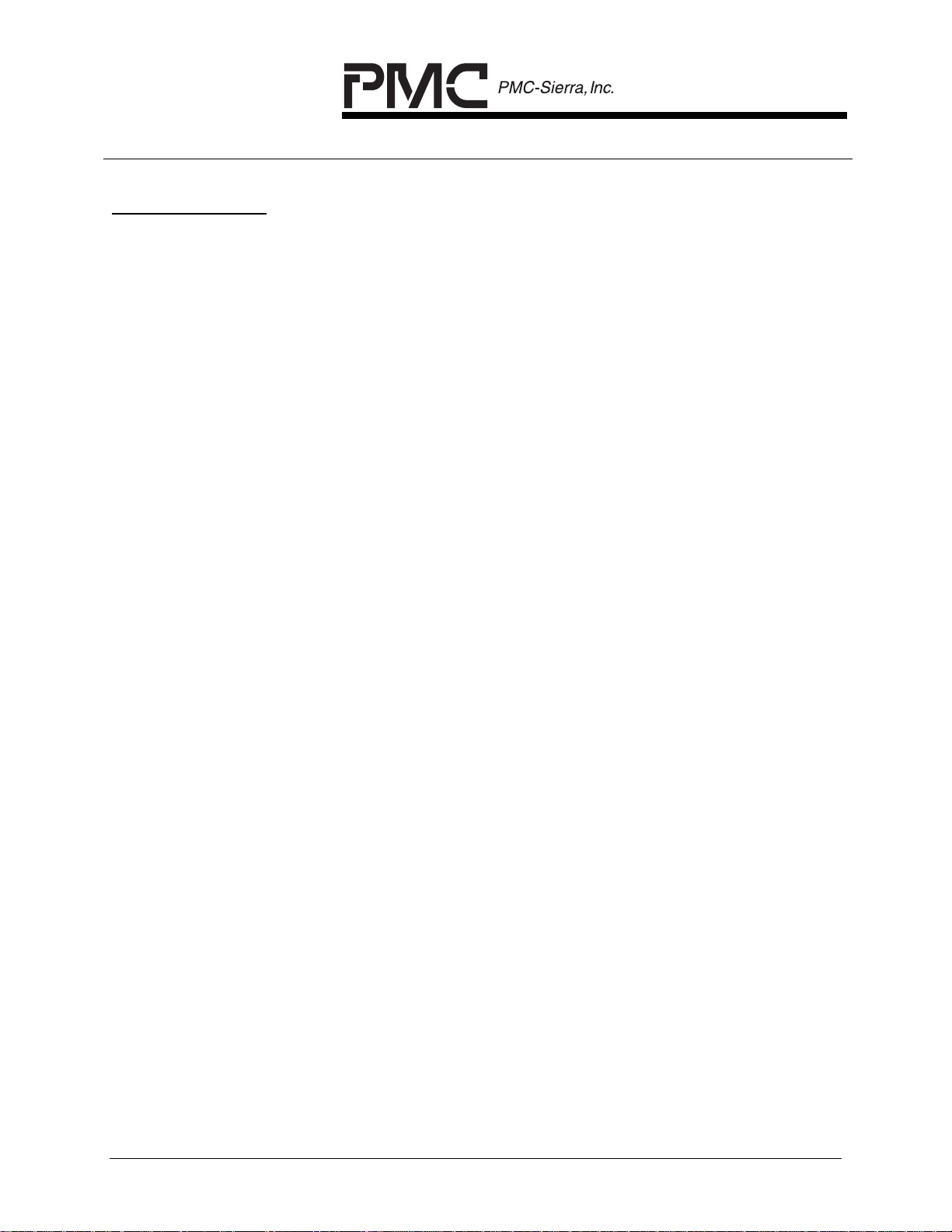

Figure 1 - 2 X 2 TUDX Switch Array Using Systolic Interconnect

SINL

TUDX

DOUTL

SINL

TUDX

DOUTL

'0'

SINR

IFP

OFP

'15'

ODEB

DOUTR

SINR

IFP

OFP

'15'

ODEB

DOUTR

'0'

'0'

'0'

SINL

SINR

SCLK

SFP

TUDX

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

DOUTL

IFP

OFP

ODEB

DOUTR

'5' '10'

SINL

SINR

SCLK

SFP

TUDX

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

DOUTL

IFP

OFP

ODEB

DOUTR

'5'

'10'

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

'15'

'15'

Systolic interconnect of TUDX devices is illustrated above. In this 2 x 2 array of

devices, PCM data is distributed left to right and gathered top to bottom with the

PCM data being re-timed as it passes through each device. Each PCM data bus

drives a single device, regardless of the size of the array and thus systolic

interconnect allows large arrays to be implemented without the use of additional

devices. In this example no systolic delay is required for the upper left hand and

lower right hand TUDX in the array. The Systolic Delay Control Register of the

lower left hand TUDX is programmed to insert a 5 clock period delay in the

DINT/DINB buses, and a 5 clock period delay in the DOUTL/DOUTR bu ses. The

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Systolic Delay Control Register of the upper right hand TUDX is programmed to

insert a 5 clock period delay in the SINL/SINR buses, and the SOUTT/SOUTB

buses.

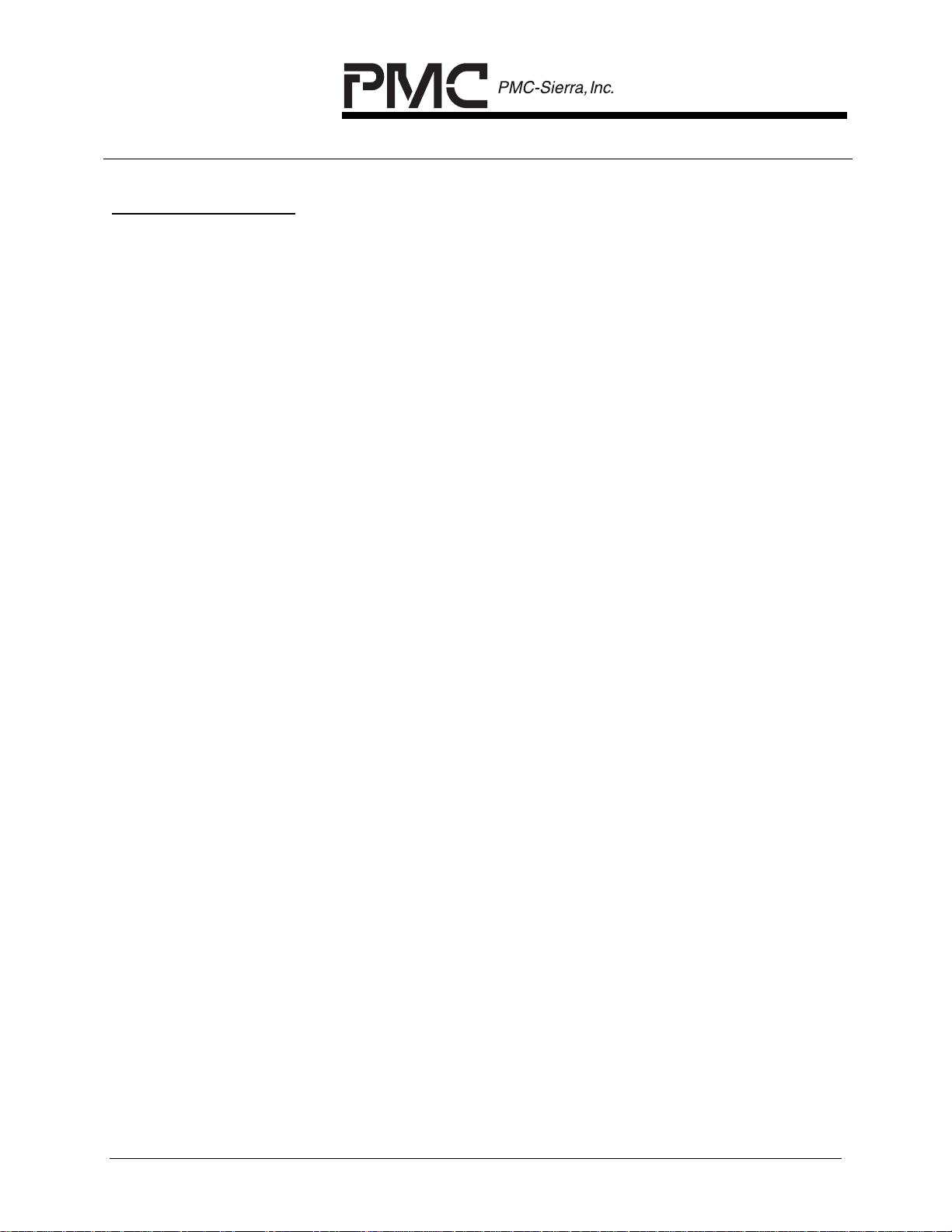

Figure 2 - 2 X 2 TUDX Switch Array Using Bused Interconnect

'5'

'0'

SINL

DOUTL

TUDX

SINR

OFP

IFP

ODEB

DOUTR

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

SINL

DOUTL

SINR

TUDX

DOUTR

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

'0'

SINL

DOUTL

SINR

TUDX

DOUTR

SINL

DOUTL

TUDX

SINR

OFP

IFP

ODEB

DOUTR

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

'5'

'0'

OFP

IFP

ODEB

'0'

OFP

IFP

ODEB

'5''5'

Bused interconnect of TUDX devices is illustrated above. In this 2 x 2 array of

devices, PCM data is distributed left to right on a common bus and gathered top

to bottom using a wired-OR type bus. Using this interconnect approach,

additional devices must be used to drive the distribution bus and sample the

wired-OR bus. To maximize the size of array that can be achieved using a wiredOR bus, the AOUTL and AOUTR buses may be parallel connected with the

DOUTL and DOUTR buses on a bit by bit basis in order to provide higher drive

levels. Due to the higher fan out of these buses, and the RC delay on the wiredOR bus, this approach cannot be extended to very large arrays without additional

circuitry. This bused array approach provides the minimum data delay through

the array (when a cross connection is made between the DINT/DINB buses and

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

the DOUTL/DOUTR buses) of nominally 275 clock periods versus 285 clock

periods using the systolic array approach.

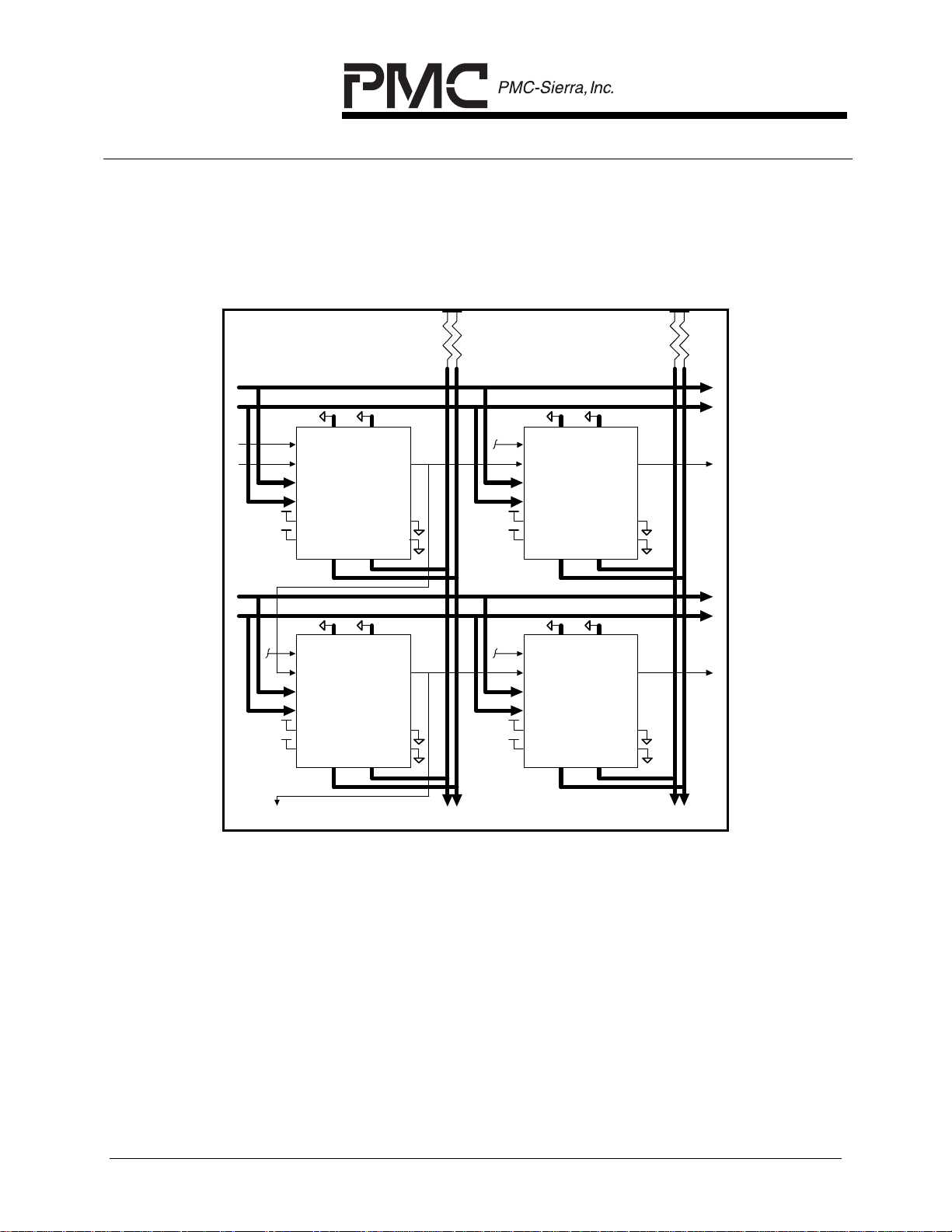

Figure 3 - 2 X 2 TUDX Switch Array Using Hybrid Interconnect

'0'

'0'

'0'

SINL

SINR

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

TUDX

DOUTL

OFP

IFP

ODEB

DOUTR

'5'

SINL

SINR

SCLK

SFP

DINT SOUTT

DINB

OFSEB

SOBEB AOBEB

TUDX

DOUTL

OFP

IFP

SOUTB

ODEB

DOUTR

'0'

SINL

SINR

SCLK

SFP

DINT SOUTT

DINB SOUTB

OFSEB

SOBEB AOBEB

TUDX

DOUTL

OFP

IFP

ODEB

DOUTR

'5'

SINL

SINR

SCLK

SFP

DINT SOUTT

DINB

OFSEB

SOBEB AOBEB

TUDX

DOUTL

OFP

IFP

SOUTB

ODEB

DOUTR

'0'

'0'

'10''10'

A hybrid approach using a mix of bused and systolic interconnect of TUDX

devices is illustrated above. In this 2 x 2 array of devices, PCM data is distributed

left to right on a common bus and gathered top to bottom with the PCM data

being re-timed as it passes through each device. Using this interconnect

approach, additional devices must be used to drive the distribution buses. This

approach overcomes the RC delay of the wired-OR bus by using systolic

interconnect from top to bottom. In this example the Systolic Delay Control

registers in the two bottom TUDX devices are programmed to delay the

DINT/DINB buses by five clock periods to match the delay seen at the

SINL/SINR inputs to these devices.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

5

BLOCK DIAGRAM

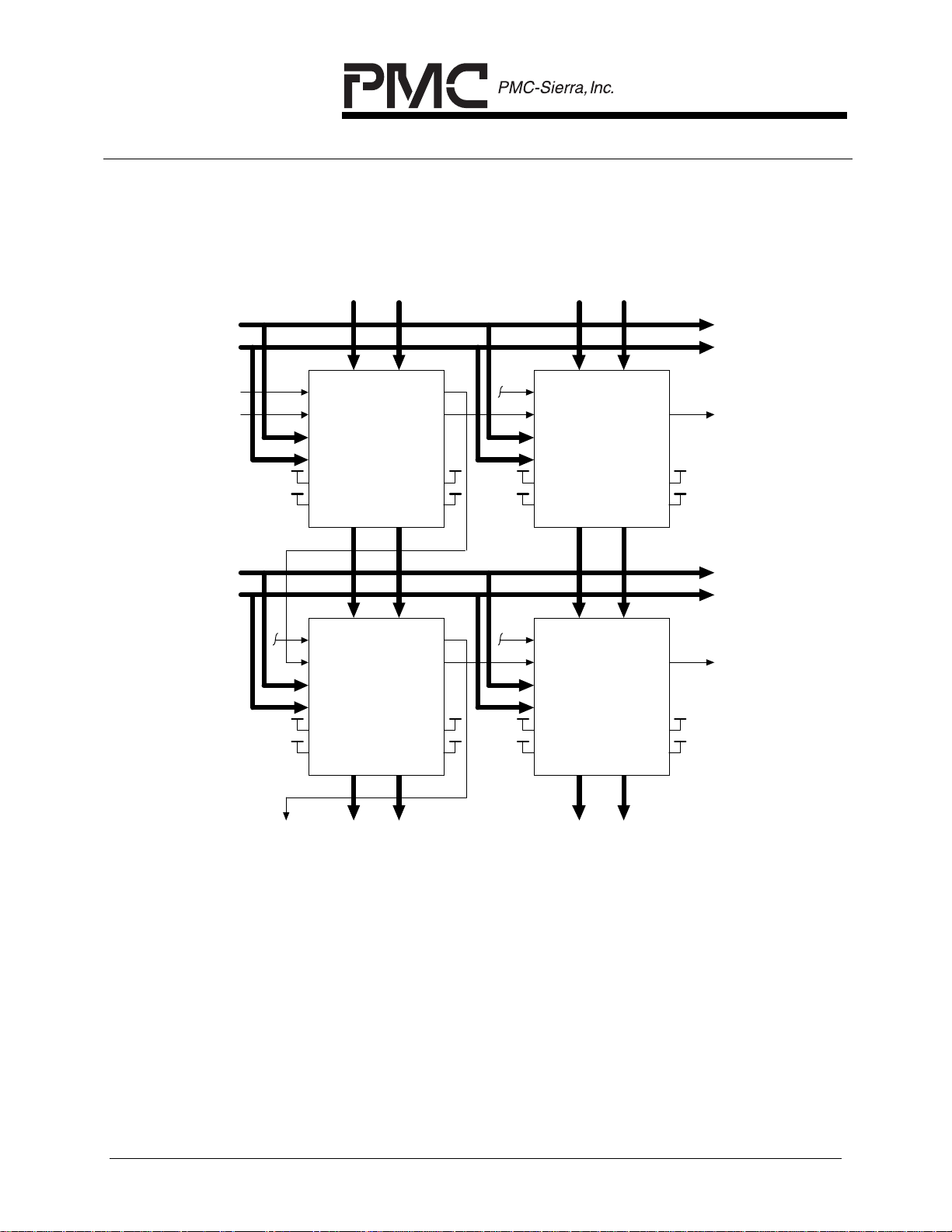

Figure 4 - Overall Device

INPUT BUS FORMATTER

INPUT

DINT[8:0]

DINB[8:0]

SCLK

PAGE

SOBEB

SFP

OFSEB

BUS

FORMATTER

SWITCHING

TIME

SWITCH

ELEMENT

TIME

SWITCH

SINL[8:0]

SINR[8:0]

SOUTT[8:0]

SWITCHING

TIME

SWITCH

ELEMENT

TIME

SWITCH

SOUTB[8:0]

IFP

OFP

MBEB

RSTB

CS1B

CS2B

RDB

WRB

ALE

A[4:0]

D[7:0]

INTB

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

MICRO

INTERFACE

OUTPUT BUS FORMATTER

ODEB

AOBEB

DOUTL[8:0]

AOUTL[8:0]

COUTL

AOUTR[8:0]

DOUTR[8:0]

COUTR

7

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Figure 5 - Each Switching Element

DINT[7:0]

DINB[7:0]

SCLK

SFP

PAGE

RSTB

TSTB

BSB

RDB

WRB

TRSB

A[1:0]

PCM

PCM

TIMING

TIMING

GENERATOR

READ ADDRESS

COMMON

BUS

INTERFACE

DATA

MEMORY

WRITE ADDRESS

CONNECTION

MEMORY

DATA

MEMORY

READ

ADDRESS

PCM

PCM

IDLE

CODE

OUTPUT

MUX

CONTROL

DOUT[7:0]

MAKE

COUT

D[7:0]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

6

DESCRIPTION

The PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect is a monolithic

integrated circuit that allows non-blocking switching of tributaries within two

SONET STS-3 or SDH STM-1 streams. Any tributary entering on either stream

can be connected to any same size tributary within either outgoing stream. The

TUDX can be programmed to cross-connect a mix of SONET VT1.5, VT2, VT3,

VT6, or STS-1 channels or SDH TU11, TU12, TU2, or TU3 channels.

Programmable idle code can also be inserted into any of these channels. The

TUDX allows cross-connection of up to 168 VT1.5 or TU11 streams, up to 126

VT2 or TU12 streams, or up to 42 VT6 or TU2 streams or any legal mix as

permitted by the SONET or SDH mappings.

The TUDX operates in conjunction with the PM5361 TUPP SONET/SDH

Tributary Unit Payload Processor which aligns SONET VTs or SDH TUs such that

they can be switched by the TUDX. Larger switches can be constructed using

arrays of TUDX devices. The TUDX is cascadable in a systolic or bused manner

and provides programmable control outputs that are useful in constructing larger

switching arrays.

No high speed clocks are required as the TUDX operates from a single 19.44

MHz clock. Parity checking is provided on input data buses and parity generation

is provided on output data buses. The TUDX is configured, controlled and

monitored via a generic 8-bit microprocessor bus interface.

The TUDX is implemented in low power, +5 Volt, CMOS technology. It has TTL

compatible inputs and outputs and is packaged in a 160 pin metric quad flat pack

(MQFP) package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

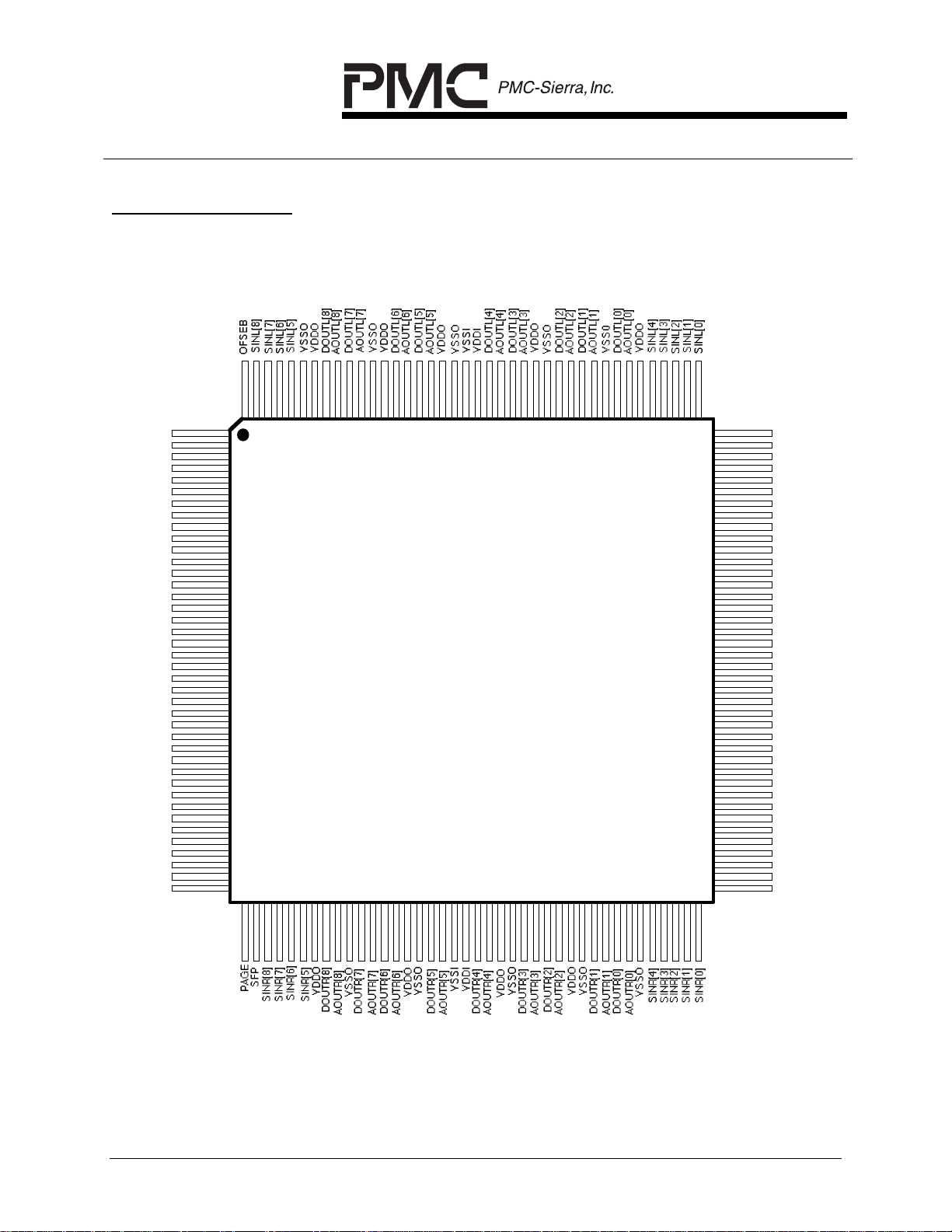

7

PIN 1

ODEB

AOBEB

DINT[0]

DINT[1]

DINT[2]

DINT[3]

DINT[4]

DINT[5]

DINT[6]

DINT[7]

DINT[8]

CS1B

CS2B

DINB[0]

VDDI

VSSI

DINB[1]

DINB[2]

DINB[3]

DINB[4]

DINB[5]

DINB[6]

DINB[7]

DINB[8]

SOBEB

VSSO

VDDO

PIN 40

PIN DIAGRAM

The TUDX is packaged in an 160 pin MQFP package having a body size of

28 mm by 28 mm and a pin pitch of 0.65 mm.

PIN 160

A[0]

A[1]

A[2]

A[3]

A[4]

Index

PIN 121

PM5371

TUDX

(TOP VIEW)

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

PIN 120

COUTL

VDDO

VSSO

SOUTT[0]

SOUTT[1]

SOUTT[2]

SOUTT[3]

SOUTT[4]

SOUTT[5]

SOUTT[6]

SOUTT[7]

SOUTT[8]

VDDO

VSSO

INTB

MBEB

RSTB

ALE

RDB_E

WRB_RWB

VDDI

VSSI

VSSO

SCLK

VDDO

SOUTB[0]

SOUTB[1]

SOUTB[2]

SOUTB[3]

SOUTB[4]

SOUTB[5]

SOUTB[6]

SOUTB[7]

SOUTB[8]

VDDO

VSSO

COUTR

OFP

IFP

VSSO

PIN 81

PIN 41

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PIN 80

10

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

8

PIN DESCRIPTION

Pin Name Type Pin

Function

No.

SCLK Input 97 The system clock (SCLK) provides timing for TUDX

internal operation. SCLK is a 19.44 MHz, nominally

50% duty cycle clock.

VCLK The test vector clock (VCLK) provides timing for TUDX

production test.

SFP Input 42 The system frame pulse (SFP) determines the frame

boundaries on the DINT[8:0] and DINB[8:0] buses

(and SINL[8:0] and SINR[8:0] buses) when OFSEB is

high. SFP determines the frame boundaries on the

SOUTT[8:0] and SOUTB[8:0] buses when OFSEB is

low. SFP must be brought high once every frame (125

µs) to mark the first C1 byte of the transport envelope

frame of the buses in question. In systolic

applications where OFSEB is high, SFP marks the C1

byte of the SINL[8:0] and SINR[8:0] buses (or the

DINT[8:0] and DINB[8:0] buses) after the

programmable systolic delay has been inserted. See

the Application Examples and Functional Timing

sections for more information. SFP is sampled on the

rising edge of SCLK.

OFSEB Input 160 The active low output frame synchronization enable

(OFSEB) signal selects the system frame alignment

marked by SFP. When OFSEB is high, SFP is

coincident with the input frame pulse (IFP). When

OFSEB is low, SFP is coincident with the output frame

pulse (OFP). In most applications, OFSEB should be

held high. The OFSEB input has an integral pull up

resistor.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

Function

No.

IFP Output 82 The input frame pulse (IFP) marks the frame

boundaries on the DINT[8:0] and DINB[8:0] buses (or

SINL[8:0] and SINR[8:0] buses). IFP pulses high for a

single SCLK period to mark the first C1 byte of the

transport envelope frame of the buses in question. In

systolic array applications, IFP marks the frame

boundaries of the SINL[8:0] and SINR[8:0] buses (or

the DINT[8:0] and DINB[8:0] buses) after the

programmable systolic delay has been inserted. See

the Application Examples and Functional Timing

sections for more information. IFP is updated on the

rising edge of SCLK.

OFP Output 83 The output frame pulse (OFP) marks the frame

boundaries on the SOUTT[8:0] and SOUTB[8:0]

buses. OFP pulses high for a single SCLK period to

mark the first C1 byte of the transport envelope frame.

OFP is updated on the rising edge of SCLK.

DINT[0]

DINT[1]

DINT[2]

DINT[3]

Input 3

The top data input bus (DINT[8:0]) carries

4

5

6

SONET/SDH frame data in byte serial format. The

DINT[8] bit is a parity bit which is not passed through

the TUDX. The TUDX may be configured to check for

even or odd input bus parity and generate interrupts

when parity errors occur. The DINT[8:0] bus is

DINT[4]

DINT[5]

7

sampled on the rising edge of SCLK.

8

DINT[6]

DINT[7]

DINT[8]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

10

11

12

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

No.

DINB[0]

DINB[1]

DINB[2]

DINB[3]

DINB[4]

DINB[5]

DINB[6]

DINB[7]

DINB[8]

DOUTL[0]

DOUTL[1]

DOUTL[2]

DOUTL[3]

DOUTL[4]

DOUTL[5]

DOUTL[6]

Input 19

22

23

24

25

26

27

28

29

Output/

OD

Output

128

131

133

137

139

145

147

Function

The bottom data input bus (DINB[8:0]) carries

SONET/SDH frame data in byte serial format. The

DINT[8] bit is a parity bit which is not passed through

the TUDX. The TUDX may be configured to check for

even or odd input bus parity and generate interrupts

when parity errors occur. The DINB[8:0] bus is

sampled on the rising edge of SCLK.

The left data output bus (DOUTL[8:0]) carries

SONET/SDH frame data in byte serial format. The

DOUTL[8] bit is a parity bit which is generated by the

TUDX. The TUDX may be configured to generate

even or odd parity. The DOUTL[8:0] bus is updated on

the rising edge of SCLK. DOUTL may be configured

as a normal output or as an open drain output, the

latter mode being useful for constructing larger

switching arrays.

DOUTL[7]

DOUTL[8]

DOUTR[0]

DOUTR[1]

DOUTR[2]

DOUTR[3]

DOUTR[4]

DOUTR[5]

DOUTR[6]

DOUTR[7]

DOUTR[8]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

Output/

OD

Output

151

153

73

71

67

65

61

57

53

51

48

The right data output bus (DOUTR[8:0]) carries

SONET/SDH frame data in byte serial format. The

DOUTR[8] bit is a parity bit which is generated by the

TUDX. The TUDX may be configured to generate

even or odd parity. The DOUTR[8:0] bus is updated

on the rising edge of SCLK. DOUTR may be

configured as a normal output or as an open drain

output, the latter mode being useful for constructing

larger switching arrays.

13

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

No.

AOUTL[0]

AOUTL[1]

AOUTL[2]

AOUTL[3]

AOUTL[4]

AOUTL[5]

AOUTL[6]

AOUTL[7]

AOUTL[8]

AOUTR[0]

AOUTR[1]

AOUTR[2]

AOUTR[3]

AOUTR[4]

AOUTR[5]

AOUTR[6]

AOUTR[7]

AOUTR[8]

Output/

OD

Output

Output/

OD

Output

127

130

132

136

138

144

146

150

152

74

72

68

66

62

58

54

52

49

Function

The left auxiliary data output bus (AOUTL[8:0]) carries

SONET/SDH frame data in byte serial format. The

AOUTL[8] bit is a parity bit which is generated by the

TUDX. The TUDX may be configured to generate

even or odd parity. The AOUTL[8:0] bus is updated on

the rising edge of SCLK. AOUTL may be configured

as a normal output or as an open drain output, the

latter mode being useful for constructing larger

switching arrays. The AOUTL output bus carries the

same information as the DOUTL bus and the two

buses may be parallel connected on a bit by bit basis

when additional output drive is required. The AOUTL

bus is held in a high impedance mode to save power

when not enabled.

The right auxiliary data output bus (AOUTR[8:0])

carries SONET/SDH frame data in byte serial format.

The AOUTR[8] bit is a parity bit which is generated by

the TUDX. The TUDX may be configured to generate

even or odd parity. The AOUTR[8:0] bus is updated

on the rising edge of SCLK. AOUTR may be

configured as a normal output or as an open drain

output, the latter mode being useful for constructing

larger switching arrays. The AOUTR output bus

carries the same information as the DOUTR bus and

the two buses may be parallel connected on a bit by

bit basis when additional output drive is required. The

AOUTR bus is held in a high impedance mode to save

power when not enabled.

AOBEB Input 2 The active low auxiliary output bus enable (AOBEB)

signal enables the AOUTL and AOUTR when low.

When AOBEB is high, the AOUTL and AOUTR output

buses are held in a high impedance mode to save

power. The AOBEB input has an integral pull up

resistor.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

No.

SINL[0]

SINL[1]

SINL[2]

SINL[3]

SINL[4]

SINL[5]

SINL[6]

SINL[7]

SINL[8]

SINR[0]

SINR[1]

SINR[2]

SINR[3]

SINR[4]

SINR[5]

SINR[6]

SINR[7]

Input 121

122

123

124

125

156

157

158

159

Input 80

79

78

77

76

46

45

44

Function

The left systolic input bus (SINL[8:0]) carries

SONET/SDH frame data in byte serial format. The

SINL[8] bit is a parity bit which is not passed through

the TUDX. The TUDX may be configured to check for

even or odd input bus parity and generate interrupts

when parity errors occur. The SINL[8:0] bus is

sampled on the rising edge of SCLK. Data on the

SINL[8:0] bus is re-timed and may be routed to the

DOUTL[8:0] in place of information switched from the

DINT[8:0] bus, and is provided for constructing larger

switching arrays using systolic data flow.

The right systolic input bus (SINR[8:0]) carries

SONET/SDH frame data in byte serial format. The

SINR[8] bit is a parity bit which is not passed through

the TUDX. The TUDX may be configured to check for

even or odd input bus parity and generate interrupts

when parity errors occur. The SINR[8:0] bus is

sampled on the rising edge of SCLK. Data on the

SINR[8:0] bus is re-timed and may be routed to the

DOUTR[8:0] in place of information switched from the

DINB[8:0] bus, and is provided for constructing larger

switching arrays using systolic data flow.

SINR[8]

SOUTT[0]

SOUTT[1]

SOUTT[2]

SOUTT[3]

SOUTT[4]

SOUTT[5]

SOUTT[6]

SOUTT[7]

SOUTT[8]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

43

Output 117

116

115

114

113

112

111

110

109

The left systolic output bus (SOUTT[8:0]) carries

SONET/SDH frame data in byte serial format. The

SOUTT[8] bit is a parity bit which is generated by the

TUDX. The TUDX may be configured to generate

even or odd parity. The SOUTT[8:0] bus is updated on

the rising edge of SCLK. The SOUTT[8:0] bus carries

a re-timed copy of the information sampled on the

DINT[8:0] bus and is provided for constructing larger

switching arrays using systolic data flow. The SOUTT

bus can be disabled to save power when not used.

15

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

Function

No.

SOUTB[0]

SOUTB[1]

SOUTB[2]

SOUTB[3]

Output 95

94

93

92

The right systolic output bus (SOUTB[8:0]) carries

SONET/SDH frame data in byte serial format. The

SOUTB[8] bit is a parity bit which is generated by the

TUDX. The TUDX may be configured to generate

even or odd parity. The SOUTB[8:0] bus is updated

on the rising edge of SCLK. The SOUTB[8:0] bus

SOUTB[4]

SOUTB[5]

91

90

carries a re-timed copy of the information sampled on

the DINB[8:0] bus and is provided for constructing

larger switching arrays using systolic data flow. The

SOUTB[6]

SOUTB[7]

SOUTB[8]

89

88

87

SOUTB bus can be disabled to save power when not

used.

SOBEB Input 30 The active low systolic output bus enable (SOBEB)

signal enables the SOUTT and SOUTB output buses

when low. When SOBEB is high, the SOUTT and

SOUTB output buses are held in a high impedance

mode to save power. The SOBEB input has an

integral pull up resistor.

COUTL Output 120 The left control output signal (COUTL) is a software

programmable control stream (on a per timeslot basis)

that can be used for controlling external hardware

when constructing larger switching arrays. After reset,

COUTL defaults to always high until otherwise

programmed. COUTL is updated on the rising edge of

SCLK.

COUTR Output 84 The right control output bus (COUTR) is a software

programmable control stream (on a per timeslot basis)

that can be used for controlling external hardware

when constructing larger switching arrays. After reset,

COUTR defaults to always high until otherwise

programmed. COUTR is updated on the rising edge

of SCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

Function

No.

ODEB Input 1 The active low open drain enable (ODEB) signal

configures the DOUTL and DOUTR output buses as

open drain outputs when low. When ODEB is high,

the DOUTL and DOUTR output buses are configured

as normal outputs. The ODEB input has an integral

pull up resistor.

PAGE Input 41 The page select (PAGE) signal selects the connection

memory pages that are used to control connections

within the TUDX. When PAGE is low, connection

memory page 0 of each switching element is used.

When PAGE is high, connection memory page 1 of

each switching element is used. The PAGE input is

sampled on the rising edge of SCLK. Internally, a

change in the active connection memory page is held

off until the next switching frame boundary (a delay of

up to approximately 14 us). While such a page swap

is pending, accesses to the connection memory by

the microprocessor should be avoided. Such a

pending page swap results in a connection memory

busy indication which can be polled. The PAGE input

has an integral pull down resistor.

MBEB Input 105 The active low Motorola bus enable (MBEB) signal

configures the TUDX for Motorola bus mode where

the RDB/E signal functions as E, and the WRB/RWB

signal functions as RWB. When MBEB is high, the

TUDX is configured for Intel bus mode where the

RDB/E signal functions as RDB. The MBEB input has

an integral pull up resistor.

CS1B Input 17 The active low chip select #1 (CS1B) signal is low

during TUDX register accesses.

If CS1B and CS2B are not required (i.e., registers

accesses are controlled using the RDB and WRB

signals only), CS1B and CS2B must be connected to

an inverted version of the RSTB input.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

17

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

Function

No.

CS2B Input 18 The active low chip select #2 (CS2B) signal is low

during TUDX register accesses.

If CS1B and CS2B are not required (i.e., registers

accesses are controlled using the RDB and WRB

signals only), CS1B and CS2B must be connected to

an inverted version of the RSTB input.

RDB Input 102 The active low read enable (RDB) signal is low during

TUDX register read accesses while in Intel bus mode

(MBEB = 1). The TUDX drives the D[7:0] bus with the

contents of the addressed register while RDB, CS1B,

and CS2B are low.

E Input 102 The active high external access (E) signal is high

during TUDX register access while in Motorola bus

mode (MBEB = 0).

WRB Input 101 The active low write strobe (WRB) signal is low during

a TUDX register write accesses while in In tel bus

mode (MBEB = 1). The D[7:0] bus contents are

clocked into the addressed register on the rising WRB

edge while CS1B and CS2B are low.

RWB The read/write select (RWB) signal selects between

TUDX register read and write accesses while in

Motorola bus mode (MBEB = 0). The TUDX drives the

D[7:0] bus with the contents of the addressed register

while CS1B and CS2B are low and RWB and E are

high. The D[7:0] bus contents are clocked into the

addressed register on the falling E edge while CS1B

and CS2B and RWB are low.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

18

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

No.

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

A[0]

A[1]

A[2]

A[3]

A[4]/TRS

I/O 31

32

33

34

37

38

39

40

Input 12

13

14

15

16

Function

The bidirectional data bus (D[7:0]) is used during

TUDX register read and write accesses.

The address bus (A[4:0]) selects specific registers

during TUDX register accesses.

The test register select (TRS) signal discriminates

between normal and test mode register accesses.

TRS is high during test mode register accesses, and

is low during normal mode register accesses. The

TRS input has an integral pull down resistor.

RSTB Input 104 The active low reset (RSTB) signal provides an

asynchronous TUDX reset. RSTB is a Schmitt

triggered input with an integral pull up resistor.

ALE Input 103 The address latch enable (ALE) is active high and

latches the address bus (A[4:0]) and TRS when low.

When ALE is high, the internal address latches are

transparent. It allows the TUDX to interface to a

multiplexed address/data bus. The ALE input has an

integral pull up resistor.

INTB OD

Output

106 The active low interrupt (INTB) signal goes low when

a TUDX interrupt source is active. INTB returns high

when the interrupt is acknowledged via an appropriate

register access. The INTB output is an open drain

output.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

19

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

No.

VDDI1

VDDI2

VDDI3

VDDI4

VSSI1

VSSI2

VSSI3

VSSI4

VDDO1

VDDO2

VDDO3

VDDO4

VDDO5

Power 20

60

100

140

Ground 21

59

99

141

Power 36

47

55

63

69

Function

The core power (VDDI) pins should be connected to a

well decoupled +5 V DC in common with VDDO.

The core ground (VSSI) pins should be connected to

GND in common with VSSO.

The pad ring power (VDDO) pins should be connected

to a well decoupled +5 V DC in common with VDDI.

VDDO6

VDDO7

VDDO8

VDDO9

VDDO10

VDDO11

VDDO12

VDDO13

VDDO14

86

96

108

119

126

135

143

148

154

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

20

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Pin Name Type Pin

No.

VSSO1

VSSO2

VSSO3

VSSO4

VSSO5

VSSO6

VSSO7

VSSO8

VSSO9

VSSO10

VSSO11

VSSO12

VSSO13

Ground 35

50

56

64

70

75

81

85

98

107

118

129

134

Function

The pad ring ground (VSSO) pins should be

connected to GND in common with VSSI.

VSSO14

VSSO15

VSSO16

142

149

155

Notes on Pin Description:

1. All TUDX inputs and bidirectionals present minimum capacitive loading and

operate at TTL logic levels.

2. All TUDX digital outputs and bidirectionals have 2 mA drive capability, except

the INTB, SOUTT[8:0], SOUTB[8:0] outputs and D[7:0] bidirectionals, which

have 4 mA drive capability, and the DOUTL[8:0], DOUTR[8:0], AOUTL[8:0]

and AOUTR[8:0] outputs, which have 8 mA drive capability.

3. The VSSO and VSSI ground pins are not internally connected together.

Failure to connect these pins externally may cause malfunction or damage

the TUDX.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

21

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

4. The VDDO and VDDI power pins are not internally connected together.

Failure to connect these pins externally may cause malfunction or damage

the TUDX.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

22

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

9

FUNCTIONAL DESCRIPTION

9.1 Input Bus Formatter

The input bus formatter captures data sampled on the DINT and DINB buses

and distributes this data to the two switching elements within the TUDX. The

input bus formatter also re-times this captured data, delaying it 5 clock cycles

and outputs copies of the information from the DINT and DINB buses on the

SOUTT and SOUTB buses, respectively. When systolic interconnect is not used,

the SOUTT and SOUTB buses can be held in a high impedance mode to save

power by strapping the SOBEB input appropriately.

For systolic array applications, a programmable delay element provides

additional delay of 5, 10, or 15 clock cycles in the DINT and DINB data paths or

in the SOUTT and SOUTB data paths. For more information on the systolic array

application, see the Application Examples section.

The input bus formatter also provides timing signals for the other blocks within

the TUDX. The system clock, SCLK, is buffered and distributed to the switching

elements and the output bus formatter. Frame pulses for the incoming and

outgoing data streams, IFP and OFP, are generated with alignment dictated by

the system frame pulse input, SFP. These frame pulses are buffered and

distributed to the switching elements. One can select whether the SFP input will

generate a coincident IFP or OFP pulse using the OFSEB configuration input.

This option is useful when constructing larger switches using arrays of TUDX

devices. The input bus formatter generates the IFP and OFP outputs. Proper

generation of IFP and OFP requires that the input bus formatter be initialized

once per SONET/SDH frame (125 µs) by a pulse on the SFP input. In the

absence of a periodic SFP input, outputs IFP and OFP are not generated

correctly.

9.2 Output Bus Formatter

The output bus formatter selects the data to be output on the DOUTL and

DOUTR buses. This data is gathered from the switching elements or the SINL

and SINR buses, on a per timeslot basis, as programmed within the switching

elements. The output bus formatter also drives the COUTL and COUTR outputs

with control signals that are programmable, on a per timeslot basis, via the

switching elements. The delay from the SINL or SINR buses to the DOUTL or

DOUTR buses is 5 clock cycles. The delay from the DINT or DINB buses to the

DOUTL or DOUTR buses for a straight through connection (from each input

timeslot to its equivalent output timeslot) is 275 clock cycles (corresponding to

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

23

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

one SONET STS-3 or SDH STM-1 row of 270 bytes plus 5 clock cycles of retiming delay).

For systolic array applications, a programmable delay element provides an

additional delay of 5, 10 or 15 clock cycles in the SINL and SINR data paths or in

the DOUTL and DOUTR data paths.

The output bus formatter can be configured to drive the DOUTL and DOUTR

buses rail to rail or drive the DOUTL and DOUTR buses as open drain outputs.

The open drain output option is selected by strapping the ODEB input

appropriately. A second set of output buses, the AOUTL and AOUTR buses,

carry the same data as the DOUTL and DOUTR buses, respectively. These pairs

of buses can be strapped together on a bit by bit basis in order to provide higher

drive capability. This is particularly useful in implementing wired-OR type output

buses. When not required, the AOUTL and AOUTR buses can be held in a high

impedance mode to save power by strapping the AOBEB input appropriately.

9.3 Switching Element

Each switching element implements two single stage, non-blocking time switches

that each process an STS-3 or STM-1 rate stream. The channelization of each

time switch corresponds to 9 byte columns within the SONET/SDH frame. Thus

the basic switching granularity is 576 kbit/s (9 x 64 kbit/s). The frame rate of

each time switch corresponds to 1/9th of the SONET/SDH frame rate. The frame

rate is thus 13.89 us (125 us ÷ 9). The frame processed by each time switch

corresponds to 270 byte rows within the SONET/SDH frame. Two time switches

that connect to a common output bus are grouped within each switching element

such that they can share a common connection memory.

Cross-connection of the various size s of VTs (or TUs) is accomplished by setting

up group connections. A VT1.5, for example, occupies three 9 byte columns

within the SONET/SDH frame and thus a VT1.5 cross-connection can be set up

by making three connections of 576 kbit/s each. A TU12, in contrast, occupies

four 9 byte columns and thus a TU12 cross-connection can be set up by making

four connections of 576 kbit/s each. The time switches are double buffered so as

to exhibit constant frame delay which preserves byte sequence integrity during

group connections, regardless of the size and routing of the group connection.

Note that the switching elements assume that the tributaries to be crossconnected occupy fixed 9 byte columns within the SONET STS-3 or SDH STM-1

frame. In order to cross-connect VT1.5, VT2, VT3, or VT6 tributaries within an

STS-3 stream or TU11, TU12, TU2, or TU3 tributaries within an STM-1 stream,

the STS-3 or STM-1 stream must be preprocessed with the PM5361 TUPP or an

equivalent circuit. Such processing must ensure that all STS-1 or AU-3 or AU-4

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

24

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

pointer adjustments are absorbed into VT or TU pointer adjustments such that

the resulting STS-3 or STM-1 frame has its VTs or TUs occupying fixed,

appropriately phase aligned positions with respect to the overall transport

envelope frame, ready for switching.

The TUDX consists of two switching elements, each containing two time

switches, which results in a 2 by 2 array of time switches. Data from each of the

DINT and DINB buses is distributed and written into the two time switches in the

corresponding row. Data is collected for output on the DOUTL and DOUTR

buses from each of the two time switches in the corresponding column or

switching element, or from the associated SINL or SINR bus. The source of data

is programmable on a per timeslot basis within the switching elements. As only

one time switch in a column can source data during a given timeslot, time switch

outputs are powered down, rather than outputting data, 50% of the time.

In addition to implementing cross-connections, the switching elements are also

capable of inserting programmable idle code into outgoing timeslots. This idle

code is arbitrarily programmable on a per timeslot basis and thus through proper

programming, a fixed, arbitrary idle code can be inserted into any outgoing VT or

TU. This capability can be used to insert tributary path AIS or to insert fixed

codes used for system diagnostic purposes.

The switching elements are implemented in a classical manner with each having

a pair of data memories, a common connection memory, timing generator, output

multiplexer, and common bus interface.

9.3.1 Data Memories

The data memories each consist of two 270 x 8 RAMs implementing a double

buffered switch core. During each switching frame, data is written into sequential

locations in one page of memory, and read from the other page of memory

based on a list of addresses provided by the connection memory. At each

switching frame boundary (every 270 bytes) the function of the two memory

pages is reversed. The data memory is 8 bits wide to allow byte wide data to be

routed through the switching element. Two data memories are required, one for

each of the input buses connected to the switching element.

9.3.2 Connection Memory

The connection memory consists of a double buffered 270 x 13 RAM. During

each switching frame, information is sequentially read from the active memory

page and used to generate the read addresses for the data memory and control

the output multiplexer. Either connection memory can be written to or read from

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

25

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

via the common bus interface and thus its contents are programmable. In this

manner, the switching action of the data memory and output multiplexer are

programmable on a per timeslot basis. Normally one would only write to the

inactive page, performing all the programming required to implement ones

desired connections, and then trigger a page swap at a frame boundary. Use of

a double buffered connection memory and active page swapping allows tributary

connections (which are implemented as group connections of 576 kbit/s

timeslots) to be coherently made or broken.

9.3.3 Timing Generator

The timing generator consists of a frame counter and clock dividers. Buffered

versions of the various derived clocks are distributed to other blocks within the

switching element as are several phase delayed versions of the frame count, as

required in such a pipelined processing structure.

9.3.4 Output Multiplexer

The output multiplexer consists of logic that selects the source of information to

be output from the switching element. Such selection is controlled on a per

timeslot basis by the connection memory and is thus programmable. Output data

can be routed from the data memory, from the lower order bits of the connection

memory, or a null value can be inserted when no connection is being made. The

null value is chosen on the fly to minimize power dissipation. The ability to

source data from the connection memory itself is how programmable idle code

insertion is provided. During those timeslots when programmable idle code is

being inserted or no connection is being made through the switching element,

the reading of data from the data memory is suppressed in order to save power.

In addition to its selection function, the output multiplexer also re-times control

signals sourced by the connection memory that are used to control the output

bus formatter of the complete device.

9.3.5 Common Bus Interface

The common bus interface allows microprocessor access to the switching

element connection memory. Access is indirect, via registers located in the

common bus interface. Each connection memory access takes up to eight SCLK

cycles to complete as circuitry waits for opportunities when the connection

memory locations in question are not being accessed during the normal course

of switching element operation.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

26

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

9.4 Microprocessor Interface

The microprocessor interface block provides normal and test mode registers, and

the logic required to connect to the microprocessor interface. The normal mode

registers are required for normal operation, and test mode registers are used to

enhance the testability of the TUDX. The register set is accessed as follows:

Table 1 - Register Memory Map

Address Register

00H TUDX Master Configuration

01H TUDX Connection Memory Control

02H TUDX Clock Monitor

03H TUDX Master Reset/Revision ID

04H TUDX Parity Configuration

05H TUDX Parity Error Interrupt Enable

06H TUDX Parity Error Interrupt Status

07H TUDX Systolic Delay Control

08H Left Switch Element Connection Address High

09H Left Switch Element Connection Address Low

0AH Left Switch Element Connection Data High

0BH Left Switch Element Connection Data Low

0CH Right Switch Element Connection Address High

0DH Right Switch Element Connection Address Low

0EH Right Switch Element Connection Data High

0FH Right Switch Element Connection Data Low

10H TUDX Master Test

11H-1FH Reserved for Test

For all register accesses, CS1B and CS2B must be low.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

27

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

10

NORMAL MODE REGISTER DESCRIPTION

Normal mode registers are used to configure and monitor the operation of the

TUDX. Nor mal mode registers (as opposed to test mode registers) are selected

when TRS (A[4]) is low.

Notes on Normal Mode Register Bits:

1. Writing values into unused register bits has no effect. However, to ensure

software compatibility with future, feature-enhanced versions of the product,

unused register bits must be written with logic 0. Reading back unused bits

can produce either a logic 1 or a logic 0; hence unused register bits should be

masked off by software when read.

2. All configuration bits that can be written into can also be read back. This

allows the processor controlling the TUDX to determine the programming

state of the block.

3. Writeable normal mode register bits are cleared to logic 0 upon reset unless

otherwise noted.

4. Writing into read-only normal mode register bit locations does not affect

TUDX operation unless otherwise noted.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

28

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 00H: Master Configuration

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 R/W SELEN 0

Bit 2 R/W SEREN 0

Bit 1 R/W COUTLEN 0

Bit 0 R/W COUTREN 0

This register is used to enable the switching elements and the generation of the

programmable control output signals.

COUTLEN:

The COUTLEN bit enables the generation of the COUTL signal under control

of the left switching element; the switching element that routes between the

DINT and DOUTL buses, or DINB and DOUTL buses, respectively. After

reset, the COUTL signal is forced high, until the COUTLEN bit is set high.

COUTREN:

The COUTREN bit ernables the generation of the COUTR signal under

control of the right switching element; the switching element that routes

between the DINT and DOUTR buses, or DINB and DOUTR buses,

respectively. After reset, the COUTR signal is forced high, until the

COUTREN bit is set high.

SELEN:

The SELEN bit enables operation of the left switching element (the switching

element that routes between the DINT and DOUTL buses, or DINB and

DOUTL buses, respectively). After reset, the left switching element is held

reset to save power, until the SELEN bit is set high.

SEREN:

The SEREN bit enables operation of the right switching element (the

switching element that routes between the DINT and DOUTR buses, or DINB

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

29

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

and DOUTR buses, respectively). After reset, the right switching element is

held reset to save power, until the SEREN bit is set high.

Note that a switching element cannot be programmed until it is enabled.

While a switching element is disabled, the output bus formatter will not select

it as a source of data, thus passing through data from the SINL or SINR bus,

as appropriate.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

30

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 01H: Connection Memory Control

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 Unused X

Bit 2 R APAGE X

Bit 1 R EPAGE X

Bit 0 R/W IPAGE 0

This register is used to control and monitor the selection of the active connection

memory page.

IPAGE:

The IPAGE bit is used to internally select the active connection memory page.

When IPAGE is set high, page 1 is selected. When IPAGE is cleared low,

page 0 is selected, provided that the external PAGE input is also low.

EPAGE:

The EPAGE bit can be read to determine the state of the external PAGE

input.

APAGE:

The APAGE bit can be read to determine the active connection memory

page. APAGE is the logical OR of the IPAGE bit and the PAGE input (which

can be read via the EPAGE bit).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

31

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 02H: Clock Monitor

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 R DINBA X

Bit 2 R DINTA X

Bit 1 R SFPA X

Bit 0 R SCLKA X

This register is used to monitor the integrity of TUDX timing input signals.

SCLKA:

The SCLKA bit indicates that SCLK is active when high. SCLKA is set high

by a low to high transition on SCLK and is set low immediately following a

read of this register. This bit is intended to be polled to detect a system failure

that freezes the SCLK signal.

SFPA:

The SFPA bit indicates that SFP is active when high. SFPA is set high by a

SCLK sampled low to high transition on SFP and is set low immediately

following a read of this register. This bit is intended to be polled to detect a

system failure that freezes the SFP signal.

DINTA:

The DINTA bit indicates that DINT bus is active when high. DINTA is set high

when all bits of the DINT[8:0] bus have changed low to high after sampled by

SCLK and is set low immediately following a read of this register. This bit is

intended to be polled to detect a system failure that freezes any of the

DINT[8:0] bits.

DINBA:

The DINBA bit indicates that DINB bus is active when high. DINBA is set

high when all bits of the DINB[8:0] bus have changed low to high after

sampled by SCLK and is set low immediately following a read of this register.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

32

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

This bit is intended to be polled to detect a system failure that freezes any of

the DINB[8:0] bits.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

33

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 03H: Master Reset/Revision ID

Bit Type Function Default

Bit 7 R/W RESET 0

Bit 6 R ID[6] 0

Bit 5 R ID[5] 0

Bit 4 R ID[4] 0

Bit 3 R ID[3] 0

Bit 2 R ID[2] 0

Bit 1 R ID[1] 0

Bit 0 R ID[0] 0

This register allows the revision of the TUDX to be read by software permitting

graceful migration to support for newer, feature enhanced versions of the TUDX,

should revision of the TUDX occur. This register also allows the TUDX to be

reset.

ID[6:0]:

The ID bits can be read to provide a binary TUDX revision number.

RESET:

The RESET bit allows the TUDX to be reset under software control. If the

RESET bit is a logic 1, the entire TUDX is held in reset. This bit is not selfclearing; therefore, a logic 0 must be written to bring the TUDX out of reset.

Holding the TUDX in a reset state effectively puts it into a low powe r, stand-by

mode. A hardware reset clears the RESET bit, thus de-asserting the

software reset.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

34

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 04H: Parity Configuration

Bit Type Function Default

Bit 7 R/W TODDO 0

Bit 6 R/W BODDO 0

Bit 5 R/W LODDO 0

Bit 4 R/W RODDO 0

Bit 3 R/W TODDI 0

Bit 2 R/W BODDI 0

Bit 1 R/W LODDI 0

Bit 0 R/W RODDI 0

This register is used to configure the parity polarity expected on input buses and

generated on output buses.

RODDI, LODDI, BODDI, TODDI:

These bits configure the parity expected on input buses. When high, odd

parity is expected. When low, even parity is expected. The RODDI bit

configures the SINR bus, the LODDI bit configures the SINL bus, the BODDI

bit configures the DINB bus, and the TODDI bit configures the DINT bus.

RODDO, LO DDO, BODDO, TODDO:

These bits configure the parity generated on output buses. When high, odd

parity is generated. When low, even parity is generated. The RODDO bit

configures the DOUTR bus, the LODDO bit configures the DOUTL bus, the

BODDO bit configures the SOUTB bus, and the TODDO bit configures the

SOUTT bus. Note that bad parity can be introduced for diagnostic purposes

by manipulating these bits.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

35

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 05H: Parity Error Interrupt Enable

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 R/W TPERE 0

Bit 2 R/W BPERE 0

Bit 1 R/W LPERE 0

Bit 0 R/W RPERE 0

This register is used to enable parity errors to generate interrupts.

RPERE, LPERE, BPERE, TPERE:

These bits enable parity errors on their respective input buses to generate

interrupts. When high, parity error interrupt generation is enabled. When low,

parity error interrupt generation is disabled, however, the parity error

indications may still be polled. The RPERE bit configures the SINR bus, the

LPERE bit configures the SINL bus, the BPERE bit configures the DINB bus,

and the TPERE bit configures the DINT bus.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

36

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 06H: Parity Error Interrupt Status

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 R TPERI X

Bit 2 R BPERI X

Bit 1 R LPERI X

Bit 0 R RPERI X

This register is used to identify the source of a parity error interrupt and

acknowledge such an interrupt.

RPERI, LPERI, BPERI, TPERI:

These bits are set high when a parity error on their respective input buses is

detected. If enabled, an interrupt will also occur. These bits are cleared low

immediately following a read of this register causing any active interrupt to be

de-asserted. These bits are latching and will remain high following the

detection of a single parity error until this register is read. These bits retain

their event capture functionality when interrupt generation is disabled and

may be polled to detect parity errors. The RPERI bit monitors the SINR bus,

the LPERI bit monitors the SINL bus, the BPERI bit monitors the DINB bus,

and the TPERI bit monitors the DINT bus.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

37

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 07H: Systolic Delay Control

Bit Type Function Default

Bit 7 Unused X

Bit 6 Unused X

Bit 5 R/W SOUTEN 0

Bit 4 R/W SINEN 0

Bit 3 R/W DOUTEN 0

Bit 2 R/W DINEN 0

Bit 1 R/W DS1 0

Bit 0 R/W DS0 0

This register is used to control the delay inserted into the SOUT, SIN, DOUT, and

DIN data paths. This feature is used in systolic array applications to match data

skew at the array boundaries for up to a 4 X 4 array without using external

components.

SOUTEN, SINEN, DOUTEN, DINEN:

These bits control the programmable delay elements, one of which is shared

between DIN and SOUT, the other between SIN and DOUT. The delay is

inserted when these bits are set high. It is not appropriate to set both DINEN

and SOUTEN high simultaneously, nor SINEN and DOUTEN. The delay

value for both delay elements is controlled by the DS1 and DS0 bits.

DS1, DS0:

The DS1 and DS0 bits select the delay value for both delay elements as

described in the following table:

Table 2 - Systolic Delay Control

DS1 DS0 Delay V alue

0 0 0 Not appropriate if any enable bits are logic 1.

01 5

10 10

11 15

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

38

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

When constructing a 4 X 4 systolic array, program the individual TUDX devices

with the following binary codes:

Table 3 - Systolic Array Delay Control

12 3 4

1

2

3

4

000000 010001 010010 110011

000101 000000 000000 100010

000110 000000 000000 100001

001111 001010 001001 000000

The systolic delays are applied to the TUDXs at the array periphery. In the first

(or top) row, the SINL[8:0] and SINR[8:0] buses are delayed by 0, 5, 10, and 15

additional clock periods (moving from left to right across the first row). In the

fourth (or bottom row, the DOUTL[8:0] and DOUTR[8:0] buses are delayed by 15,

10, 5, and 0 clock periods (again moving from left to right). In the first (or

leftmost) column, the DINT[8:0] and DINB[8:0] buses are delayed by 0, 5, 10,

and 15 clock periods (moving from the top to the bottom of the first column). In

the fourth (or rightmost) column, the SOUTT[8:0] and SOUTB[8:0] buses are

delayed by 15, 10, 5, and 0 clock periods (again moving from top to bottom). The

above array produces a 35 SCLK cycle delay between the input and output

busses.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

39

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 08H,0CH: Connection Address High

Bit Type Function Default

Bit 7 R/W RWB X

Bit 6 Unused X

Bit 5 Unused X

Bit 4 Unused X

Bit 3 Unused X

Bit 2 Unused X

Bit 1 R/W CMP X

Bit 0 R/W CA8 X

This register is used to trigger accesses to switching element connection

memory and specify the memory location to be accessed.

RWB:

The RWB bit selects the type of connection memory access. The completion

of a write access to this register will trigger a read of a switching element

connection memory if RWB is high. If RWB is low, the completion of a write

access to this register will trigger a write to a switching element connection

memory. The data to be written or data read is passed through the

Connection Data Low and Connection Data High registers. The connection

memory address and page to be accessed is determined by the Connection

Address Low and Connection Address High registers. A connection memory

access requires several SCLK cycles; completion of an access is indicated by

the BUSY bit in the Connection Data High register. The instantiation of the

Connection Address and Data registers utilized selects the switching element

to be programmed. Registers 08H-0BH control the left switching element,

and registers 0CH-0FH control the right switching element.

CMP:

The CMP bit, selects the connection memory page to be accessed. Selection

of which connection memory page is active is done using the PAGE input or

the Connection Memory Control register. A logic 1 on this bit directs the read

or write operation to the active page memory page. A logic 0 on this bit

directs the read or write operation to the inactive memory page. Accesses to

the active CM memory page are likely to be much longer than accesses to

the inactive memory page. This is because of the continual read accesses by

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

40

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

the internal timeslot counter to the active memory page. Each CM page is

broken into two independent banks of 135 X13. This increases the micro's

access rate to active memory pages.

CA8:

The CA8 bit , together with the CA7-CA0 bits of the Connection Address Low

register selects the connection memory location to be accessed.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

41

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 09H,0DH: Connection Address Low

Bit Type Function Default

Bit 7 R/W CA7 X

Bit 6 R/W CA6 X

Bit 5 R/W CA5 X

Bit 4 R/W CA4 X

Bit 3 R/W CA3 X

Bit 2 R/W CA2 X

Bit 1 R/W CA1 X

Bit 0 R/W CA0 X

This register is used to specify the memory location in switching element

connection memory to be accessed.

CA7-CA0:

The CA7-CA0 bits , together with the CA8 bit of the Connection Address High

register select the connection memory location to be accessed. Connection

memory locations correspond to outgoing timeslots on the DOUTL or DOUTR

buses. Each timeslot carries a 9 x 64 kbit/s channel corresponding to one

column in a 270 x 9 byte STS-3 (or STM-1) frame. Connection memory

address 0 corresponds to the first column (the column that starts with the A1

byte of STS-1 #1 in an STS-3 stream) and address 269 corresponds to the

last column (the column that ends with the last SPE byte of STS-1 #3 in an

STS-3 stream). See the sections on Operation, Functional Timing, and

Application Examples.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

42

PM5371 TUDX

DATA SHEET

PMC-920525 ISSUE 6 SONET/SDH TRIBUTARY UNIT CROSS CONNECT

Register 0AH,0EH: Connection Data High

Bit Type Function Default

Bit 7 R BUSY 0

Bit 6 Unused X

Bit 5 Unused X

Bit 4 R/W COUT X

Bit 3 R/W MAKE X

Bit 2 R/W IDLE X

Bit 1 R/W TOP X

Bit 0 R/W CD8 X

This register is used to detect when accesses to switching element connection

memory are permitted and to pass data to connection memory during such

accesses.

BUSY: