Page 1

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

PM5366

TEMAP-84

HIGH DENSITY 84/63 CHANNEL VT/TU

MAPPER AND M13 MULTIPLEXER

DATASHEET

PROPRIETARY AND CONFIDENTIAL

PRELIMINARY

ISSUE 1: APRIL 2001

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

Page 2

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

CONTENTS

1 FEATURES .............................................................................................. 1

2 APPLICATIONS ..................................................................................... 13

3 REFERENCES....................................................................................... 14

4 APPLICATION EXAMPLES ................................................................... 18

5 BLOCK DIAGRAM ................................................................................. 21

5.1 TOP LEVEL BLOCK DIAGRAM .................................................. 21

5.2 DS3/E3 FRAMER ONLY BLOCK DIAGRAM............................... 22

6 DESCRIPTION ...................................................................................... 23

7 PIN DIAGRAM ....................................................................................... 27

8 PIN DESCRIPTION................................................................................ 28

9 FUNCTIONAL DESCRIPTION............................................................... 61

9.1 TRANSPARENT VIRTUAL TRIBUTARIES ................................. 61

9.2 THE TRIBUTARY INDEXING...................................................... 62

9.3 T1 PERFORMANCE MONITORING ........................................... 64

9.4 E1 PERFORMANCE MONITORING........................................... 67

9.5 T1/E1 PERFORMANCE DATA ACCUMULATION....................... 73

9.6 T1/E1 HDLC RECEIVER............................................................. 73

9.7 T1/E1 RECEIVE AND TRANSMIT DIGITAL JITTER

ATTENUATORS .......................................................................... 74

9.8 T1/E1 PSEUDO RANDOM BINARY SEQUENCE GENERATION

AND DETECTION (PRBS).......................................................... 79

9.9 DS3 FRAMER (DS3-FRMR) ....................................................... 79

9.10 DS3 BIT ORIENTED CODE DETECTION .................................. 81

PROPRIETARY AND CONFIDENTIAL i

Page 3

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

9.11 DS3/E3 HDLC RECEIVER (RDLC)............................................. 82

9.12 DS3/E3 PERFORMANCE MONITOR ACCUMULATOR (DS3/E3-

PMON) ........................................................................................ 82

9.13 DS3 TRANSMITTER (DS3-TRAN).............................................. 83

9.14 DS3/E3 HDLC TRANSMITTERS ................................................ 85

9.15 DS3 PSEUDO RANDOM PATTERN GENERATION AND

DETECTION (PRGD).................................................................. 86

9.16 M23 MULTIPLEXER (MX23)....................................................... 86

9.17 DS2 FRAMER (DS2 FRMR)........................................................ 87

9.18 M12 MULTIPLEXER (MX12)....................................................... 89

9.19 E3 FRAMER................................................................................ 90

9.20 E3 TRANSMITTER ..................................................................... 92

9.21 E3 TRAIL TRACE BUFFER......................................................... 94

9.22 TRIBUTARY PAYLOAD PROCESSOR (VTPP) .......................... 94

9.23 RECEIVE TRIBUTARY PATH OVERHEAD PROCESSOR

(RTOP)........................................................................................ 96

9.24 RECEIVE TRIBUTARY TRACE BUFFER (RTTB)....................... 98

9.25 RECEIVE TRIBUTARY BIT ASYNCHRONOUS DEMAPPER

(RTDM)........................................................................................ 99

9.26 RECEIVE TRIBUTARY BYTE SYNCHRONOUS DEMAPPER . 102

9.27 DS3 MAPPER DROP SIDE (D3MD)......................................... 103

9.28 TRANSMIT TRIBUTARY PATH OVERHEAD PROCESSOR

(TTOP) ...................................................................................... 106

9.29 TRANSMIT REMOTE ALARM PROCESSOR (TRAP).............. 107

9.30 TRANSMIT TRIBUTARY BIT ASYNCHRONOUS MAPPER

(TTMP) ...................................................................................... 108

PROPRIETARY AND CONFIDENTIAL ii

Page 4

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

9.31 TRANSMIT TRIBUTARY BYTE SYNCHRONOUS MAPPER ... 109

9.32 DS3 MAPPER ADD SIDE (D3MA) ............................................ 109

9.33 EXTRACT SCALEABLE BANDWIDTH INTERCONNECT

(EXSBI) ......................................................................................111

9.34 INSERT SCALEABLE BANDWIDTH INTERCONNECT

(INSBI)........................................................................................112

9.35 FLEXIBLE BANDWIDTH PORTS ..............................................113

9.36 JTAG TEST ACCESS PORT......................................................113

9.37 MICROPROCESSOR INTERFACE ...........................................115

10 NORMAL MODE REGISTER DESCRIPTION ..................................... 138

11 TEST FEATURES DESCRIPTION ...................................................... 139

11.1 JTAG TEST PORT .................................................................... 142

12 OPERATION ........................................................................................ 149

12.1 TRIBUTARY INDEXING ............................................................ 149

12.2 CLOCK AND FRAME SYNCHRONIZATION CONSTRAINTS .. 151

12.3 DS3 FRAME FORMAT.............................................................. 154

12.4 SERVICING INTERRUPTS....................................................... 156

12.5 USING THE PERFORMANCE MONITORING FEATURES...... 156

12.6 USING THE INTERNAL DS3 OR E3 HDLC TRANSMITTER ... 160

12.7 USING THE INTERNAL DS3 OR E3 DATA LINK RECEIVER .. 164

12.8 T1/E1 LOOPBACK MODES...................................................... 168

12.9 DS3 AND E3 LOOPBACK MODES........................................... 170

12.10 TELECOM BUS MAPPER/DEMAPPER LOOPBACK MODES. 173

12.11 SBI BUS DATA FORMATS........................................................ 174

PROPRIETARY AND CONFIDENTIAL iii

Page 5

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

12.12 JTAG SUPPORT ....................................................................... 196

13 FUNCTIONAL TIMING......................................................................... 204

13.1 DS3 LINE SIDE INTERFACE TIMING ...................................... 204

13.2 DS3 AND E3 SYSTEM SIDE INTERFACE TIMING.................. 208

13.3 TELECOM DROP BUS INTERFACE TIMING........................... 212

13.4 TELECOM ADD BUS INTERFACE TIMING.............................. 215

13.5 SONET/SDH SERIAL ALARM PORT TIMING .......................... 218

13.6 SBI DROP BUS INTERFACE TIMING ...................................... 219

13.7 SBI ADD BUS INTERFACE TIMING ......................................... 220

14 ABSOLUTE MAXIMUM RATINGS....................................................... 222

15 D.C. CHARACTERISTICS ................................................................... 223

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS..... 226

17 TEMAP-84 TIMING CHARACTERISTICS ........................................... 230

18 ORDERING AND THERMAL INFORMATION...................................... 252

19 MECHANICAL INFORMATION ............................................................ 253

PROPRIETARY AND CONFIDENTIAL iv

Page 6

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

LIST OF FIGURES

FIGURE 1 - HIGH-DENSITY LINE CARD APPLICATION............................... 18

FIGURE 2 - OC-12 MULTI-SERVICE SWITCH APPLICATION ...................... 19

FIGURE 3 - FRACTIONAL DS3 APPLICATION.............................................. 19

FIGURE 4 - TEMAP-84 BLOCK DIAGRAM .................................................... 21

FIGURE 5 - DS3/E3 FRAMER ONLY MODE BLOCK DIAGRAM ................... 22

FIGURE 6 - PIN DIAGRAM ............................................................................. 27

FIGURE 7 - CRC MULTIFRAME ALIGNMENT ALGORITHM ......................... 70

FIGURE 8 - JITTER TOLERANCE T1 MODES............................................... 75

FIGURE 9 - JITTER TOLERANCE E1 MODES .............................................. 76

FIGURE 10- JITTER TRANSFER T1 MODES ................................................. 77

FIGURE 11 -JITTER TRANSFER E1 MODES.................................................. 78

FIGURE 12- DS3 FRAME STRUCTURE ....................................................... 154

FIGURE 13- FER COUNT VS. BER (E1 MODE) ........................................... 158

FIGURE 14- CRCE COUNT VS. BER (E1 MODE) ........................................ 159

FIGURE 15- FER COUNT VS. BER (T1 ESF MODE).................................... 159

FIGURE 16- CRCE COUNT VS. BER (T1 ESF MODE)................................. 160

FIGURE 17- CRCE COUNT VS. BER (T1 SF MODE)................................... 160

FIGURE 18- TYPICAL DATA FRAME............................................................. 167

FIGURE 19- EXAMPLE MULTI-PACKET OPERATIONAL SEQUENCE........ 167

FIGURE 20- T1/E1 LINE LOOPBACK............................................................ 169

FIGURE 21- T1/E1 DIAGNOSTIC DIGITAL LOOPBACK............................... 170

FIGURE 22- DS3 DIAGNOSTIC LOOPBACK DIAGRAM .............................. 171

PROPRIETARY AND CONFIDENTIAL v

Page 7

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

FIGURE 23- DS3 AND E3 LINE LOOPBACK DIAGRAM............................... 172

FIGURE 24- DS2 LOOPBACK DIAGRAM ..................................................... 172

FIGURE 25- TELECOM DIAGNOSTIC LOOPBACK DIAGRAM.................... 173

FIGURE 26- TELECOM LINE LOOPBACK DIAGRAM .................................. 174

FIGURE 27- BOUNDARY SCAN ARCHITECTURE....................................... 196

FIGURE 28- TAP CONTROLLER FINITE STATE MACHINE......................... 198

FIGURE 29- INPUT OBSERVATION CELL (IN_CELL) .................................. 201

FIGURE 30- OUTPUT CELL (OUT_CELL) .................................................... 202

FIGURE 31- BIDIRECTIONAL CELL (IO_CELL) ........................................... 202

FIGURE 32- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS203

FIGURE 33- RECEIVE BIPOLAR DS3 STREAM........................................... 204

FIGURE 34- RECEIVE UNIPOLAR DS3 STREAM........................................ 204

FIGURE 35- RECEIVE BIPOLAR E3 STREAM ............................................. 205

FIGURE 36- RECEIVE UNIPOLAR E3 STREAM .......................................... 205

FIGURE 37- TRANSMIT BIPOLAR DS3 STREAM........................................ 206

FIGURE 38- TRANSMIT UNIPOLAR DS3 STREAM ..................................... 206

FIGURE 39- TRANSMIT BIPOLAR E3 STREAM........................................... 207

FIGURE 40- TRANSMIT UNIPOLAR E3 STREAM........................................ 207

FIGURE 41- FRAMER MODE DS3 TRANSMIT INPUT STREAM ................. 208

FIGURE 42- FRAMER MODE DS3 TRANSMIT INPUT STREAM WITH

TGAPCLK .................................................................................... 208

FIGURE 43- FRAMER MODE DS3 RECEIVE OUTPUT STREAM................ 209

FIGURE 44- FRAMER MODE DS3 RECEIVE OUTPUT STREAM WITH

RGAPCLK.................................................................................... 209

PROPRIETARY AND CONFIDENTIAL vi

Page 8

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

FIGURE 45- FRAMER MODE G.751 E3 TRANSMIT INPUT STREAM ......... 209

FIGURE 46- FRAMER MODE G.751 E3 TRANSMIT INPUT STREAM WITH

TGAPCLK .................................................................................... 210

FIGURE 47- FRAMER MODE G.751 E3 RECEIVE OUTPUT STREAM........ 210

FIGURE 48- FRAMER MODE G.751 E3 RECEIVE OUTPUT STREAM WITH

RGAPCLK.................................................................................... 210

FIGURE 49- FRAMER MODE G.832 E3 TRANSMIT INPUT STREAM ..........211

FIGURE 50- FRAMER MODE G.832 E3 TRANSMIT INPUT STREAM WITH

TGAPCLK .....................................................................................211

FIGURE 51- FRAMER MODE G.832 E3 RECEIVE OUTPUT STREAM........ 212

FIGURE 52- FRAMER MODE G.832 E3 RECEIVE OUTPUT STREAM WITH

RGAPCLK.................................................................................... 212

FIGURE 53- TELECOM DROP BUS TIMING - STS-1 SPES / AU3 VCS ...... 213

FIGURE 54- TELECOM DROP BUS TIMING - LOCKED STS-1 SPES / AU3

VCS.............................................................................................. 214

FIGURE 55- TELECOM DROP BUS TIMING - AU4 VC................................. 215

FIGURE 56- TELECOM ADD BUS TIMING - LOCKED STS-1 SPES / AU3 VCS

..................................................................................................... 216

FIGURE 57- TELECOM ADD BUS TIMING - LOCKED AU4 VC CASE......... 217

FIGURE 58- REMOTE SERIAL ALARM PORT TIMING ................................ 219

FIGURE 59- SBI DROP BUS T1/E1 FUNCTIONAL TIMING.......................... 219

FIGURE 60- SBI DROP BUS DS3/E3 FUNCTIONAL TIMING....................... 220

FIGURE 61- SBI ADD BUS JUSTIFICATION REQUEST FUNCTIONAL

TIMING ........................................................................................ 220

FIGURE 62- DS3/E3 TRANSMIT INTERFACE TIMING................................. 231

FIGURE 63- DS3/E3 RECEIVE INTERFACE TIMING ................................... 234

FIGURE 64- LINE SIDE TELECOM BUS INPUT TIMING.............................. 237

PROPRIETARY AND CONFIDENTIAL vii

Page 9

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

FIGURE 65- TELECOM BUS OUTPUT TIMING ............................................ 239

FIGURE 66- TELECOM BUS TRISTATE OUTPUT TIMING .......................... 239

FIGURE 67- SBI ADD BUS TIMING............................................................... 242

FIGURE 68- SBI DROP BUS TIMING............................................................ 244

FIGURE 69- SBI DROP BUS COLLISION AVOIDANCE TIMING .................. 244

FIGURE 70- EGRESS FLEXIBLE BANDWIDTH PORT TIMING................... 245

FIGURE 71- INGRESS FLEXIBLE BANDWIDTH PORT TIMING.................. 246

FIGURE 72- XCLK INPUT TIMING ................................................................ 247

FIGURE 73- TRANSMIT LINE INTERFACE TIMING ..................................... 248

FIGURE 74- REMOTE SERIAL ALARM PORT TIMING ................................ 249

FIGURE 75- JTAG PORT INTERFACE TIMING ............................................ 251

FIGURE 76- 324 PIN PBGA 23X23MM BODY............................................... 253

PROPRIETARY AND CONFIDENTIAL viii

Page 10

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

LIST OF TABLES

TABLE 1 - E1 FRAMER FRAMING STATES ................................................ 71

TABLE 2 - PATH SIGNAL LABEL MISMATCH STATE.................................. 97

TABLE 3 - ASYNCHRONOUS T1 TRIBUTARY MAPPING......................... 100

TABLE 4 - ASYNCHRONOUS E1 TRIBUTARY MAPPING......................... 101

TABLE 5 - ASYNCHRONOUS DS3 MAPPING TO STS-1 (STM-0/AU3).... 103

TABLE 6 - DS3 AIS FORMAT...................................................................... 104

TABLE 7 - DS3 DESYNCHRONIZER CLOCK GAPPING ALGORITHM..... 106

TABLE 8 - DS3 SYNCHRONIZER BIT STUFFING ALGORITHM................ 111

TABLE 9 - REGISTER MEMORY MAP........................................................115

TABLE 10 - INSTRUCTION REGISTER ....................................................... 142

TABLE 11 - IDENTIFICATION REGISTER ................................................... 142

TABLE 12 - BOUNDARY SCAN REGISTER ................................................ 143

TABLE 13 - INDEXING FOR 1.544 MBIT/S TRIBUTARIES.......................... 150

TABLE 14 - INDEXING FOR 2.048 MBIT/S TRIBUTARIES.......................... 151

TABLE 15 - 77.76 SBI AND TELECOM BUS ALIGNMENT OPTIONS ........ 152

TABLE 16 - 19.44 MHZ SBI TO 77.76 MHZ TELECOM TO BUS ALIGNMENT

OPTIONS..................................................................................... 153

TABLE 17 - 77.76 MHZ SBI TO 19.44 MHZ TELECOM TO BUS ALIGNMENT

OPTIONS..................................................................................... 153

TABLE 18 - PMON COUNTER SATURATION LIMITS (E1 MODE).............. 157

TABLE 19 - PMON COUNTER SATURATION LIMITS (T1 MODE).............. 157

TABLE 20 - STRUCTURE FOR CARRYING MULTIPLEXED LINKS ........... 176

TABLE 21 - T1/TVT1.5 TRIBUTARY COLUMN NUMBERING...................... 176

PROPRIETARY AND CONFIDENTIAL ix

Page 11

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

TABLE 22 - E1/TVT2 TRIBUTARY COLUMN NUMBERING ........................ 177

TABLE 23 - SBI T1/E1 LINK RATE INFORMATION ..................................... 180

TABLE 24 - SBI T1/E1 CLOCK RATE ENCODING....................................... 180

TABLE 25 - DS3 LINK RATE INFORMATION............................................... 181

TABLE 26 - DS3 CLOCK RATE ENCODING................................................ 181

TABLE 27 - T1 FRAMING FORMAT ............................................................. 182

TABLE 28 - T1 CHANNEL ASSOCIATED SIGNALING BITS........................ 183

TABLE 29 - E1 FRAMING FORMAT ............................................................. 185

TABLE 30 - E1 CHANNEL ASSOCIATED SIGNALING BITS ....................... 186

TABLE 31 - DS3 FRAMING FORMAT .......................................................... 187

TABLE 32 - DS3 BLOCK FORMAT............................................................... 188

TABLE 33 - DS3 MULTI-FRAME STUFFING FORMAT................................ 188

TABLE 34 - E3 FRAMING FORMAT ............................................................. 189

TABLE 35 - E3 FRAME STUFFING FORMAT .............................................. 190

TABLE 36 - TRANSPARENT VT1.5/TU11 FORMAT .................................... 191

TABLE 37 - TRANSPARENT VT2/TU12 FORMAT ....................................... 194

TABLE 38 - ABSOLUTE MAXIMUM RATINGS............................................. 222

TABLE 39 - D.C. CHARACTERISTICS......................................................... 223

TABLE 40 - MICROPROCESSOR INTERFACE READ ACCESS ................ 226

TABLE 41 - MICROPROCESSOR INTERFACE WRITE ACCESS............... 228

TABLE 42 - RSTB TIMING............................................................................ 230

TABLE 43 - DS3/E3 TRANSMIT INTERFACE TIMING................................. 230

TABLE 44 - DS3/E3 RECEIVE INTERFACE TIMING ................................... 234

PROPRIETARY AND CONFIDENTIAL x

Page 12

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

TABLE 45 - LINE SIDE TELECOM BUS INPUT TIMING – 19.44 MHZ

(FIGURE 67) ................................................................................ 236

TABLE 46 - TELECOM BUS OUTPUT TIMING - 19.44 MHZ

(FIGURE 65 AND FIGURE 66) .................................................... 238

TABLE 47 - TELECOM BUS OUTPUT TIMING – 77.76 MHZ

(FIGURE 65 AND FIGURE 66) .................................................... 238

TABLE 48 - SBI ADD BUS TIMING – 19.44 MHZ (FIGURE 67) ................... 240

TABLE 49 - SBI ADD BUS TIMING – 77.76 MHZ (FIGURE 67) ................... 241

TABLE 50 - SBI DROP BUS TIMING - 19.44 MHZ

(FIGURE 65 FIGURE 68)............................................................. 242

TABLE 51 - SBI DROP BUS TIMING - 77.76 MHZ

(FIGURE 68 TO FIGURE 69)....................................................... 243

TABLE 52 - EGRESS FLEXIBLE BANDWIDTH PORT TIMING

(FIGURE 70) ................................................................................ 245

TABLE 53 - INGRESS FLEXIBLE BANDWIDTH PORT TIMING

(FIGURE 71) ................................................................................ 246

TABLE 54 - XCLK INPUT (FIGURE 72)........................................................ 247

TABLE 55 - TRANSMIT LINE INTERFACE TIMING (FIGURE 73) ............... 248

TABLE 56 - REMOTE SERIAL ALARM PORT TIMING ................................ 249

TABLE 57 - JTAG PORT INTERFACE.......................................................... 250

TABLE 58 - ORDERING INFORMATION...................................................... 252

TABLE 59 - THERMAL INFORMATION – THETA JA VS. AIRFLOW ............ 252

PROPRIETARY AND CONFIDENTIAL xi

Page 13

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

1 FEATURES

• Integrates three SONET/SDH VT1.5/VT2/TU11/TU12 bit asynchronous or byte

synchronous mappers, three full featured M13 multiplexers with DS3 framers,

three E3 framers, and three SONET/SDH DS3 mappers in a single monolithic

device for terminating 84-1.544 Mbit/s or 63-2.048 Mbit/s data streams.

• Each SPE/DS3 independently programmable to allow the following modes of

operation:

• Five T1 modes of operation:

• Three STS-1, AU3 or TUG3 Bit Asynchronous VT1.5 or TU-11 Mappers with

ingress or egress per tributary link monitoring.

• Up to 84 T1 streams mapped as byte synchronous VT1.5 virtual tributaries into

three STS-1 SPEs or TU-11 tributary units into three STM-1/VC3 or TUG3 from a

STM-1/VC4.

• DS3 M13 Multiplexer with ingress or egress per link monitoring. Includes the

option to asynchronously map the DS3s into three STS-1/STM-0 SPEs.

• Up to 84 DS3 multiplexed 1.544 Mbit/s streams are mapped as bit asynchronous

VT1.5 virtual tributaries or TU-11 tributary units, providing a transmultiplexing

function between DS3 and SONET/SDH.

• Up to 63 T1 streams mapped as bit asynchronous TU-12 tributary units into three

STM-1/VC3 or TUG3 from a STM-1/VC4.

• Four E1 modes of operation:

• Three STS-1, AU3 or TUG3 Bit Asynchronous VT2 or TU-12 Mappers with

ingress or egress per tributary link monitoring.

• Up to 63 E1 streams mapped as byte synchronous VT2 virtual tributaries into

three STS-1 SPE or TU-12 tributary units into a STM-1/VC3 or TUG3 from a

STM-1/VC4.

• Up to 63 2.048 Mbit/s streams multiplexed into three DS3s following the ITU-T

G.747 recommendation. Includes the option to asynchronously map the DS3s

into three STS-1/STM-0 SPEs.

PROPRIETARY AND CONFIDENTIAL 1

Page 14

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Up to 63 DS3 multiplexed 2.048 Mbit/s streams are mapped as bit asynchronous

VT2 virtual tributaries or TU-12 tributary units, providing a transmultiplexing

function between DS3 and SONET/SDH.

• Two unchannelized DS3 modes of operation:

• Standalone unchannelized DS3 framer mode for access to the entire DS3

payload.

• Up to three DS3 streams are mapped bit asynchronously into VC-3s.

• Standalone unchannelized E3 framer mode (ITU-T Rec. G.751 or G.832) for

access to the entire E3 payload.

• Up to 84 VT1.5/TU11 or 63 VT2/TU12 tributaries can be passed between the line

SONET/SDH bus and the SBI bus as transparent virtual tributaries with pointer

processing.

• Supports a byte serial Scaleable Bandwidth Interconnect (SBI) bus interface for

high density system side device interconnection of up to 84 T1 streams, 63 E1

streams, 3 DS3 streams or 3 E3 streams. This interface also supports

transparent virtual tributaries when used with the SONET/SDH mapper.

• Supports insertion and extraction of arbitrary rate (eg. fractional DS3) data

streams to and from the SBI bus interface.

• Provides jitter attenuation in the T1 or E1 receive and transmit directions.

• Provides three independent de-jittered 1.544 MHz or 2.048 MHz recovered

clocks for system timing and redundancy.

• Provides per link diagnostic and line loopbacks.

• Provides an on-board programmable binary sequence generator and detector for

error testing at DS3 and E3 rates. Includes support for patterns recommended in

ITU-T O.151.

• Also provides PRBS generators and detectors on each tributary for error testing

at 1.544 Mbit/s and 2.048 Mbit/s rates as recommended in ITU-T O.151 and

O.152.

• Supports the M23 and C-bit parity DS3 formats.

PROPRIETARY AND CONFIDENTIAL 2

Page 15

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• When configured to operate as a DS3 or E3 Framer, gapped transmit and

receive clocks can be optionally generated for interface to link layer devices

which only need access to payload data bits.

• DS3 or E3 Transmit clock source can be selected from either an external

oscillator or from the receive side clock (loop-timed).

• Provides a SONET/SDH Add/Drop bus interface with integrated VT1.5, TU-11,

VT2 and TU-12 mapper for T1and E1 streams. Also provides a DS3 mapper.

• System side interface is an SBI bus.

• Provides a generic 8-bit microprocessor bus interface for configuration, control

and status monitoring.

• Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

test purposes.

• Low power 1.8V/3.3V CMOS technology. All pins are 5V tolerant.

• 324-pin fine pitch PBGA package (23mm x 23mm). Supports industrial

temperature range (-40oC to 85oC) operation.

Each one of 84 T1 performance monitor sections:

• Provides non-intrusive performance monitoring of either ingress or egress paths,

as selected on a per-tributary basis.

• Frames to DS-1 signals in SF, SLC96 and ESF formats.

• Frames to TTC JT-G.704 multiframe formatted J1 signals. Supports the

alternate CRC-6 calculation for Japanese applications.

• Provides Red, Yellow, and AIS alarm integration.

• Supports RAI-CI and AIS-CI alarm detection and generation.

• Non-intrusive performance monitoring provided by the TEMAP-84 also

provides an HDLC interface with 128 bytes of buffering for terminating the

facility data link in either the ingress or egress paths, as selected on a pertributary basis.

• Provides Inband Loopback Code detection.

PROPRIETARY AND CONFIDENTIAL 3

Page 16

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Provides performance monitoring counters sufficiently large as to allow

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the performance monitoring counters and interrupts the

microprocessor once per second.

• An unframed pseudo-random sequence user selectable from 27 –1, 211 –1, 215 –

1 or 220 –1, may be detected in the T1 stream in either the ingress or egress

directions. The detector counts pattern errors using a 16-bit non-saturating PRBS

error counter.

• Line side interface is either from the DS3 interface via the M13 multiplex or from

the SONET/SDH Drop bus via the VT1.5, TU-11, VT2 or TU-12 demapper.

• Frames in the presence of and detects the “Japanese Yellow” alarm.

Each one of 63 E1 performance monitor sections:

• Provides non-intrusive performance monitoring of either ingress or egress paths,

as selected on a per-tributary basis.

• Frames to ITU-T G.704 basic and CRC-4 multiframe formatted E1 signals. The

framing procedures are consistent ITU-T G.706 specifications.

• Non-intrusive performance monitoring provided by the TEMAP-84 also

provides an HDLC interface with 128 bytes of buffering for terminating the

facility data link in either the ingress or egress paths, as selected on a pertributary basis.

• Provides performance monitoring counters sufficiently large as to allow

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the performance monitoring counters and interrupts the

microprocessor once per second.

• An unframed pseudo-random sequence user selectable from 27 –1, 211 –1, 215 –

1 or 220 –1, may be detected in the E1 stream in either the ingress or egress

directions. The detector counts pattern errors using a 16-bit non-saturating PRBS

error counter.

Each one of 84 transmit tributaries:

• May be timed to its associated receive clock (loop timing) or may derive its timing

from a common egress clock or a common transmit clock; the transmit line clock

may be synthesized from an N*8 kHz reference.

• Provides a digital phase locked loop for generation of a low jitter transmit clock.

PROPRIETARY AND CONFIDENTIAL 4

Page 17

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Provides a FIFO buffer for jitter attenuation in the transmitter.

Each one of three SONET/SDH Tributary Path Processing Sections:

• Interfaces with a byte wide Telecom Add/Drop bus, interfacing directly with the

PM5362 TUPP-PLUS and PM5342 SPECTRA-155 at 19.44 MHz.

• Seamlessly interfaces with a 77.76 MHz Drop bus. Interfaces to a 77.76 MHz

Add bus with minimal external logic.

• Compensates for pleisiochronous relationships between incoming and outgoing

higher level (STS-1, AU4, AU3) synchronous payload envelope frame rates

through processing of the lower level tributary pointers.

• Optionally frames to the H4 byte in the path overhead to determine tributary

multi-frame boundaries and generates change of loss-of-frame status interrupts.

• Detects loss of pointer (LOP) and re-acquisition for each tributary and optionally

generates interrupts.

• Detects tributary path alarm indication signal (AIS) and return to normal state for

each tributary and optionally generates interrupts

• Detects tributary elastic store underflow and overflow and optionally generates

interrupts.

• Provides individual tributary path signal label register that hold the expected label

and detects tributary path signal label mismatch alarms (PSLM) and return to

matched state for each tributary and optionally generates interrupts.

• Detects tributary path signal label unstable alarms (PSLU) and return to stable

state for each tributary and optionally generates interrupts.

• Detects assertion and removal of tributary extended remote defect indications

(RDI) for each tributary and optionally generates interrupts.

• Calculates and compares the tributary path BIP-2 error detection code for each

tributary and configurable to accumulate the BIP-2 errors on block or bit basis in

internal registers.

• Allows insertion of all-zeros or all-ones tributary idle code with unequipped

indication and valid pointer into any tributary under software control.

• Allows software to force the AIS insertion on a per tributary basis.

PROPRIETARY AND CONFIDENTIAL 5

Page 18

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Inserts valid H4 byte and all-zeros fixed stuff bytes. Remaining path overhead

bytes (J1, B3, C2,G1, F2, Z3, Z4, Z5) are set to all-zeros.

• Inserts valid pointers and all-zeros transport overhead bytes on the outgoing

Telecom Add bus, with valid control signals.

• Support in-band error reporting by updating the FEBE, RDI and auxiliary RDI bits

in the V5 byte with the status of the incoming stream and remote alarm pins.

• Calculates and inserts the tributary path BIP-2 error detection code for each

tributary.

Each one of three SONET/SDH VT/TU Mapper Sections:

• Inserts up to 28 bit asynchronous mapped VT1.5 virtual tributaries into an STS-1

SPE from T1 streams.

• Inserts up to 28 bit asynchronous mapped TU-11 tributary units into a STM1/VC4 TUG3 or STM-1/VC3 from T1 streams.

• Inserts up to 28 byte synchronous mapped VT1.5 virtual tributaries into an STS-1

SPE or TU-11 tributary units into an STM-1/VC3 or TUG3 from a STM-1/VC4.

• Inserts up to 21 bit asynchronous mapped VT2 virtual tributaries into an STS-1

SPE from E1 streams.

• Inserts up to 21 bit asynchronous mapped TU-12 tributary units into an STM1/VC4 TUG3 or STM-1/VC3 from E1 or T1 streams.

• Processes the tributary trace message (J2) of the tributaries carried in each

STS-1/TUG-3 synchronous payload envelope.

• Bit asynchronous mapping assigns stuff control bits for all streams independently

using an all digital control loop. Stuff control bits are dithered to produce

fractional mapping jitter at the receiving desynchronizer.

• Sets all fixed stuff bits for asynchronous mappings to zeros or ones per

microprocessor control

• Extracts up to 28 bit asynchronous mapped VT1.5 virtual tributaries from an

STS-1 SPE into T1 streams via an optional elastic store.

• Extracts up to 28 bit asynchronous mapped TU-11 tributary units from an STM1/VC4 TUG3 or STM-1/VC3 into T1 streams via an optional elastic store.

PROPRIETARY AND CONFIDENTIAL 6

Page 19

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Extracts up to 21 bit asynchronous mapped VT2 virtual tributaries from an STS-1

SPE into E1 streams via an optional elastic store.

• Extracts up to 21 bit asynchronous mapped TU-12 tributary units from an STM1/VC4 TUG3 or STM-1/VC3 into E1 or T1 streams via an optional elastic store.

• Demapper ignores all transport overhead bytes, path overhead bytes and stuff

(R) bits

• Performs majority vote C-bit decoding to detect stuff requests.

Each one of three SONET/SDH DS3 Mapper Sections:

• Maps a DS3 stream into an STS-1 SPE (AU3).

• Sets all fixed stuff (R) bits to zeros or ones per microprocessor control

• Extracts a DS3 stream from an STS-1 SPE (AU3).

• Demapper ignores all transport overhead bytes, path overhead bytes and stuff

(R) bits

• Performs majority vote C-bit decoding to detect stuff requests

• Complies with DS3 to STS-1 asynchronous mapping standards

Each one of three DS3 Receiver Sections:

• Frames to a DS3 signal with a maximum average reframe time of less than 1.5

ms (as required by TR-TSY-000009 Section 4.1.2 and TR-TSY-000191 Section

5.2).

• Decodes a B3ZS-encoded signal and indicates line code violations. The

definition of line code violation is software selectable.

• Provides indication of M-frame boundaries from which M-subframe boundaries

and overhead bit positions in the DS3 stream can be determined by external

processing.

• Detects the DS3 alarm indication signal (AIS) and idle signal. Detection

algorithms operate correctly in the presence of a 10-3 bit error rate.

• Detection times of 2.23 ms and 13.5 ms are supported. The fast detection time

meets the requirement of TR-TSY-000191 Section 5. The longer detection time

PROPRIETARY AND CONFIDENTIAL 7

Page 20

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

meets the ANSI T1M1.3 Section 7.1.2.4 requirement that AIS be detected in less

than 100 ms and is intended for non-BOC (Bell Operating Company)

applications.

• Extracts valid X-bits and indicates far end receive failure (FERF). The far end

receive failure status only changes if the two X-bits are the same. The status is

buffered for two M-frames, ensuring a better than 99.99% chance of freezing the

correct status for the duration of the out of frame occurrence.

• Accumulates up to 65,535 line code violation (LCV) events per second, 65,535

P-bit parity error events per second, 1023 F-bit or M-bit (framing bit) events per

second, 65,535 excessive zero (EXZ) events per second, and when enabled for

C-bit parity mode operation, up to 16,383 C-bit parity error events per second,

and 16,383 far end block error (FEBE) events per second (note that, over a one

second interval, only 9399 P-bit errors, C-bit parity errors, or FEBE events can

occur).

• Detects and validates bit-oriented codes in the C-bit parity far end alarm and

control channel.

• Terminates the C-bit parity path maintenance data link with an integral HDLC

receiver having a 128-byte deep FIFO buffer with programmable interrupt

threshold. Supports polled or interrupt-driven operation. Selectable none, one or

two address match detection on first byte of received packet.

• Programmable pseudo-random test-sequence detection–(up to 2

32

-1 bit length

patterns conforming to ITU-T O.151 standards) and analysis features.

Each one of three DS3 Transmit Sections:

• Provides the overhead bit insertion for a DS3 stream.

• Provides a bit serial clock and data interface, and allows the M-frame boundary

and/or the overhead bit positions to be located via an external interface

• Provides B3ZS encoding.

• Generates an B3ZS encoded 100… repeating pattern to aid in pulse mask

testing.

• Inserts far end receive failure (FERF), the DS3 alarm indication signal (AIS) and

the idle signal when enabled by internal register bits.

PROPRIETARY AND CONFIDENTIAL 8

Page 21

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Provides optional automatic insertion of far end receive failure (FERF) on

detection of loss of signal (LOS), out of frame (OOF), alarm indication signal

(AIS) or red alarm condition.

• Provides diagnostic features to allow the generation of line code violation error

events, parity error events, framing bit error events, and when enabled for the Cbit parity application, C-bit parity error events, and far end block error (FEBE)

events.

• Supports insertion of bit-oriented codes in the C-bit parity far end alarm and

control channel.

• Optionally inserts the C-bit parity path maintenance data link with an integral

HDLC transmitter. Supports polled and interrupt-driven operation.

• Provides programmable pseudo-random test sequence generation (up to 232-1

bit length sequences conforming to ITU-T O.151 standards) or any repeating

pattern up to 32 bits. The test pattern can be framed or unframed. Diagnostic

abilities include single bit error insertion or error insertion at bit error rates

ranging from 10-1 to 10-7.

M23 Multiplexer Section:

• Multiplexes 7 DS2 bit streams into a single M23 format DS3 bit stream.

• Performs required bit stuffing/destuffing including generation and interpretation of

C-bits.

• Includes required FIFO buffers for rate adaptation in the multiplex path.

• Allows insertion and detection of per DS2 payload loopback requests encoded in

the C-bits to be activated under microprocessor control.

• Internally generates a DS2 clock for use in integrated M13 or C-bit parity

multiplex applications. Alternatively accepts external DS2 clock reference.

• Allows per DS2 alarm indication signal (AIS) to be activated or cleared for either

direction under microprocessor control.

• Allows DS2 alarm indication signal (AIS) to be activated or cleared in the

demultiplex direction automatically upon loss of DS3 frame alignment or signal.

• Supports C-bit parity DS3 format.

PROPRIETARY AND CONFIDENTIAL 9

Page 22

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

DS2 Framer Section:

• Frames to a DS2 (ANSI T1.107 section 8) signal with a maximum average

reframe time of less than 7 ms (as required by TR-TSY-000009 Section 4.1.2

and TR-TSY-000191 Section 5.2).

• Detects the DS2 alarm indication signal (AIS) in 9.9 ms in the presence of a 10

bit error rate.

• Extracts the DS2 X-bit remote alarm indication (RAI) bit and indicates far end

receive failure (FERF). The far end receive failure status only changes when the

associated bit has been in the same state for two consecutive frames. The

status is buffered for six M-frames, ensuring a better than 99.9% chance of

freezing the correct status for the duration of the out of frame occurrence.

• Accumulates up to 255 DS2 M-bit or F-bit error events per second.

DS2 Transmitter Section:

• Generates the required X, F, and M bits into the transmitted DS2 bit stream.

Allows inversion of inserted F or M bits for diagnostic purposes.

• Provides for transmission of far end receive failure (FERF) and alarm indication

signal (AIS) under microprocessor control.

• Provides optional automatic insertion of far end receive failure (FERF) on

detection of out of frame (OOF), alarm indication signal (AIS) or red alarm

condition.

-3

M12 Multiplexer Section:

• Multiplexes four DS1 or three 2048 kbit/s (according to ITU-T Rec. G.747) bit

streams into a single M12 format DS2 bit stream.

• Performs required bit stuffing including generation and interpretation of C-bits.

• Includes required FIFO buffers for rate adaptation in the multiplex path.

• Performs required inversion of second and fourth multiplexed DS1 streams as

required by ANSI T1.107 Section 7.2.

• Allows insertion and detection of per DS1 payload loopback requests encoded in

the C-bits to be activated under microprocessor control.

PROPRIETARY AND CONFIDENTIAL 10

Page 23

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Allows per tributary alarm indication signal (AIS) to be activated or cleared for

either direction under microprocessor control.

• Allows automatic tributary AIS to be activated upon DS2 out of frame.

Each one of three E3 Framer Sections:

• Frames to G.751 and G.832 E3 unchannelized data streams.

• For G.832, terminates the Trail Trace and either the Network Requirement or the

General Purpose data link.

Each one of three E3 Transmit Sections:

• Provides frame insertion for the G.751 or G.832 E3 applications, alarm insertion,

and diagnostic features.

• For G.832, the Trail Trace is inserted, and an integral HDLC transmitter is

provided to insert either the Network Requirement or the General Purpose data

link.

Scaleable Bandwidth Interconnect (SBI) Bus:

• Provides a high density byte serial interconnect for all framed and unframed

TEMAP-84 links. Utilizes an Add/Drop configuration to asynchronously mutliplex

up to 84 T1s, 63 E1s, 3 E3s or 3 DS3s, with multiple payload or link layer

processors.

• Operates at either 19.44 MHz or 77.76 MHz.

• External devices can access unframed DS3, framed unchannelized DS3,

unframed E3, framed unchannelized E3, unframed (clear channel) T1s, framed

T1s (byte synchronous mapping only), unframed (clear channel) E1s, framed

E1s (byte synchronous mapping only), arbitrary rate clear channel data stream

(eg. fractional DS3), transparent virtual tributaries or transparent tributary units

over this interface.

• Up to three arbitrary rate data streams inserted into and extracted from the SBI

via bit serial ports.

• Transparent VT/TU access can be selected only when tributaries are mapped

into SONET/SDH.

PROPRIETARY AND CONFIDENTIAL 11

Page 24

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Transmit timing is mastered either by the TEMAP-84 or a layer 2 device

connecting to the SBI bus. Timing mastership is selectable on a per tributary

basis, where a tributary is either an individual T1, E1, E3 or a DS3.

PROPRIETARY AND CONFIDENTIAL 12

Page 25

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

2 APPLICATIONS

• SONET/SDH Add Drop Multiplexers

• SONET/SDH Terminal Multiplexers

• M23 Based M13 Multiplexer

• C-Bit Parity Based M13 Multiplexer

• Channelized and Unchannelized DS3 Frame Relay Interfaces

• Optical Access Equipment

PROPRIETARY AND CONFIDENTIAL 13

Page 26

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

3 REFERENCES

• American National Standard for Telecommunications - Digital Hierarchy Synchronous DS3 Format Specifications, ANSI T1.103-1993

• American National Standard for Telecommunications – ANSI T1.105 –

“Synchronous Optical Network (SONET) – Basic Description Including Multiplex

Structure, Rates, and Formats,” October 27, 1995.

• American National Standard for Telecommunications – ANSI T1.105.02 –

“Synchronous Optical Network (SONET) – Payload Mappings,” October 27,

1995.

• American National Standard for Telecommunications - Digital Hierarchy Formats Specification, ANSI T1.107-1995

• American National Standard for Telecommunications - Digital Hierarchy - Layer 1

In-Service Digital Transmission Performance Monitoring, ANSI T1.231-1997

• American National Standard for Telecommunications - Carrier to Customer

Installation - DS-1 Metallic Interface Specification, ANSI T1.403-1995

• American National Standard for Telecommunications - Customer Installation–toNetwork - DS3 Metallic Interface Specification, ANSI T1.404-1994

• American National Standard for Telecommunications - Integrated Services Digital

Network (ISDN) Primary Rate- Customer Installation Metallic Interfaces Layer 1

Specification, ANSI T1.408-1990

• Bell Communications Research, TR–TSY-000009 - Asynchronous Digital

Multiplexes Requirements and Objectives, Issue 1, May 1986

• Bell Communications Research - DS-1 Rate Digital Service Monitoring Unit

Functional Specification, TA-TSY-000147, Issue 1, October, 1987

• Bell Communications Research - Alarm Indication Signal Requirements and

Objectives, TR-TSY-000191 Issue 1, May 1986

• Bell Communications Research - Wideband and Broadband Digital CrossConnect Systems Generic Criteria, TR-NWT-000233, Issue 3, November 1993

PROPRIETARY AND CONFIDENTIAL 14

Page 27

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• Bell Communications Research – Digital Interface Between The SLC96 Digital

Loop Carrier System And A Local Digital Switch, TR-TSY-000008, Issue 2,

August 1987

• Bellcore GR-253-CORE – “SONET Transport Systems: Common Criteria,” Issue

2, Revision 1, December 1997.

• Bell Communications Research - Integrated Digital Loop Carrier Generic

Requirements, Objectives, and Interface, TR-NWT-000303, Issue 2, December,

1992

• Bell Communications Research - Transport Systems Generic Requirements

(TSGR): Common Requirement, TR-TSY-000499, Issue 5, December, 1993

• Bell Communications Research - OTGR: Network Maintenance Transport

Surveillance - Generic Digital Transmission Surveillance, TR-TSY-000820,

Section 5.1, Issue 1, June 1990

• AT&T - Requirements For Interfacing Digital Terminal Equipment To Services

Employing The Extended Superframe Format, TR 54016, September, 1989.

• AT&T - Accunet T1.5 - Service Description and Interface Specification, TR 62411,

December, 1990

• ITU Study Group XVIII – Report R 105, Geneva, 9-19 June 1992

• ETSI - ETS 300 011 - ISDN Primary Rate User-Network Interface Specification

and Test Principles, 1992.

• ETSI - ETS 300 233 - Access Digital Section for ISDN Primary Rates, May 1994

• ETSI - ETS 300 324-1 - Signaling Protocols and Switching (SPS); V interfaces at

the Digital Local Exchange (LE) V5.1 Interface for the Support of Access

Network (AN) Part 1: V5.1 Interface Specification, February, 1994.

• ETSI - ETS 300 347-1 - Signaling Protocols and Switching (SPS); V Interfaces at

the Digital Local Exchange (LE) V5.2 Interface for the Support of Access

Network (AN) Part 1: V5.2 Interface Specification, September 1994.

• ETSI ETS 300 417-1-1 – “Transmission and Multiplexing (TM); Generic

Functional Requirements for Synchronous Digital Hierarchy (SDH) equipment;

Part 1-1: Generic processes and performance,” January, 1996.

• ETSI, Generic Functional Requirements for Synchronous Digital Hierarchy (SDH)

Equipment, Jan 1996

PROPRIETARY AND CONFIDENTIAL 15

Page 28

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• ITU-T - Recommendation G.704 - Synchronous Frame Structures Used at

Primary Hierarchical Levels, July 1995.

• ITU-T - Recommendation G.706 - Frame Alignment and CRC Procedures

Relating to G.704 Frame Structures, 1991.

• ITU-T Recommendation G.707 – Network Node Interface for the Synchronous

Digital Hierarchy, 1996

• ITU-T Recommendation G.747 – Second Order Digital Multiplex Equipment

Operating at 6312 kbit/s and Multiplexing Three Tributaries at 2048 kbit/s, 1988

• ITU-T Recommendation G.751, - CCITT Blue Book Fasc. III.4, "Digital Multiplex

Equipments Operating at the Third Order Bit Rate of 34,368 kbit/s and the Fourth

Order Bit Rate of 139,264 kbit/s and Using Positive Justification”, 1988

• ITU-T Recommendation G.775, - Loss of Signal (LOS) and Alarm Indication

Signal (AIS) Defect Detection and Clearance Criteria, 11/94

• ITU-T Recommendation G.783 – Characteristics of Synchronous Digital

Hierarchy (SDH) Equipment Functional Blocks, April, 1997.

• ITU-T Recommendation G.823, - The Control of Jitter and Wander within Digital

Networks which are Based on the 2048 kbit/s Hierarchy, 03/94

• ITU-T Recommendation G.832 - "Transport of SDH Elements on PDH Networks:

Frame and Multiplexing Structures", 1993.

• ITU-T Recommendation G.964, - V-Interfaces at the Digital Local Ex–hange (LE)

- V5.1 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN),

June 1994.

• ITU-T Recommendation G.965, - V-Interfaces at the Digital Local Ex–hange (LE)

- V5.2 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN),

March –995.

• ITU-T - Recommendation I.431 - Primary Rate User-Network Interface – Layer 1

Specification, 1993.

• ITU-T Recommendation O.151 – Error Performance Measuring Equipment

Operating at the Primary Rate and Above, October 1992

• ITU-T Recommendation O.152 – Error Performance Measuring Equipment for

Bit Rates of 64 kbit/s and N x 64 kbit/s, October 1992

PROPRIETARY AND CONFIDENTIAL 16

Page 29

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

• ITU-T Recommendation O.153 - Basic Parameters for the Measurement of Error

Performance at Bit Rates below the Primary Rate, October 1992.

• ITU-T Recommendation Q.921 - ISDN User-Network Interface Data Link Layer

Specification, March 1993

• International Organization for Standardization, ISO 3309:1984 - High-Level Data

Link Control procedures - Frame Structure

• TTC Standard JT-G704 - Frame Structures on Primary and Secondary

Hierarchical Digital Interfaces, 1995.

• TTC Standard JT-G706 - Frame Synchronization and CRC Procedure

• TTC Standard JT-I431 - ISDN Primary Rate User-Network Interface Layer 1 -

Specification, 1995.

• Nippon Telegraph and Telephone Corporation - Technical Reference for HighSpeed Digital Leased Circuit Services, Third Edition, 1990.

PROPRIETARY AND CONFIDENTIAL 17

Page 30

PRELIMINARY

PM5366 TEMAP-84

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

AND M13 MULTIPLEXER

4 APPLICATION EXAMPLES

PM5366 TEMAP-84 in conjunction with PMC's PM4318 OCTLIU provides a highdensity line card for SONET/SDH Add/Drop Multiplexers' as shown in Figure 1.

Figure 1 - High-Density Line Card Application

Work

Prot

Prot

Dro pAdd

SBI

OC-12

PM5313

SPECT RA-62 2

PM5363

TUPP-622

PM4318

OCTLIU

8 x T1

or

8 x E1

OC-12

Eas t Ca rd

SPECT RA-62 2

West Card

PM5313

PM5363

TUPP-622

Tribut ary

Cross -Connec t

PM5366

TEMAP-84

PM4318

OCTLIU

PM4318

OCTLIU

Figure 2 shows a OC-12 Multi-Service Switch application, whereby PM5366

TEMAP-84 provides VT/TU mapping and Performance Monitoring. PM5366

TEMAP-84 connects seamlessly to PMC's link layer products using the

Scaleable Bandwidth Interconnect (SBI) bus.

PROPRIETARY AND CONFIDENTIAL 18

Page 31

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

Figure 2 - OC-12 Multi-Service Switch Application

Telec om

PM536 6

TEMAP-84

PM5313

OC-1 2

SPECTRA-622

DS3

DS3

LIU

DS3

LIU

LIU

PM536 6

TEMAP-84

PM5366

TEMAP-84

PM536 6

TEMAP-84

Figure 3 - Fractional DS3 Application

PM7384

FREEDM -8 4

PM73122

AAL1 gat or -32

FPGA

Packet/Cell

Interne tworking

APPI

Function

SBI

Bus

Utopia

UtopiaSBI APP I

PM7324

S/ UNI-ATL AS

PM7826

S/ UNI-AP EX

O

O

K

P

T

L

F

A

C

M

D

S

R

R

R

PM5366

DS3

TEMAP-84

LIU

K

O

I

L

P

T

C

I

F

A

T

D

M

T

T

44.736

FPGA

MHz

To support evolving fractional DS3 applications, flow-controlled ports provide

access to SBI bus bandwidth. Several non-standard schemes have been

PROPRIETARY AND CONFIDENTIAL 19

T

N

A

E

K

D

L

W

C

W

B

F

B

W

I

F

B

I

F

I

K

Q

L

E

C

W

B

F

E

T

N

R

A

E

D

D

W

W

W

B

B

B

F

F

F

E

E

E

Page 32

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

devised to use a portion of the DS3 payload. Given that these protocols are

subject to change, they are best supported by external programmable logic.

Figure 3 illustrates one implementation. Other implementations and applications

are possible.

In the ingress direction, the framed DS3 is presented to an FPGA, whose

responsibility it is to identify the utilitized bits of the payload. Valid bits are

indicated to the Ingress Flexible Bandwidth Port via an enable signal, IFBWEN.

The bits are collected into bytes by the TEMAP-84 and inserted into the payload

of the SBI Drop bus.

In the egress direction, an FPGA formats the payload of a DS3, while the

TEMAP-84 inserts the DS3 frame overhead. The FPGA contains a data buffer.

Based on the DS3 frame alignment dictated by the TMFPO signal, the FPGA

inserts bits from the data buffer into the DS3 payload according to the protocol

supported. To ensure the data buffer is replenished, the FPGA asserts the

EFBWDREQ signal to initiate the transfer of a bit. The Egress Flexible

Bandwidth Port responds by asserting EFWBEN coincident with EFWBDAT

presenting valid data. The SBI Add bus participates by modulating its

SAJUST_REQ output to match the SBI data rate to that required to keep internal

FIFOs centered.

PROPRIETARY AND CONFIDENTIAL 20

Page 33

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

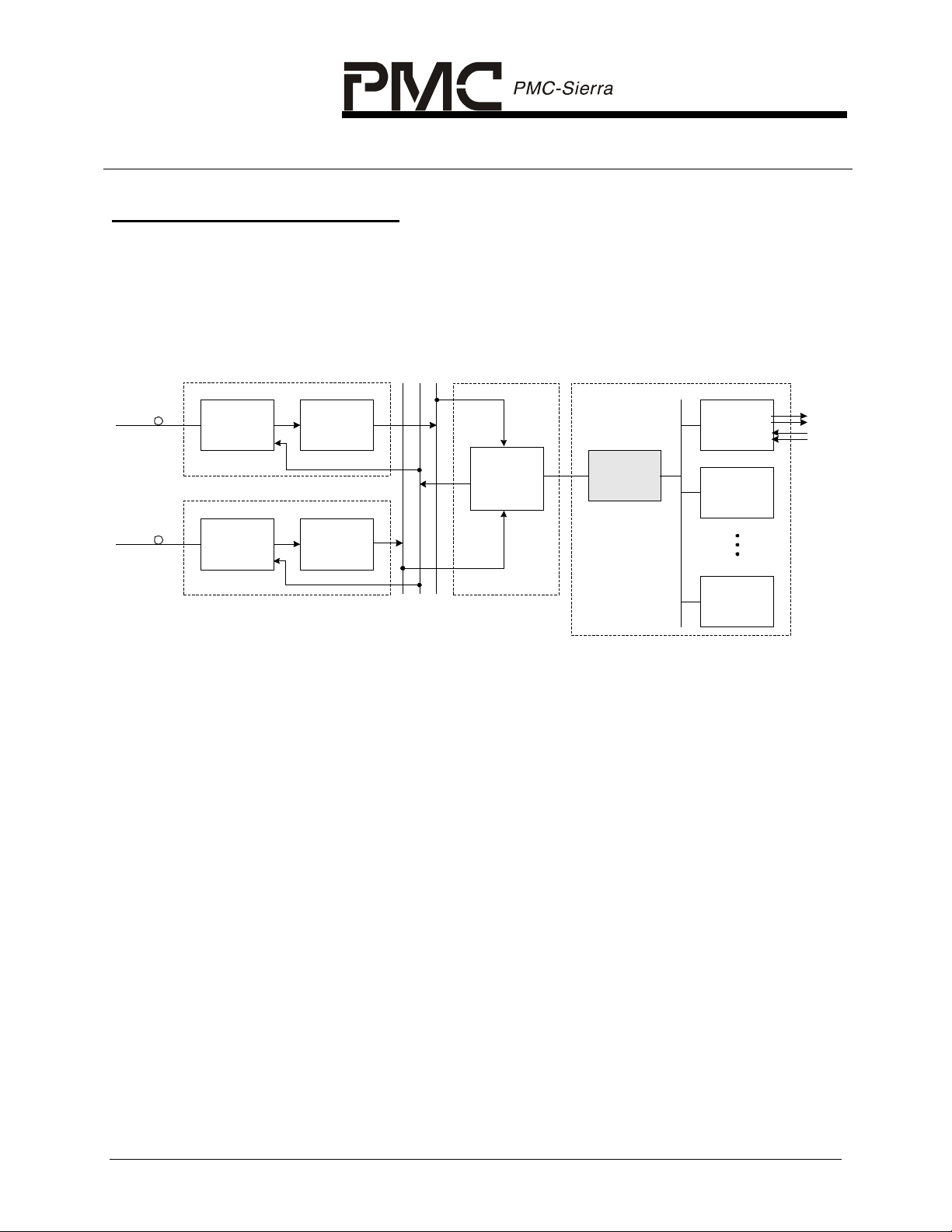

5 BLOCK DIAGRAM

5.1 Top Level Block Diagram

Figure 4 shows the complete TEMAP-84. T1 links can be multiplexed into the

DS3s or can be mapped into the telecom bus as SONET VT1.5 virtual tributaries

or as SDH TU-11 or TU-12 tributary units. E1 links can be mapped into the

telecom bus as SONET VT2 virtual tributaries or as SDH TU-12 tributary units.

System side access to the T1s and E1s is available through the SBI bus. DS3

line side access is via the clock and data interface for line interface units (LIUs)

or DS3 mapped into the SONET/SDH telecom bus. Unchannelized DS3 system

side access is available through the SBI bus.

Figure 4 - TEMAP-84 Block Diagram

LIUs

M13

M13

D3MA

Telecom Bus

M13

M13

VTPP

M13

M13

VTPP

Telecom Bus

M13

M13

D3MD

LIUs

DS3 /E3 Tx System I/F

M13

M13

DS3/E3

TRAN

TTOP

M13

M13

RTOP/

RTTB

M13

M13

DS3/E3

FRMR

DS3/E3 Rx System I/F

M13

M13

M13

TRAP

M13

M13

M13

M13

M13

PISO

INSBI

(byte)

TTMP

(bit)

RTDM

(bit)

EXSBI

(byte)

M13

M13

SIPO

Transm ux

datapath

T1/E1

JAT84

T1/E1

JAT84

Flexible

B/W Port

T1/E1

FRMR84

Ingress

Flexible

B/W Port

Egress

EXSBI

SBI 155

INSBI

PROPRIETARY AND CONFIDENTIAL 21

Page 34

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

5.2 DS3/E3 Framer Only Block Diagram

Figure 5 shows the TEMAP-84 configured as a DS3 or E3 framer. In this mode

the TEMAP-84 provides access up to three full DS3/E3 unchannelized payloads.

The payload access (right side of diagram) has two clock and data interfacing

modes, one utilizing a gapped clock to mask out the DS3/E3 overhead bits and

the second utilizing an ungapped clock with overhead indications on a separate

overhead signal. The SBI bus can also be used to provide access to the

unchannelized DS3/E3.

Figure 5 - DS3/E3 Framer Only Mode Block Diagram

TDPR

Tx

HDLC

TICLK

TCLK

TPOS/TDAT

TNEG/TMFP

RCLK/VCLK

RPOS/RDAT

RNEG/RLCV

B3ZS/

HDB3

Encode

B3ZS/

HDB3

Decode

TRAN

DS3/E3

Transmit

Framer

FRMR

DS3/E3

Receive

Framer

TDATI

TFPO/TMFPO/TGAPCLK

TFPI/TMFPI

RGAPCLK/RSCLK

RDATO

RFPO/RMFPO

ROVRHD

RDLC

Rx

HDLC

PMON

Perf.

Monitor

3X

PROPRIETARY AND CONFIDENTIAL 22

Page 35

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

6 DESCRIPTION

The PM5366 High Density 84/63 Channel VT/TU Mapper and M13 Multiplexer

(TEMAP-84) is a feature-rich device for use in any applications requiring high

density link termination over T1 and E1 (G.747) channelized DS3 or T1 and E1

channelized SONET/SDH facilities.

The TEMAP-84 supports asynchronous multiplexing and demultiplexing of 84

1.544 Mbit/s or 63 2.048 Mbit/s tributaries into three DS3 signals as specified by

ANSI T1.107, Bell Communications Research TR-TSY-000009 and ITU-T Rec.

G.747. It supports bit asynchronous or byte synchronous mapping and

demapping of 84 T1s or 63 E1s into SONET/SDH as specified by ANSI T1.105,

Bell Communications Research GR-253-CORE and ITU-T Recommendation

G.707. The TEMAP-84 also supports mapping of 63 T1s into SDH via TU-12s.

Up to 84 Transparent VT1.5s and TU-11s or 63 Transparent VT2s and TU-12s

can be transferred between the SONET/SDH interface and the SBI bus

interface.

This device can also be configured as a DS3 or E3 framer, providing external

access to the full DS3 or E3 payload, or a VT/TU mapper, providing access to

unframed 1.544 Mbit/s and 2.048 Mbit/s links.

The TEMAP-84 can be used as a SONET/SDH VT/TU mapper or M13

multiplexer with performance monitoring in either the ingress or egress direction

for up to 84 T1s or 63 E1s.

Each of the T1 and E1 jitter attenuators and performance monitors is

independently software configurable, allowing timing master and feature

selection without changes to external wiring. 1.544 Mbit/s and 63 2.048 Mbit/s

tributaries may be mixed at a VC-3/TUG-3/DS3 granularity.

In the ingress direction, each of the 84 T1 links is either demultiplexed from a

channelized DS3 or extracted from SONET VT1.5, TU-11 or TU-12 mapped bus.

Each T1 performance monitor can be configured to frame to the common DS1

signal formats (SF, SLC96, ESF).

T1 performance monitoring with accumulation of CRC-6 errors, framing bit

errors, out-of-frame events, and changes of frame alignment is provided. . The

TEMAP-84 also detects the presence of ESF bit oriented codes, and detects and

terminates HDLC messages on the ESF data link. The HDLC messages are

terminated in a 128 byte FIFO.

PROPRIETARY AND CONFIDENTIAL 23

Page 36

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

In the ingress direction, each of the 63 2.048 Mbit/s links is either demultiplexed

from a DS3 according to ITU-T Rec. G.747 or extracted from SONET/SDH VT2

or TU-12 mapped bus.

The E1 performance monitors support detection of various alarm conditions such

as loss of frame, loss of signaling multiframe and loss of CRC multiframe. The

E1 framers also support reception of remote alarm signal, remote multiframe

alarm signal, alarm indication signal, and time slot 16 alarm indication signal.

E1 performance monitoring with accumulation of CRC-4 errors, far end block

errors and framing bit errors is provided. The TEMAP-84 provides a receive

HDLC controller for the detection and termination of messages on the national

use bits.

The TEMAP-84 can generate a low jitter transmit clock from a variety of clock

references, and also provides jitter attenuation in the receive path. Three jitter

attenuated recovered T1/E1 clocks can be routed outside the TEMAP-84 for

network timing applications.

A Scaleable Bandwidth Interconnect (SBI) high density byte serial system

interface provides higher levels of integration and dense interconnect. The SBI

bus interconnects up to 84 T1s or 63 E1 both synchronously or asynchronously.

The SBI allows transmit timing to be mastered by either the TEMAP-84 or link

layer device connected to the SBI bus. In addition to unframed T1s and E1s, the

TEMAP-84 can transport framed or unframed DS3 or E3 links over the SBI bus.

When configured as a DS3 multiplexer/demultiplexer or DS3 framer, the TEMAP84 accepts and outputs either digital B3ZS-encoded bipolar or unipolar signals

compatible with M23 and C-bit parity applications.

In the DS3 receive direction, the TEMAP-84 frames to DS3 signals with a

maximum average reframe time of 1.5 ms in the presence of 10

-3

bit error rate

and detects line code violations, loss of signal, framing bit errors, parity errors, Cbit parity errors, far end block errors, AIS, far end receive failure and idle code.

The DS3 framer is an off-line framer, indicating both out of frame (OOF) and

change of frame alignment (COFA) events. The error events (C-BIT, FEBE, etc.)

are still indicated while the framer is OOF, based on the previous frame

alignment. When in C-bit parity mode, the Path Maintenance Data Link and the

Far End Alarm and Control (FEAC) channels are extracted. HDLC receivers are

provided for Path Maintenance Data Link support. In addition, valid bit-oriented

codes in the FEAC channels are detected and are available through the

microprocessor port.

DS3 error event accumulation is also provided by the TEMAP-84. Framing bit

errors, line code violations, excessive zeros occurrences, parity errors, C-bit

PROPRIETARY AND CONFIDENTIAL 24

Page 37

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

parity errors, and far end block errors are accumulated. Error accumulation

continues even while the off-line framers are indicating OOF. The counters are

intended to be polled once per second, and are sized so as not to saturate at a

-3

10

bit error rate. Transfer of count values to holding registers is initiated through

the microprocessor interface.

In the DS3 transmit direction, the TEMAP-84 inserts DS3 framing, X and P bits.

When enabled for C-bit parity operation, bit-oriented code transmitters and

HDLC transmitters are provided for insertion of the FEAC channels and the Path

Maintenance Data Links into the appropriate overhead bits. Alarm Indication

Signals, Far End Receive Failure and idle signal can be inserted using either

internal registers or can be configured for automatic insertion upon received

errors. When M23 operation is selected, the C-bit Parity ID bit (the first C-bit of

the first M sub-frame) is forced to toggle so that downstream equipment will not

confuse an M23-formatted stream with stuck-at-1 C-bits for C-bit Parity

application. Transmit timing is from an external reference or from the receive

direction clock.

The TEMAP-84 also supports diagnostic options which allow it to insert, when

appropriate for the transmit framing format, parity or path parity errors, F-bit

framing errors, M-bit framing errors, invalid X or P-bits, line code violations,

all-zeros, AIS, Remote Alarm Indications, and Remote End Alarms. A Pseudo

Random Binary Sequence (PRBS) can be inserted into a DS3 payload and

checked in the receive DS3 payload for bit errors. A fixed 100100… pattern is

available for insertion directly into the B3ZS encoder for proper pulse mask

shape verification.

The TEMAP-84 may be used as an E3 framer for the transport of framed but

unchannelized E3 data streams complying to the ITU-T Recommendations

G.751 or G.832. The line interface may be configured as either unipolar or

HDB3-encoded.

When configured in DS3 multiplexer mode, seven 6312 kbit/s data streams are

demultiplexed and multiplexed into and out of each DS3 signal. Bit stuffing and

rate adaptation is performed. The C-bits are set appropriately, with the option of

inserting DS2 loopback requests. Interrupts can be generated upon detection of

loopback requests in the received DS3. AIS may be inserted in the any of the

6312 kbit/s tributaries in both the multiplex and demultiplex directions. C-bit

parity is supported by sourcing a 6.3062723 MHz clock, which corresponds to a

stuffing ratio of 100%.

Framing to the demultiplexed 6312 kbit/s data streams supports DS2 (ANSI

TI.107) frame formats. The maximum average reframe time is 7ms for DS2. Far

end receive failure is detected and M-bit and F-bit errors are accumulated. The

DS2 framer is an off-line framer, indicating both OOF and COFA events. Error

PROPRIETARY AND CONFIDENTIAL 25

Page 38

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

events (FERF, MERR, FERR, PERR, RAI, framing word errors) are still indicated

while the DS2 framer is indicating OOF, based on the previous alignment.

Each of the seven 6312 kbit/s multiplexers per DS3 may be independently

configured to multiplex and demultiplex four 1544 kbit/s DS1s or three

2048 kbit/s according to ITU-T Rec. G.747 into and out of a DS2 formatted

signal. Tributary frequency deviations are accommodated using internal FIFOs

and bit stuffing. The C-bits are set appropriately, with the option of inserting DS1

loopback requests. Interrupts can be generated upon detection of loopback

requests in the received DS2. AIS may be inserted in any of the low speed

tributaries in both multiplex and demultiplex directions.

When configured as a DS3 or E3 framer the unchannelized payload of the DS3

and E3 links are available to an external device.

The SONET/SDH line side interface provides STS-1 SPE synchronous payload

envelope processing and generation, TUG3 tributary unit group processing and

generation within a VC4 virtual container and VC3 virtual container processing

and generation. The payload processor aligns and monitors the performance of

SONET virtual tributaries (VTs) or SDH tributary units (TUs). Maintenance

functions per tributary include detection of loss of pointer, AIS alarm, tributary

path signal label mismatch and tributary path signal label unstable alarms.

Optionally interrupts can be generated due to the assertion and removal of any

of the above alarms. Counts are accumulated for tributary path BIP-2 errors on a

block or bit basis and for FEBE indications. The synchronous payload envelope

generator generates all tributary pointers and calculates and inserts tributary

path BIP-2. The generator also inserts FEBE, RDI and enhanced RDI in the V5

byte. Software can force AIS insertion on a per tributary basis.

A SONET/SDH mapper maps and demaps up to 84 T1s, 63 E1s or three DS3s

into three STS-1 SPEs, TUG3s or VC3s through three elastic stores. The fixed

stuff (R) bits are all set to zeros or ones under microprocessor control. The bit

asynchronous demapper performs majority vote C-bit decoding to detect stuff

requests for T1, E1 and DS3 asynchronous mappings. The VT1.5/VT2/TU11/TU-12 mapper uses an elastic store and a jitter attenuator capability to

minimize jitter introduced via bit stuffing.

The TEMAP-84 is configured, controlled and monitored via a generic 8-bit

microprocessor bus through which all internal registers are accessed. All

sources of interrupts can be masked and acknowledged through the

microprocessor interface.

PROPRIETARY AND CONFIDENTIAL 26

Page 39

PRELIMINARY

A

YAAA

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

7 PIN DIAGRAM

The TEMAP-84 is packaged in a 324-pin PBGA package having a body size of

23mm by 23mm and a ball pitch of 1.0 mm. The center 36 balls are not used as

signal I/Os and are thermal balls. Pin names and locations are defined in the Pin

Description Table in section 8. Mechanical information for this package is in the

section 19.

Figure 6 - Pin Diagram

22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

B

C

M

N

R

U

W

D

E

F

G

324 PBGA

H

J

K

L

P

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS

Bottom View

T

V

B

22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

PROPRIETARY AND CONFIDENTIAL 27

Page 40

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

8 PIN DESCRIPTION

Pin Name Type Pin

No.

DS3 and E3 Line Side Interface

RCLK[3]

RCLK[2]

RCLK[1]

RPOS/RDAT[3]

RPOS/RDAT[2]

RPOS/RDAT[1]

Input P1

T1

Y1

Input P2

U1

V3

Function

Receive Input Clocks (RCLK[3:1]). RCLK[3:1]

provide the receive direction timing for the three DS3s

or E3s. RCLK[3:1] are nominally 44.736 MHz or

34.368 MHz, 50% duty cycle clock inputs.

Positive Input Pulse (RPOS[3:1]). RPOS[3:1]

represent the positive pulses received on the B3ZSencoded DS3s or HDB3-encoded E3s when dual rail

input format is selected.

Receive Data Input (RDAT[3:1]). RDAT[3:1]

represent the NRZ (unipolar) DS3 or E3 input data

streams when single rail input format is selected.

RPOS[3:1] and RDAT[3:1] are sampled on the rising

edge of the associated RCLK by default and may be

enabled to be sampled on the falling edge of the

associated RCLK by setting the RFALL bit in the

DS3/E3 Master Receive Line Options register.

RNEG/RLCV[3]

RNEG/RLCV[2]

RNEG/RLCV[1]

TCLK[3]

TCLK[2]

TCLK[1]

Input P3

T3

W2

Output R3

V1

W3

Negative Input Pulse (RNEG[3:1]). RNEG[3:1]

represent the negative pulses received on the B3ZSencoded DS3s or HDB3-encoded E3s when dual rail

input format is selected.

Line code violation (RLCV[3:1]). RLCV[3:1]

represent receive line code violations when single rail

input format is selected.

RNEG[3:1] and RLCV[3:1] are sampled on the rising

edge of the associated RCLK by default and may be

enabled to be sampled on the falling edge of RCLK by

setting the RFALL bit in the DS3/E3 Master Receive

Line Options register.

Transmit Clock (TCLK[3:1]). TCLK[3:1] provide

timing for circuitry downstream of the DS3 and E3

transmitters of the TEMAP-84. TCLK[3:1] are

nominally 44.736 MHz or 34.368 MHz, 50% duty cycle

clocks.

PROPRIETARY AND CONFIDENTIAL 28

Page 41

PRELIMINARY

DATASHEET

PMC-2010672 ISSUE 1 HIGH DENSITY 84/63 CHANNEL VT/TU MAPPER

PM5366 TEMAP-84

AND M13 MULTIPLEXER

Pin Name Type Pin

No.

TPOS/TDAT[3]

TPOS/TDAT[2]

TPOS/TDAT[1]

TNEG/TMFP[3]

TNEG/TMFP[2]

TNEG/TMFP[1]

Output R2

U2

AA1

Output U4

W1

AB1

Function

Transmit Positive Pulse (TPOS[3:1]). TPOS[3:1]