STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

PM5365

TEMAP

VT/TU MAPPER AND M13 MULTIPLEXER

DATA SHEET

PROPRIETARY AND CONFIDENTIAL

RELEASED

ISSUE 3: SEPTEMBER 2001

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use i

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS...................................................................................... 11

3 REFERENCES .......................................................................................12

4 APPLICATION EXAMPLES....................................................................16

5 BLOCK DIAGRAM..................................................................................17

5.1 TOP LEVEL BLOCK DIAGRAM...................................................17

5.2 VT/TU MAPPER ONLY MODE BLOCK DIAGRAM......................19

5.3 DS3 FRAMER ONLY BLOCK DIAGRAM.....................................20

6 DESCRIPTION .......................................................................................21

7 PIN DIAGRAM ........................................................................................25

8 PIN DESCRIPTION ................................................................................26

9 FUNCTIONAL DESCRIPTION ...............................................................57

9.1 T1 FRAMER (T1-FRMR)..............................................................57

9.2 E1 FRAMER (E1-FRMR) .............................................................57

9.3 PERFORMANCE MONITOR COUNTERS (T1/E1-PMON) .........64

9.4 T1 ALARM INTEGRATOR (ALMI)................................................65

9.5 RECEIVE AND TRANSMIT DIGITAL JITTER ATTENUATOR (RJAT,

TJAT) ...........................................................................................65

9.6 TIMING OPTIONS (TOPS) ..........................................................72

9.7 PSEUDO RANDOM BINARY SEQUENCE GENERATION AND

DETECTION (PRBS) ...................................................................73

9.8 PSEUDO RANDOM PATTERN GENERATION AND DETECTION

(PRGD) ........................................................................................73

9.9 DS3 FRAMER (DS3-FRMR) ........................................................73

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use ii

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

9.10 PERFORMANCE MONITOR ACCUMULATOR (DS3-PMON) .....76

9.11 DS3 TRANSMITTER (DS3-TRAN) ..............................................76

9.12 M23 MULTIPLEXER (MX23)........................................................77

9.13 DS2 FRAMER (DS2-FRMR) ........................................................78

9.14 M12 MULTIPLEXER (MX12)........................................................80

9.15 TRIBUTARY PAYLOAD PROCESSOR (VTPP)...........................81

9.15.1 CLOCK GENERATOR.......................................................81

9.15.2 INCOMING TIMING GENERATOR ...................................81

9.15.3 INCOMING MULTIFRAME DETECTOR ...........................82

9.15.4 POINTER INTERPRETER................................................82

9.15.5 PAYLOAD BUFFER...........................................................82

9.15.6 OUTGOING TIMING GENERATOR..................................82

9.15.7 POINTER GENERATOR ...................................................83

9.16 RECEIVE TRIBUTARY PATH OVERHEAD PROCESSOR (RTOP)

.....................................................................................................84

9.16.1 CLOCK GENERATOR.......................................................84

9.16.2 TIMING GENERATOR ......................................................84

9.16.3 ERROR MONITOR............................................................84

9.17 RECEIVE TRIBUTARY DEMAPPER (RTDM)..............................86

9.18 PARALLEL IN TO SERIAL OUT CONVERTER (PISO) ...............88

9.19 DS3 MAPPER DROP SIDE (D3MD)............................................89

9.19.1 DS3 DEMAPPER ..............................................................90

9.19.2 DS3 DEMAPPER ELASTIC STORE .................................91

9.19.3 DS3 DESYNCHRONIZER.................................................91

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use iii

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

9.20 TRANSMIT TRIBUTARY PATH OVERHEAD PROCESSOR (TTOP)92

9.21 TRANSMIT REMOTE ALARM PROCESSOR (TRAP) ................93

9.22 TRANSMIT TRIBUTARY MAPPER (TTMP).................................94

9.23 SERIAL IN TO PARALLEL OUT CONVERTER (SIPO) ...............95

9.24 DS3 MAPPER ADD SIDE (D3MA)...............................................95

9.24.1 DS3 MAPPER SERIALIZER .............................................96

9.24.2 DS3 MAPPER ELASTIC STORE ......................................96

9.24.3 DS3 SYNCHRONIZER......................................................96

9.25 EGRESS SYSTEM INTERFACE (ESIF)......................................97

9.26 INGRESS SYSTEM INTERFACE (ISIF) ......................................98

9.27 EXTRACT SCALEABLE BANDWIDTH INTERCONNECT (EXSBI)

.....................................................................................................99

9.28 INSERT SCALEABLE BANDWIDTH INTERCONNECT (INSBI)100

9.29 SCALEABLE BANDWIDTH INTERCONNECT PISO (SBIPISO)100

9.30 SCALEABLE BANDWIDTH INTERCONNECT SIPO (SBISIPO)101

9.31 JTAG TEST ACCESS PORT......................................................101

9.32 MICROPROCESSOR INTERFACE ...........................................101

10 NORMAL MODE REGISTER DESCRIPTION......................................127

11 TEST FEATURES DESCRIPTION .......................................................128

11.1 JTAG TEST PORT.....................................................................136

11.1.1 BOUNDARY SCAN REGISTER......................................137

12 OPERATION.........................................................................................148

12.1 DS3 FRAME FORMAT...............................................................148

12.2 SERVICING INTERRUPTS .......................................................150

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use iv

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

12.3 USING THE PERFORMANCE MONITORING FEATURES.......150

12.4 T1/E1 FRAMER LOOPBACK MODES ......................................155

12.5 DS3 LOOPBACK MODES .........................................................157

12.6 TELECOM BUS MAPPER/DEMAPPER LOOPBACK MODES .160

12.7 SBI BUS DATA FORMATS.........................................................161

12.8 SERIAL CLOCK AND DATA FORMAT .......................................176

12.9 PRGD PATTERN GENERATION...............................................176

12.10 JTAG SUPPORT........................................................................179

12.10.1 TAP CONTROLLER ...................................................181

13 FUNCTIONAL TIMING .........................................................................188

13.1 DS3 LINE SIDE INTERFACE TIMING .......................................188

13.2 DS3 SYSTEM SIDE INTERFACE TIMING ................................190

13.3 TELECOM DROP BUS INTERFACE TIMING ...........................191

13.4 TELECOM ADD BUS INTERFACE TIMING ..............................194

13.5 SONET/SDH SERIAL ALARM PORT TIMING ...........................196

13.6 SBI DROP BUS INTERFACE TIMING .......................................198

13.7 SBI ADD BUS INTERFACE TIMING..........................................199

13.8 EGRESS SERIAL CLOCK AND DATA INTERFACE TIMING ....199

13.9 INGRESS SERIAL CLOCK AND DATA INTERFACE TIMING ...200

14 ABSOLUTE MAXIMUM RATINGS........................................................201

15 D.C. CHARACTERISTICS....................................................................202

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS......205

17 TEMAP TIMING CHARACTERISTICS .................................................209

18 ORDERING AND THERMAL INFORMATION ......................................231

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use v

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

19 MECHANICAL INFORMATION.............................................................232

FIGURES

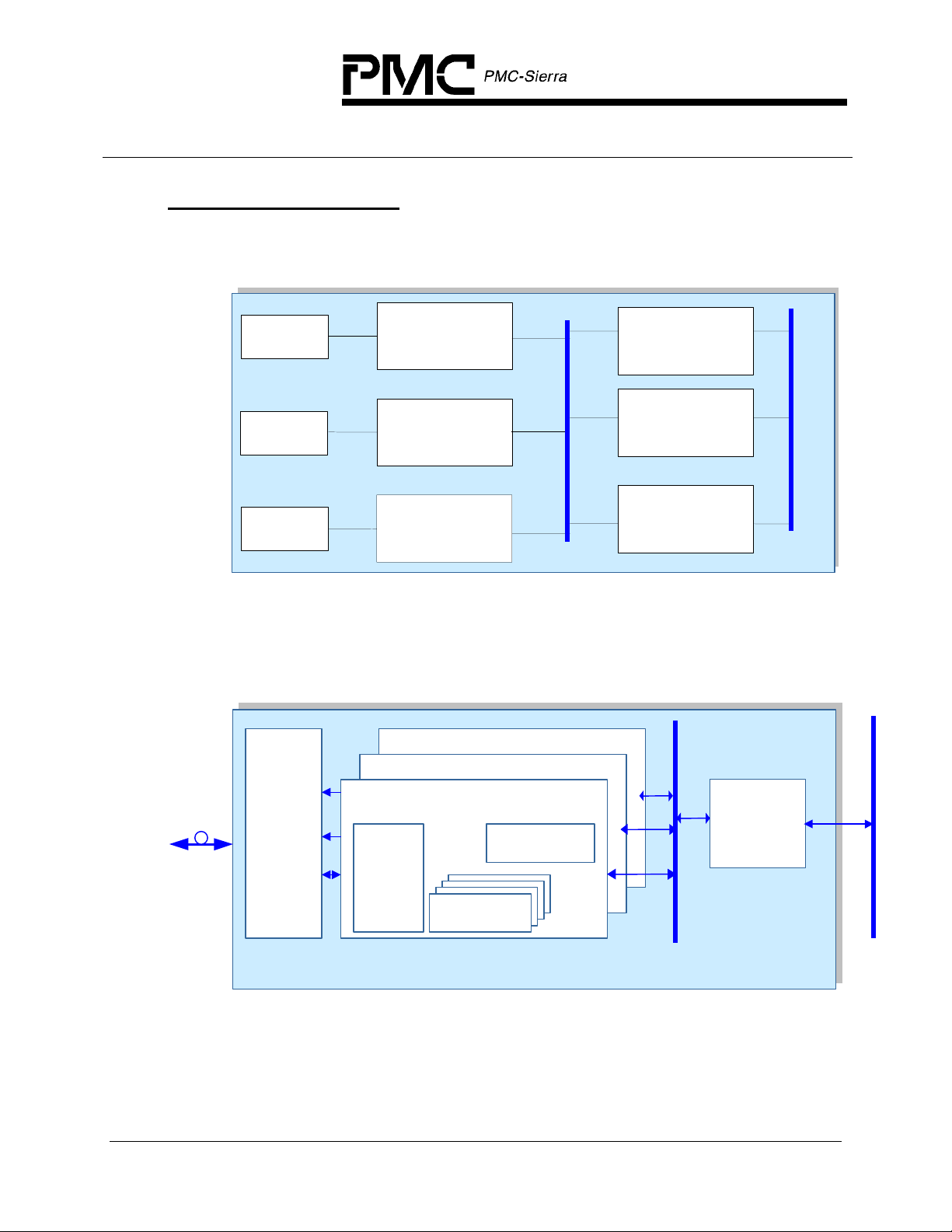

FIGURE 1 - CHANNELIZED DS3 CIRCUIT EMULATION APPLICATION.......16

FIGURE 2 - HIGH DENSITY FRAME RELAY APPLICATION ..........................16

FIGURE 3 - TEMAP BLOCK DIAGRAM ..........................................................18

FIGURE 4 - VT/TU MAPPER BLOCK DIAGRAM ............................................19

FIGURE 5 - DS3 FRAMER ONLY MODE BLOCK DIAGRAM .........................20

FIGURE 6 - PIN DIAGRAM..............................................................................25

FIGURE 7 - CRC MULTIFRAME ALIGNMENT ALGORITHM ..........................61

FIGURE 8 - DJAT JITTER TOLERANCE T1 MODES......................................68

FIGURE 9 - DJAT JITTER TOLERANCE E1 MODES .....................................69

FIGURE 10 - DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY T1

MODES 70

FIGURE 11 - DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY E1

MODES 70

FIGURE 12 - DJAT JITTER TRANSFER T1 MODES ........................................71

FIGURE 13 - DJAT JITTER TRANSFER E1 MODES........................................72

FIGURE 14 - CLOCK MASTER: CLEAR CHANNEL .........................................98

FIGURE 15 - CLOCK SLAVE: CLEAR CHANNEL .............................................98

FIGURE 16 - CLOCK MASTER: CLEAR CHANNEL .........................................99

FIGURE 17: DS3 FRAME STRUCTURE ........................................................148

FIGURE 18 - FER COUNT VS. BER (E1 MODE)............................................152

FIGURE 19 - CRCE COUNT VS. BER (E1 MODE) .........................................153

FIGURE 20 - FER COUNT VS. BER (T1 ESF MODE) ....................................153

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use vi

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

FIGURE 21 - CRCE COUNT VS. BER (T1 ESF MODE) .................................154

FIGURE 22 - CRCE COUNT VS. BER (T1 SF MODE)....................................155

FIGURE 23: T1/E1 LINE LOOPBACK.............................................................156

FIGURE 24: T1/E1 DIAGNOSTIC DIGITAL LOOPBACK................................157

FIGURE 25: DS3 DIAGNOSTIC LOOPBACK DIAGRAM ...............................158

FIGURE 26: DS3 LINE LOOPBACK DIAGRAM..............................................159

FIGURE 27: DS2 LOOPBACK DIAGRAM.......................................................159

FIGURE 28: TELECOM DIAGNOSTIC LOOPBACK DIAGRAM.....................160

FIGURE 29: TELECOM LINE LOOPBACK DIAGRAM ...................................161

FIGURE 30: PRGD PATTERN GENERATOR .................................................176

FIGURE 31: BOUNDARY SCAN ARCHITECTURE ........................................180

FIGURE 32: TAP CONTROLLER FINITE STATE MACHINE..........................182

FIGURE 33: INPUT OBSERVATION CELL (IN_CELL) ...................................185

FIGURE 34: OUTPUT CELL (OUT_CELL) .....................................................186

FIGURE 35: BIDIRECTIONAL CELL (IO_CELL).............................................186

FIGURE 36: LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS 187

FIGURE 37: RECEIVE BIPOLAR DS3 STREAM............................................188

FIGURE 38: RECEIVE UNIPOLAR DS3 STREAM .........................................188

FIGURE 39: TRANSMIT BIPOLAR DS3 STREAM .........................................189

FIGURE 40: TRANSMIT UNIPOLAR DS3 STREAM.......................................189

FIGURE 41: FRAMER MODE DS3 TRANSMIT INPUT STREAM ..................190

FIGURE 42: FRAMER MODE DS3 TRANSMIT INPUT STREAM WITH

TGAPCLK 190

FIGURE 43: FRAMER MODE DS3 RECEIVE OUTPUT STREAM.................191

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use vii

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

FIGURE 44: FRAMER MODE DS3 RECEIVE OUTPUT STREAM WITH

RGAPCLK 191

FIGURE 45: TELECOM DROP BUS TIMING - STS-1 SPES / AU3 VCS........192

FIGURE 46: TELECOM DROP BUS TIMING - LOCKED STS-1 SPES / AU3 VCS

193

FIGURE 47: TELECOM DROP BUS TIMING - AU4 VC..................................194

FIGURE 48: OUTPUT BUS TIMING - LOCKED STS-1 SPES / AU3 VCS......195

FIGURE 49 - OUTPUT BUS TIMING - LOCKED AU4 VC CASE.....................196

FIGURE 50: REMOTE SERIAL ALARM PORT TIMING..................................197

FIGURE 51: SBI DROP BUS T1/E1 FUNCTIONAL TIMING...........................198

FIGURE 52: SBI DROP BUS DS3 FUNCTIONAL TIMING .............................198

FIGURE 53: SBI ADD BUS JUSTIFICATION REQUEST FUNCTIONAL TIMING

199

FIGURE 54: T1 AND E1 EGRESS INTERFACE CLOCK MASTER: CLEAR

CHANNEL MODE............................................................................................199

FIGURE 55: T1 AND E1 EGRESS INTERFACE CLOCK SLAVE: CLEAR

CHANNEL MODE............................................................................................200

FIGURE 56: T1 AND E1 INGRESS INTERFACE CLOCK MASTER: CLEAR

CHANNEL MODE............................................................................................200

FIGURE 57: DS3 TRANSMIT INTERFACE TIMING ....................................... 211

FIGURE 58: DS3 RECEIVE INTERFACE TIMING..........................................214

FIGURE 59: LINE SIDE TELECOM BUS INPUTTIMING................................216

FIGURE 60: TELECOM BUS OUTPUT TIMING .............................................217

FIGURE 61: TELECOM BUS TRISTATE OUTPUT TIMING ...........................217

FIGURE 62: SBI ADD BUS TIMING................................................................219

FIGURE 63: SBI DROP BUS TIMING.............................................................220

FIGURE 64: SBI DROP BUS COLLISION AVOIDANCE TIMING ...................221

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use viii

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

FIGURE 65: XCLK INPUT TIMING .................................................................222

FIGURE 66: EGRESS INTERFACE INPUT TIMING - CLOCK MASTER : CLEAR

CHANNEL MODE............................................................................................223

FIGURE 67: EGRESS INTERFACE INPUT TIMING - CLOCK SLAVE : CLEAR

CHANNEL MODE............................................................................................224

FIGURE 68: INGRESS INTERFACE TIMING - CLOCK MASTER MODES....225

FIGURE 69: TRANSMIT LINE INTERFACE TIMING ......................................226

FIGURE 70: REMOTE SERIAL ALARM PORT TIMING..................................228

FIGURE 71: JTAG PORT INTERFACE TIMING..............................................230

FIGURE 72: 324 PIN PBGA 23X23MM BODY................................................232

TABL ES

TABLE 1 - E1-FRMR FRAMING STATES......................................................62

TABLE 2 - PATH SIGNAL LABEL MISMATCH STATE ..................................85

TABLE 3 - ASYNCHRONOUS T1 TRIBUTARY MAPPING............................86

TABLE 4 - ASYNCHRONOUS E1 TRIBUTARY MAPPING ...........................87

TABLE 5 - DESYNCHRONIZER CLOCK GENERATION ALGORITHM ........89

TABLE 6 - ASYNCHRONOUS DS3 MAPPING TO STS-1 (STM-0/AU3).......90

TABLE 7 - DS3 AIS FORMAT. .......................................................................90

TABLE 8 - DS3 DESYNCHRONIZER CLOCK GAPPING ALGORITHM. ......92

TABLE 9 - DS3 SYNCHRONIZER BIT STUFFING ALGORITHM. ................97

TABLE 10 - REGISTER MEMORY MAP .......................................................102

TABLE 11 - INSTRUCTION REGISTER........................................................136

TABLE 12 - IDENTIFICATION REGISTER ....................................................137

TABLE 13 - BOUNDARY SCAN CHAIN ........................................................137

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use ix

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

TABLE 14 - PMON COUNTER SATURATION LIMITS (E1 MODE) ..............151

TABLE 15 - PMON COUNTER SATURATION LIMITS (T1 MODE)...............151

TABLE 16 - STRUCTURE FOR CARRYING MULTIPLEXED LINKS ............163

TABLE 17 – T1/TVT1.5 TRIBUTARY COLUMN NUMBERING......................163

TABLE 18 - E1/TVT2 TRIBUTARY COLUMN NUMBERING .........................164

TABLE 19: SBI T1/E1 LINK RATE INFORMATION.........................................165

TABLE 20: SBI T1/E1 CLOCK RATE ENCODING ..........................................166

TABLE 21: DS3 LINK RATE INFORMATION ..................................................166

TABLE 22: DS3 CLOCK RATE ENCODING ...................................................167

TABLE 23 - T1 FRAMING FORMAT ..............................................................168

TABLE 24 – E1 FRAMING FORMAT.............................................................169

TABLE 25 - DS3 FRAMING FORMAT ...........................................................171

TABLE 26 - DS3 BLOCK FORMAT ...............................................................172

TABLE 27 - DS3 MULTI-FRAME STUFFING FORMAT.................................172

TABLE 28 - TRANSPARENT VT1.5/TU11 FORMAT .....................................173

TABLE 29 – TRANSPARENT VT2/TU12 FORMAT .......................................175

TABLE 30: PSEUDO RANDOM PATTERN GENERATION (PS BIT = 0)........178

TABLE 31: REPETITIVE PATTERN GENERATION (PS BIT = 1)...................179

TABLE 32 - ABSOLUTE MAXIMUM RATINGS..............................................201

TABLE 33 - D.C. CHARACTERISTICS .........................................................202

TABLE 34: MICROPROCESSOR INTERFACE READ ACCESS ....................205

TABLE 35: MICROPROCESSOR INTERFACE WRITE ACCESS ..................207

TABLE 36: RTSB TIMING ...............................................................................209

TABLE 37: DS3 TRANSMIT INTERFACE TIMING..........................................209

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use x

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

TABLE 38: DS3 RECEIVE INTERFACE TIMING ............................................213

TABLE 39: LINE SIDE TELECOM BUS INPUT TIMING (FIGURE 62) ...........215

TABLE 40 – TELECOM BUS OUTPUT TIMING (FIGURE 63 TO FIGURE 64)216

TABLE 41: SBI ADD BUS TIMING (FIGURE 62) ............................................218

TABLE 42 – SBI DROP BUS TIMING (FIGURE 63 TO FIGURE 64) ..............219

TABLE 43: XCLK INPUT (FIGURE 65) ...........................................................222

TABLE 44: EGRESS INTERFACE INPUT TIMING - CLOCK MASTER : CLEAR

CHANNEL MODE (FIGURE 66)......................................................................223

TABLE 45: EGRESS INTERFACE INPUT TIMING - CLOCK SLAVE : CLEAR

CHANNEL MODE (FIGURE 67)......................................................................224

TABLE 46: INGRESS INTERFACE TIMING - CLOCK MASTER MODES

(FIGURE 68)....................................................................................................225

TABLE 47: TRANSMIT LINE INTERFACE TIMING (FIGURE 69)...................226

TABLE 48: REMOTE SERIAL ALARM PORT TIMING....................................227

TABLE 49: JTAG PORT INTERFACE .............................................................229

TABLE 50 - ORDERING AND THERMAL INFORMATION ............................231

TABLE 51 - THERMAL INFORMATION – THETA JA VS. AIRFLOW.............231

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use xi

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

1 FEATURES

· Integrates a SONET/SDH VT1.5/VT2/TU11/TU12 bit asynchronous mapper,

a full featured M13 multiplexer with DS3 framer, and a SONET/SDH DS3

mapper in a single monolithic device for terminating DS3 multiplexed T1

streams, SONET/SDH mapped T1 streams or SONET/SDH mapped E1

streams.

· Five fundamental modes of operation:

· Single STS-1, AU3 or TUG3 Bit Asynchronous VT1.5 or TU-11 Mapper

with ingress or egress per tributary link monitoring for 28 T1s.

· DS3 M13 Multiplexer with ingress or egress per link monitoring for 28 T1s.

· Up to 28 DS3 multiplexed T1 streams are mapped as bit asynchronous

VT1.5 virtual tributaries or TU-11 tributary units, providing a

transmultiplexing (“transmux”) function between DS3 and SONET/SDH

with ingress or egress per tributary link monitoring for 28 T1s.

· Single STS-1, AU3 or TUG3 Bit Asynchronous VT2 or TU-12 Mapper with

ingress or egress per tributary link monitoring for 21 E1s or 21 T1s.

· Up to 21 E1 streams multiplexed into a DS3 following the ITU-T G.747

recommendation. This E1 mode of operation is restricted to using the

serial clock and data system interfaces.

· Up to 28 VT1.5/TU11 or 21 VT2/TU12 tributaries can be passed between the

line SONET/SDH bus and the SBI bus as transparent virtual tributaries with

pointer processing.

· When adding and dropping T1 or E1 tributaries the mapper and demapper

blocks allow for up to 28 VT1.5/TU11 or 21 VT2/TU12 tributaries to be

processed from any tributary location within the full STS-3/STM-1. On the

telecom DROP bus side this requires that the STS-3/STM-1 be in locked

mode such that the J1 bytes immediately follow the C1 bytes.

· Supports a byte serial Scaleable Bandwidth Interconnect (SBI) bus interface

for high density system side device interconnection of up to 84 T1 streams,

63 E1 streams or 3 DS3 streams. This interface also supports transparent

virtual tributaries when used with the SONET/SDH mapper.

· Provides jitter attenuation in the T1 or E1 receive and transmit directions.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 1

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Provides two independent de-jittered T1 or E1 recovered clocks for system

timing and redundancy.

· Provides an on-board programmable binary sequence generator and detector

for error testing at DS3 rates. Includes support for patterns recommended in

ITU-T O.151.

· Also provides PRBS generators and detectors on each tributary for error

testing at DS1, E1 and NxDS0 rates as recommended in ITU-T O.151 and

O.152.

· Supports the M23 and C-bit parity DS3 formats.

· Standalone unchannelized DS3 framer mode for access to the entire DS3

payload.

· When configured to operate as a DS3 Framer, gapped transmit and receive

clocks can be optionally generated for interface to link layer devices which

only need access to payload data bits.

· DS3 Transmit clock source can be selected from either an external oscillator

or from the receive side clock (loop-timed).

· Provides a SONET/SDH Add/Drop bus interface with integrated VT1.5, TU11, VT2 and TU-12 mapper for T1and E1 streams. Also provides a DS3

mapper.

· Register level compatibility with the PM8315 TEMUX, the PM4388 TOCTL

Octal T1 Framer, the PM6388 EOCTL Octal E1 Framer, the PM4351 COMET

E1/T1 transceiver and the PM8313 D3MX M13 Multiplexer/Demultiplexer.

· Provides a generic 8-bit microprocessor bus interface for configuration,

control and status monitoring.

· Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

test purposes.

· Low power 2.5V/3.3V CMOS technology. All pins are 5V tolerant.

· 324-pin fine pitch PBGA package (23mm x 23mm). Supports industrial

temperature range (-40oC to 85oC) operation.

Each one of 28 T1 performance monitoring sections:

· Frames to DS-1 signals in SF and ESF formats.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 2

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Frames to TTC JT-G.704 multiframe formatted J1 signals. Supports the

alternate CRC-6 calculation for Japanese applications.

· Accepts gapped data streams to support higher rate demultiplexing.

· Provides Red, Yellow, and AIS alarm integration.

· Provides performance monitoring counters sufficiently large as to allow

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the performance monitoring counters and interrupts the

microprocessor once per second, timed to the receive line.

· A pseudo-random sequence user selectable from 211 –1, 215 –1 or220 –1, may

be detected in the T1 stream in either the ingress or egress directions. The

detector counts pattern errors using a 24-bit non-saturating PRBS error

counter. The pseudo-random sequence can be the entire T1 or any

combination of DS0s within a framed T1.

· Line side interface is either from the DS3 interface via the M13 multiplex or

from the SONET/SDH Drop bus via the VT1.5, TU-11, VT2 or TU-12

demapper.

· System side interface is either serial clock and data or SBI bus.

· Frames in the presence of and detects the “Japanese Yellow” alarm.

· Provides external access for up to two de-jittered recovered T1 clocks.

Each one of 21 E1 performance monitoring sections:

· Frames to ITU-T G.704 basic and CRC-4 multiframe formatted E1 signals.

The framing procedures are consistent ITU-T G.706 specifications.

· Provides performance monitoring counters sufficiently large as to allow

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the performance monitoring counters and interrupts the

microprocessor once per second, timed to the receive line.

· A pseudo-random sequence user selectable from 211 –1, 215 –1 or220 –1, may

be detected in the E1 stream in either the ingress or egress directions. The

detector counts pattern errors using a 24-bit non-saturating PRBS error

counter. The pseudo-random sequence can be the entire E1 or any

combination of timeslots within the framed E1.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 3

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Line side interface is from the SONET/SDH Drop bus via the VT2 or TU-12

demapper.

· System side interface is either serial clock and data or SBI bus.

· Provides external access for up to two de-jittered recovered E1 clocks.

SONET/SDH Tributary Path Processing Section:

· Interfaces with a byte wide Telecom Add/Drop bus, interfacing directly with

the PM5362 TUPP-PLUS and PM5342 SPECTRA-155.

· Compensates for pleisiochronous relationships between incoming and

outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope

frame rates through processing of the lower level tributary pointers.

· Optionally frames to the H4 byte in the path overhead to determine tributary

multi-frame boundaries and generates change of loss-of-frame status

interrupts.

· Detects loss of pointer (LOP) and re-acquisition for each tributary and

optionally generates interrupts.

· Detects tributary path alarm indication signal (AIS) and return to normal state

for each tributary and optionally generates interrupts

· Detects tributary elastic store underflow and overflow and optionally

generates interrupts.

· Provides individual tributary path signal label register that hold the expected

label and detects tributary path signal label mismatch alarms (PSLM) and

return to matched state for each tributary and optionally generates interrupts.

· Detects tributary path signal label unstable alarms (PSLU) and return to

stable state for each tributary and optionally generates interrupts.

· Detects assertion and removal of tributary extended remote defect indications

(RDI) for each tributary and optionally generates interrupts.

· Calculates and compares the tributary path BIP-2 error detection code for

each tributary and configurable to accumulate the BIP-2 errors on block or bit

basis in internal registers.

· Allows insertion of all-zeros or all-ones tributary idle code with unequipped

indication and valid pointer into any tributary under SW control.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 4

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Allows SW to force the AIS insertion on a per tributary basis.

· Inserts valid H4 byte and all-zeros fixed stuff bytes. Remaining path overhead

bytes (J1, B3, C2,G1, F2, Z3, Z4, Z5) are set to all-zeros.

· Inserts valid pointers and all-zeros transport overhead bytes on the outgoing

telecom Add bus, with valid control signals.

· Support in-band error reporting by updating the FEBE, RDI and auxiliary RDI

bits in the V5 byte with the status of the incoming stream and remote alarm

pins.

· Calculates and inserts the tributary path BIP-2 error detection code for each

tributary.

SONET/SDH VT/TU Mapper Section:

· Inserts up to 28 bit asynchronous mapped VT1.5 virtual tributaries into an

STS-1 SPE from T1 streams.

· Inserts up to 28 bit asynchronous mapped TU-11 tributary units into a STM1/VC4 TUG3 or STM-1/VC3 from T1 streams.

· Inserts up to 21 bit asynchronous mapped VT2 virtual tributaries into an STS1 SPE from E1 streams.

· Inserts up to 21 bit asynchronous mapped TU-12 tributary units into an STM1/VC4 TUG3 or STM-1/VC3 from E1 or T1 streams.

· Bit asynchronous mapping assigns stuff control bits for all streams

independently using an all digital control loop. Stuff control bits are dithered to

produce fractional mapping jitter at the receiving desynchronizer.

· Sets all fixed stuff bits for asynchronous mappings to zeros or ones per

microprocessor control

· Extracts up to 28 bit asynchronous mapped VT1.5 virtual tributaries from an

STS-1 SPE into T1 streams via an optional elastic store.

· Extracts up to 28 bit asynchronous mapped TU-11 tributary units from an

STM-1/VC4 TUG3 or STM-1/VC3 into T1 streams via an optional elastic

store.

· Extracts up to 21 bit asynchronous mapped VT2 virtual tributaries from an

STS-1 SPE into E1 streams via an optional elastic store.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 5

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Extracts up to 21 bit asynchronous mapped TU-12 tributary units from an

STM-1/VC4 TUG3 or STM-1/VC3 into E1 or T1 streams via an optional

elastic store.

· Demapper ignores all transport overhead bytes, path overhead bytes and

stuff (R) bits

· Performs majority vote C-bit decoding to detect stuff requests.

SONET/SDH DS3 Mapper Section:

· Maps a DS3 stream into an STS-1 SPE (AU3).

· Sets all fixed stuff (R) bits to zeros or ones per microprocessor control

· Extracts a DS3 stream from an STS-1 SPE (AU3).

· Demapper ignores all transport overhead bytes, path overhead bytes and

stuff (R) bits

· Performs majority vote C-bit decoding to detect stuff requests

· Complies with DS3 to STS-1 asynchronous mapping standards

DS3 Receiver Section:

· Frames to a DS3 signal with a maximum average reframe time of less than

1.5 ms (as required by TR-TSY-000009 Section 4.1.2 and TR-TSY-000191

Section 5.2).

· Decodes a B3ZS-encoded signal and indicates line code violations. The

definition of line code violation is software selectable.

· Provides indication of M-frame boundaries from which M-subframe

boundaries and overhead bit positions in the DS3 stream can be determined

by external processing.

· Detects the DS3 alarm indication signal (AIS) and idle signal. Detection

-3

algorithms operate correctly in the presence of a 10

bit error rate.

· Accumulates up to 65,535 line code violation (LCV) events per second,

65,535 P-bit parity error events per second, 1023 F-bit or M-bit (framing bit)

events per second, 65,535 excessive zero (EXZ) events per second, and

when enabled for C-bit parity mode operation, up to 16,383 C-bit parity error

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 6

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

events per second, and 16,383 far end block error (FEBE) events per

second.

· Detects and validates bit-oriented codes in the C-bit parity far end alarm and

control channel.

· Terminates the C-bit parity path maintenance data link with an integral HDLC

receiver having a 128-byte deep FIFO buffer with programmable interrupt

threshold. Supports polled or interrupt-driven operation. Selectable none,

one or two address match detection on first byte of received packet.

· Programmable pseudo-random test-sequence detection–(up to 2

32

-1 bit

length patterns conforming to ITU-T O.151 standards) and analysis features.

DS3 Transmit Section:

· Provides the overhead bit insertion for a DS3 stream.

· Provides a bit serial clock and data interface, and allows the M-frame

boundary and/or the overhead bit positions to be located via an external

interface

· Provides B3ZS encoding.

· Generates an B3Zs encoded 100… repeating pattern to aid in pulse mask

testing.

· Inserts far end receive failure (FERF), the DS3 alarm indication signal (AIS)

and the idle signal when enabled by internal register bits.

· Provides optional automatic insertion of far end receive failure (FERF) on

detection of loss of signal (LOS), out of frame (OOF), alarm indication signal

(AIS) or red alarm condition.

· Provides diagnostic features to allow the generation of line code violation

error events, parity error events, framing bit error events, and when enabled

for the C-bit parity application, C-bit parity error events, and far end block

error (FEBE) events.

· Supports insertion of bit-oriented codes in the C-bit parity far end alarm and

control channel.

· Optionally inserts the C-bit parity path maintenance data link with an integral

HDLC transmitter. Supports polled and interrupt-driven operation.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 7

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Provides programmable pseudo-random test sequence generation (up to

232-1 bit length sequences conforming to ITU-T O.151 standards) or any

repeating pattern up to 32 bits. The test pattern can be framed or unframed.

Diagnostic abilities include single bit error insertion or error insertion at bit

error rates ranging from 10-1 to 10-7.

M23 Multiplexer Section:

· Multiplexes 7 DS2 bit streams into a single M23 format DS3 bit stream.

· Performs required bit stuffing/destuffing including generation and

interpretation of C-bits.

· Includes required FIFO buffers for rate adaptation in the multiplex path.

· Allows insertion and detection of per DS2 payload loopback requests

encoded in the C-bits to be activated under microprocessor control.

· Internally generates DS2 clock for use in integrated M13 or C-bit parity

multiplex applications. Alternatively accepts external DS2 clock reference.

· Allows per DS2 alarm indication signal (AIS) to be activated or cleared for

either direction under microprocessor control.

· Allows DS2 alarm indication signal (AIS) to be activated or cleared in the

demultiplex direction automatically upon loss of DS3 frame alignment or

signal.

· Supports C-bit parity DS3 format.

DS2 Framer Section:

· Frames to a DS2 (ANSI T1.107 section 8) signal with a maximum average

reframe time of less than 7 ms (as required by TR-TSY-000009 Section 4.1.2

and TR-TSY-000191 Section 5.2).

· Detects the DS2 alarm indication signal (AIS) in 9.9 ms in the presence of a

10-3 bit error rate.

· Extracts the DS2 X-bit remote alarm indication (RAI) bit and indicates far end

receive failure (FERF).

· Accumulates up to 255 DS2 M-bit or F-bit error events per second.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 8

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

DS2 Transmitter Section:

· Generates the required X, F, and M bits into the transmitted DS2 bit stream.

Allows inversion of inserted F or M bits for diagnostic purposes.

· Provides for transmission of far end receive failure (FERF) and alarm

indication signal (AIS) under microprocessor control.

· Provides optional automatic insertion of far end receive failure (FERF) on

detection of out of frame (OOF), alarm indication signal (AIS) or red alarm

condition.

M12 Multiplexer Section:

· Multiplexes four DS1 bit streams into a single M12 format DS2 bit stream.

· Performs required bit stuffing including generation and interpretation of C-

bits.

· Includes required FIFO buffers for rate adaptation in the multiplex path.

· Performs required inversion of second and fourth multiplexed DS1 streams

as required by ANSI T1.107 Section 7.2.

· Allows insertion and detection of per DS1 payload loopback requests

encoded in the C-bits to be activated under microprocessor control.

· Allows per tributary alarm indication signal (AIS) to be activated or cleared for

either direction under microprocessor control.

· Allows automatic tributary AIS to be activated upon DS2 out of frame.

Scaleable Bandwidth Interconnect (SBI) Bus:

· Provides a high density byte serial interconnect for all framed and unframed

TEMAP links. Utilizes an Add/Drop configuration to asynchronously mutliplex

up to 84 T1s, 63 E1s or 3 DS3s, equivalent to three TEMAPs, with multiple

payload or link layer processors.

· External devices can access unframed DS3, framed unchannelized DS3,

unframed (clear channel) T1s, unframed (clear channel) E1s, transparent

virtual tributaries or transparent tributary units over this interface.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 9

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Transparent VT/TU access can be selected only when tributaries are mapped

into SONET/SDH.

· Transparent VT1.5s and TU-11s can be selected on a per tributary basis in

combination with framed and unframed T1s. Transparent VT2s and TU-12s

can be selected on a per tributary basis in combination with framed and

unframed E1s.

· Transmit timing is mastered either by the TEMAP or a layer 2 device

connecting to the SBI bus. Timing mastership is selectable on a per tributary

basis, where a tributary is either an individual T1, E1 or a DS3.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 10

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

2 APPLICATIONS

· SONET/SDH Add Drop Multiplexers

· SONET/SDH Terminal Multiplexers

· M23 Based M13 Multiplexer

· C-Bit Parity Based M13 Multiplexer

· Channelized and Unchannelized DS3 Frame Relay Interfaces

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 11

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

3 REFERENCES

· American National Standard for Telecommunications - Digital Hierarchy Synchronous DS3 Format Specifications, ANSI T1.103-1993

· American National Standard for Telecommunications – ANSI T1.105 –

“Synchronous Optical Network (SONET) – Basic Description Including Multiplex

Structure, Rates, and Formats,” October 27, 1995.

· American National Standard for Telecommunications – ANSI T1.105.02 –

“Synchronous Optical Network (SONET) – Payload Mappings,” October 27,

1995.

· American National Standard for Telecommunications - Digital Hierarchy Formats Specification, ANSI T1.107-1995

· American National Standard for Telecommunications - Digital Hierarchy - Layer 1

In-Service Digital Transmission Performance Monitoring, ANSI T1.231-1997

· American National Standard for Telecommunications - Carrier to Customer

Installation - DS-1 Metallic Interface Specification, ANSI T1.403-1995

· American National Standard for Telecommunications - Customer Installation–toNetwork - DS3 Metallic Interface Specification, ANSI T1.404-1994

· American National Standard for Telecom–unications - Integrated Services Digital

Network (ISDN) Primary Rate- Customer Installation Metallic Interfaces Layer 1

Specification, ANSI T1.408-1990

· Bell Communications Research, TR–TSY-000009 - Asynchronous Digital

Multiplexes Requirements and Objectives, Issue 1, May 1986

· Bell Communications Research - DS-1 Rate Digital Service Monitoring Unit

Functional Specification, TA-TSY-000147, Issue 1, October, 1987

· Bell Communications Research - Alarm Indication Signal Requirements and

Objectives, TR-TSY-000191 Issue 1, May 1986

· Bell Communications Research - Wideband and Broadband Digital CrossConnect Systems Generic Criteria, TR-NWT-000233, Issue 3, November 1993

· Bellcore GR-253-CORE – “SONET Transport Systems: Common Criteria,” Issue

2, Revision 1, December 1997.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 12

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· Bell Communications Research - Integrated Digital Loop Carrier Generic

Requirements, Objectives, and Interface, TR-NWT-000303, Issue 2, December,

1992

· Bell Communications Research - Transport Systems Generic Requirements

(TSGR): Common Requirement, TR-TSY-000499, Issue 5, December, 1993

· Bell Communications Research - OTGR: Network Maintenance Transport

Surveillance - Generic Digital Transmission Surveillance, TR-TSY-000820,

Section 5.1, Issue 1, June 1990

· AT&T - Requirements For Interfacing Digital Terminal Equipment To Services

Employing The Extended Superframe Format, TR 54016, September, 1989.

· AT&T - Accunet T1.5 - Service Description and Interface Specification, TR 62411,

December, 1990

· ITU Study Group XVIII – Report R 105, Geneva, 9-19 June 1992

· ETSI - ETS 300 011 - ISDN Primary Rate User-Network Interface Specification

and Test Principles, 1992.

· ETSI - ETS 300 233 - Access Digital Section for ISDN Primary Rates, May 1994

· ETSI - ETS 300 324-1 - Signaling Protocols and Switching (SPS); V interfaces at

the Digital Local Exchange (LE) V5.1 Interface for the Support of Access

Network (AN) Part 1: V5.1 Interface Specification, February, 1994.

· ETSI - ETS 300 347-1 - Signaling Protocols and Switching (SPS); V Interfaces at

the Digital Local Exchange (LE) V5.2 Interface for the Support of Access

Network (AN) Part 1: V5.2 Interface Specification, September 1994.

· ETSI ETS 300 417-1-1 – “Transmission and Multiplexing (TM); Generic

Functional Requirements for Synchronous Digital Hierarchy (SDH) equipment;

Part 1-1: Generic processes and performance,” January, 1996.

· ETSI, Generic Functional Requirements for Synchronous Digital Hierarchy (SDH)

Equipment, Jan 1996

· ITU-T - Recommendation G.704 - Synchronous Frame Structures Used at

Primary Hierarchical Levels, July 1995.

· ITU-T - Recommendation G.706 - Frame Alignment and CRC Procedures

Relating to G.704 Frame Structures, 1991.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 13

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· ITU-T - Recommendation G.732 – Characteristics of Primary PCM Multiplex

Equipment Operating at 2048 kbit/s, 1993.

· ITU-T Recommendation G.707 – Network Node Interface for the Synchronous

Digital Hierarchy, 1996

· ITU-T Recommendation G.747 – Second Order Digital Multiplex Equipment

Operating at 6312kbit/s and Multiplexing Three Tributaries at 2048 kbit/s, 1988

· ITU-T Recommendation G.775, - Loss of Signal (LOS) and Alarm Indication

Signal (AIS) Defect Detection and Clearance Criteria, 11/94

· ITU-T Recommendation G.783 – “Characteristics of Synchronous Digital

Hierarchy (SDH) Equipment Functional Blocks,” April, 1997.

· ITU-T Recommendation G.823, - The Control of Jitter and Wander within Digital

Networks which are Based on the 2048 kbit/s Hierarchy, 03/94

· ITU-T Recommendation G.964, - V-Interfaces at the Digital Local Ex–hange (LE)

- V5.1 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN),

June 1994.

· ITU-T Recommendation G.965, - V-Interfaces at the Digital Local Ex–hange (LE)

- V5.2 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN),

March –995.

· ITU-T - Recommend–tion I.431 - Primary Rate User-Network Interface – Layer 1

Specification, 1993.

· ITU-T Recommendation O.151 – Error Performance Measuring Equipment

Operating at the Primary Rate and Above, October 1992

· ITU-T Recommendation O.152 – Error Performance Measuring Equipment for

Bit Rates of 64 kbit/s and N x 64 kbit/s, October 1992

· ITU-T Recommendation O.153 - Basic Parameters for the Measurement of Error

Performance at Bit Rates below the Primary Rate, October 1992.

· ITU-T Recommendation Q.921 - ISDN User-Network Interface Data Link Layer

Specification, March 1993

· International Organization for Standardization, ISO 3309:1984 - High-Level Data

Link Control procedures - Frame Structure

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 14

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

· PMC-Sierra Inc., PMC-1980577 – Saturn Compatible Scaleable Bandwidth

Interface (SBI) Specification, Issue 3, 1998

· TTC Standard JT-G704 - Frame Structures on Primary and Secondary

Hierarchical Digital Interfaces, 1995.

· TTC Standard JT-G706 - Frame Synchronization and CRC Procedure

· TTC Standard JT-I431 - ISDN Primary Rate User-Network Interface Layer 1 -

Specification, 1995.

· Nippon Telegraph and Telephone Corporation - Technical Reference for HighSpeed Digital Leased Circuit Services, Third Edition, 1990.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 15

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

4 APPLICATION EXAMPLES

Figure 1 - Channelized DS3 Circuit Emulation Application

PM5365

DS3 LIU

DS3 LIU

DS3 LIU

TEMAP

28 T1/21 E1 PMON

M13 Mux, DS3 framer

PM5365

TEMAP

28 T1/21 E1 PMON

M13 Mux, DS3 framer

PM5365

TEMAP

28 T1/21 E1 PMON

M13 Mux, DS3 framer

SBI

Bus

Figure 2 - High Density Frame Relay Application

PM5365 TEMAP #3

PM5365 TEMAP #2

PM5365 TEMAP #1

in VT1.5 or VT2.0 Mapper Mode

T1 PMON #28

or E1 PMON #21

Mapper

and

Telecom

Bus I/F

T1 or E1

PMON #1

…

High Density T1/E1 Frame Relay Port Card

STS-3/

STM-1

PM5342

SPECTRA

155

Payload

Extractor/

Aligner

PM73122

AAL1gator-32

ATM SAR

PM73122

AAL1gator-32

ATM SAR

PM73122

AAL1gator-32

ATM SAR

SBI

Bus

Utopia

Bus

PM7384

FREEDM

84P672

High Density

HDLC

Controller

PCI

Bus

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 16

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

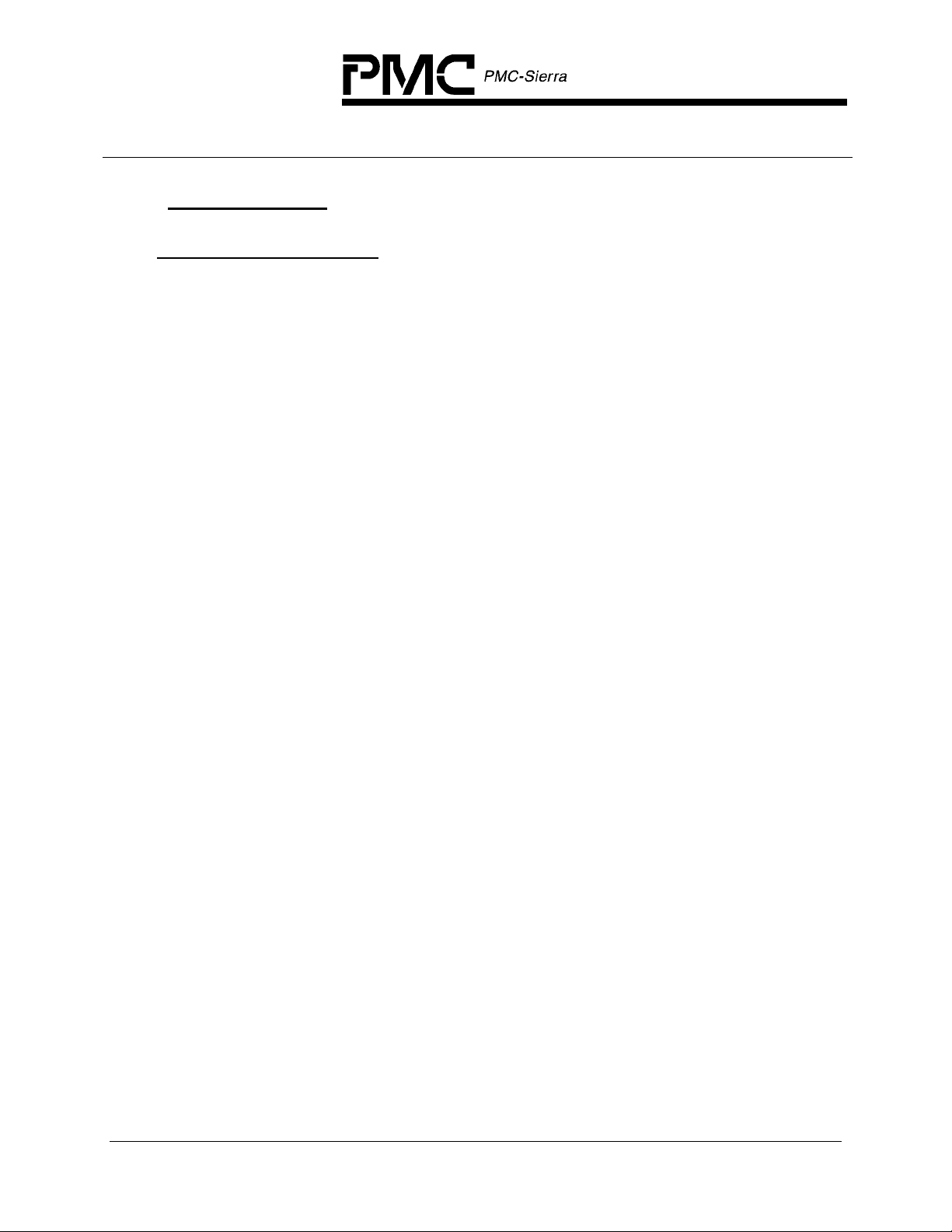

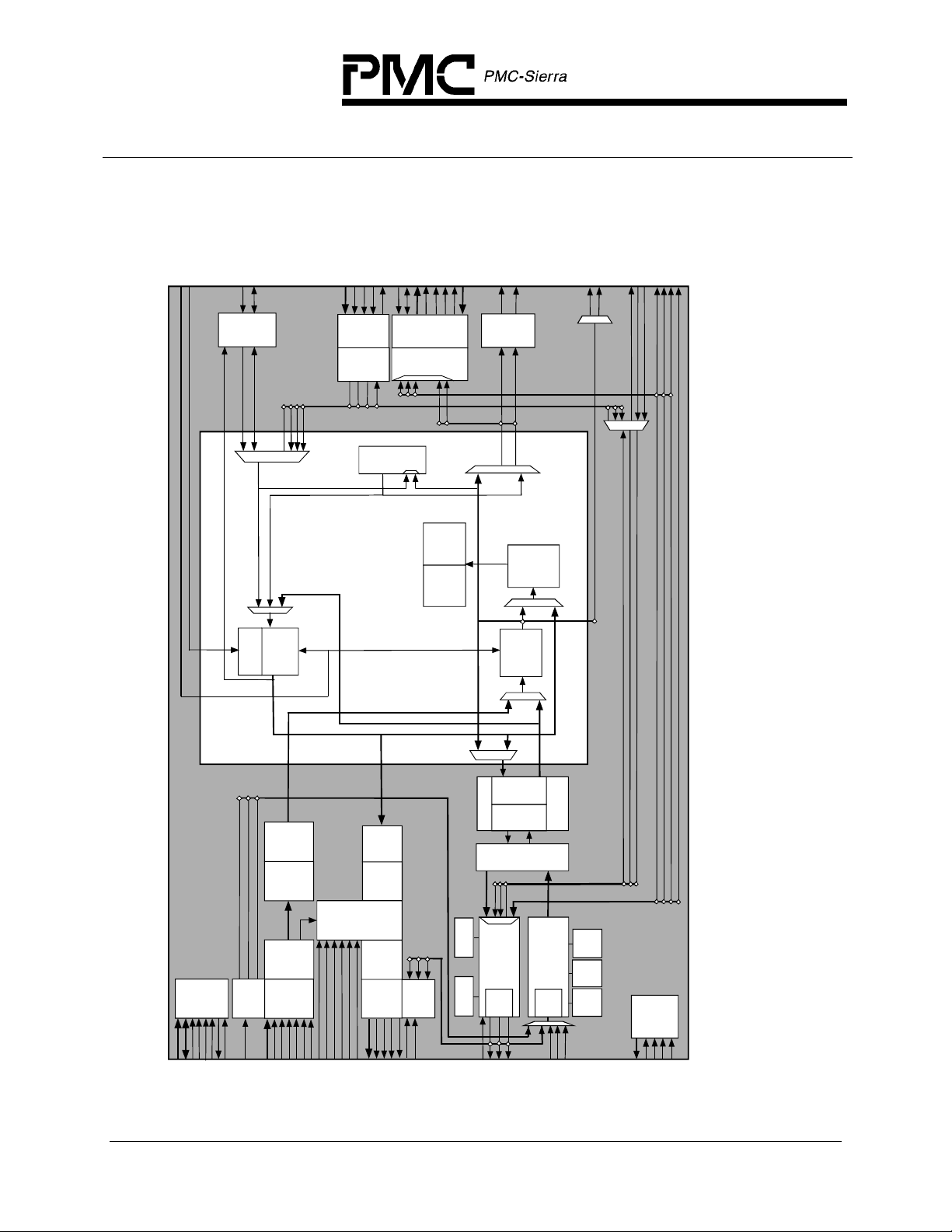

5 BLOCK DIAGRAM

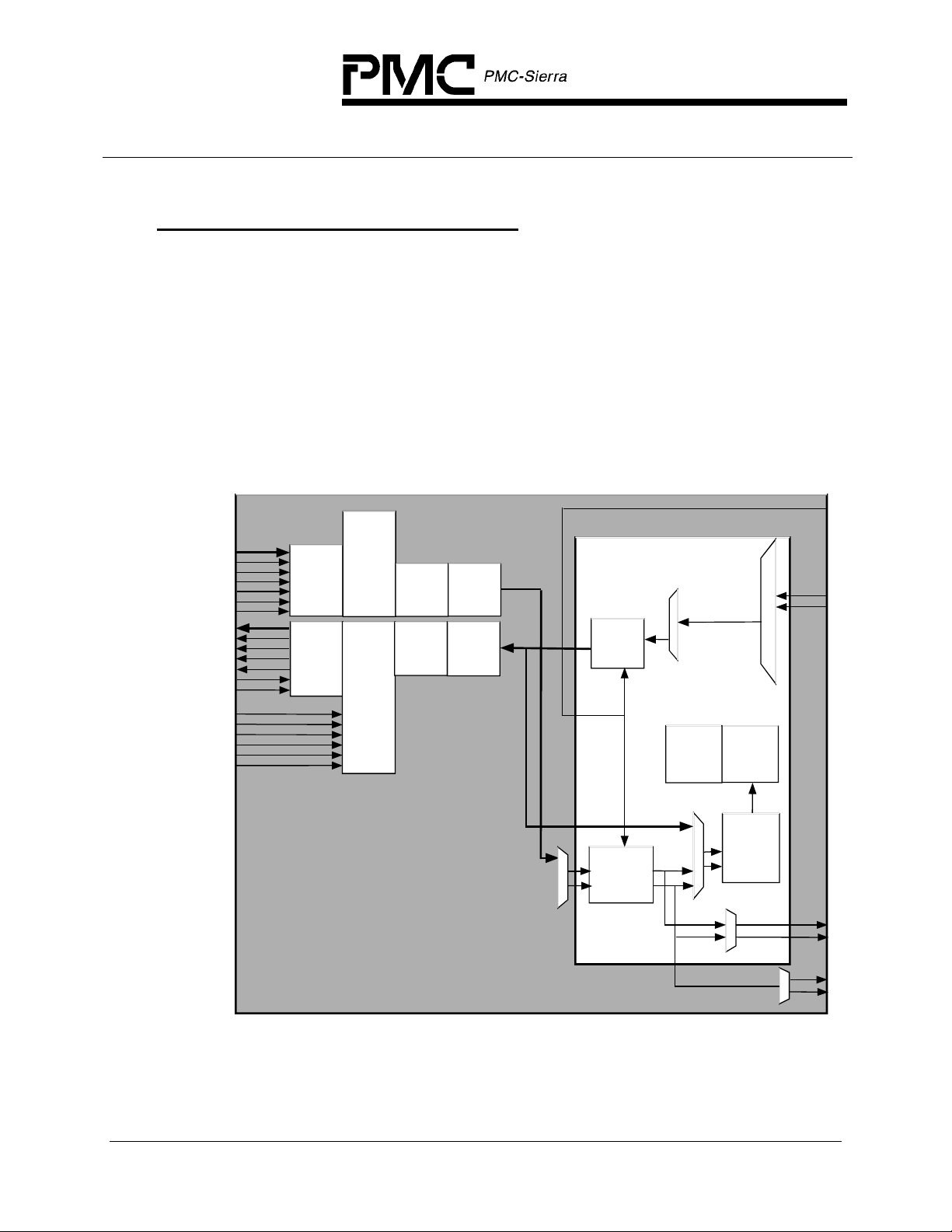

5.1 Top Level Block Diagram

Figure 3 shows the complete TEMAP. Clear Channel T1 links can be multiplexed

into the DS3 or can be mapped into the telecom bus as SONET VT1.5 virtual

tributaries or as SDH TU-11 or TU-12 tributary units, shown at the bottom of the

diagram. Clear Channel E1 links can be mapped into the telecom bus as SONET

VT2 virtual tributaries or as SDH TU-12 tributary units, shown at the bottom of

the diagram. System side access to the T1s and E1s is available as serial clock

and data or the SBI bus. DS3 line side access is via the clock and data interface

for line interface units or DS3 mapped into the SONET/SDH telecom bus.

Unchannelized DS3 system side access is available through a serial clock and

data interface or the SBI bus, both shown at the top of the diagram.

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 17

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

Figure 3 - TEMAP Block Diagram

K

L

/

C

Q

]

8

2

]

:

8

1

K

K

L

L

C

C

T

X

C

[

2

:

K

1

[

L

D

C

E

E

]

E

0

:

R

7

[

_

A

T

A

D

A

S

K

L

T

S

C

P

D

A

S

P

5

L

F

F

U

J

V

P

1

E

A

A

A

C

R

S

S

S

S

S

]

]

0

0

:

:

1

7

[

[

T

A

T

C

T

C

A

A

P

L

5

B

A

D

P

V

D

I

I

B

B

D

D

D

D

S

S

S

S

S

S

]

8

2

]

:

8

1

[

2

:

K

1

L

[

C

D

I

I

O

P

F

1

2

K

K

M

L

L

T

/

C

C

O

V

V

P

C

C

F

E

E

T

R

R

O

S

P

I

R

/

F

P

K

K

F

M

D

L

L

R

M

H

C

/

O

C

I

T

P

R

/

T

P

O

T

I

A

V

A

A

P

A

P

G

D

F

O

D

G

F

R

R

R

T

R

T

T

e

s

c

m

s

F

a

e

I

f

e

t

r

r

S

s

e

g

y

E

t

E

S

n

I

s

n

r

r

o

i

e

t

t

o

t

t

S

i

p

T

a

J

P

O

u

A

l

O

n

J

a

g

t

i

e

T

T

n

t

i

t

g

i

A

m

i

D

T

I

s

I

s

B

e

B

S

r

X

S

g

E

E

l

O

e

l

S

l

I

o

a

P

t

r

I

a

B

P

S

S

B

R

P

s

I

s

I

s

u

B

l

a

i

r

e

S

n

r

e

t

t

a

P

s

B

e

B

u

r

S

S

g

B

N

I

n

I

l

O

l

e

l

P

a

l

I

i

r

o

a

S

t

r

I

e

a

B

S

P

S

r

-

o

r

/

t

r

e

c

o

n

e

t

t

e

a

e

G

D

r

o

I

t

m

a

r

M

r

a

g

L

l

e

A

A

t

n

I

e

c

s

r

n

r

o

N

a

e

t

t

i

O

m

n

n

r

u

M

o

o

f

o

P

r

M

C

e

P

e

s

c

m

s

a

e

F

e

f

I

t

r

r

s

S

g

e

I

y

t

n

S

I

n

I

R

,

t

n

M

n

o

e

i

e

R

t

m

r

c

m

F

m

-

a

a

a

l

n

r

r

1

t

g

A

F

E

i

x

l

/

E

1

A

T

r

r

e

t

o

t

t

i

T

a

J

A

u

l

J

n

a

t

i

e

R

t

g

t

i

A

D

s

r

e

m

a

r

F

g

n

i

r

1

o

E

t

i

1

n

2

o

r

M

o

e

1

c

T

n

8

a

2

m

f

r

o

o

f

e

r

n

e

O

P

X

/

2

1

X

M

R

M

R

F

r

r

o

e

t

e

l

t

p

l

r

a

O

e

p

i

e

l

r

l

S

a

v

I

e

a

n

r

m

P

S

o

a

e

C

P

D

r

y

e

e

r

p

v

a

M

i

t

p

e

D

a

u

c

T

b

e

i

M

R

r

e

R

T

D

P

A

R

T

r

y

o

H

e

r

/

s

P

v

a

i

s

O

t

O

e

e

u

h

c

T

c

b

t

e

i

R

o

a

r

r

R

P

T

P

r

e

e

o

-

F

o

I

r

P

c

i

M

M

]

]

B

B

B

0

0

:

:

S

R

D

3

7

[

C

R

1

W

[

D

A

d

i

c

s

D

3

S

s

a

f

M

S

e

r

p

3

c

D

e

o

t

o

D

r

r

n

I

P

D

B

B

E

M

L

T

T

2

A

S

5

N

I

R

K

L

C

r

o

r

d

s

e

a

U

P

s

p

o

T

P

l

/

e

p

T

y

c

T

a

a

V

o

V

M

r

P

P

]

5

1

L

L

T

T

P

P

0

J

:

D

1

7

[

D

C

A

L

D

T

L

A

D

D

L

K

S

I

P

V

P

D

L

F

S

S

C

A

T

T

L

A

E

D

D

L

S

D

S

E

L

L

W

A

A

D

D

E

E

A

A

D

D

R

R

A

A

R

R

r

l

e

o

t

t

e

l

r

l

O

l

e

a

a

P

i

v

I

r

r

n

a

S

e

o

P

S

C

t

y

i

r

r

e

P

m

a

t

p

s

M

u

p

n

T

b

a

a

i

T

r

r

M

T

T

r

t

i

o

e

t

s

m

m

o

s

r

s

e

a

m

n

l

c

e

a

o

A

r

r

R

T

P

r

t

y

i

o

H

r

/

s

P

a

m

s

t

O

s

O

e

u

h

n

T

t

c

b

a

i

a

T

o

r

r

r

P

T

T

P

r

t

e

i

o

r

d

d

s

e

a

A

i

U

P

m

3

s

p

o

T

S

s

P

M

l

/

S

e

n

T

a

V

r

T

]

K

P

P

0

:

F

C

D

7

T

T

[

A

S

S

L

A

E

E

T

A

W

W

D

D

D

A

A

A

L

R

R

p

3

y

c

T

d

a

D

a

D

o

d

V

M

r

P

A

P

L

1

1

E

K

V

P

L

C

O

1

A

A

C

A

J

L

L

F

L

1

E

C

R

A

L

L

1

#

C

L

R

D

P

H

D

T

x

t

i

T

N

m

3

s

A

S

n

R

D

a

T

r

T

C

C

A

E

O

e

S

F

d

B

Z

o

X

x

c

3

T

n

B

E

K

T

K

L

L

A

C

D

C

I

T

T

T

/

S

O

P

T

n

U

2

X

e

1

M

2

S

D

3

2

X

M

r

e

m

a

r

F

P

F

M

T

/

G

E

N

T

s

M

U

v

2

E

e

M

1

D

S

M

r

/

f

e

o

R

m

e

M

a

r

n

R

F

O

F

X

/

3

U

X

2

M

U

M

E

M

D

r

.

N

o

f

t

i

r

O

n

e

e

r

M

o

P

v

R

e

i

3

P

M

e

M

S

m

c

a

R

D

e

r

F

F

R

C

C

x

L

L

R

D

D

R

H

e

C

S

Z

3

B

C

d

x

O

o

A

R

c

E

B

e

F

R

D

K

T

V

L

A

C

C

L

D

R

R

R

/

/

S

G

E

O

P

N

R

R

s

s

e

c

t

G

r

c

A

o

A

T

P

t

J

s

e

T

I

B

K

S

O

D

T

L

M

D

T

S

C

T

T

T

R

T

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 18

STANDARD PRODUCT

DATASHEET

PMC-1991148 ISSUE 3 HIGH DENSITY VT/TU MAPPER

PM5365 TEMAP

AND M13 MULTIPLEXER

5.2 VT/TU Mapper Only Mode Block Diagram

Figure 4 shows the TEMAP configured as a VT or TU mapper. In this mode the

TEMAP provides access for up to 28 independent unframed 1.544Mb/s streams

or 21 independent unframed 2.048Mb/s streams. The 1.544Mb/s and 2.048Mb/s

streams can be accessed on the system side as clock and data as shown in

Figure 4, or they can be accessed via the SBI bus. The T1 or E1 framers and

performance monitoring blocks can be used to monitor the passing traffic in

either the ingress or egress direction. The M13 Multiplexer mode operates in

much the same way as the VT and TU mapper shown in Figure 4.

Figure 4 - VT/TU Mapper Block Diagram

VT

VT

RTOP

Receive

Tributary

Path O/H

Processor

TRAP/

TTOP

Transmit

Remote

Alarm

&

Tributary

PathO/H

Processors

RTDM

Receive

Tributary

DeMapper

TTMP

Transmit

Tributary

Mapper

PISO

Parallel to

Serial

Converter

SIPO

Serial to

Parallel

Converter

LDDAT A[7:0]

LDC1 J1

LDDP

LDPL

LDT PL

LDV5

LDAIS

LADA TA[7 :0]

LADP

LAPL

LAC1J 1V1

LAOE

LAC1

LREF CLK

RADE AST

RAD EAS LCK

RADE ASTFP

RADW EST

RADW ESTCK

RADW ESTFP

VTPP

Payload

Processor

VTPP

Payload

Processor

XCL K

ECLK [1:2 8]

ED[1 :28]

TJAT

Digital Jitter

Attenuator

PMON

Performance

Monitor

Counters

ALMI

Alarm

Integrator

T1/E1-FRMR

Framer:

Frame

Alignment,

RJAT

Digital Jitter

Attenuator

One of 28 T 1 or

21 E1 Fram ers

Alarm

Extraction

Proprietary and Confidential to PMC-Sierra, Inc. and for its Customers’ Internal Use 19

ID[1:2 8]

ICLK[ 1:28 ]

REC VCL K1

REC VCL K2

Loading...

Loading...