PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5361

TUPP

SONET/SDH TRIBUTARY UNIT PAYLOAD

PROCESSOR

DATA SHEET

ISSUE 8: JULY 1998

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

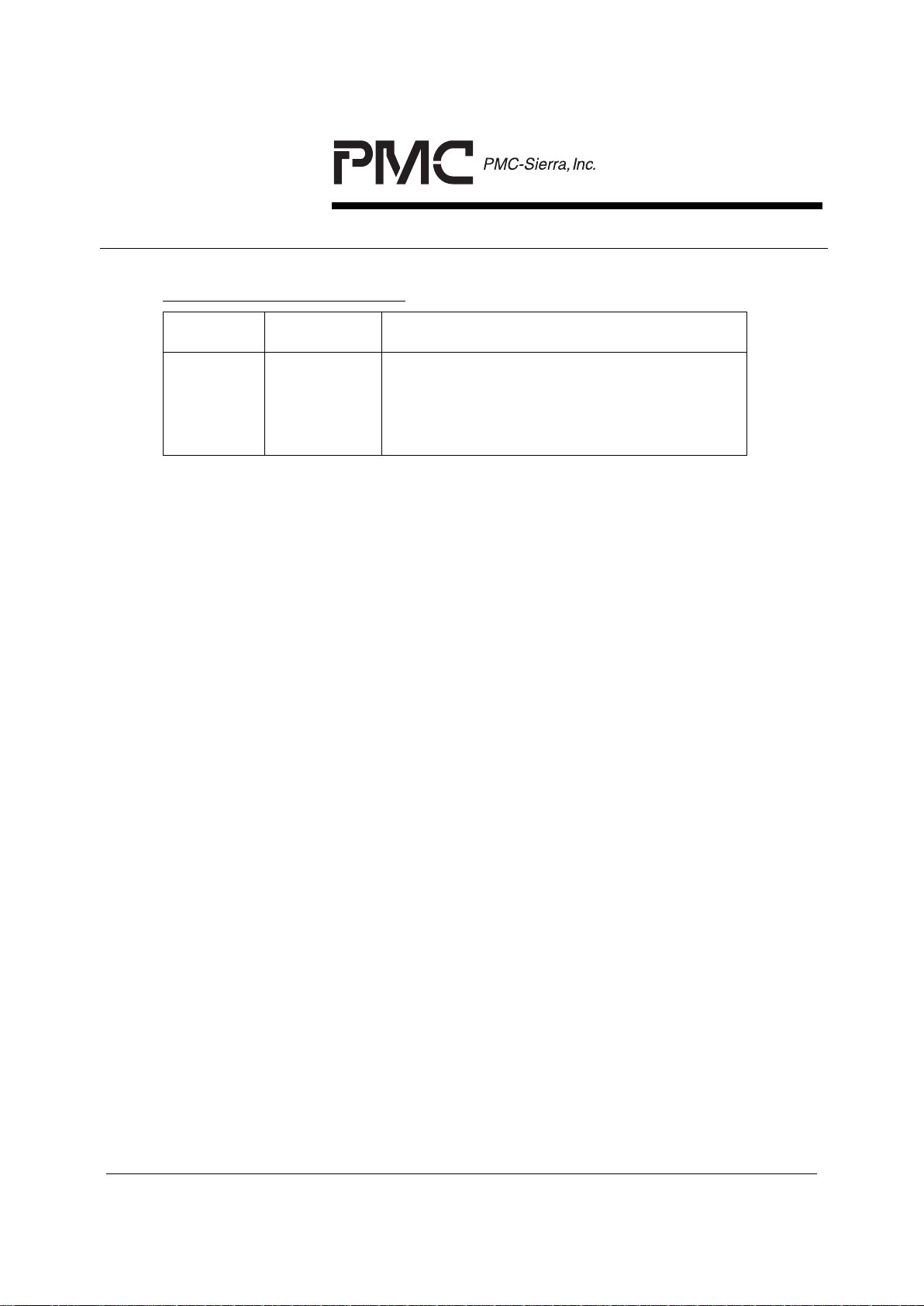

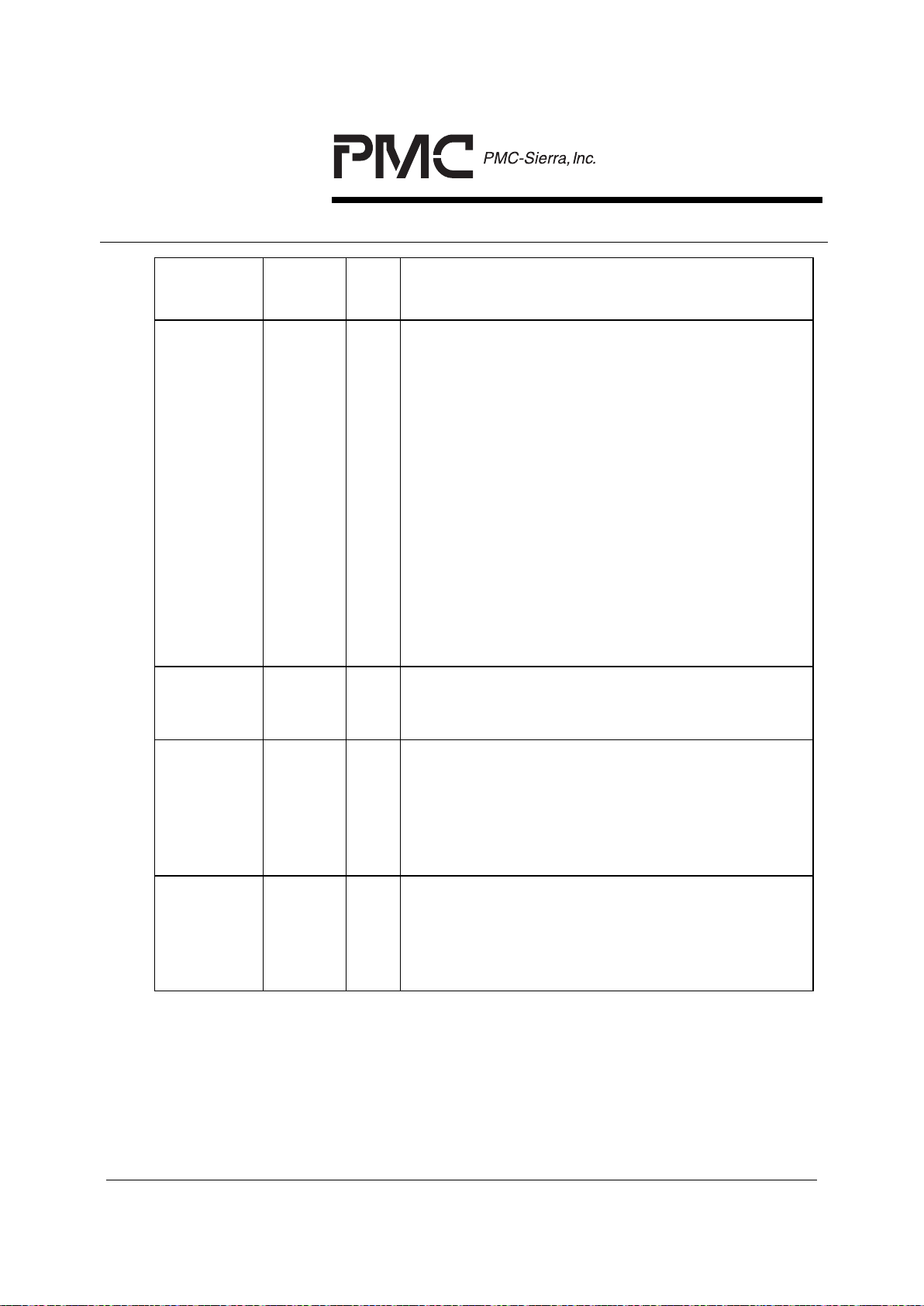

PUBLIC REVISION HISTORY

Issue No. Issue Date Details of Change

8 July 1998 Data Sheet Reformatted — No Change in

Technical Content.

Generated R8 data sheet from PMC-

920102, issue R10.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

CONTENTS

1 FEATURES......................................................................................................................................1

2 APPLICATIONS...............................................................................................................................3

3 REFERENCES................................................................................................................................4

4 APPLICATION EXAMPLE................................................................................................................5

5 BLOCK DIAGRAM...........................................................................................................................6

6 DESCRIPTION................................................................................................................................8

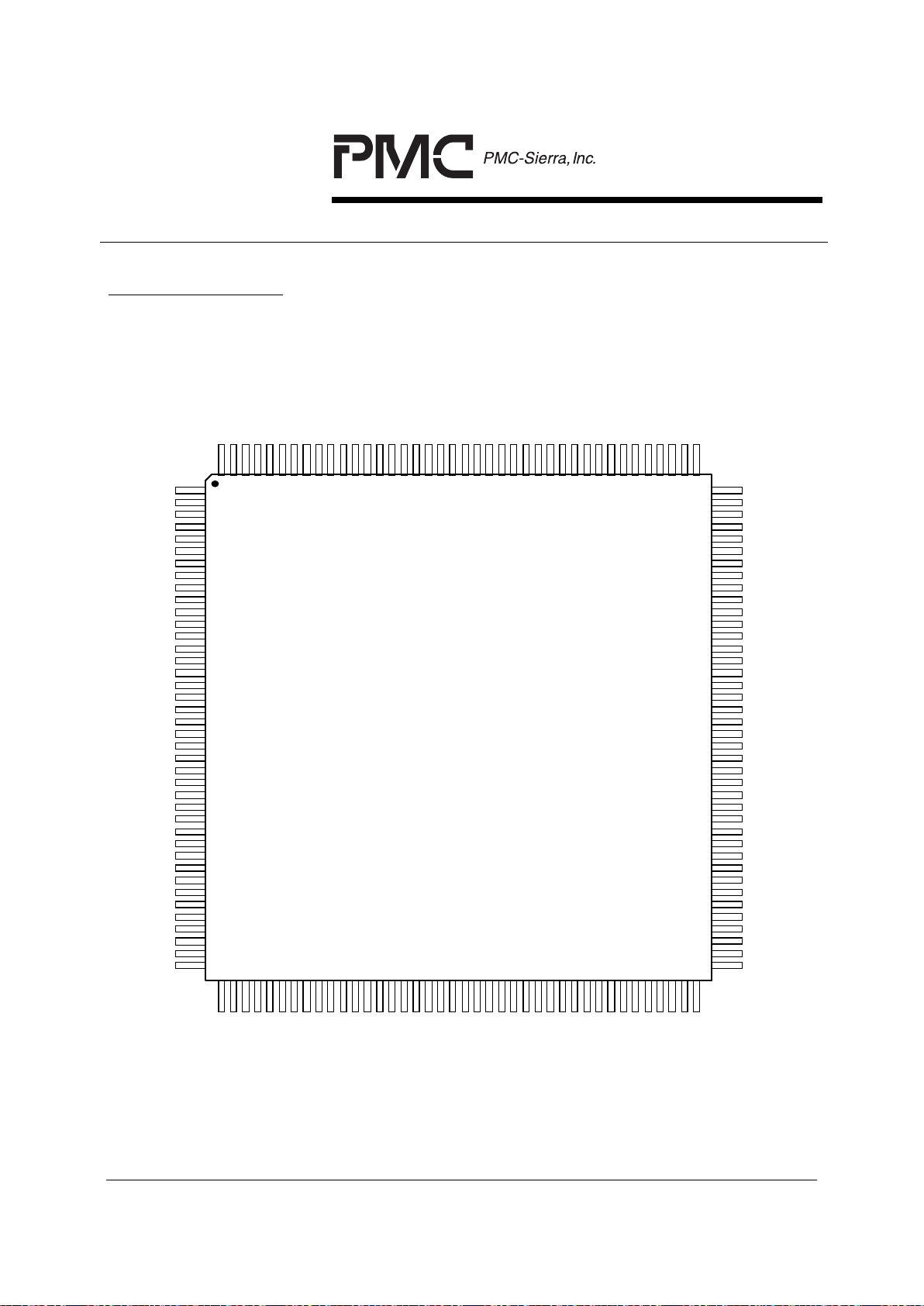

7 PIN DIAGRAM...............................................................................................................................10

8 PIN DESCRIPTION.......................................................................................................................11

9 FUNCTIONAL DESCRIPTION......................................................................................................22

9.1 INPUT BUS DEMULTIPLEXER.....................................................................22

9.2 OUTPUT BUS MULTIPLEXER......................................................................22

9.3 TRIBUTARY PAYLOAD PROCESSOR..........................................................23

9.3.1 CLOCK GENERATOR.....................................................................23

9.3.2 INCOMING TIMING GENERATOR..................................................23

9.3.3 INCOMING MULTIFRAME DETECTOR..........................................24

9.3.4 POINTER INTERPRETER..............................................................24

9.3.5 PAYLOAD BUFFER.........................................................................24

9.3.6 OUTGOING TIMING GENERATOR ................................................25

9.3.7 POINTER GENERATOR.................................................................25

9.3.8 COMMON BUS INTERFACE ..........................................................26

9.4 MICROPROCESSOR INTERFACE...............................................................26

9.5 REGISTER MEMORY MAP...........................................................................26

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

10 NORMAL MODE REGISTER DESCRIPTION...............................................................................29

11 TEST FEATURES DESCRIPTION ................................................................................................64

11.1 I/O TEST MODE............................................................................................67

12 OPERATION..................................................................................................................................68

12.1 CONFIGURATION OPTIONS........................................................................68

12.2 STS-1 MODE.................................................................................................70

12.3 AU3 MODE....................................................................................................70

12.4 AU4 MODE....................................................................................................71

13 FUNCTIONAL TIMING ..................................................................................................................74

14 ABSOLUTE MAXIMUM RATINGS.................................................................................................82

15 D.C. CHARACTERISTICS .............................................................................................................83

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS ...............................................85

17 TUPP TIMING CHARACTERISTICS.............................................................................................92

18 ORDERING AND THERMAL INFORMATION ...............................................................................96

19 MECHANICAL INFORMATION......................................................................................................97

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

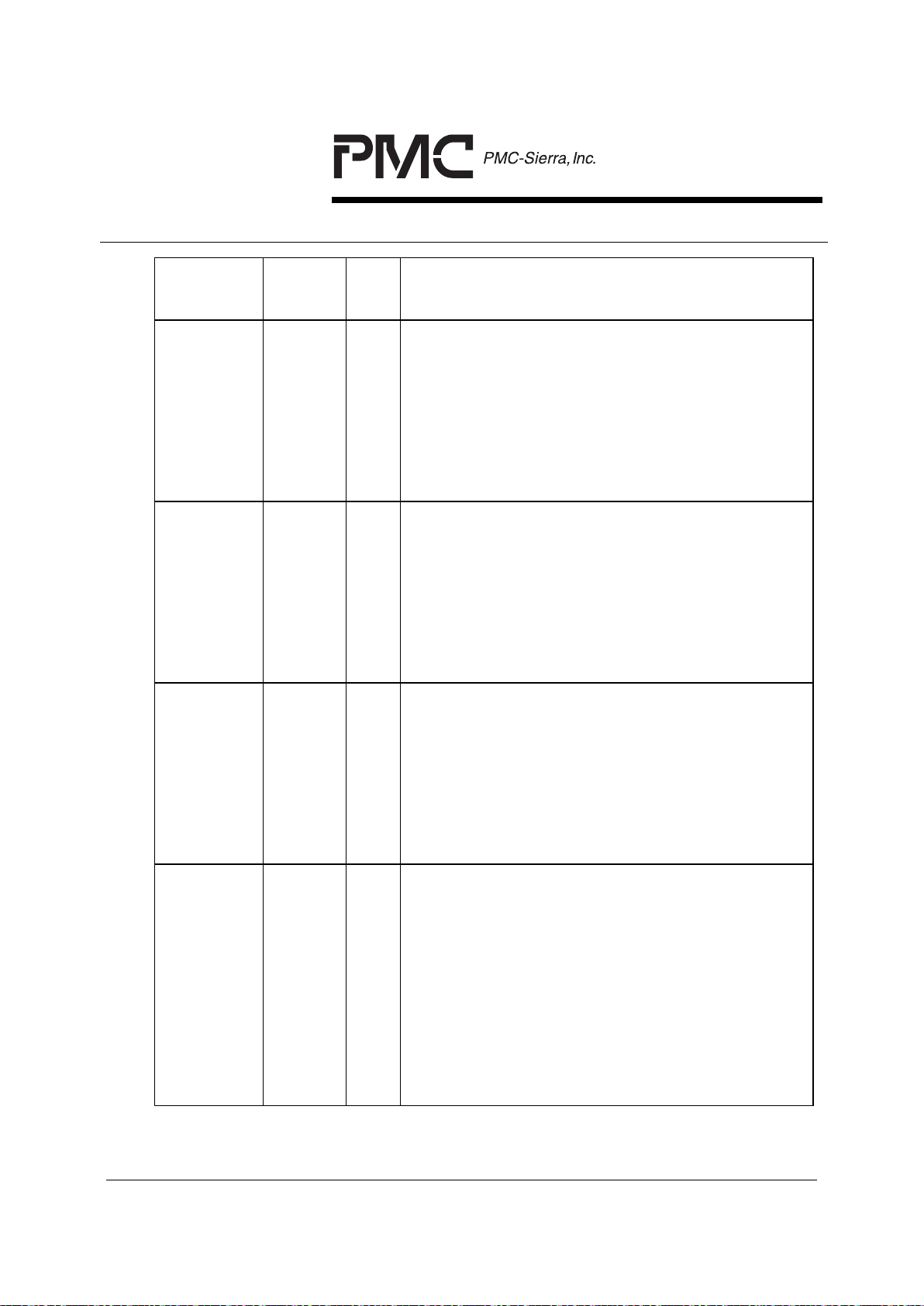

LIST OF REGISTERS

REGISTER 00H: MASTER INCOMING CONFIGURATION.........................................................................30

REGISTER 01H: MASTER OUTGOING CONFIGURATION........................................................................32

REGISTER 02H: INPUT SIGNAL ACTIVITY MONITOR..............................................................................34

REGISTER 03H: MASTER RESET AND IDENTITY....................................................................................36

REGISTER 04H: TRIBUTARY PAYLOAD PROCESSOR #1 CONFIGURATION.......................................... 37

REGISTER 05H: TRIBUTARY PAYLOAD PROCESSOR #2 CONFIGURATION.......................................... 39

REGISTER 06H: TRIBUTARY PAYLOAD PROCESSOR #3 CONFIGURATION.......................................... 41

REGISTER 07H: TPP AND H4 OOF INTERRUPT ENABLE .......................................................................43

REGISTER 08H: TPP INTERRUPT STATUS AND H4 OOF STATUS..........................................................45

REGISTER 09H: PARITY ERROR AND H4 OOF INTERRUPT...................................................................47

REGISTER 20H, 40H, 60H: TU3, OR TU #1 IN TUG2 #1, CONFIGURATION AND STATUS......................49

REGISTER 21H-26H, 41H-46H, 61H-66H: TU #1 IN TUG2 #2 TO TUG2 #7, CONFIGURATION AND

STATUS 51

REGISTER 27H, 47H, 67H: TU3 OR TU #1 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT .........................53

REGISTER 28H-2EH, 48H-4EH, 68H-6EH: TU #2 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND

STATUS 55

REGISTER 2FH, 4FH, 6FH: TU #2 IN TUG2 #1 TO TUG2 #7.....................................................................57

REGISTER 30H-36H, 50H-56H, 70H-76H: TU #3 IN TUG2 #1 TO TUG2 #7, CONFIGURATION AND

STATUS 58

REGISTER 37H, 57H, 77H: TU #3 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT .......................................60

REGISTER 38H-3EH, 58H-5EH, 78H-7EH: TU #4 IN TUG2 #2 TO TUG2 #7, CONFIGURATION AND

STATUS 61

REGISTER 3FH, 5FH, 7FH: TU #4 IN TUG2 #1 TO TUG2 #7, LOP INTERRUPT.......................................63

REGISTER 80H: MASTER TEST ................................................................................................................66

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

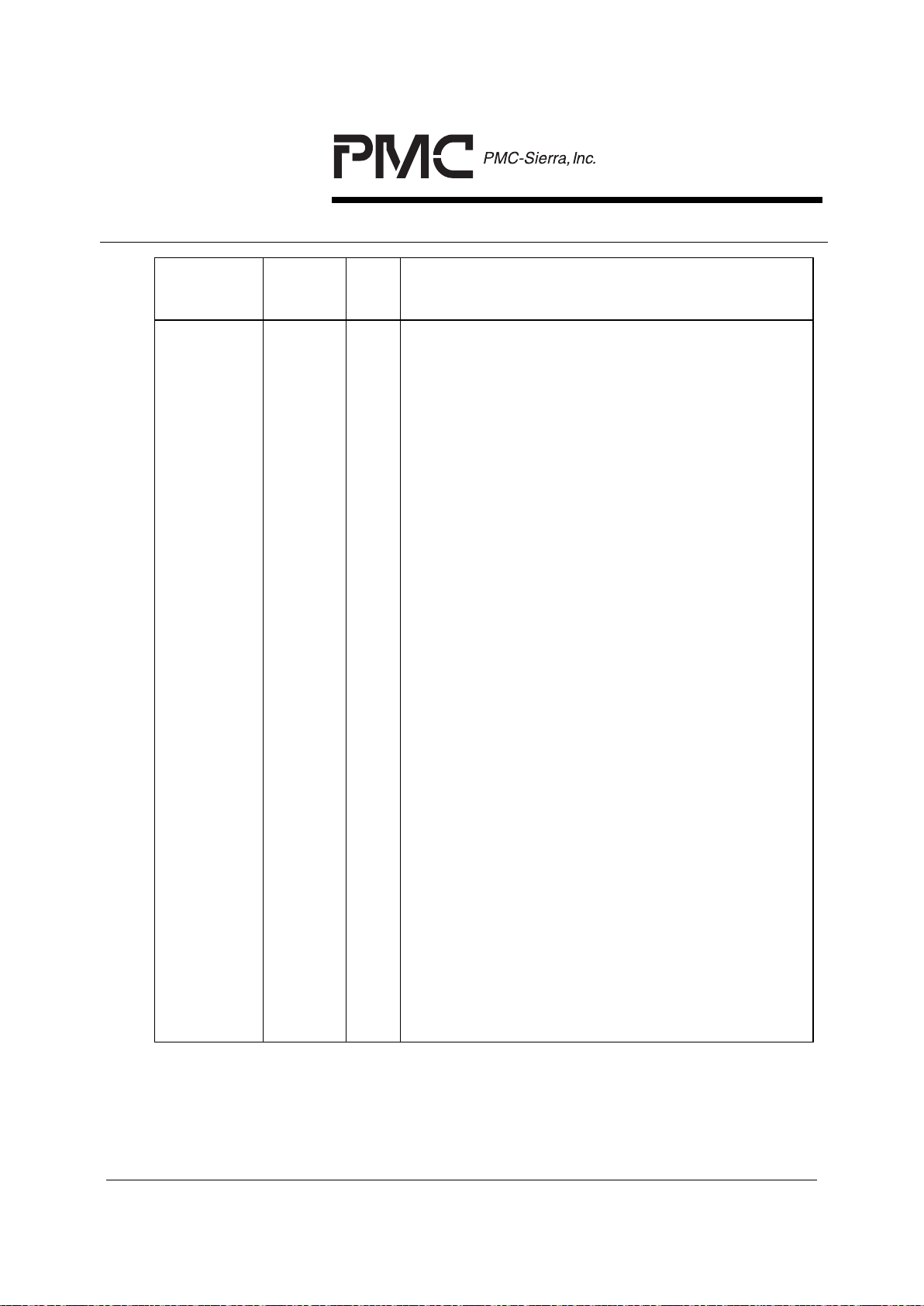

LIST OF FIGURES

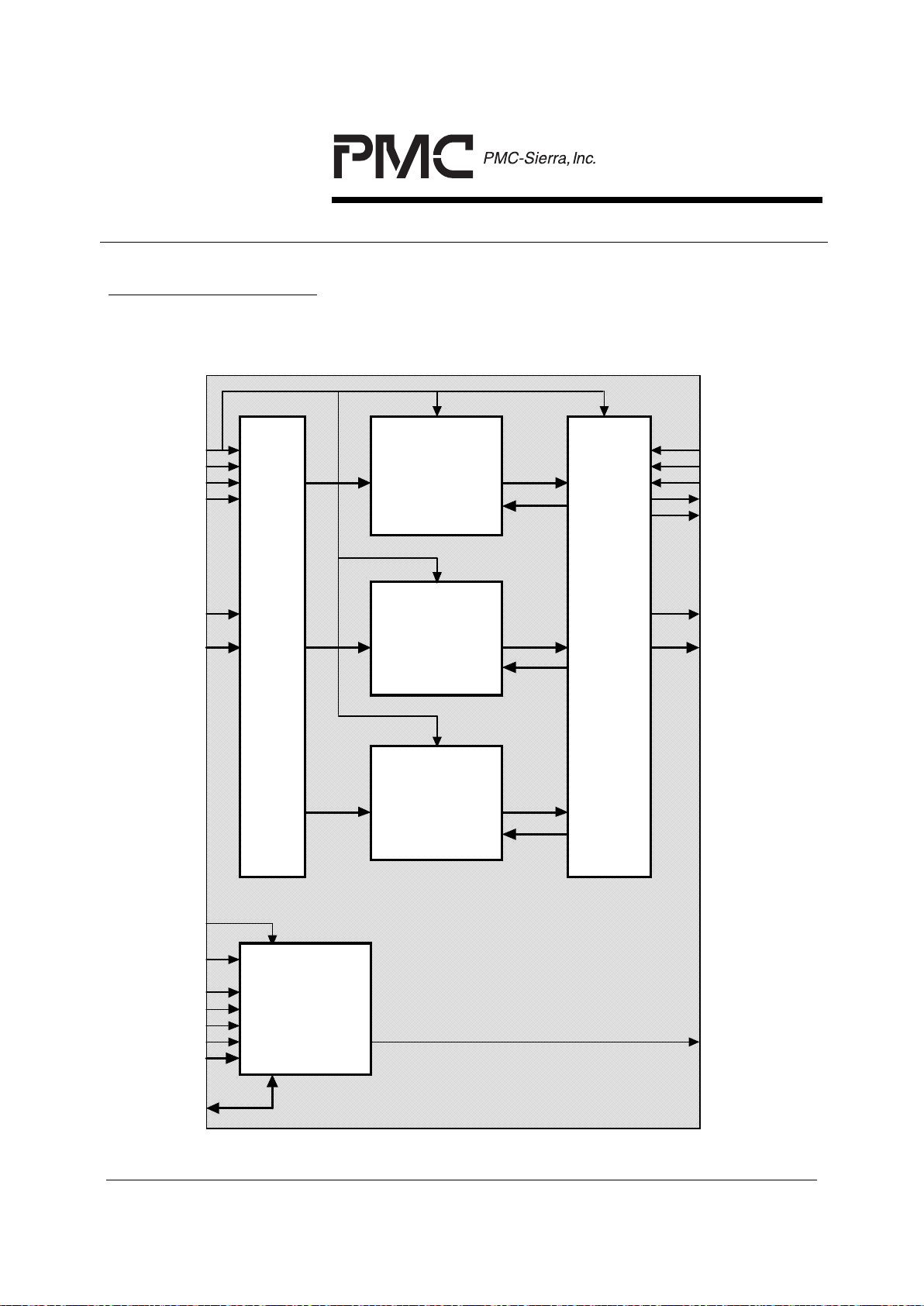

FIGURE 1 - SONET/SDH TRIBUTARY CROSS-CONNECT APPLICATION..........................................5

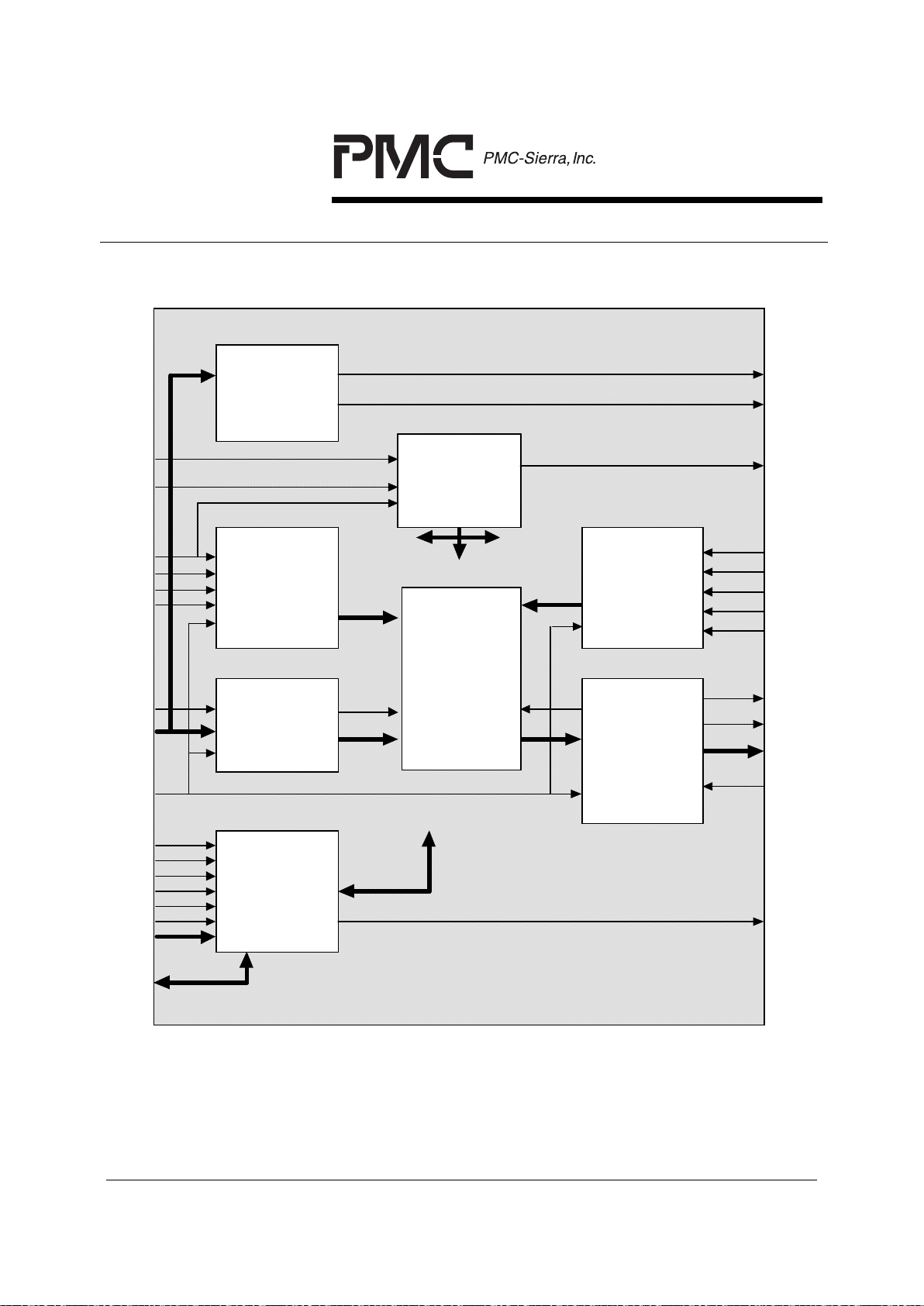

FIGURE 2 - OVERALL DEVICE.............................................................................................................6

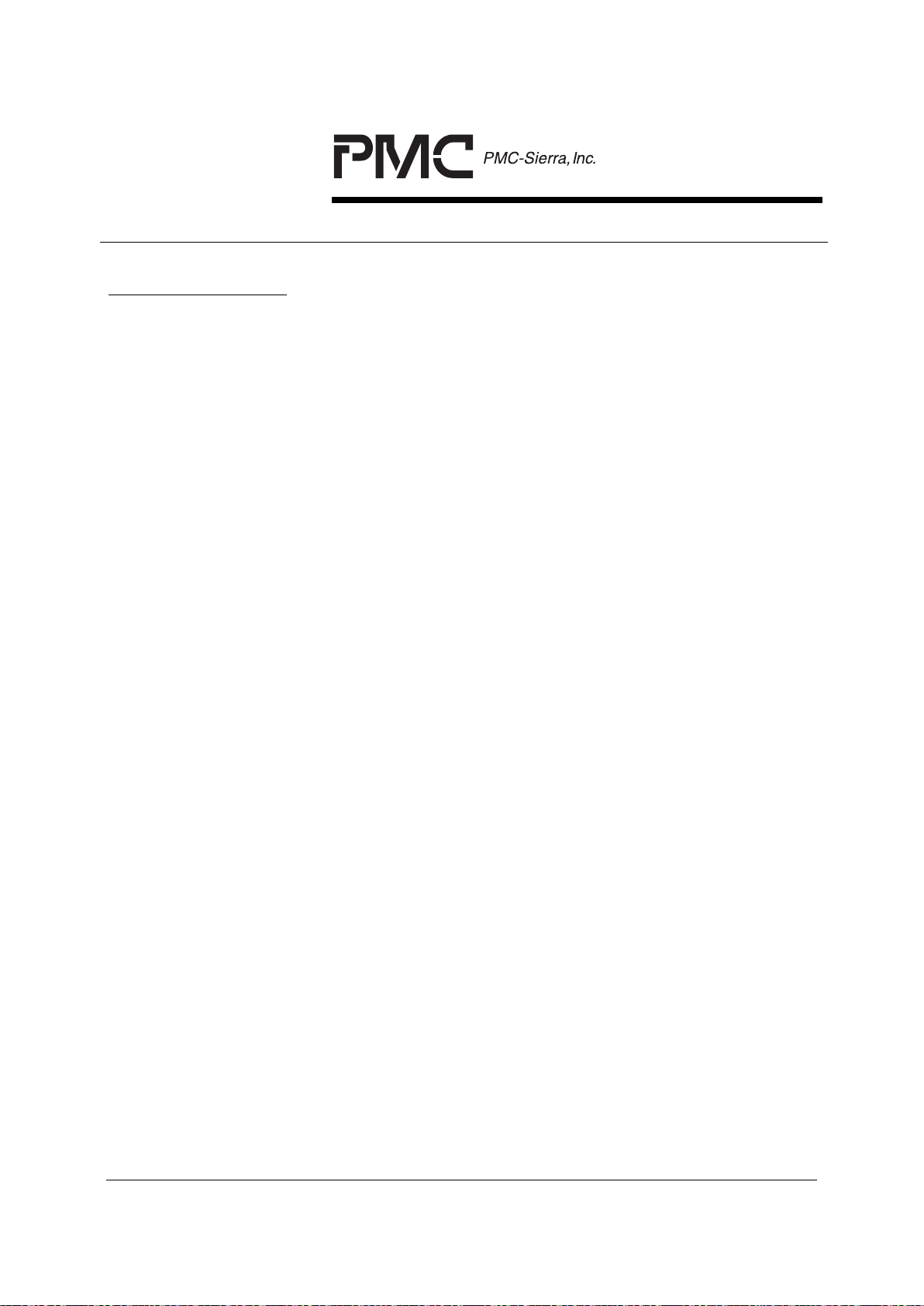

FIGURE 3 - EACH TRIBUTARY PAYLOAD PROCESSOR..................................................................... 7

FIGURE 4 - SONET STS-3 CARRYING VT1.5 WITHIN STS-1 ...........................................................70

FIGURE 5 - SDH STM-1 CARRYING TU12 WITHIN VC3/AU3............................................................71

FIGURE 6 - SDH STM-1 CARRYING TU12 WITHIN TUG3/AU4..........................................................71

FIGURE 7 - SDH STM-1 CARRYING TU3 WITHIN TUG3...................................................................72

FIGURE 8 - SDH STM-1 CARRYING MIX OF TU11, TU12, TU3 WITHIN TUG3/AU4.........................73

FIGURE 9 - INPUT BUS TIMING - SIMPLE STS-1/AU3 CASE...........................................................74

FIGURE 10 - INPUT BUS TIMING - COMPLEX STS-1 / AU3 CASE.....................................................75

FIGURE 11 - INPUT BUS TIMING - AU4 CASE.....................................................................................76

FIGURE 12 - OUTPUT BUS TIMING - LOCKED STS-1 SPES / AU3 VCS CASE .................................77

FIGURE 13 - OUTPUT BUS TIMING - FLOATING STS-1 SPES / AU3 VCS CASE...............................78

FIGURE 14 - OUTPUT BUS TIMING - LOCKED AU4 VC CASE ...........................................................79

FIGURE 15 - OUTPUT BUS TIMING - FLOATING AU4 VC CASE.........................................................80

FIGURE 16 - BY-PASSED MODE FUNCTIONAL TIMING .....................................................................81

FIGURE 17 - MICROPROCESSOR INTERFACE READ TIMING (INTEL MODE).................................86

FIGURE 18 - MICROPROCESSOR INTERFACE READ TIMING (MOTOROLA MODE).......................87

FIGURE 19 - MICROPROCESSOR INTERFACE WRITE TIMING (INTEL MODE)................................89

FIGURE 20 - MICROPROCESSOR INTERFACE WRITE TIMING (MOTOROLA MODE)......................90

FIGURE 21 - INPUT TIMING..................................................................................................................93

FIGURE 22 - OUTPUT TIMING..............................................................................................................94

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

LIST OF TABLES

TABLE 1 - TEST MODE REGISTER MEMORY MAP........................................................................64

TABLE 2 - I/O TEST MODE — INPUT READ REGISTER DESCRIPTION .......................................67

TABLE 3 - I/O TEST MODE — OUTPUT WRITE REGISTER DESCRIPTION..................................67

TABLE 4 - D.C. CHARACTERISTICS ................................................................................................83

TABLE 5 - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 17, FIGURE 18)..............85

TABLE 6 - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 19, FIGURE 20)............88

TABLE 7 - TUPP INPUT (FIGURE 21)...............................................................................................92

TABLE 8 - TUPP OUTPUT (FIGURE 22)...........................................................................................94

TABLE 9 - TUPP ORDERING INFORMATION...................................................................................96

TABLE 10 - TUPP THERMAL INFORMA TION.....................................................................................96

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

1

FEATURES

•

Configurable, multi-channel, payload processor for alignment of SONET

virtual tributaries (VTs) or SDH tributary units (TUs). Processes an STS-3 or

STM-1 byte serial data stream.

•

Transfers all incoming tributaries in the three STS-1 synchronous payload

envelopes of an STS-3 byte serial stream to the three STS-1 synchronous

payload envelopes of an outgoing STS-3 byte serial stream.

•

Transfers all incoming tributaries in the single AU4 or three AU3 administrative

units of an STM-1 byte serial stream to the single AU4 or three AU3

administrative units of an outgoing STM-1 byte serial stream.

•

Compensates for pleisiochronous relationships between incoming and

outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope

frame rates through processing of the lower level (VT6, VT3, VT2, VT1.5,

TU3, TU2, TU12, or TU11) tributary pointers.

•

Provides multiframe synchronization for ring closure at the headend node in

a SONET/SDH ring.

•

Provides independently configurable AU3/AU4 frame format on incoming and

outgoing directions.

•

Configurable to process any legal mix of tributaries such as VT1.5, VT2, VT3,

VT6, TU11, TU12, TU2, or TU3. Each VT group or TUG2 can be configured

to carry one of four tributary types. TUG2s can be multiplexed into VC3s or

TUG3s. Each TUG3 can also be configured to carry a TU3.

•

Optionally frames to the H4 byte in the path overhead to determine tributary

multiframe boundaries. Internally generated H4 bytes with leading logic 1 bits

are inserted into the outgoing administrative units.

•

Verifies parity on the IC1J1 and ISPE signals and on the incoming data

stream and generates parity on the outgoing data stream.

•

Detects loss of pointer and re-acquisition for each tributary and optionally

generates interrupts. Loss of pointer detection can optionally generate

tributary path AIS.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

•

Allows insertion of all zeros or all ones tributary idle code with unequipped

indication and valid pointer into any tributary.

•

Allows insertion of tributary path AIS into any tributary.

•

Operates in conjunction with the PM5323 TSPP Triple SONET/SDH Payload

Processor and the PM5344 SONET/SDH Path Terminating Transceiver to

align tributaries such that they can be switched by the PM5371 TUDX

SONET/SDH Tributary Unit Cross-Connect.

•

Operates from a single 19.44 MHz clock.

•

Provides a generic 8-bit microprocessor bus interface for configuration,

control, and status monitoring.

•

Low power, +5 Volt, CMOS technology, TTL compatible inputs and outputs.

•

160 pin plastic quad flat pack (PQFP) package

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

2

APPLICATIONS

•

SONET and SDH Wideband Cross-Connects

•

SONET and SDH Add-Drop and Terminal Multiplexers

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

3

REFERENCES

1. American National Standard for Telecommunications - Digital Hierarchy Optical Interface Rates and Formats Specification, ANSI T1.105-1988.

2. CCITT Blue Book, Recommendation G.708 - "Network Node Interface For

The Synchronous Digital Hierarchy", Volume III, Fascicle III.4, 1988.

3. CCITT Blue Book, Recommendation G.709 - "Synchronous Multiplexing

Structure", Volume III, Fascicle III.4, 1988.

4. CCITT Study Group XVIII, Report R 33 - "Recommendations Drafted By

Working Party XVIII/7" (Digital Hierarchies) To Be Approved In 1990 Including

Revised Draft Recommendations G.708 and G.709", June 1990.

5. Bell Communications Research - SONET Transport Systems: Common

Generic Criteria, TR-TSY-000253, Issue 2, December 1991.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

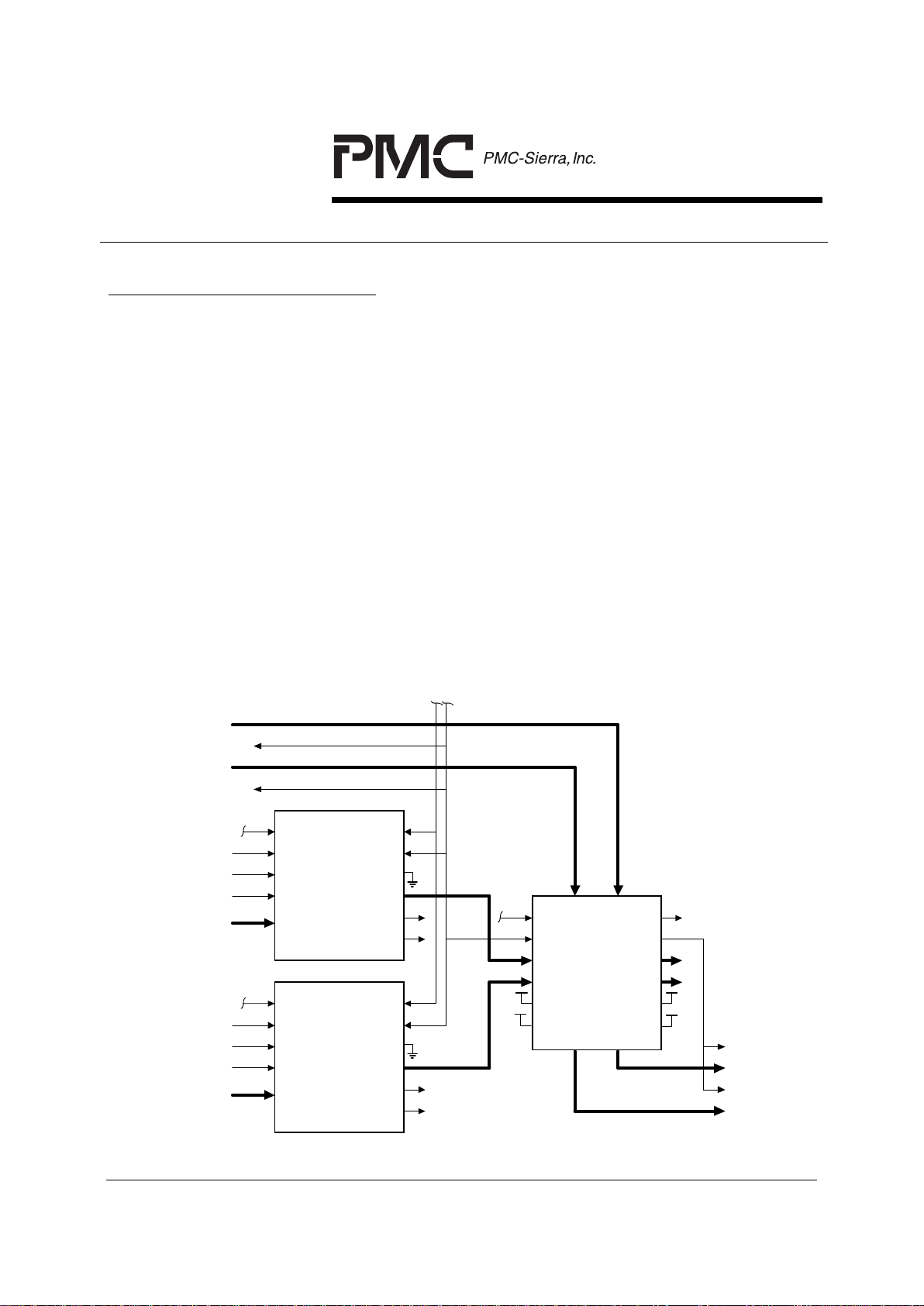

4

APPLICATION EXAMPLE

The PM5361 TUPP is typically used as part of a SONET/SDH tributary crossconnect. TUPPs can be used to transfer the payloads of incoming tributaries into

outgoing tributaries that are aligned to facilitate switching. A typical example is

shown below.

This example shows the tributaries extracted from an STS-1 or AU3 path

terminating device, such as the PM5344 SPTX SONET/SDH Path Terminating

Transceiver, being routed through TUPPs so as to be aligned for crossconnection using the PM5371 TUDX SONET/SDH Tributary Unit Cross-Connect.

The TUPP (and SPTX) can be bypassed by switching through whole STS-1s or

AU3s that are output by the PM5323 TSPP Triple SONET/SDH Payload

Processor. Note that in this application example, the TUPPs are operating in

locked output mode (i.e. their OJ1EN bits are low) to allow convenient interfacing

to the TUDX chip.

Figure 1 - SONET/SDH Tributary Cross-Connect Application

PM5361

TUPP

ISPE OSPE

ITMF DOUT/OPAR

OTSPE

IC1J1

SCLK

OC1J1

OTMF

OTV5

SINL

DOUTL

DINL

SOUTL

OFSEB

DINR

SOUTR

ODEB

SFP

SCLK

OFP

IFP

SINR

DOUTR

From PM5344

SPTX #2

From PM5344

SPTX #1

From PM5344

SPTX #1

From PM5344

SPTX #2

To PM5344

SPTX #2

To PM5344

SPTX #1

DIN/IPAR

ISPE OSPE

ITMF

DOUT/OPAR

OTSPE

IC1J1

SCLK

OC1J1

OTMF

OTV5

DIN/IPAR

SOBEB AOBEB

PM5371

TUDX

PM5361

TUPP

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

5

BLOCK DIAGRAM

Figure 2 - Overall Device

RSTB

CSB

RDB

WRB

ALE

A[7:0]

MBEB

D[7:0]

DIN[7:0]

SCLK

IC1J1

TRIBUTARY

PAYLOAD

PROCESSOR

INPUT

DEMUX

MICRO-

PROCESSOR

INTERFACE

ISPE

TRIBUTARY

PAYLOAD

PROCESSOR

TRIBUTARY

PAYLOAD

PROCESSOR

OUTPUT

MUX

DOUT[7:0]

OTMF

OC1J1

OSPE

OTSPE

OTV5

INTB

ITMF

IPAR

OPAR

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

Figure 3 - Each Tributary Payload Processor

OTV5

OTSPE

DIN[7:0]

OSPE

POINTER

INTERPRETER

RSTB

TSTB

BSB

RDB

WRB

TRSB

A[4:0]

D[7:0]

COMMON

BUS

INTERFACE

PAYLOAD

BUFFER

POINTER

GENERATOR

INCOMING

TIMING

GENERATOR

OUTGOING

TIMING

GENERATOR

INCOMING

MULTIFRAME

DETECTOR

CLOCK

GENERATOR

IC1J1

ISPE

SCLK

TO ALL BLOCKS

IOCLK

DTMF

DOUT[7:0]

OC1J1

OTMF

INT

NOFILT

ITUG3

ITMF

TU3

OTUG3

TRIG

OOF

ICODE1

ICODE

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

6

DESCRIPTION

The PM5361 TUPP SONET/SDH Tributary Unit Payload Processor is a

monolithic integrated circuit that implements a configurable, multi-channel,

payload processor for alignment of SONET virtual tributaries (VTs) or SDH

tributary units (TUs.)

When configured for SONET compatible operation, the TUPP transfers all

tributaries in the three STS-1 synchronous payload envelopes of an incoming

STS-3 byte serial stream to the three STS-1 synchronous payload envelopes of

an outgoing STS-3 byte serial stream. Similarly, when configured for SDH

compatible operation, the TUPP transfers all tributaries in the single AU4 or three

AU3 administrative units of an incoming STM-1 byte serial stream to a single

AU4 or three AU3 administrative units of an outgoing STM-1 byte serial stream.

The TUPP compensates for pleisiochronous relationships between incoming and

outgoing higher level (STS-1, AU4, AU3) synchronous payload envelope frame

rates through processing of the lower level (VT6, VT3, VT2, VT1.5, TU3, TU2,

TU12, TU11) tributary pointers.

The TUPP is configurable to process any legal mix of tributaries. Each VT group

can be configured to carry any one of the four tributary types (VT1.5, VT2, VT3,

or VT6) and each TUG2 can be configured to carry any one of three tributary

types (TU11, TU12, or TU2). TUG2s can be multiplexed into a VC3 or a TUG3.

Alternatively, each TUG3 can be configured to carry a TU3.

The TUPP operates in conjunction with the PM5323 TSPP Triple SONET/SDH

Payload Processor and the PM5344 SONET/SDH Path Terminating Transceiver

to align tributaries such that they can be switched by the PM5371 TUDX

SONET/SDH Tributary Unit Cross-Connect.

The TUPP provides useful maintenance functions. They include detection of loss

of pointer and pointer re-acquisition for each tributary, and optional generation of

interrupts. The TUPP also allows insertion of tributary path AIS or tributary idle

(unequipped). The TUPP can also insert inverted new data flag fields that can

be used to diagnose downstream pointer processing elements.

No auxiliary high speed clocks are required as the TUPP operates from a single

19.44 MHz line rate clock. The TUPP is configured, controlled and monitored via

a generic 8-bit microprocessor bus interface.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

The TUPP is implemented in low power, +5 Volt, CMOS technology. It has TTL

compatible inputs and outputs and is packaged in a 160 pin PQFP package.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

7

PIN DIAGRAM

The TUPP is packaged in an 160 pin PQFP package having a body size of

28 mm by 28 mm and a pin pitch of 0.65 mm.

PM5361

TUPP

VSST

NC

ALE

NC

RDB/E

NC

WRB/RWB

VSST

VSST

NC

OTV5

NC

OTSPENCOSPE

VDDI

NC

NC

VSST

VSST

VSST

NC

NC

VDDI

VDDO

SCLK

VSSO

VSSI

NCNCNC

VSST

VSST

VSST

VSST

NC

NC

DNC (ODV)

NC

VDDO

VSSO

NC

DOUT[0]

NC

DOUT[1]

NC

OPAR

VSST

VSST

VSST

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

(A[8]) DNC

CSB

MBEB

VSST

NC

DIN[0]

NC

ITMF

NC

VSSI

NC

ISPE

NC

VDDI

VSST

VSST

VSST

NC

NCNCNC

DOUT[2]D[0]

D[1]

D[2]

D[3]

DIN[1]NCDIN[2]

NC

DOUT[3]

NC

NC

IC1J1

NCNCNC

VSSO

VDDO

VDDI

VSSI

VSSO

D[4]

NC

VDDO

VDDI

VSSI

VSSO

NC

DIN[3]NCDIN[4]

NC

D[5]

D[6]

D[7]

NC

INTB

VSSO

NC

DOUT[4]

DIN[5]NCDIN[6]NCDIN[7]

NC

IPAR

NC

NC

DOUT[5]

NC

DOUT[6]

NC

DOUT[7]

NC

VDDO

VSSO

VSSI

OC1J1NCOTMF

NC

VSST

VSST

RSTB

VSST

NC

VDDO

VSSO

NC

DNC (IMFA)

VSST

VSST

VDDI

NC

VSSI

NCNCNC

VSST

VSST

PIN 1

PIN 160

PIN 121

PIN 120

PIN 40

PIN 41

PIN 80

Index

PIN 81

(TOP VIEW)

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

8

PIN DESCRIPTION

Pin Name Type Pin

No.

Function

SCLK Input 153 The system clock (SCLK) provides timing for

TUPP internal operation. SCLK is a 19.44 MHz,

nominally 50% duty cycle clock.

VCLK The test vector clock (VCLK) signal is used

during TUPP production testing to verify internal

functionality.

IC1J1 Input 44 The input C1/J1 frame pulse (IC1J1) identifies

the transport envelope and synchronous payload

envelope frame boundaries on the DIN[7:0] bus.

IC1J1 is set high while ISPE is low to mark the

first C1 byte of the transport envelope frame on

the DIN[7:0] bus. IC1J1 is set high while ISPE is

high to mark each of the J1 bytes of the

synchronous payload envelope(s) on the

DIN[7:0] bus. IC1J1 must be present at every

occurrence of the first C1 and all J1 bytes. The

TUPP will ignore a pulse on IC1J1 at the byte

position of the V1 byte of the first tributary of

each TUG3 or VC3. IC1J1 is sampled on the

rising edge of SCLK.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

Pin Name Type Pin

No.

Function

ITMF Input 52 The active high incoming tributary multiframe

(ITMF) signal identifies the first frame of the

tributary multiframe for each STS-1 synchronous

payload envelope, AU3, or AU4 administrative

unit. ITMF is enabled by the setting the ITMFEN

register bit high. When ITMFEN bit is low, the

path overhead H4 byte is used to determine

tributary multiframe boundaries. ITMF is

selectable to pulse high during the V1 byte of the

first tributary or during the H4 byte which

indicates that the next frame is the first frame of

the tributary multiframe. Selection between

marking V1 or H4 bytes is controlled by the

ITMFH4 register bit. Pulses on ITMF are only

effective during the H4 or V1 byte positions, as

appropriate. ITMF is ignored at other byte

positions. The ITMFEN and ITMFH4 bits are

located in the master incoming configuration

register. ITMF is sampled on the rising edge of

SCLK.

ISPE Input 48 The active high incoming synchronous payload

envelope (ISPE) signal identifies the bytes within

the transport envelope frame on the DIN[7:0] bus

that carry the AU3 or AU4 virtual containers, and

STS-1 synchronous payload envelopes. ISPE

must be brought high to mark each such byte.

ISPE is sampled on the rising edge of SCLK.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

Pin Name Type Pin

No.

Function

IPAR Input 70 The incoming stream parity (IPAR) signal carries

the parity of the incoming signals. The parity

calculation encompasses the IC1J1 signal, the

ISPE signal and the DIN[7:0] bus. IC1J1 and

ISPE can be included in the parity calculation by

setting the INCIC1J1 and INCISPE register bits

respectively high. Odd parity is selected by

setting the IOP register bit high, and even parity

is selected by setting the IOP bit low. The

INCIC1J1, INCISPE and IOP bits are located in

the master incoming configuration register. IPAR

is sampled on the rising edge of SCLK.

OC1J1 Input 127 The outgoing C1/J1 frame pulse (OC1J1) marks

the transport envelope and synchronous payload

envelope frame boundaries on the DOUT[7:0]

bus. When the OJ1EN register bit is set low,

OC1J1 pulses high to mark the first C1 byte of

the transport envelope frame on the DOUT[7:0]

bus. The position of the J1 bytes is implicit and

fixed to the bytes immediately following the last

C1 byte.

When the OJ1EN register bit is set high, the

OC1J1 signal pulses high while ISPE is low to

mark the first C1 byte of the transport envelope

frame on the DOUT[7:0] bus and pulses high

while OSPE is high to mark each of the J1 bytes

of the synchronous payload envelope(s) on the

DOUT[7:0] bus. OC1J1 must be present at every

occurrence of the first C1 byte and all J1 bytes.

A V1 pulse added to the OC1J1 input will be

ignored by the TUPP.

The OJ1EN bit is located in the master outgoing

configuration register. OC1J1 is sampled on the

rising edge of SCLK.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

Pin Name Type Pin

No.

Function

OTMF Input 125 The active high outgoing tributary multiframe

(OTMF) signal identifies the first frame of the

tributary multiframe for each AU3, or AU4

administrative unit, and STS-1 synchronous

payload envelope. OTMF is selectable to pulse

high during the V1 byte of the first tributary or

during the H4 byte of the path overhead which

indicates that the next frame is the first frame of

the tributary multiframe. Selection between

marking V1 or H4 bytes is controlled by the

OTMFH4 bit located in the master outgoing

configuration register. Pulses on OTMF are only

effective during the H4 or V1 byte positions, as

appropriate. OTMF is ignored at other byte

positions. OTMF is sampled on the rising edge

of SCLK.

OSPE Input 132 The active high outgoing synchronous payload

envelope (OSPE) signal identifies the bytes

within the transport envelope frame on the

DOUT[7:0] bus that carry the AU3 or AU4 virtual

container(s), and the STS-1 synchronous

payload envelopes. When the OJ1EN register bit

is set high, OSPE must be set high to mark each

such byte. When the OJ1EN bit is set low, the

outgoing virtual container (synchronous payload

envelope) is locked with the J1 byte immediately

following the C1 byte. OSPE is ignored.

DOUT[7:0], OTSPE, and OTV5 contain valid data

only for bytes in the AU3 or AU4 virtual

container(s), or the STS-1 synchronous payload

envelopes. Their contents should be ignored for

bytes in the transport overhead. The OJ1EN bit

is located in the master outgoing configuration

register. OSPE is sampled on the rising edge of

SCLK.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

15

Pin Name Type Pin

No.

Function

DIN[0]

DIN[1]

DIN[2]

DIN[3]

DIN[4]

DIN[5]

DIN[6]

DIN[7]

Input 54

56

58

60

62

64

66

68

The data input bus (DIN[7:0]) carries

SONET/SDH frame data in byte serial format.

DIN[7] is the most significant bit, corresponding

to bit 1 of each serial word, the bit transmitted

first. DIN[0] is the least significant bit,

corresponding to bit 8 of each serial word, the

last bit transmitted. The DIN[7:0] bus is sampled

on the rising edge of SCLK.

DOUT[0]

DOUT[1]

DOUT[2]

DOUT[3]

DOUT[4]

DOUT[5]

DOUT[6]

DOUT[7]

Output 110

108

106

104

97

95

93

91

The data output bus (DOUT[7:0]) carries

SONET/SDH frame data in byte serial format.

DOUT[7] is the most significant bit,

corresponding to bit 1 of each serial word, the bit

transmitted first DOUT[0] is the least significant

bit, corresponding to bit 8 of each serial word,

the last bit transmitted. DOUT[7:0] contains valid

data only for bytes in the AU3 or AU4 virtual

container(s), or the STS-1 synchronous payload

envelopes. Its contents should be ignored for

bytes in the transport overhead. The DOUT[7:0]

bus is updated on the rising edge of SCLK.

OPAR Output 89 The outgoing stream parity (OPAR) signal carries

the parity of the outgoing data stream. Odd

parity is selected by setting the OOP register bit

in the master parity configuration register high,

and even parity is selected by setting the OOP

bit low. OPAR is updated on the rising of SCLK.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

Pin Name Type Pin

No.

Function

OTSPE Output 134 The outgoing tributary synchronous payload

envelope (OTSPE) signal marks the bytes

carrying the tributary synchronous payload

envelope(s). OTSPE is set high to mark each

such byte on the DOUT[7:0] bus. OTSPE,

contains valid data only for bytes in the AU3 or

AU4 virtual container(s), or the STS-1

synchronous payload envelopes. Its contents

should be ignored for bytes in the transport

overhead. OTSPE is updated on the rising edge

of SCLK.

OTV5 Output 136 The outgoing tributary V5 byte (OTV5) signal

marks the various tributary V5 bytes. OTV5 is set

high to mark each tributary V5 byte on the

DOUT[7:0] bus. When the output tributary is a

TU3, OTV5 marks the J1 byte of the TU3. OTV5

contains valid data only for bytes in the AU3 or

AU4 virtual container(s), or the STS-1

synchronous payload envelopes. Its contents

should be ignored for bytes in the transport

overhead. OTV5 is updated on the rising edge of

SCLK.

MBEB Input 14 The active low Motorola bus enable (MBEB)

signal configures the TUPP for Motorola bus

mode where the RDB/E signal functions as E,

and the WRB/RWB signal functions as RWB.

When MBEB is high, the TUPP is configured for

Intel bus mode where the RDB/E signal functions

as RDB. The MBEB input has an integral pull up

resistor.

CSB Input 13 The active low chip select (CSB) signal is low

during TUPP register accesses.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

17

Pin Name Type Pin

No.

Function

RDB/ Input 35 The active low read enable (RDB) signal is low

during TUPP register read accesses while in

Intel bus mode. The TUPP drives the D[7:0] bus

with the contents of the addressed register while

RDB and CSB are low.

E The active high external access (E) signal is high

during TUPP register access while in Motorola

bus mode.

WRB/ Input 37 The active low write strobe (WRB) signal is low

during a TUPP register write accesses while in

Intel bus mode. The D[7:0] bus contents are

clocked into the addressed register on the rising

WRB edge while CSB is low.

RWB The read/write select (RWB) signal selects

between TUPP register read and write accesses

while in Motorola bus mode. The TUPP drives

the D[7:0] bus with the contents of the addressed

register while CSB is low and RWB and E are

high. The D[7:0] bus contents are clocked into

the addressed register on the falling E edge

while CSB and RWB are low.

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

I/O 15

16

17

18

23

24

25

26

The bidirectional data bus D[7:0] is used during

TUPP register read and write accesses.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

18

Pin Name Type Pin

No.

Function

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

Input 4

5

6

7

8

9

10

The address bus A[7:0] selects specific registers

during TUPP register accesses.

A[7]/TRS 11 The test register select (TRS) signal selects

between normal and test mode register

accesses. TRS is high during test mode register

accesses, and is low during normal mode

register accesses. TRS has an integral pull down

resistor.

RSTB Input 31 The active low reset (RSTB) signal provides an

asynchronous TUPP reset. RSTB is a Schmitt

triggered input with an integral pull up resistor.

ALE Input 33 The address latch enable (ALE) is active high

and latches the address bus A[7:0] when low.

When ALE is high, the internal address latches

are transparent. It allows the TUPP to interface

to a multiplexed address/data bus. ALE has an

integral pull up resistor.

INTB OD

Output

28 The active low interrupt (INTB) signal goes low

when a TUPP interrupt source is active. INTB

returns high when the interrupt is acknowledged

via an appropriate register access. INTB is an

open drain output.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

19

Pin Name Type Pin

No.

Function

VDDI1

VDDI2

VDDI3

VDDI4

VDDI5

VDDI6

Power 20

46

72

101

131

155

The core power (VDDI1 - VDDI6) pins should be

connected to a well decoupled +5 V DC in

common with VDDO.

VSSI1

VSSI2

VSSI3

VSSI4

VSSI5

VSSI6

Ground 21

50

74

100

128

151

The core ground (VSSI1 - VSSI6) pins should be

connected to GND in common with VSSO.

VDDO1

VDDO2

VDDO3

VDDO4

VDDO5

VDDO6

Power 19

87

102

113

130

154

The pad ring power (VDDO1 - VDDO6) pins

should be connected to a well decoupled +5 V

DC in common with VDDI.

VSSO1

VSSO2

VSSO3

VSSO4

VSSO5

VSSO6

VSSO7

VSSO8

Ground 22

29

86

99

112

129

138

152

The pad ring ground (VSSO1 - VSSO8) pins

should be connected to GND in common with

VSSI.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

20

Pin Name Type Pin

No.

Function

VSST1

VSST2

VSST3

VSST4

VSST5

VSST6

VSST7

VSST8

VSST9

VSST10

VSST11

VSST12

VSST13

VSST14

VSST15

VSST16

VSST17

VSST18

VSST19

VSST20

VSST21

VSST22

VSST23

VSST24

Ground 1

2

3

38

39

40

41

42

43

78

79

80

81

82

83

118

119

120

121

122

123

158

159

160

The thermal ground (VSST1 - VSST24) pins

should be connected to GND in common with

VSSI and VSSO. They may also be left floating.

The VSST pins may be electrically connected

together (fused) and connected to the back of

the die to improve the thermal characteristics of

the package.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

21

Notes on Pin Description:

1. All TUPP inputs and bidirectionals present minimum capacitive loading and

operate at TTL logic levels.

2. All TUPP digital outputs and bidirectionals have 4 mA drive capability.

3. The VSSO and VSSI ground pins are not internally connected together.

Failure to connect these pins externally may cause malfunction or damage

the TUPP.

4. The VDDO and VDDI power pins are not internally connected together.

Failure to connect these pins externally may cause malfunction or damage

the TUPP.

PM5361 TUPP

DATA SHEET

PMC-920526 ISSUE 8 TRIBUTARY UNIT PAYLOAD PROCESSOR

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

22

9

FUNCTIONAL DESCRIPTION

9.1 Input Bus Demultiplexer

The input bus demultiplexer captures data sampled on the DIN bus and

distributes this data to the three tributary payload processors within the TUPP.

The input bus demultiplexer also provides timing signals for the other blocks

within the TUPP. The system clock, SCLK, is buffered and distributed to the

tributary payload processors and the output bus multiplexer. Frame alignment

signals for the incoming data stream, IC1J1, ITMF, and ISPE, are sampled,

buffered and distributed to the tributary payload processors (TPPs). In order to

have synchronous operation of the TPPs with a single clock, the incoming data

and control signals may be delayed by up to two system clock cycles before

distribution to the TPP. The delay is used to align the incoming data with the

outgoing data at each TPP. The amount of delay is adjusted such that the

separation of the incoming STS/AU frame and the outgoing frame at each TPP

appears to be in multiples of three SCLK periods.

When configured for AU4 mode, the input bus demultiplexer provides the

necessary timing coordination between the three tributary payload processors.

The single J1 byte marker input on IC1J1 is retimed and distributed to each of

the three tributary payload processors. The tributary multiframe detected by

TPP #1 is distributed to the two other TPPs, as TPP #1 is the only one receiving

a valid H4 byte.

9.2 Output Bus Multiplexer

The output bus multiplexer gathers data from the three tributary payload

processors within the TUPP and multiplexes this data onto the DOUT[7:0] bus. It

also multiplexes signals from each tributary payload processor that mark tributary

SPEs and tributary V5 bytes onto the shared OTSPE and OTV5 signals.

The output bus multiplexer also provides timing signals for other blocks within the

TUPP. Frame alignment signals for the outgoing data stream, OC1J1, OSPE and

OTMF, are sampled, buffered and distributed to the tributary payload processors

(TPPs). The output bus multiplexer contains a four frame counter that will

flywheel in the absence of an active OTMF input, internally generating tributary

multiframe timing for the outgoing data stream. When configured for locked

output mode, i.e. when OJ1EN is low, the output bus multiplexer will internally

Loading...

Loading...