PM5349

PMC-Sierra,Inc.

Quad 155 Mb/s ATM Physical Layer Device

S/UNI-155-QUAD

PMC-980863 (R3) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 1999 PMC-Sierra, Inc.

FEATURES

• Quad-channel ATM OC-3c

(155 Mb/s) PHY.

• Provides on-chip clock and data

recovery and clock synthesis.

• Exceeds Bellcore-GR-253 jitter

requirements.

• Provides a generic 8-bit

microprocessor interface for device

control and register access.

• Provides standard IEEE 1149.1 JTAG

test port for boundary scan.

SONET RECEIVER

• Recovers clock and data.

• Frames to and desc rambl es recove red

stream.

• Filters and captures Automatic

Protection Switch (APS) byes (K1, K2)

and detects APS byte failure.

• Detects signal degrade and signal

failure threshold crossing alarms.

• Captures and debounces

synchronization status byte (S1).

• Counts received section BIP-8 (B1),

line BIP-24 (B2), and BIP-8 (B3)

errors, and line and path FEBEs.

• Detects LOS, OOF, LOF, LAIS, LRDI,

LOP, PAIS, PRDI, and PERDI.

• Provides individual divide by eight

recovered clocks for each channel.

• Provides individual 8 kHz receive

frame pulses for each channel.

SONET TRANSMITTER

• Synthesizes the 155.52 MHz trans mit

clock from a 19.44 MHz reference.

• Provides a single transmit frame pulse

input to align the transport frames to a

system reference.

• Provides single transmit clock as

timing reference for transmit outputs.

• Inserts register pr ogrammable APS

(K1 and K2) and synchronization

status (S1) bytes.

• Inserts PAIS, PRDI, LAIS, and LRDI.

• Scrambles the transmit data stream .

ATM PROCESSOR

• Implements the ATM Forum User

Network Interface Specifica tion .

• Inserts and extracts ATM cell s into and

from the SONET SPE.

• Performs cell payload scrambling and

descrambling.

• Provides a UTOPIA Level 2-compliant

system inter face.

• Provides synchronous 4-cell transmit

and receive FIFO buffers.

PACKAGING

• Implemented in low power 3.3 V

CMOS technology.

• Packaged in a 304-pin Ball Grid Array

(BGA) package.

• Industrial temp. range (-40° to +85°C).

APPLICATIONS

• Enterprise and Edge ATM Switches

• ATM Switches and Hubs

• Multiprotocol Switches

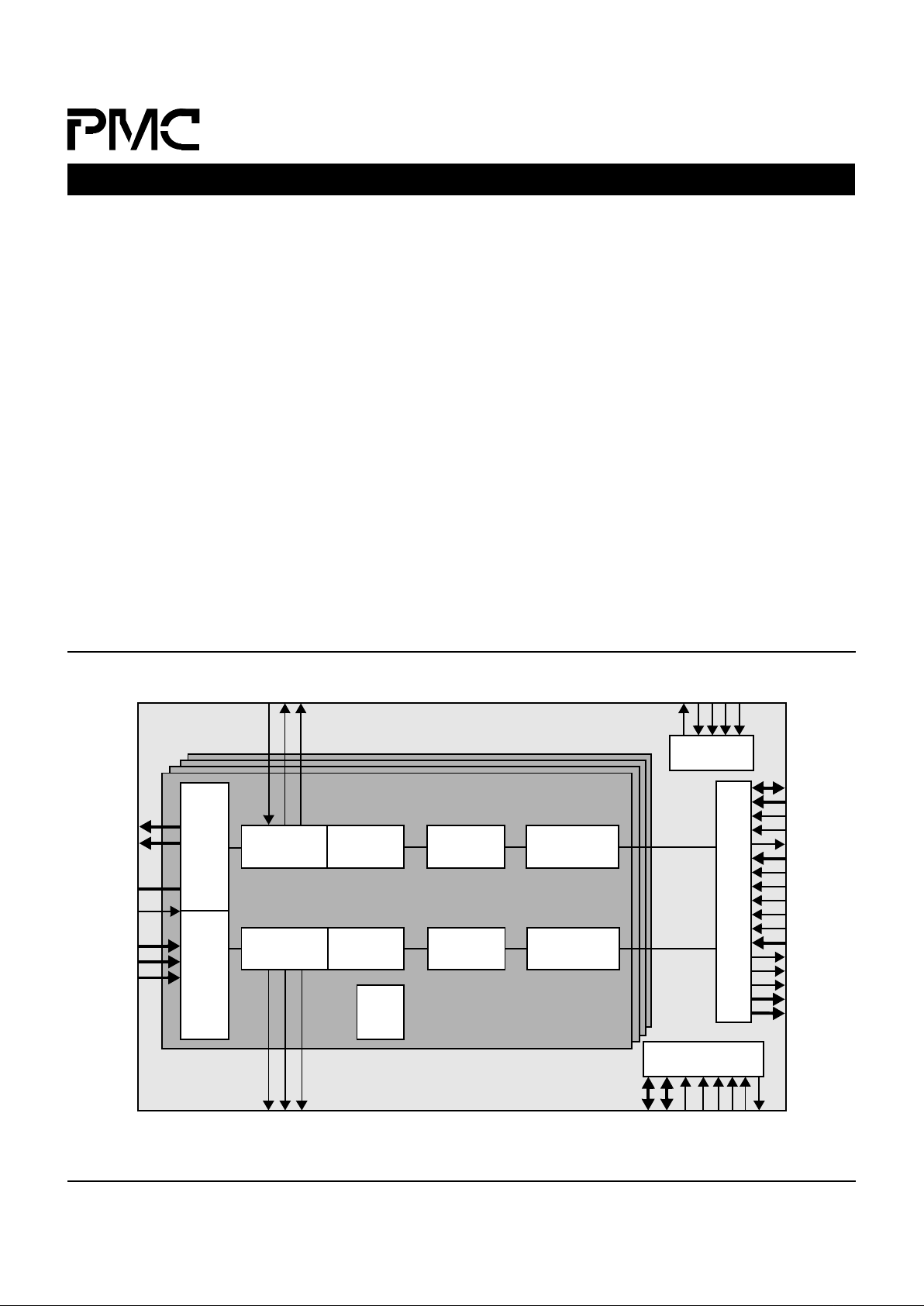

DRCA[4:1]

JTAG Test

Access Port

UTOPIA Level 2

System Interface

Transmit Path

O/H Processor

RDAT[15:0]

RPRTY

RSOC

RCA

RADR[4:0]

RENB

RFCLK

PHY_OEN

TFCLK

TENB

TADR[4:0]

TCA

TSOC

TPRTY

TDAT[15:0]

DTCA[4:1]

Receive Path

O/H Processor

Transmit Section

O/H Processor

Transmit Line

O/H Processor

Receive Line

O/H Processor

RALRM[4:1]

RFPO[4:1]

RCLK[4:1]

TXD[4:1]+

TXD[4:1]-

ATB[3:0]

REFCLK

RXD[4:1]+

RXD[4:1]-

SD[4:1]

TRSTB

TCK

TMS

TDI

TDO

D[7:0]

A[10:0]

ALE

CSB

WRB

RDB

RSTB

INTB

Microprocessor

Interface

Transmit

Line

Interface

Receive

Line

Interface

Transmit ATM

Cell Processor

Receive

APS,

Sync,

BERM

Receive Section

O/H Processor

TCLK

TFPO

TFPI

Receive ATM

Cell Processor

BLOCK DIAGRAM

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

PM5349 S/UNI-155-QUAD

Quad 155 Mb/s ATM Physical Layer Device

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

PMC-980863 (R3)

1999 PMC-Sierra, Inc.

August, 1999

SATURN and S/UNI-155-QUAD

are trademarks of PMC-Sierra,

Inc.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

TYPICAL APPLICATION

STS-3c (STM-1) ATM SWITCH PORT APPLICATION

SD4

Optical

Transceiver

Optical

Transceiver

UTOPIA Level 2

Interface

TxClk

ATM Layer Device

TxEnb

TxAddr[4:0]

TxClav

TxSOC

TxPrty

TxData[15:0]

RxClk

RxEnb

RxAddr[4:0]

RxClav

RxSOC

RxPrty

RxData[15:0]

RXD4+/-

TXD4+/-

Optical

Transceiver

Optical

Transceiver

TFCLK

PM5349

681,48$'

Quad 155 Mb/s ATM

Physical Layer Device

TENB

TADR[4:0]

TCA

TSOC

TPRTY

TDAT[15:0]

RFCLK

RENB

RADR[4:0]

RCA

RSOC

RPRTY

RDAT[15:0]

SD3

RX3+/-

TXD3+/-

SD2

RX2+/-

TXD2+/-

SD1

RX1+/-

TXD1+/-

Loading...

Loading...