PMC-Sierra,Inc.

PM5351

S/UNI-155-TETRA

Quad 155 Mbit/s ATM and Packet Over SONET/SDH Physical Layer Device

FEATURES

• Quad channel ATM and Packet over

SONET OC-3c (155 Mbit/s) PHY.

• Provides on-chip clock and data

recovery and clock synthe sis.

• Exceeds Bellcore-GR-253 jitter

requirements.

• Inserts and extracts ATM cells or POS

packets into/from SONET SPE.

• Filters and captures Automatic

Protection Switch byes (K1 and K2)

and detects APS byte failure.

• Detects signal degrade and signal

failure thresholds crossing alarms.

• Captures and debounces

synchronization status byte (S1).

• Extracts and inserts the 16- or 64-byte

section trace (J0) and path trace (J1)

messages.

• Extracts and inserts section/line data

communication channels (DCC).

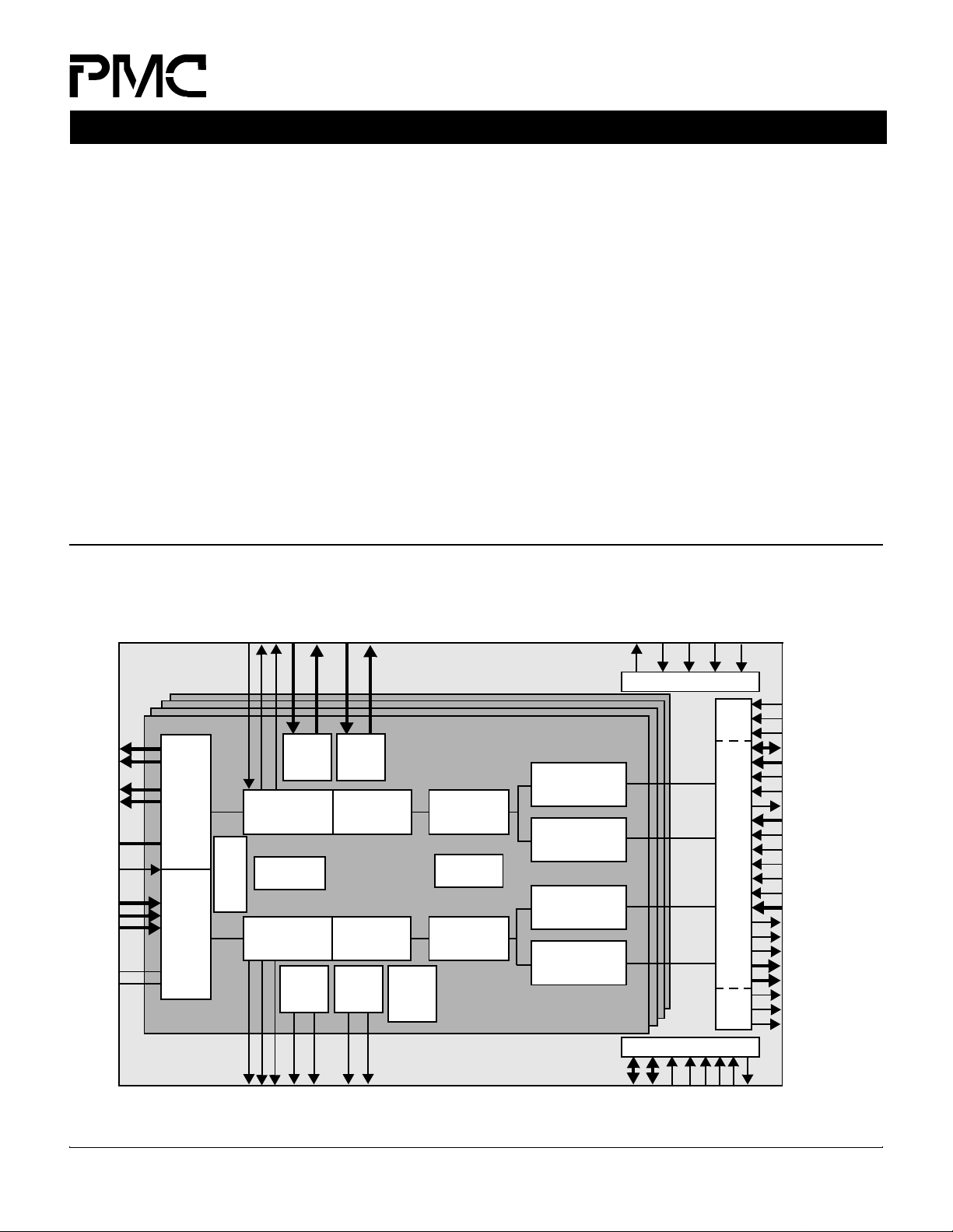

BLOCK DIAGRAM

• Provides circuitry to meet holdover,

wander and long term stability.

• Provides a generic 8-bit

microprocessor interface for device

control and register access.

• Provides standard IEEE 1149.1 JTAG

test port for boundary scan.

ATM

• Implements the ATM Forum User

Network Interface Specification.

• Performs cell payload scrambling and

descrambling.

• Provides a UTOPIA Level 2-compliant

system interface.

• Provides synchronous 4-cell transmit

and receive FIFO buffers.

PACKET OVER SONET

• Generic design that supports packet

based protocols like PPP, HDLC and

Frame Relay.

• Implements the PPP over SONET/

SDH specification according to RFC

1619 and 1662 of the IETF.

• Performs flag sequence detection and

insertion.

• Performs CRC-CCITT and CRC-32

FCS generation and validation.

• Performs byte stuffing and destuffing.

• Checks for mi nimum and maximum

packet lengths.

PACKAGING

• Low power, 3.3 V CMOS technology.

• Packaged in a 304-pin Ball Grid Array

(BGA) package.

• Industrial temp. range (-40° to +85°C).

APPLICATIONS

• WAN and Edge ATM Switches

• Multiprotocol Switches

• Layer 3 Switches

• Routers, Packet Switches, and Hubs

TXC[4:1]+

TXC[4:1]-

TXD[4:1]+

TXD[4:1]-

ATB[3:0]

REFCLK

RXD[4:1]+

RXD[4:1]-

SD[4:1]

CP[4:1]

CN[4:1]

Transmit

Line

Interface

Receive

Line

Interface

TFPI

TFPO

TCLK

Transmit Section

O/H Processor

Section

Trace Buffer

WAN

Synchronization

Receive Section

O/H Processor

TSD[4:1]

Section

DCC

Insert

Section

DCC

Extract

TSDCLK[4:1]

TLD[4:1]

Line

DCC

Insert

Transmit Line

O/H Processor

Receive Line

O/H Processor

Line

DCC

Extract

TLDCLK[4:1]

Receive

APS,

Sync,

BERM

Transmit Path

O/H Processor

Path Trace

Buffer

Receive Path

O/H Processor

Transmit ATM

Cell Processor

Transmit POS

Frame Processor

Receive POS

Frame Processor

Receive ATM

Cell Processor

TDO

TDI

TMS

TCK

JTAG Test Access Port

UTOPIA Level 2 /

Microprocessor Interface

TRSTB

TMOD

TERR

TEOP

DTCA[4:1]/DTPA[4:1]

TDAT[15:0]

TPRTY

TSOC/TSOP

TCA

TADR[4:0]

TENB

TFCLK

PHY_OEN

RFCLK

RENB

RADR[4:0]

RCA/RVAL

RSOC/RSOP

RPRTY

POS-PHY Level 2 System Interface

RDAT[15:0]

DRCA[4:1]/DRP[4:1]

REOP

RERR

RMOD

]

E

0

:

L

0

A

CSB

1

[

D[7:0]

RSD[4:1]

RCLK[4:1]

RFPO[4:1]

RALRM[4:1]

PMC-1980862 (R3) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 2001 PMC-Sierra, Inc.

RLD[4:1]

RSDCLK[4:1]

RLDCLK[4:1]

A

RDB

INTB

WRB

RSTB

Preliminary PM5351 S/UNI-TETRA

Quad 155 Mbit/s ATM and Packet Over SONET/SDH Physical Layer Device

TYPICAL APPLICATIONS

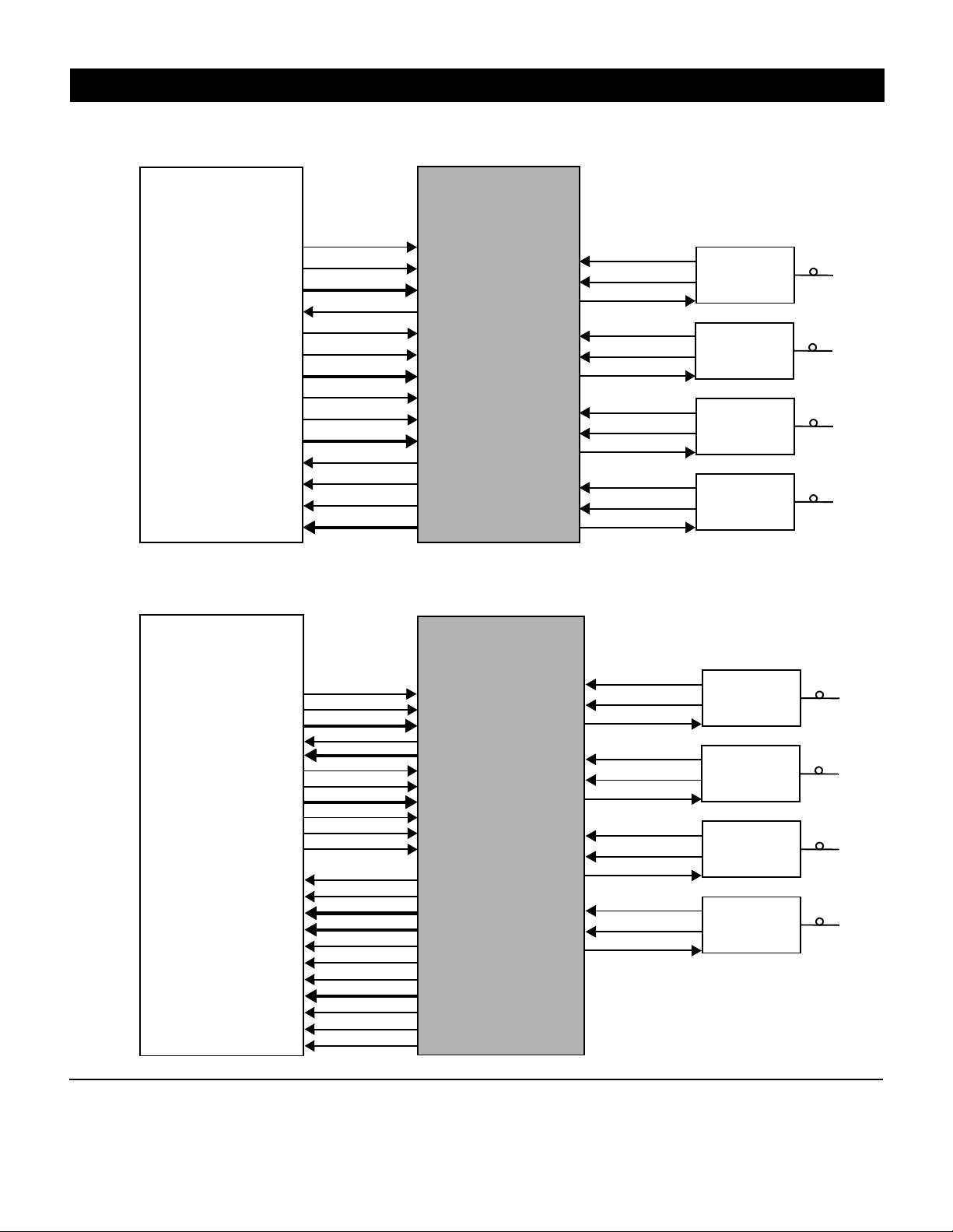

STS-3c (STM-1) ATM SWITCH PORT APPLICATION

ATM Layer Device

TxClk

TxEnb

TxAddr[4:0]

TxClav

TxSOC

TxPrty

TxData[15:0]

RxClk

RxEnb

RxAddr[4:0]

RxClav

RxSOC

RxPrty

RxData[15:0]

UTOPIA Level 2

Interface

SONET/SDH Physical

TFCLK

TENB

TADR[4:0]

TCA

TSOC

TPRTY

TDAT[15:0]

RFCLK

RENB

RADR[4:0]

RCA

RSOC

RPRTY

RDAT[15:0]

STS-3c (STM-1) PACKET OVER SONET APPLICATION

Link Layer Device

TFCLK

TENB

TADR[4:0]

STPA

DTPA[4:1]

TSOP

TPRTY

TDAT[15:0]

TMOD

TEOP

TERR

RFCLK

RENB

RADR[4:0]

DRPA[4:1]

RVAL

RSOP

RPRTY

RDAT[15:0]

RMOD

REOP

RERR

S/UNI

Quad 155 Mb/s ATM

SONET/SDH Physical

TFCLK

TENB

TADR[4:0]

STPA

DTPA[4:1]

TSOP

TPRTY

TDAT[15:0]

TMOD

TEOP

TERR

RFCLK

RENB

RADR[4:0]

DRPA[4:1]

RVAL

RSOP

RPRTY

RDAT[15:0]

RMOD

REOP

RERR

PM5351

®

-155-TETRA

S/UNI

Quad 155 Mb/s ATM

and Packet Over

Layer Device

PM5351

®

-155-TETRA

and Packet Over

Layer Device

RX1+/-

SD1

TXD1+/-

RX2+/-

SD2

TXD2+/-

RX3+/-

SD3

TXD3+/-

RXD4+/-

SD4

TXD4+/-

RX1+/-

SD1

TXD1+/-

RX2+/-

SD2

TXD2+/-

RX3+/-

SD3

TXD3+/-

RXD4+/-

SD4

TXD4+/-

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

PMC-1980862 (R3)

2001 PMC-Sierra, Inc. SATURN and

S/UNI-155-TETRA are trademarks of

PMC-Sierra, Inc.

Loading...

Loading...