PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

PM5350

S/UNI-

R

155-ULTRA

S/UNI-155-ULTRA

SATURN USER NETWORK INTERFACE

155.52 & 51.84 MBIT/S

DATA SHEET

ISSUE 5: JUNE 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

PUBLIC REVISION HISTORY

Issue No Date of issue Details of Change

5 June 1998 Data Sheet Reformatted — No Change in

Technical Content.

Generated R5 data sheet from PMC-969489, R7

4 November 1997 Eng Doc (7) revised.

3 Dec 20, 1996 Third Revision

2 Oct 15, 1996 Second Revision

1 Sept 12, 1996 Creation of Document

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................4

3 REFERENCES.........................................................................................5

4 APPLICATION EXAMPLES......................................................................6

5 BLOCK DIAGRAM....................................................................................7

6 PIN DIAGRAM........................................................................................10

7 PIN DESCRIPTION................................................................................11

7.1 UTP-5 AND PECL RECEIVER ....................................................27

7.2 CLOCK RECOVERY....................................................................27

7.3 SERIAL TO PA RALLEL CONVERTER.........................................28

7.4 RECEIVE SECTION OVERHEAD PROCESSOR........................28

7.4.1 FRAMER...........................................................................28

7.4.2 DESCRAMBLE .................................................................29

7.4.3 ERROR MONITOR............................................................29

7.4.4 LOSS OF SIGNAL ............................................................29

7.4.5 LOSS OF FRAME.............................................................30

7.5 RECEIVE LINE OVERHEAD PROCESSOR ...............................30

7.5.1 LINE REMOTE DEFECT INDICATION DETECT ..............30

7.5.2 LINE AIS DETECT............................................................30

7.5.3 ERROR MONITOR............................................................30

7.6 RECEIVE PATH OVERHEAD PROCESSOR...............................31

7.6.1 POINTER INTERPRETER................................................31

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

7.6.2 ERROR MONITOR............................................................32

7.7 RECEIVE ATM CELL PROCESSOR ...........................................32

7.7.1 CELL DELINEATION.........................................................32

7.7.2 DESCRAMBLER...............................................................33

7.7.3 CELL FILTER AND HCS VERIFICATION..........................34

7.7.4 PERFORMANCE MONITOR.............................................35

7.7.5 GFC EXTRACTION PORT................................................36

7.7.6 RECEIVE FIFO.................................................................36

7.8 UTP-5 AND PECL TRANSMITTER .............................................37

7.9 CLOCK SYNTHESIS...................................................................37

7.10 PARALLEL TO SERIAL CONVERTER.........................................37

7.11 TRANSMIT SECTION OVERHEAD PROCESSOR.....................37

7.11.1LINE AIS INSERT.............................................................37

7.11.2BIP-8 INSERT...................................................................37

7.11.3FRAMING AND IDENTITY INSERT..................................38

7.11.4SCRAMBLER....................................................................38

7.12 TRANSMIT LINE OVERHEAD PROCESSOR.............................38

7.12.1BIP CALCULATE...............................................................38

7.12.2LINE REMOTE DEFECT INDICATION INSERT................38

7.12.3LINE FEBE INSERT..........................................................39

7.13 TRANSMIT PATH OVERHEAD PROCESSOR ............................40

7.13.1POINTER GENERATOR...................................................40

7.13.2BIP-8 CALCULATE...........................................................41

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

7.13.3FEBE CALCULATE ...........................................................41

7.13.4SPE MULTIPLEXER..........................................................41

7.14 TRANSMIT ATM CELL PROCESSOR.........................................42

7.14.1IDLE/UNASSIGNED CELL GENERATOR.........................43

7.14.2SCRAMBLER....................................................................43

7.14.3HCS GENERATOR............................................................43

7.14.4GFC INSERTION PORT ...................................................43

7.14.5TRANSMIT FIFO...............................................................43

7.15 DROP SIDE INTERFACE............................................................44

7.15.1RECEIVE INTERFACE......................................................44

7.15.2TRANSMIT INTERFACE...................................................45

7.16 PARALLEL OUTPUT PORT AND LED DISPLAY CONTROLLER45

7.17 MICROPROCESSOR INTERFACE .............................................45

8 REGISTER MEMORY MAP....................................................................46

8.1 TEST MODE REGISTER MEMORY MAP.................................131

8.2 TEST MODE 0 DETAILS............................................................134

9 OPERATION.........................................................................................136

9.1 OVERHEAD BYTE USAGE.......................................................136

9.2 CELL DATA STRUCTURE..........................................................139

9.3 PARALLEL OUTPUT PORT AND LED DISPLAY CONTROLLER

OPERATION..............................................................................141

9.3.1 DIRECT CONTROL PARALLEL OUTPUT PORT ...........141

9.3.2 ALARM MONITOR..........................................................141

9.3.3 TRAFFIC MONITOR .......................................................141

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

9.4 LOOPBACK OPERATION..........................................................142

9.5 BOARD DESIGN RECOMMENDATIONS..................................146

9.6 POWER SUPPLIES SEQUENCING..........................................147

9.7 SELECTING BETWN TWISTED-PAIR AND PECL INTERFACES

...................................................................................................148

9.8 INTERFACING TRANSMIT AND RECEIVE DATA LINES WITH

PECL DEVICES.........................................................................148

9.9 INTERFACING TRANSMIT AND RECEIVE DATA LINES WITH

UTP-5 CABLE............................................................................151

9.10 CLOCKING OPTIONS...............................................................152

9.11 DROP SIDE RECEIVE INTERFACE..........................................154

9.12 DROP SIDE TRANSMIT INTERFACE .......................................156

10 ABSOLUTE MAXIMUM RATINGS........................................................158

11 D.C. CHARACTERISTICS ....................................................................159

12 EXTERNAL COMPONENTS................................................................164

13 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS......167

14 S/UNI-ULTRA TIMING CHARACTERISTICS........................................171

15 ORDERING AND THERMAL INFORMATION ......................................180

16 MECHANICAL INFORMATION.............................................................181

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

LIST OF REGISTERS

REGISTER 0X00: S/UNI-ULTRA MASTER RESET AND IDENTITY / LOAD

METERS.................................................................................................50

REGISTER 0X01: S/UNI-ULTRA MASTER CONFIGURATION ........................52

REGISTER 0X02: S/UNI-ULTRA MASTER INTERRUPT STATUS....................54

REGISTER 0X03: S/UNI-ULTRA MASTER MODE CONTROL.........................56

REGISTER 0X04: S/UNI-ULTRA MASTER CLOCK MONITOR........................57

REGISTER 0X05: S/UNI-ULTRA MASTER CONTROL.....................................59

REGISTER 0X06: S/UNI-ULTRA CLOCK SYNTHESIS CONTROL AND STATUS

................................................................................................................61

REGISTER 0X08: S/UNI-ULTRA CLOCK RECOVERY CONTROL AND STATUS

................................................................................................................62

REGISTER 0X09: S/UNI-ULTRA CLOCK RECOVERY CONFIGURATION ......64

REGISTER 0X0A: S/UNI-ULTRA LINE TRANSMITTER CONFIGURATION 1..6 5

REGISTER 0X0B: S/UNI-ULTRA LINE TRANSMITTER CONFIGURATION 2..6 6

REGISTER 0X0C: S/UNI-ULTRA LINE RECEIVER CONFIGURATION............67

REGISTER 0X10: RSOP CONTROL/INTERRUPT ENABLE............................68

REGISTER 0X11: RSOP STATUS/INTERRUPT STATUS .................................70

REGISTER 0X12: RSOP SECTION BIP-8 LSB................................................72

REGISTER 0X13: RSOP SECTION BIP-8 MSB...............................................73

REGISTER 0X14: TSOP CONTROL.................................................................74

REGISTER 0X15: TSOP DIAGNOSTIC............................................................75

REGISTER 0X18: RLOP CONTROL/STATUS...................................................76

REGISTER 0X19: RLOP INTERRUPT ENABLE/INTERRUPT STATUS...........77

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

REGISTER 0X1A: RLOP LINE BIP-8/24 LSB...................................................79

REGISTER 0X1B: RLOP LINE BIP-8/24...........................................................80

REGISTER 0X1C: RLOP LINE BIP-8/24 MSB..................................................81

REGISTER 0X1D: RLOP LINE FEBE LSB .......................................................82

REGISTER 0X1E: RLOP LINE FEBE ...............................................................83

REGISTER 0X1F: RLOP LINE FEBE MSB.......................................................84

REGISTER 0X20: TLOP CONTROL.................................................................85

REGISTER 0X21: TLOP DIAGNOSTIC ............................................................86

REGISTER 0X30: RPOP STATUS/CONTROL..................................................87

REGISTER 0X31: RPOP INTERRUPT STATUS ...............................................88

REGISTER 0X33: RPOP INTERRUPT ENABLE..............................................89

REGISTER 0X37: RPOP PATH SIGNAL LABEL...............................................91

REGISTER 0X38: RPOP PATH BIP-8 LSB .......................................................92

REGISTER 0X39: RPOP PATH BIP-8 MSB ......................................................93

REGISTER 0X3A: RPOP PATH FEBE LSB.......................................................94

REGISTER 0X3B: RPOP PATH FEBE MSB......................................................95

REGISTER 0X3D: RPOP PATH BIP-8 CONFIGURATION................................96

REGISTER 0X40: TPOP CONTROL/DIAGNOSTIC..........................................97

REGISTER 0X41: TPOP POINTER CONTROL................................................98

REGISTER 0X45: TPOP ARBITRARY POINTER LSB ...................................100

REGISTER 0X46: TPOP ARBITRARY POINTER MSB ..................................101

REGISTER 0X48: TPOP PATH SIGNAL LABEL .............................................102

REGISTER 0X49: TPOP PATH STATUS..........................................................103

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

REGISTER 0X50: RACP CONTROL/STATUS ................................................104

REGISTER 0X51: RACP INTERRUPT ENABLE/STATUS ..............................106

REGISTER 0X52: RACP MATCH HEADER PATTERN...................................108

REGISTER 0X53: RACP MATCH HEADER MASK.........................................109

REGISTER 0X54: RACP CORRECTABLE HCS ERROR COUNT..................110

REGISTER 0X55: RACP UNCORRECTABLE HCS ERROR COUNT ............111

REGISTER 0X56: RACP RECEIVE CELL COUNTER (LSB) .........................112

REGISTER 0X57: RACP RECEIVE CELL COUNTER....................................113

REGISTER 0X58: RACP RECEIVE CELL COUNTER (MSB).........................114

REGISTER 0X59: RACP CONFIGURATION ..................................................115

REGISTER 0X60: TACP CONTROL/STATUS..................................................117

REGISTER 0X61: TACP IDLE/UNASSIGNED CELL HEADER PATTERN......119

REGISTER 0X62: TACP IDLE/UNASSIGNED CELL PAYLOAD OCTET

PATTERN..............................................................................................120

REGISTER 0X63: TACP FIFO CONTROL.......................................................121

REGISTER 0X64: TACP TRANSMIT CELL COUNTER (LSB)........................123

REGISTER 0X65: TACP TRANSMIT CELL COUNTER..................................124

REGISTER 0X66: TACP TRANSMIT CELL COUNTER (MSB).......................125

REGISTER 0X67: TACP CONFIGURATION....................................................126

REGISTER 0X68: S/UNI-ULTRA POPC CONTROL.......................................128

REGISTER 0X69: S/UNI-ULTRA POPC STROBE RATE 0.............................130

REGISTER 0X6A: S/UNI-ULTRA POPC STROBE RATE 1.............................131

REGISTER 0X80: MASTER TEST..................................................................133

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

LIST OF FIGURES

FIGURE 1 - TYPICAL ATM ADAPTER UTP-5 INTERFACE..............................6

FIGURE 2 - STS-3C/STM-1JITTER TOLERANCE..........................................28

FIGURE 3 - CELL DELINEATION STATE DIAGRAM.......................................33

FIGURE 4 - HCS VERIFICATION STATE DIAGRAM.......................................35

FIGURE 5 - STS-3C/STM-1 DEFAULT TRANSPORT OVERHEAD VALUES ..39

FIGURE 6 - STS-1 DEFAULT TRANSPORT OVERHEAD VALUES................40

FIGURE 7 - DEFAULT PATH OVERHEAD VALUES.........................................42

FIGURE 8 - STS-3C (STM-1) OVERHEAD....................................................136

FIGURE 9 - STS-1 OVERHEAD ....................................................................137

FIGURE 10- DATA STRUCTURE....................................................................140

FIGURE 11- TWISTED-PAIR LOOPBACK OPERATION ................................143

FIGURE 12- LINE LOOPBACK OPERATION .................................................144

FIGURE 13- SERIAL DIAGNOSTIC LOOPBACK OPERATION.....................145

FIGURE 14- PARALLEL DIAGNOSTIC LOOPBACK OPERATION ................146

FIGURE 15- INTERFACING TXD+/- TO PECL ...............................................149

FIGURE 16- INTERFACING WITH RXD+/- USING PECL (2 EXAMPLES) ....150

FIGURE 17- INTERFACING TXD+/- AND RXD+/- WITH UTP-5.....................152

FIGURE 18- CONCEPTUAL CLOCKING STRUCTURE................................153

FIGURE 19- RECEIVE FIFO EMPTY OPTION (RCALEVEL0=1)..................154

FIGURE 20- RECEIVE FIFO NEAR EMPTY OPTION (RCALEVEL0=0) .......154

FIGURE 21- RECEIVE GFC SERIAL LINK ....................................................155

FIGURE 22- TRANSMIT FIFO........................................................................156

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

FIGURE 23- TRANSMIT GFC SERIAL LINK..................................................157

FIGURE 24- MICROPROCESSOR INTERFACE READ TIMING....................168

FIGURE 25- MICROPROCESSOR INTERFACE WRITE TIMING..................170

FIGURE 26- RECEIVE FRAME PULSE OUTPUT TIMING............................171

FIGURE 27- LINE SIDE TRANSMIT INTERFACE TIMING.............................172

FIGURE 28- DROP SIDE RECEIVE SYNCHRONOUS INTERFACE TIMING

(TSEN = 0) .....................................................................................................173

FIGURE 29- DROP SIDE RECEIVE SYNCHRONOUS INTERFACE TIMING

(TSEN = 1) .....................................................................................................175

FIGURE 30- GFC EXTRACT PORT TIMING..................................................176

FIGURE 31- DROP SIDE TRANSMIT SYNCHRONOUS INTERFACE...........177

FIGURE 32- GFC INSERT PORT TIMING......................................................178

FIGURE 33- THETA JA VS. AIR FLOW...........................................................180

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

LIST OF TABLES

TABLE 1 - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 24) .

.....................................................................................................167

TABLE 2 - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 25)

.....................................................................................................169

TABLE 3 - LINE SIDE REFERENCE CLOCK..............................................171

TABLE 4 - LINE SIDE RECEIVE INTERFACE (FIGURE 26).......................171

TABLE 5 - LINE SIDE TRANSMIT INTERFACE (FIGURE 27)....................172

TABLE 6 - DROP SIDE RECEIVE SYNCHRONOUS INTERFACE (TSEN = 0)

(FIGURE 28) ...................................................................................................172

TABLE 7 - DROP SIDE RECEIVE SYNCHRONOUS INTERFACE (TSEN = 1)

(FIGURE 29) ...................................................................................................174

TABLE 8 - GFC EXTRACT PORT (FIGURE 30)..........................................176

TABLE 9 - DROP SIDE TRANSMIT SYNCHRONOUS INTERFACE (FIGURE

31) .....................................................................................................176

TABLE 10 - GFC INSERT PORT (FIGURE 32).............................................178

TABLE 11 - S/UNI-ULTRA ORDERING INFORMATION ................................180

TABLE 12 - S/UNI-ULTRA THERMAL INFORMATION..................................180

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

1

FEATURES

Single chip ATM User-Network Interface operating at 155.52 and 51.84

•

Mbit/s.

Provides an Analog Edge Interface that can be selected to interface directly

•

with Category-5 Unshielded Twisted Pair (UTP-5) or Shielded Twisted Pair

cables, or to interface with Pseudo-ECL (PECL) optical data links (ODLs),

using a minimum of passive components.

Implements the ATM Forum User Network Interface Specification and the

•

ATM physical layer for Broadband ISDN according to CCITT

Recommendation I.432.

Processes duplex 155.52 Mbit/s STS-3c/STM-1 (direct interface to a twisted

•

pair cable or PECL interface to a PMD device) or 51.84 Mbit/s STS-1 (PECL

interface to a PMD device only) data streams with on-chip clock and data

recovery and clock synthesis.

Performs clock recovery and clock synthesis using on-chip loop filters.

•

Provides Saturn Compliant Inte rface - PHYsical layer (SCI-PHY™) FIFO

•

buffers in both transmit and receive paths with parity support. Compatible with

ATM Forum Utopia Level 1 specification.

Inserts and extracts the generic flow control (GFC) bits via a simple ser ial

•

interface and provides a transmit XOFF function to allow for local flow control.

Provides a generic 8-bit microprocessor bus interface for configuration,

•

control, and status monitoring.

Low power, +5 Volt, CMOS technology.

•

128 pin high performance plastic quad flat pack (PQFP) 14 mm x 20 mm

•

package.

The receiver section:

Provides a serial interface at 155.52 or 51.84 Mbit/s.

•

Adaptively equalizes the received differential signal.

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Recovers the clock and data; frames to the recovered data stream;

•

descrambles the received data; interprets the received payload pointer (H1,

H2); and extracts the STS-3c or STS-1 synchronous payload envelope (VC4)

and path overhead.

Extracts ATM cells from the synchronous payload envelope using ATM cell

•

delineation and provides optional ATM cell payload descrambling, header

check sequence (HCS) error detection and error correction, and

idle/unassigned cell filtering.

Provides a synchronous 8-bit wide, four cell FIFO buffer.

•

Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line

•

alarm indication signal (LAIS), line remote defect indication (RDI), loss of

pointer (LOP), path alarm indication signal (PAIS), loss of cell delineation and

path remote defect indication (PRDI).

Counts received section BIP-8 (B1) errors, received line BIP-8/24 (B2) errors,

•

line far end block errors (line FEBE), received path BIP-8 (B3) errors and path

far end block errors (path FEBE).

Counts received HCS errored cells that are discarded, received HCS errored

•

cells that are corrected and passed on, and the total received cells passed

on.

The transmitter section:

Provides a serial interface at 155.52 or 51.84 Mbit/s.

•

Provides a serial interface at 155.52 or 51.84 Mbit/s. Generates data of the

•

correct amplitude and shape to directly interface with a signal transformer and

transmit over a UTP-5 cable.

Provides a synchronous 8-bit wide, four cell FIFO buffer.

•

Provides idle/unassigned cell insertion, HCS generation/insertion, and ATM

•

cell payload scrambling; Inserts ATM cells into the transmitted STS-3c (STM-

1) or STS-1 synchronous payload envelope using H4 framing

Generates the transmit payload pointer (H1, H2) and inserts the path

•

overhead; scrambles the transmitted STS-3c (STM-1) or STS-1 stream and

inserts framing bytes (A1, A2) and the identity byte (C1).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Synthesizes the 155.52 MHz, 51.84 MHz transmit clock from a one-eighth

•

frequency reference.

Inserts path alarm indication signal (PAIS), path remote defect indication

•

(RDI), line alarm indication signal (LAIS) and line RDI.

Inserts path BIP-8 codes (B3), path far end block error (path FEBE)

•

indications, line BIP-8/24 codes (B2), line far end block error (line FEBE)

indications, section BIP-8 codes (B1) to allow performance monitoring at the

far end.

Allows forced insertion of all zeros data (after scrambling) or corruption of

•

framing byte or section, line, or path BIP-8 codes for diagnostic purposes.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

2

APPLICATIONS

ATM LANs over twisted pair cables (UTP-5) at155.52 Mbit/s

•

ATM LANs over optical fibers (using PECL ODLs) at either 155 Mbit/s or

•

51.84 Mbit/s

Workstations and Personal Computer NIC Cards

•

LAN switches and hubs

•

SONET or SDH compliant ATM User-Network Interfaces

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

3

REFERENCES

1. CCITT Recommendation G.709 - "Synchronous Multiplexing Structure",

1990.

2. CCITT Recommendation I.432, "B-ISDN User Network Interface - Physical

Interface Specification", June 1990.

3. Bell Communications Research - SONET Transport Systems: Common

Generic Criteria, GR-253-CORE, Issue 1, December 1994.

4. ATM Forum - ATM User-Network Interface Specification,V3.1, September

1994

5. ATM Forum - ATM Physical Medium Dependent Interface Specification for

155 Mbit/s over Twister Pair Cable, V1.0, September 1994

6. T1.105, American National Standard for Telecommunications - Digital

Hierarchy - Optical Interface Rates and Formats Specifications (SONET),

1991.

7. Telecommunications Industry Association (TIA), Commercial Building

Telecommunications Wiring Standard, EIA/TIA-568.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM5350 S/UNI-ULTRA

y

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

4

APPLICATION EXAMPLES

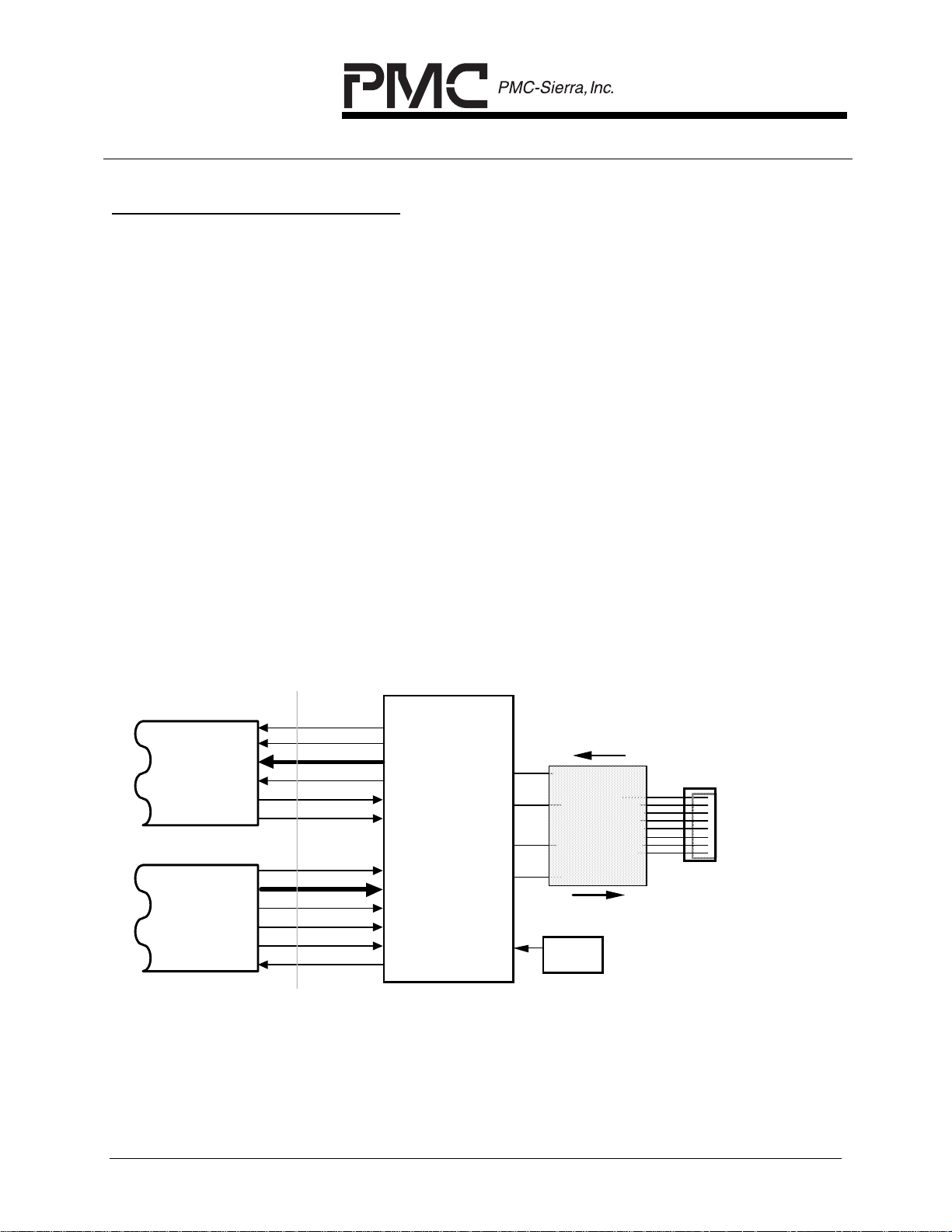

The PM5350 S/UNI-ULTRA is typically used to implement the core of an ATM

User Network Interface by which an ATM terminal is linked to an ATM switching

system using SONET/SDH compatible transport.

The S/UNI-ULTRA finds application at either end of terminal to switch links or

switch to switch links, typically in private network (LAN) applications. In this

application, the S/UNI-ULTRA typically interfaces on its line side with line

coupling transformers and baluns.

The S/UNI-ULTRA may be loop timed internally (the recovered clock is used in

the transmit direction) or source timed (separate transmit and receive clocks).

The drop side interfaces directly with ATM adaptation layer or ATM layer

processors. The initial configuration and ongoing control and monitoring of the

S/UNI-ULTRA is provided via a generic microprocessor interface. The S/UNIULTRA also supports a "hardware-only" operating mode where an exter nal

microprocessor is not required. This application is shown in Figure 1.

Figure 1 - Typical ATM Adapter UTP-5 Interface

Receive

AAL

Processor

ATM Terminal

Transmit

AAL

Processor

SCI-PHY

Interface

RXPRTY

RDAT[7:0]

RRDENB

TXPRTY

TDAT[7:0]

TFCLK

TWRENB

RCA

RSOC

RFCLK

TSOC

TCA

RXD+

RXD–

PM5350

S/UNI-155-ULTRA

TXD+

TXD–

REFCLK

Receive

MAGNETICS

Transmit

19.44 MHz

Oscillator

RJ-45

UTP-5 Facilit

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

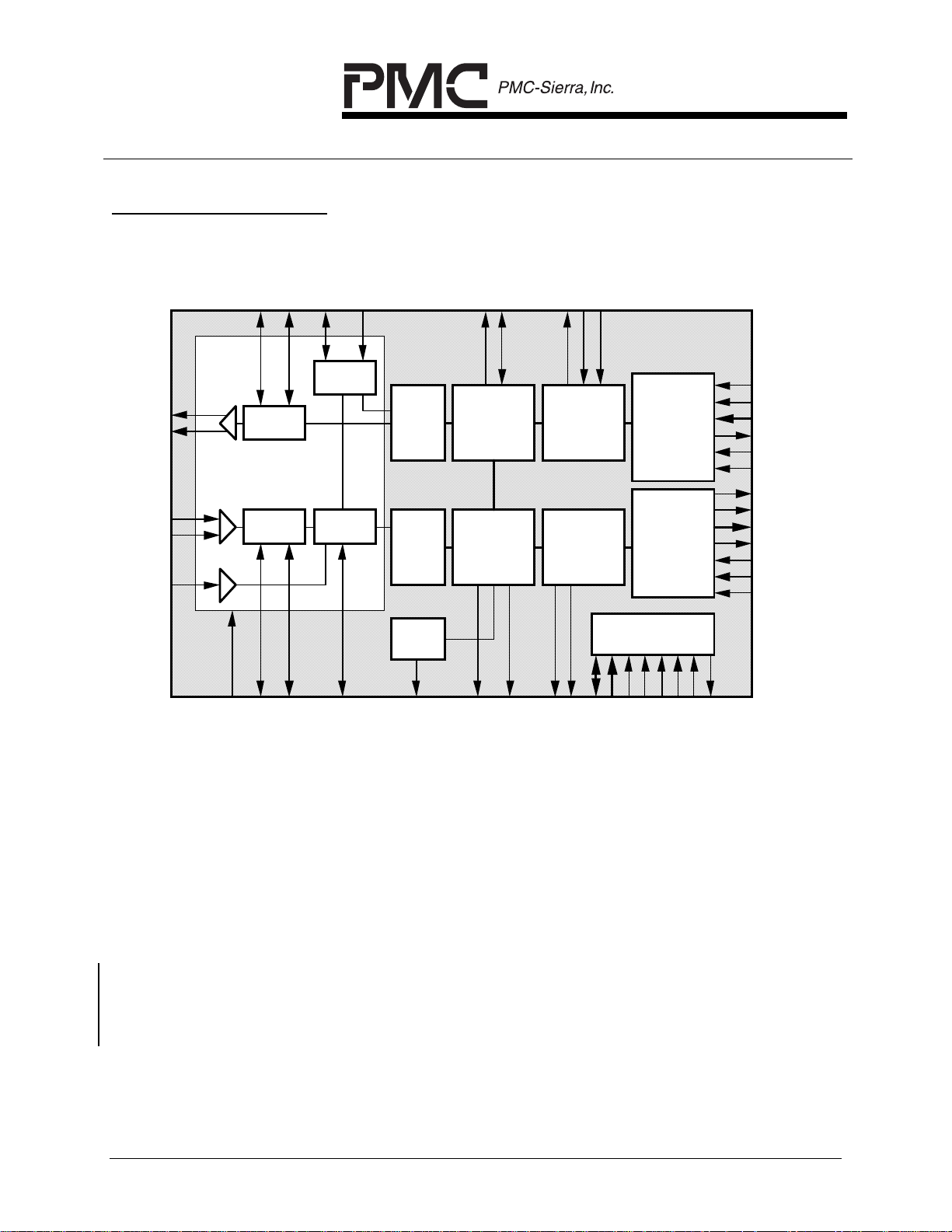

5

BLOCK DIAGRAM

TXD+

TXD-

Analog Edge

RXD+

RXD-

SD

TVREF

Twisted

Pair Tx

Twisted

Pair Rx

TRREF

Clk Gen.

TM

Clk/Data

ATP2

Rec.

REFCLK

Parallel

Serial

Serial

Parallel

Control

to

to

LED

TCLK

TFP

Tx

Framer &

Overhead

Processor

Rx

Framer &

Overhead

Processor

XOFF

TGFC

TCP

Tx ATM

Cell

Processor

Rx ATM

Cell

Processor

Tx ATM

Cell

FIFO

Rx ATM

Cell

FIFO

Microprocessor

I/F

TSOC

TXPRTY

TDAT[7:0]

TCA

TWRENB

TFCLK

RSOC

RXPRTY

RDAT[7:0]

RCA

RRDENB

RFCLK

TSEN

RCAP1

PECLSEL

RCAP2

ATP1

OUT[1:0]

RCLK

RFP

RCP

RGFC

A[7:0]

D[7:0]

ALE

CSB

RDB

WRB

INTB

RSTB

Description

The PM5350 S/UNI-ULTRA Saturn User Network Interface is a monolithic

integrated circuit that implements the SONET/SDH processing and ATM mapping

functions of a 155 Mbit/s or 51Mbit/s ATM User Network Interface. It is fully

compliant with both SONET and SDH requirements and ATM Forum UNI

specifications.

The S/UNI-ULTRA is capable of directly interfacing with UTP-5 cable. At the

receiver end, it performs adaptive equalization. It is fully compliant with the ATM

Forum PMD Interface specifications for 155 Mb/s over twisted pair cable.

The S/UNI-ULTRA receives SONET/SDH frames via a bit serial interface,

recovers clock and data, and processes section, line, and path overhead. It

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

performs framing (A1, A2), descrambling, detects alarm conditions, and monitors

section, line, and path bit interleaved parity (B1, B2, B3), accumulating error

counts at each level for performance monitoring purposes. Line and path far end

block error indications (M0 or M1, G1) are also accumulated. The S/UNI-ULTRA

interprets the received payload pointers (H1, H2) and extracts the synchronous

payload envelope which carries the received ATM cell payload.

The S/UNI-ULTRA frames to the ATM payload using cell delineation. HCS error

correction is provided. Idle/unassigned cells may be dropped according to a

programmable filter. Cells are also dropped upon detection of an uncorrectable

header check sequence error. The ATM cell payloads are descrambled. Generic

flow control (GFC) bits from error free cells are extracted and presented on a

serial link for external processing.

Legitimate ATM cells are written to a four cell FIFO buffer. These cells are read

from the FIFO using a synchronous 8 bit wide datapath interface with cell-based

handshake. Counts of received ATM cell headers that are errored and

uncorrectable, those that are errored and correctable and all passed cells are

accumulated independently for performance monitoring purposes.

The S/UNI-ULTRA transmits SONET/SDH frames via a bit serial interface and

formats section, line, and path overhead appropriately. It performs framing

pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates

section, line, and path bit interleaved parity (B1, B2, B3) as required to allow

performance monitoring at the far end. Line and path far end block error

indications (M0 or M1, G1) are also inserted.

The S/UNI-ULTRA generates the payload pointer (H1, H2) and inserts the

synchronous payload envelope which carries the ATM cell payload. It supports

the insertion of a variety of errors into the transmit stream, such as framing

pattern errors, bit interleaved parity errors, and illegal pointers, which are useful

for system diagnostics.

ATM cells are written to an internal programmable-length 4-cell FIFO using a

synchronous 8 bit wide datapath interface. Idle/unassigned cells are

automatically inserted when the internal FIFO contains less than one cell or the

XOFF input is asserted. Generic flow control (GFC) bits may be inserted

downstream of the FIFO via a serial link so that all FIFO latency may be

bypassed. A transmission off (XOFF) input is provided to allow the suspension

of active ATM cell transmission independent of the FIFO fill state.

The S/UNI-ULTRA generates the header check sequence and scrambles the

payload of the ATM cells. Payload scrambling can be disabled.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

No line rate clocks are required directly by the S/UNI-ULTRA as it synthesizes

the transmit clock and recovers the receive clock using a 19.44 MHz reference

clock.

The S/UNI-ULTRA provides output control signals that can be used to command

an LED display, making it easy to visually monitor either alarms, or the transmit

and receive activity.

The S/UNI-ULTRA is configured, controlled and monitored via a generic 8-bit

microprocessor bus interface. It is implemented in low power, +5 Volt CMOS

technology. It has TTL and pseudo-ECL (PECL) compatible inputs and outputs

and is packaged in a 128 pin PQFP package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

6

PIN DIAGRAM

The S/UNI-ULTRA is packaged in an 128 pin PQFP package having a body size

of 14 mm by 20 mm and a pin pitch of 0.50 mm.

VSSI5

PIN 1

VSS

REFCLK

TAVS2

TAVD2

TAVS1

TAVD1

ATP1

QAVS

QAVD

TAVS3

TAVD3

TXD+

TXD-

TAVD3

TAVS3

TAVD4

TAVS4

TVREF

TRREF

TAVS4

RAVD3

RAVS3

RXD-

RXD+

RAVS3

RAVS3

RCAP1

RCAP2

RAVD3

QAVD

QAVS

ATP2

RAVD1

RAVS1

RAVD2

RAVS2

VSS

PIN 38

PIN 128

.

SD

A[5]

A[6]

A[7]

VSS

Index Pin

A[4]

A[3]

A[2]

A[1]

A[0]

VDDI5

D[7]

D[6]

D[5]

D[4]

VDDO6

VSSO6

D[3]

PM5350

S/UNI-ULTRA

Top

View

D[2]

D[1]

D[0]

INTB

VSSI4

VDDI4

VSS

PIN 103

ALE

PIN 102

VSS

RSTB

CSB

RDB

WRB

TSOC

TXPRTY

TDAT[7]

TDAT[6]

TDAT[5]

TDAT[4]

TDAT[3]

TDAT[2]

TDAT[1]

TDAT[0]

TWRENB

TFCLK

VDDI3

VSSI3

TCA

RSOC

RXPRTY

VDDO5

VSSO5

RDAT[7]

RDAT[6]

RDAT[5]

RDAT[4]

RDAT[3]

RDAT[2]

VDDO4

VSSO4

RDAT[1]

RDAT[0]

RCA

RRDENB

RFCLK

VSS

PIN 65

PIN 39 PIN 64

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

VSS

PECLSEL

OUT[1]

VSSI1

OUT[0]

XOFF

VDDI1

VSSI6

VSSO1

VDDO1

RCP

TCP

TGFC

TCLK

VSSO2

VDDO2

RFP

RCLK

TFP

RGFC

TSEN

VDDI2

VSSI2

VDDO3

VSS

VSSO3

10

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

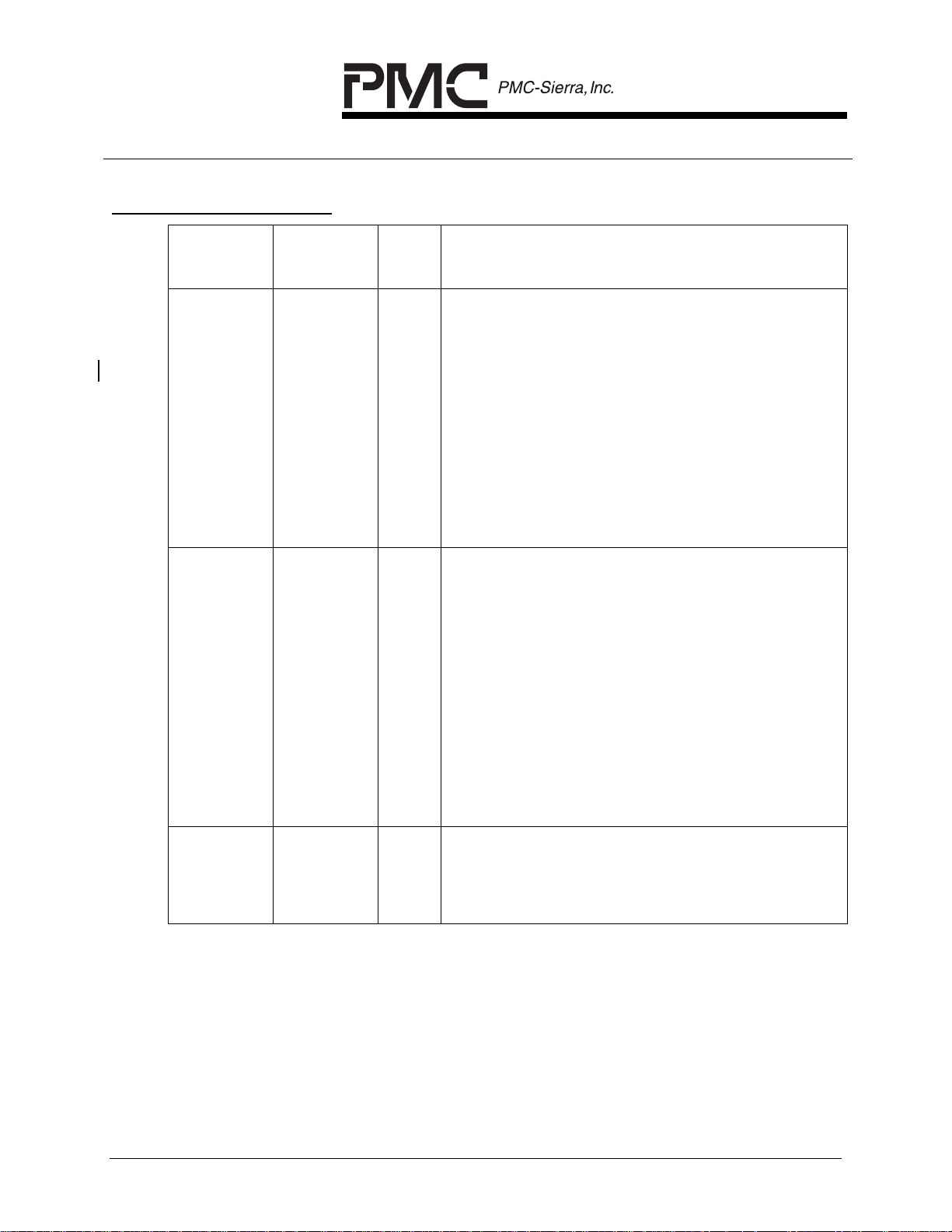

7

PIN DESCRIPTION

Pin Name Type Pin

Function

No.

PECLSEL TTL Input 40 The PECL mode select (PECLSEL) is used to

configure the Analog Edge PMD interface for

either PECL or Twisted-pair. A TTL low

configures the interface for while a TTL high

configures the interface for PECL, enabling

direct interfacing with optical transceivers.

Refer to the OPERATION section for a detailed

description of Twisted-Pair mode and PECL

mode configurations. Different termination at

TXD+/- and RXD+/- are required depending on

the selected mode.

RXD+

RXD-

Diff.

Analog

Input

24

23

The differential receiver inputs (RXD+/-) NRZ

data, from the balun/transformer module

interface to these pins when operating in

Twisted-pair mode (as configured via the

PECLSEL pin tied low), or from an optical data

link (ODL) when in PECL mode (as configured

via the PECLSEL pin tied high).

RXD+/- are truly differential inputs offering

superior common-mode noise rejection. Refer

to the APPLICATIONS section of this

document for a description of the required

termination network.

REFCLK TTL Input 2 The reference clock input (REFCLK) must

provide a jitter-free 19.44 MHz reference clock.

It is used as the reference clock by both clock

recovery and clock synthesis circuits.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

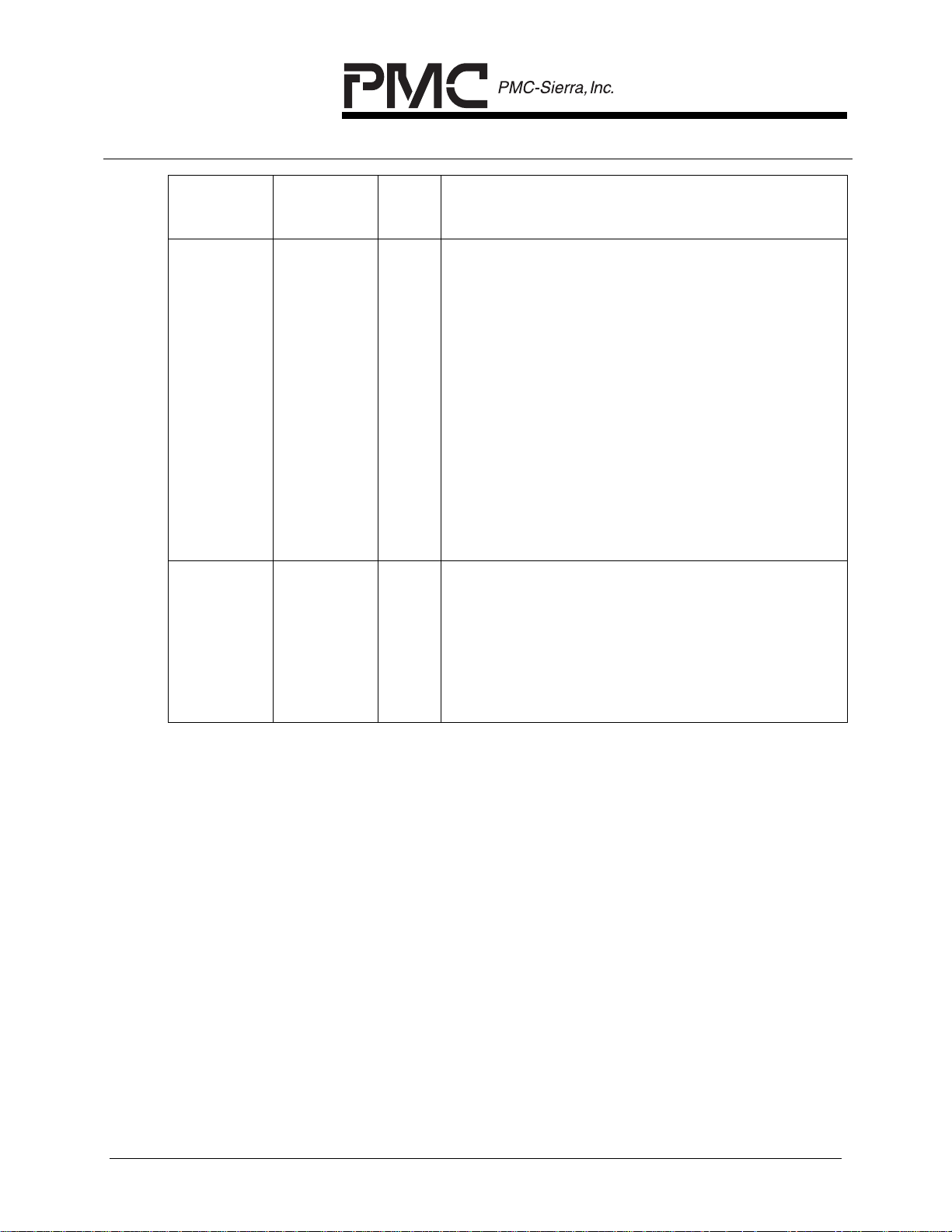

Pin Name Type Pin

Function

No.

SD Single-

Ended

PECL

Input

29 The Signal Detect pin (SD) indicates the

presence of valid receive signal power from the

Optical Physical Medium Dependent Device

when operating in PECL mode (as configured

via the PECLSEL pin tied high). A PECL high

indicates the presence of valid data and a

PECL low indicates a loss of signal. It is

mandatory that SD be terminated into the

equivalent network that RXD+/- is terminated

into.

When operated in Twisted-pair mode (as

configured via the PECLSEL pin tied low), SD

has no function and should be connected to

the analog ground common to RAVS3.

RCLK Output 55 The receive clock (RCLK) output provides a

timing reference for the S/UNI-ULTRA receive

outputs. RCLK is a divide by eight of the

recovered line rate clock. RGFC, RCP, RFP

and OUT[1] (when configured for alarm

monitoring) are updated on the rising edge of

RCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

No.

OUT[1]

OUT[0]

Output 41

42

Function

The alarm/output por t pins has three functions

as selected by POPC control register bits.

When configured to output alarms, the OUT[1]

output indicates a receive alarm (RALM

function) based on the state of the receive

framer. OUT[1] is low if no receive alarms are

active. OUT[1] is high if an alarm condition is

detected. OUT[1] is updated on the rising

edge of RCLK. In this operation mode OUT[0]

is used as a single bit parallel output port, as

described below.

When configured as a parallel output port,

OUT[1] and OUT[0] can be used to control the

operation of external devices. The signal levels

on the output port are determined by register

bits.

When configured as a traffic indicator port,

OUT[1] indicates the receive traffic activity and

OUT[0] indicates the transmit traffic activity. In

this operation mode OUT[1] and OUT[0]

pulses high fom 100ms on cell receive and

transmit events and can be used to control an

LED display.

RFP Output 56 The receive frame pulse (RFP) output, when

the framing alignment has been found (the

OOF register bit is logic 0), is an 8 kHz signal

derived from the receive line clock. RFP

pulses high for one RCLK cycle every 2430

RCLK cycles for STS-3c (STM-1) rate or every

810 RCLK cycles for STS-1 rate. RFP is

updated on the rising edge of RCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TXD+

TXD-

Diff.

Analog

Output

12

13

The transmit differential data/positive pulse

outputs (TXD+, TXD-) contain NRZ encoded

data. These outputs are open drain current

sinks which interface directly with the Twistedpair network or with an Optical Interface

Module requiring PECL levels.

Refer to the APPLICATIONS section of this

document for a description of the required

termination network.

TFP I/O 58 The active high framing position (TFP) signal is

an 8 kHz timing marker for the transmitter. TFP

defaults to being an input and is used to align

the SONET/SDH transport frame generated by

the S/UNI-ULTRA device to a system

reference. TFP should be brought high for a

single TCLK period every 810 (STS-1) or 2430

(STS-3/STM-1) TCLK cycles, or a multiple

thereof. TFP may be tied low if such

synchronization is not required. TFP is

sampled on the rising edge of TCLK. TFP must

not be used as an input when loop-timed.

When selected as an output through the

interface configuration register, TFP pulses

high for one TCLK cycle every 2430 TCLK

cycles for STS-3c (STM-1) rate or every 810

TCLK cycles for STS-1 rate. TFP is updated

on the rising edge of TCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TSEN Input 59 The tristate enable (TSEN) input selects the

configuration of the receive datapath

(RDAT[7:0], RXPRTY and RSOC). When

TSEN is tied high, RDAT[7:0] operates as a

tristate bus controlled by RRDENB. When

RRDENB is high upon RFCLK rising,

RDAT[7:0], RXPRTY and RSOC are tristated.

When RRDENB is low upon RFCLK rising,

RDAT[7:0], RXPRTY and RSOC are enabled.

When TSEN is tied low, RDAT[7:0], RXPRTY

and RSOC are always enabled, regardless of

the state of RRDENB.

RFCLK Input 66 The receive read clock (RFCLK) is used to

read ATM cells from the receive FIFO. RFCLK

must cycle at a high enough rate to avoid FIFO

overflow. RRDENB is sampled using the rising

edge of RFCLK. RSOC, RDAT[7:0], RXPRTY

and RCA are updated on the rising edge of

RFCLK

RRDENB Input 67 The active low receive read enable input

(RRDENB) is used to initiate reads from the

receive FIFO. When sampled low using the

rising edge of RFCLK, a byte is read from the

internal synchronous FIFO and output on bus

RDAT[7:0] if one is available. When sampled

high using the rising edge of RFCLK, no read

is performed and RDAT[7:0] and RSOC are

tristated if the TSEN input is high. RRDENB

must operate in conjunction with RFCLK to

access the FIFO at a high enough

instantaneous rate as to avoid FIFO overflows.

The ATM layer device may deassert RRDENB

at anytime it is unable to accept another byte.

When the RCA signal is configured to be

deasserted with zero octets (as opposed to

four) in the FIFO, the RCA signal identifies the

valid octets.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

15

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

No.

RDAT[0]

RDAT[1]

RDAT[2]

RDAT[3]

RDAT[4]

RDAT[5]

RDAT[6]

RDAT[7]

RXPRTY Tristate

Tristate

Output

69

70

73

74

75

76

77

78

81 The receive parity (RXPRTY) signal indicates

Output

Function

The receive cell data (RDAT[7:0]) bus carries

the ATM cell octets that are read from the

receive FIFO. RDAT[7:0] is updated on the

rising edge of RFCLK and is tristated when not

valid if the TSEN input is high. The RDAT[7:0]

bus is always driven when TSEN is low,

regardless of the level of RRDENB.

the parity of the RDAT[7:0] bus. Odd or even

parity selection can be made using a register.

RXPRTY is updated on the rising edge of

RFCLK and is tristated when not valid if the

TSEN input is high. RXPRTY is always driven

when TSEN is low, regardless of the level of

RRDENB.

RSOC Tristate

Output

82 The receive start of cell (RSOC) signal marks

the start of cell on the RDAT[7:0] bus. When

RSOC is high, the first octet of the cell is

present on the RDAT[7:0] stream. RSOC is

updated on the rising edge of RFCLK and is

tristated when not valid if the TSEN input is

high. RSOC is always driven when TSEN is

low, regardless of the level of RRDENB.

RCA Output 68 The receive cell available (RCA) signal

indicates when a cell is available in the receive

FIFO. RCA can be configured to be

deasserted when either zero or four bytes

remain in the FIFO. RCA is updated on the

rising edge of RFCLK. The active polarity of

this signal is programmable and defaults to

active high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

RGFC Output 57 The receive generic flow control (RGFC)

output presents the extracted GFC bits in a

serial stream. The four GFC bits are presented

for each received cell, with the RCP output

indicating the position of the most significant

bit. The updating of RGFC by particular GFC

bits may be disabled through the RACP

Configuration register. The serial link is forced

low if cell delineation is lost. RGFC is updated

on the rising edge of RCLK.

RCP Output 49 The receive cell pulse (RCP) indicates the

location of the four GFC bits in the RGFC

serial stream. RCP is coincident with the most

significant GFC bit. RCP is updated on the

rising edge of RCLK.

TCLK Output 52 The transmit byte clock (TCLK) output provides

a timing reference for S/UNI-ULTRA transmit

outputs. TCLK is a divide by eight of the

synthesized line rate clock. TGFC, TCP and

TFP are sampled on the rising edge of TCLK.

TFCLK Input 86 The transmit write clock (TFCLK) is used to

write ATM cells to the four cell transmit FIFO.

A complete 53 octet cell must be written to the

FIFO before being inserted in the synchronous

payload envelope (SPE). Idle/unassigned cells

are inserted when a complete cell is not

available. TDAT[7:0], TXPRTY, TWRENB and

TSOC are sampled on the rising edge of

TFCLK. TCA is updated on the rising edge of

TFCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

17

PM5350 S/UNI-ULTRA

DATA SHEET

PMC-960924 ISSUE 5 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TDAT[0]

TDAT[1]

TDAT[2]

TDAT[3]

Input 88

89

90

91

The transmit cell data (TDAT[7:0]) bus carries

the ATM cell octets that are written to the

transmit FIFO. TDAT[7:0] is sampled on the

rising edge of TFCLK and is considered valid

only when TWRENB is simultaneously

asserted.

TDAT[4]

TDAT[5]

TDAT[6]

TDAT[7]

92

93

94

95

TXPRTY Input 96 The transmit parity (TXPRTY) signal indicates

the parity of the TDAT[7:0] bus. Odd or even

parity selection can be made using a register

bit. TXPRTY is sampled on the rising edge of

TFCLK and is considered valid only when

TWRENB is simultaneously asserted.

A parity error is indicated by a status bit and a

maskable interrupt. Cells with parity errors are

not filtered, so the TXPRTY input may be

unused.

TWRENB Input 87 The active low transmit write enable input

(TWRENB) is used to initiate writes to the

transmit FIFO. When sampled low using the

rising edge of TFCLK, the byte on TDAT[7:0] is

written into the transmit FIFO. When sampled

high using the rising edge of TFCLK, no write

is performed. A complete 53 octet cell must be

written to the transmit FIFO before it is

inserted into the SPE. Idle/unassigned cells

are inserted when a complete cell is not

available.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

18

Loading...

Loading...