PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

PM5348

TM

S/

UNI-

155-DUAL

S/UNI-155-DUAL

DUAL SATURN USER NETWORK

INTERFACE 155.52 & 51.84 MBIT/S

DATA SHEET

ISSUE 7: JUNE 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

REVISION HISTORY

Issue No. Issue Date Details of Change

7 June 1997 Data Sheet Reformatted — No Change in Technical

Content.

Generated R7 data sheet from PMC-950716, R7

6 Feb 1997 Eng doc P6 revised

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

CONTENTS

1 FEATURES...............................................................................................9

2 APPLICATIONS........................................................................................9

3 REFERENCES.........................................................................................9

4 APPLICATION EXAMPLES......................................................................9

5 BLOCK DIAGRAM....................................................................................9

6 DESCRIPTION.........................................................................................9

7 PIN DIAGRAM..........................................................................................9

8 PIN DESCRIPTION..................................................................................9

9 FUNCTIONAL DESCRIPTION.................................................................9

9.1 CLOCK RECOVERY......................................................................9

9.2 SERIAL TO PARALLEL CONVERTER...........................................9

9.3 RECEIVE SECTION OVERHEAD PROCESSOR..........................9

9.3.1 FRAMER.............................................................................9

9.3.2 DESCRAMBLE ...................................................................9

9.3.3 ERROR MONITOR..............................................................9

9.3.4 LOSS OF SIGNAL ..............................................................9

9.3.5 LOSS OF FRAME...............................................................9

9.4 RECEIVE LINE OVERHEAD PROCESSOR .................................9

9.4.1 LINE REMOTE DEFECT INDICATION DETECT ................9

9.4.2 LINE AIS DETECT..............................................................9

9.4.3 AUTOMATIC PROTECTION SWITCH CONTROL BLOCK.9

9.4.4 ERROR MONITOR..............................................................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

9.5 RECEIVE PATH OVERHEAD PROCESSOR.................................9

9.5.1 POINTER INTERPRETER..................................................9

9.5.2 ERROR MONITOR..............................................................9

9.6 RECEIVE ATM CELL PROCESSOR.............................................9

9.6.1 CELL DELINEATION...........................................................9

9.6.2 DESCRAMBLER.................................................................9

9.6.3 CELL FILTER AND HCS VERIFICATION............................9

9.6.4 PERFORMANCE MONITOR...............................................9

9.6.5 RECEIVE FIFO...................................................................9

9.7 CLOCK SYNTHESIS.....................................................................9

9.8 PARALLEL TO SERIAL CONVERTER...........................................9

9.9 TRANSMIT SECTION OVERHEAD PROCESSOR.......................9

9.9.1 LINE AIS INSERT...............................................................9

9.9.2 BIP-8 INSERT.....................................................................9

9.9.3 FRAMING AND SECTION TRACE .....................................9

9.9.4 GENERATION OF TFP .......................................................9

9.9.5 SCRAMBLER......................................................................9

9.10 TRANSMIT LINE OVERHEAD PROCESSOR...............................9

9.10.1APS INSERT.......................................................................9

9.10.2BIP CALCULATE.................................................................9

9.10.3LINE REMOTE DEFECT INDICATION INSERT..................9

9.10.4LINE FEBE INSERT............................................................9

9.11 TRANSMIT PATH OVERHEAD PROCESSOR..............................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

9.11.1POINTER GENERATOR.....................................................9

9.11.2BIP-8 CALCULATE..............................................................9

9.11.3FEBE CALCULATE.............................................................9

9.11.4SPE MULTIPLEXER............................................................9

9.12 TRANSMIT ATM CELL PROCESSOR...........................................9

9.12.1IDLE/UNASSIGNED CELL GENERATOR...........................9

9.12.2SCRAMBLER......................................................................9

9.12.3HCS GENERATOR..............................................................9

9.12.4TRANSMIT FIFO.................................................................9

9.13 SATURN COMPLIANT SPLIT-BUS PHY INTERFACE (SPHY)......9

9.14 MICROPROCESSOR INTERFACE ...............................................9

10 REGISTER MEMORY MAP......................................................................9

11 NORMAL MODE REGISTER DESCRIPTION..........................................9

12 TEST FEATURES DESCRIPTION ...........................................................9

12.1 TEST MODE 0 DETAILS................................................................9

12.2 JTAG TEST PORT..........................................................................9

13 OPERATION.............................................................................................9

13.1 OVERHEAD BYTE USAGE...........................................................9

13.2 CELL DATA STRUCTURE..............................................................9

13.3 LOOPBACK OPERATION..............................................................9

13.4 BOARD DESIGN RECOMMENDATIONS......................................9

13.5 DRIVING DIFFERENTIAL INPUTS SINGLE ENDED ....................9

13.6 DRIVING THE DIFFERENTIAL REFERENCE CLOCK.................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

13.7 INTERFACING TO ECL OR PECL DEVICES................................9

13.8 CLOCK RECOVERY......................................................................9

13.9 BIT ERROR RATE MONITOR........................................................9

13.10 JTAG SUPPORT............................................................................9

13.11 POWER SEQUENCING................................................................9

14 FUNCTIONAL TIMING .............................................................................9

14.1 DROP SIDE RECEIVE INTERFACE..............................................9

14.2 DROP SIDE TRANSMIT INTERFACE...........................................9

15 ABSOLUTE MAXIMUM RATINGS............................................................9

16 D.C. CHARACTERISTICS........................................................................9

17 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS..........9

18 S/UNI-DUAL TIMING CHARACTERISTICS..............................................9

19 ORDERING AND THERMAL INFORMATION ..........................................9

20 MECHANICAL INFORMATION.................................................................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

LIST OF REGISTERS

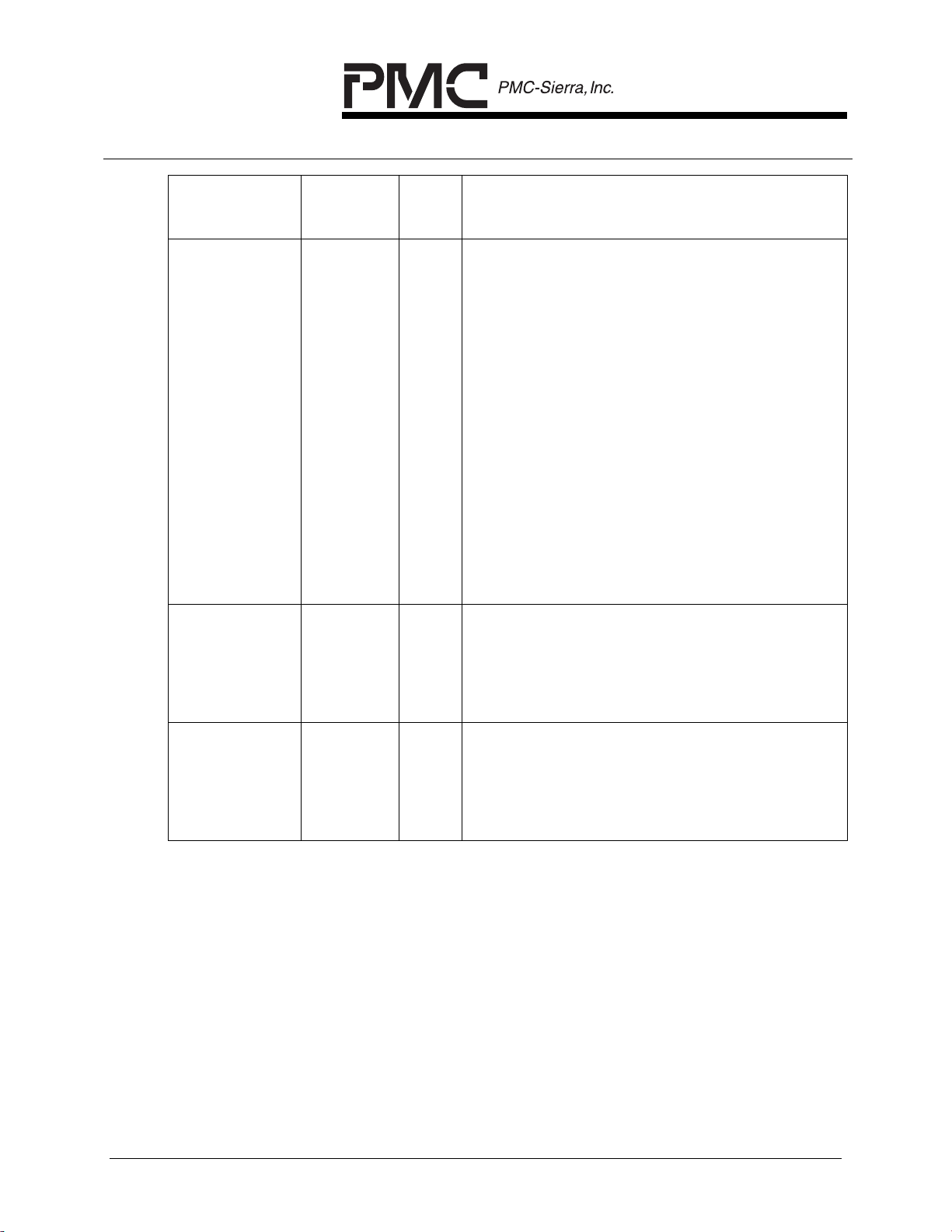

REGISTER 0X000: S/UNI-DUAL MASTER RESET AND IDENTITY / CHANNEL

#1 MONITORING UPDATE.......................................................................9

REGISTER 0X080: S/UNI-DUAL CHANNEL #2 MONITORING UPDATE...........9

REGISTER 0X001, 0X081: S/UNI-DUAL CONFIGURATION..............................9

REGISTER 0X002, 0X082: S/UNI-DUAL INTERRUPT STATUS.........................9

REGISTER 0X003: S/UNI-DUAL MASTER MODE CONTROL...........................9

REGISTER 0X004: S/UNI-DUAL MASTER CLOCK MONITOR..........................9

REGISTER 0X005, 0X085: S/UNI-DUAL CONTROL..........................................9

REGISTER 0X006: S/UNI-DUAL CLOCK SYNTHESIS CONTROL AND STATUS

..................................................................................................................9

REGISTER 0X007, 0X087: S/UNI-DUAL CLOCK RECOVERY CONTROL AND

STATUS ....................................................................................................9

REGISTER 0X008: S/UNI-DUAL INTERFACE CONTROL .................................9

REGISTER 0X009: S/UNI-DUAL OUTPUT PORT CONTROL............................9

REGISTER 0X00A: S/UNI-DUAL POP[0] STROBE RATE..................................9

REGISTER 0X00B: S/UNI-DUAL POP[1] STROBE RATE..................................9

REGISTER 0X00C: S/UNI-DUAL POP[2] STROBE RATE..................................9

REGISTER 0X00D: S/UNI-DUAL POP[3] STROBE RATE..................................9

REGISTER 0X00E, 0X08E: TRANSMIT SYNCHRONIZATION STATUS ............9

REGISTER 0X010, 0X090: RSOP CONTROL/INTERRUPT ENABLE ...............9

REGISTER 0X011, 0X091: RSOP STATUS/INTERRUPT STATUS.....................9

REGISTER 0X012, 0X092: RSOP SECTION BIP-8 LSB....................................9

REGISTER 0X013, 0X093: RSOP SECTION BIP-8 MSB...................................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

REGISTER 0X014, 0X094: TSOP CONTROL ....................................................9

REGISTER 0X015, 0X095: TSOP DIAGNOSTIC................................................9

REGISTER 0X018, 0X098: RLOP CONTROL/STATUS......................................9

REGISTER 0X019, 0X099: RLOP INTERRUPT ENABLE/INTERRUPT STATUS9

REGISTER 0X01A, 0X09A: RLOP LINE BIP-8/24 LSB......................................9

REGISTER 0X01B, 0X09B: RLOP LINE BIP-8/24..............................................9

REGISTER 0X01C, 0X09C: RLOP LINE BIP-8/24 MSB.....................................9

REGISTER 0X01D, 0X09D: RLOP LINE FEBE LSB...........................................9

REGISTER 0X01E, 0X09E: RLOP LINE FEBE...................................................9

REGISTER 0X01F, 0X09F: RLOP LINE FEBE MSB...........................................9

REGISTER 0X020, 0X0A0: TLOP CONTROL ....................................................9

REGISTER 0X021, 0X0A1: TLOP DIAGNOSTIC................................................9

REGISTER 0X022, 0X0A2: TLOP TRANSMIT K1 ..............................................9

REGISTER 0X023, 0X0A3: TLOP TRANSMIT K2 ..............................................9

REGISTER 0X030, 0X0B0: RPOP STATUS/CONTROL .....................................9

REGISTER 0X031, 0X0B1: RPOP INTERRUPT STATUS ..................................9

REGISTER 0X033, 0X0B3: RPOP INTERRUPT ENABLE.................................9

REGISTER 0X037, 0X0B7: RPOP PATH SIGNAL LABEL..................................9

REGISTER 0X038, 0X0B8: RPOP PATH BIP-8 LSB...........................................9

REGISTER 0X039, 0X0B9: RPOP PATH BIP-8 MSB..........................................9

REGISTER 0X03A, 0X0BA: RPOP PATH FEBE LSB .........................................9

REGISTER 0X03B, 0X0BB: RPOP PATH FEBE MSB ........................................9

REGISTER 0X03D, 0X0BD: RPOP PATH BIP-8 CONFIGURATION...................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

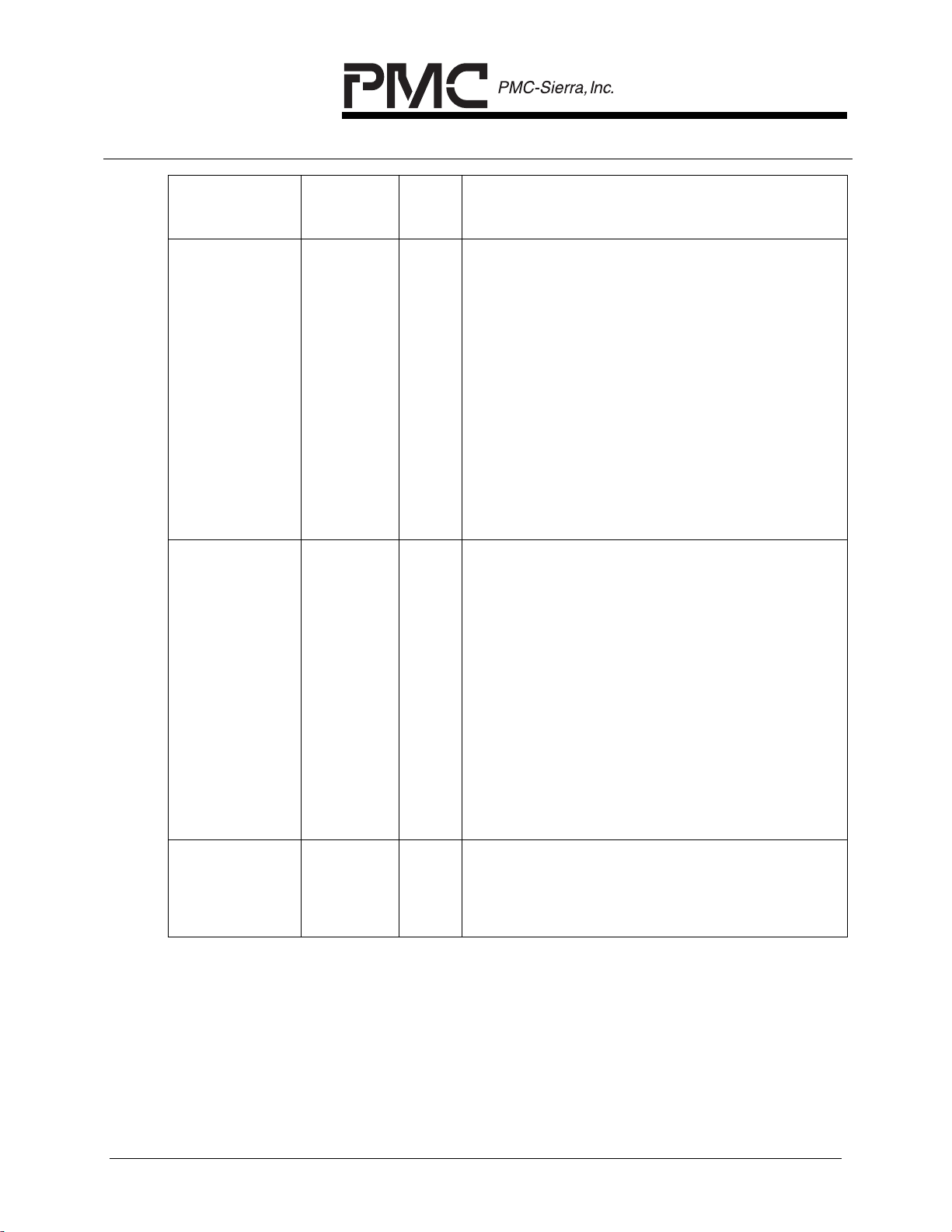

REGISTER 0X040, 0X0C0: TPOP CONTROL/DIAGNOSTIC.............................9

REGISTER 0X041, 0X0C1: TPOP POINTER CONTROL...................................9

REGISTER 0X045, 0X0C5: TPOP ARBITRARY POINTER LSB ........................9

REGISTER 0X046, 0X0C6: TPOP ARBITRARY POINTER MSB .......................9

REGISTER 0X048, 0X0C8: TPOP PATH SIGNAL LABEL ..................................9

REGISTER 0X049, 0X0C9: TPOP PATH STATUS...............................................9

REGISTER 0X050, 0X0D0: RACP CONTROL/STATUS .....................................9

REGISTER 0X051, 0X0D1: RACP INTERRUPT ENABLE/STATUS ...................9

REGISTER 0X052, 0X0D2: RACP MATCH HEADER PATTERN........................9

REGISTER 0X053, 0X0D3: RACP MATCH HEADER MASK..............................9

REGISTER 0X054, 0X0D4: RACP CORRECTABLE HCS ERROR COUNT.......9

REGISTER 0X055, 0X0D5: RACP UNCORRECTABLE HCS ERROR COUNT .9

REGISTER 0X056, 0X0D6: RACP RECEIVE CELL COUNTER (LSB)...............9

REGISTER 0X057, 0X0D7: RACP RECEIVE CELL COUNTER.........................9

REGISTER 0X058, 0X0D8: RACP RECEIVE CELL COUNTER (MSB)..............9

REGISTER 0X059, 0X0D9: RACP CONFIGURATION........................................9

REGISTER 0X060, 0X0E0: TACP CONTROL/STATUS.......................................9

REGISTER 0X061, 0X0E1: TACP IDLE/UNASSIGNED CELL HEADER

PATTERN..................................................................................................9

REGISTER 0X062, 0X0E2: TACP IDLE/UNASSIGNED CELL PAYLOAD OCTET

PATTERN..................................................................................................9

REGISTER 0X063, 0X0E3: TACP FIFO CONTROL............................................9

REGISTER 0X064, 0X0E4: TACP TRANSMIT CELL COUNTER (LSB) .............9

REGISTER 0X065, 0X0E5: TACP TRANSMIT CELL COUNTER........................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

REGISTER 0X066, 0X0E6: TACP TRANSMIT CELL COUNTER (MSB).............9

REGISTER 0X067, 0X0E7: TACP CONFIGURATION.........................................9

REGISTERS 0X068, 0X0E8: RASE INTERRUPT ENABLE...............................9

REGISTERS 0X069, 0X0E9: RASE INTERRUPT STATUS ................................9

REGISTERS 0X06A, 0X0EA: RASE CONFIGURATION/CONTROL REGISTER9

REGISTERS 0X06B, 0X0EB: RASE SF ACCUMULATION PERIOD (LSB)........9

REGISTERS 0X06C, 0X0EC: RASE SF ACCUMULATION PERIOD..................9

REGISTERS 0X06D, 0X0ED: RASE SF ACCUMULATION PERIOD (MSB).......9

REGISTERS 0X06E, 0X0EE: RASE SF SATURATION THRESHOLD (LSB) .....9

REGISTERS 0X06F, 0X0EF: RASE SF SATURATION THRESHOLD (MSB)......9

REGISTERS 0X070, 0X0F0: RASE SF DECLARING THRESHOLD (LSB)........9

REGISTERS 0X071, 0X0F1: RASE SF DECLARING THRESHOLD (MSB).......9

REGISTERS 0X072, 0X0F2: RASE SF CLEARING THRESHOLD (LSB)..........9

REGISTERS 0X073, 0X0F3: RASE SF CLEARING THRESHOLD (MSB).........9

REGISTERS 0X07D, 0X0FD: RASE RECEIVE K1.............................................9

REGISTERS 0X07E, 0X0FE: RASE RECEIVE K2.............................................9

REGISTERS 0X07F, 0X0FF: RASE RECEIVE S1..............................................9

REGISTER 0X100: MASTER TEST....................................................................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

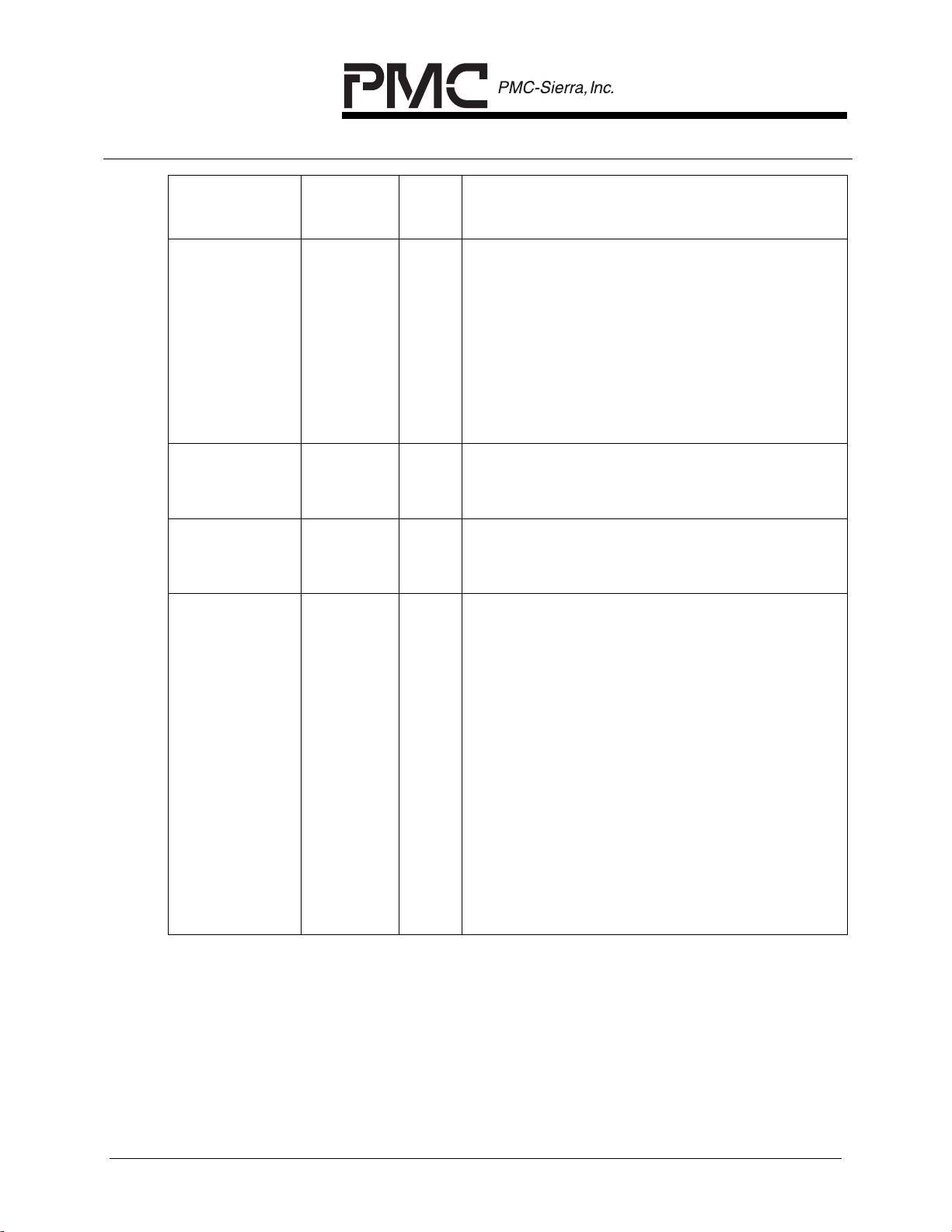

LIST OF FIGURES

FIGURE 1 - SPLIT-BUS 8-BIT DIRECT-PHY ATM SWITCH INTERFACE .........9

FIGURE 2 - DIRECT 8-BIT OR 16-BIT MULTI-PHY ATM SWITCH INTERFACE9

FIGURE 3 - STS-3C/STM-1JITTER TOLERANCE ............................................9

FIGURE 4 - CELL DELINEATION STATE DIAGRAM.........................................9

FIGURE 5 - HCS VERIFICATION STATE DIAGRAM ......................................... 9

FIGURE 6 - STS-3C/STM-1 DEFAULT TRANSPORT OVERHEAD VALUES ....9

FIGURE 7 - STS-1 DEFAULT TRANSPORT OVERHEAD VALUES...................9

FIGURE 8 - DEFAULT PATH OVERHEAD VALUES...........................................9

FIGURE 9 - STS-3C (STM-1) OVERHEAD........................................................9

FIGURE 10- STS-1 OVERHEAD ........................................................................9

FIGURE 11- 16-BIT WIDE, 27 WORD STRUCTURE..........................................9

FIGURE 12- 8-BIT WIDE, 53 WORD STRUCTURE............................................9

FIGURE 13- LINE LOOPBACK MODE...............................................................9

FIGURE 14- SERIAL DIAGNOSTIC LOOPBACK MODE...................................9

FIGURE 15- PARALLEL DIAGNOSTIC LOOPBACK MODE..............................9

FIGURE 16- SINGLE ENDED DRIVING DIFFERENTIAL INPUTS....................9

FIGURE 17- DRIVING REFCLK INPUTS...........................................................9

FIGURE 18- INTERFACING S/UNI-DUAL TO ECL OR PECL ............................9

FIGURE 19- CLOCK RECOVERY CIRCUIT - UNITY GAIN BUFFER LOOP

FILTER .........................................................................................................9

FIGURE 20- BOUNDARY SCAN ARCHITECTURE............................................9

FIGURE 21- TAP CONTROLLER FINITE STATE MACHINE..............................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

FIGURE 22- INPUT OBSERVATION CELL (IN_CELL).......................................9

FIGURE 23- OUTPUT CELL (OUT_CELL).........................................................9

FIGURE 24- BIDIRECTIONAL CELL (IO_CELL)................................................9

FIGURE 25- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS....9

FIGURE 26- SPLIT-BUS MODE, RECEIVE FIFO EMPTY OPTION...................9

FIGURE 27- 16-BIT MULTI-PHY MODE, RECEIVE FIFO EMPTY AND

TRISTATE OPTIONS...........................................................................................9

FIGURE 28- 8-BIT MULTI-PHY MODE, RECEIVE FIFO NEAR EMPTY OPTION

.........................................................................................................9

FIGURE 29- SPLIT-BUS MODE, TRANSMIT FIFO EMPTY OPTION ................9

FIGURE 30- 16-BIT MULTI-PHY MODE, TRANSMIT FIFO NEAR EMPTY

OPTION .........................................................................................................9

FIGURE 31- MICROPROCESSOR INTERFACE READ TIMING........................9

FIGURE 32- MICROPROCESSOR INTERFACE WRITE TIMING......................9

FIGURE 33- RECEIVE FRAME PULSE OUTPUT TIMING ................................9

FIGURE 34- TRANSMIT FRAME PULSE OUTPUT TIMING..............................9

FIGURE 35- DROP SIDE RECEIVE SYNCHRONOUS INTERFACE TIMING

(TSEN = 0) .........................................................................................................9

FIGURE 36- DROP SIDE RECEIVE SYNCHRONOUS INTERFACE TIMING

(TSEN = 1) .........................................................................................................9

FIGURE 37- DROP SIDE TRANSMIT SYNCHRONOUS INTERFACE...............9

FIGURE 38- THETA JA VS. AIR FLOW ...............................................................9

FIGURE 39- 160 PIN METRIC PLASTIC QUAD FLAT PACK (R SUFFIX):.........9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

LIST OF TABLES

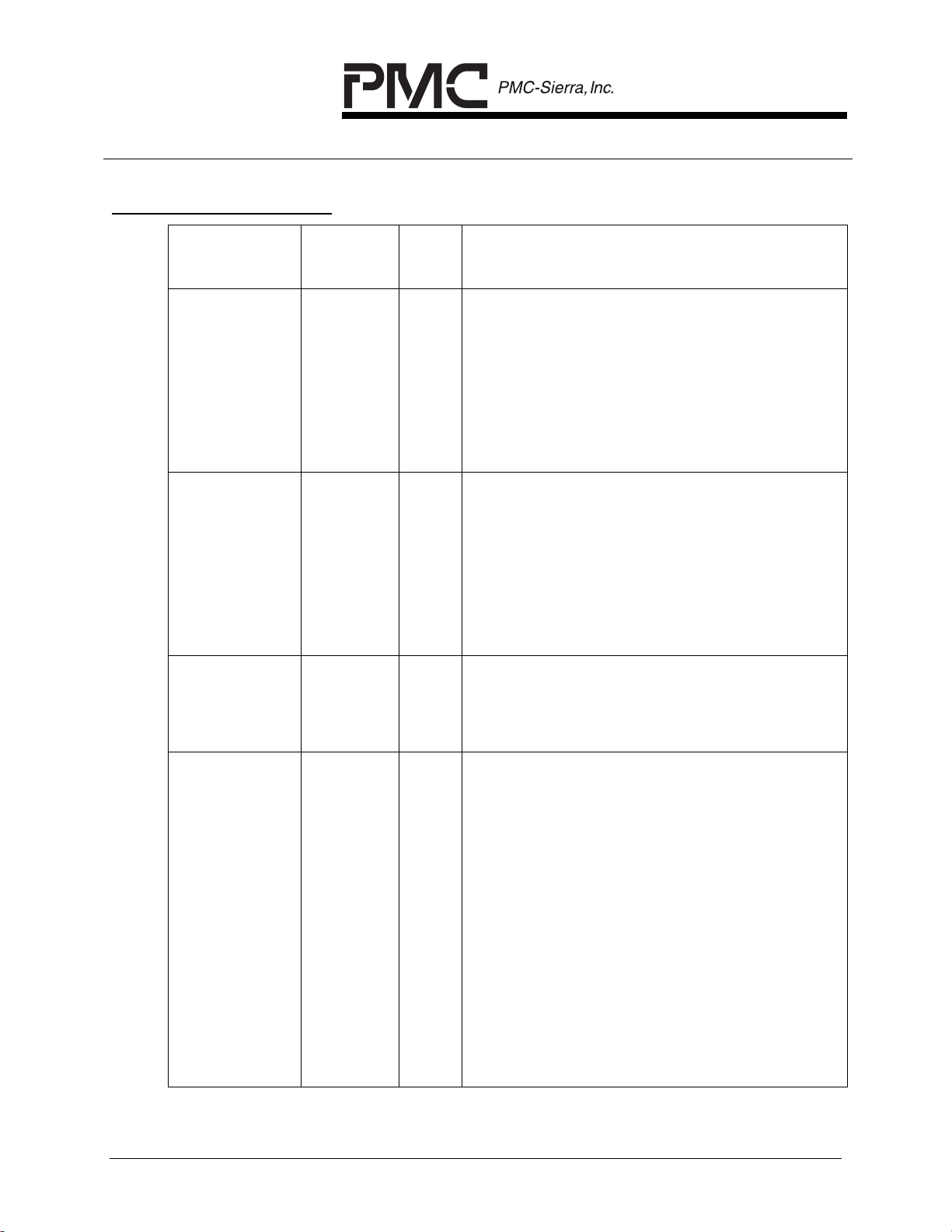

TABLE 1 - ........................................................................................................9

TABLE 2 - TEST MODE REGISTER MEMORY MAP......................................9

TABLE 3 - ........................................................................................................9

TABLE 4 - ........................................................................................................9

TABLE 5 - ........................................................................................................9

TABLE 6 - INSTRUCTION REGISTER............................................................9

TABLE 7 - ........................................................................................................9

TABLE 8 - ........................................................................................................9

TABLE 9 - ........................................................................................................9

TABLE 10 - S/UNI-DUAL ABSOLUTE MAXIMUM RATINGS ............................9

TABLE 11 - S/UNI-DUAL D.C. CHARACTERISTICS.........................................9

TABLE 12 - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 31) .

.........................................................................................................9

TABLE 13 - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 32)

.........................................................................................................9

TABLE 14 - LINE SIDE REFERENCE CLOCK..................................................9

TABLE 15 - RECEIVE FRAME PULSE OUTPUT (FIGURE 33)........................9

TABLE 16 - TRANSMIT FRAME PULSE (FIGURE 34).....................................9

TABLE 17 - DROP SIDE RECEIVE SYNCHRONOUS INTERFACE (FIGURE

35) .........................................................................................................9

TABLE 18 - DROP SIDE RECEIVE SYNCHRONOUS INTERFACE (FIGURE

36) .........................................................................................................9

TABLE 19 - DROP SIDE TRANSMIT SYNCHRONOUS INTERFACE (FIGURE

37) .........................................................................................................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

TABLE 20 - S/UNI-DUAL ORDERING INFORMATION .....................................9

TABLE 21 - S/UNI-DUAL THERMAL INFORMATION........................................9

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

1

FEATURES

Single chip dual ATM User-Network Interface operating at 155.52 and 51.84

•

Mbit/s. Also capable of operating at ATM Forum mid-range PHY subrates of

25.92 and 12.96 Mbit/s.

Provides essential hardware and software compatibility with industry-standard

•

PM5346 S/UNI-LITE device.

Implements the ATM Forum User Network Interface Specification and the

•

ATM physical layer for Broadband ISDN according to CCITT

Recommendation I.432.

Processes two duplex 155.52 Mbit/s STS-3c/STM-1 or 51.84 Mbit/s STS-1

•

data streams with on-chip clock and data recovery and clock synthesis.

Provides Saturn Compliant Inte rface - PHYsical layer (SCI-PHY™) FIFO

•

buffers in both transmit and receive paths with parity support. Compatible

with ATM Forum Utopia Level 2 specification. The FIFOs may be

independently bypassed.

Inserts and extracts the generic flow control (GFC) bits via a simple serial

•

interface and provides a transmit XOFF function to allow for local flow control.

Supports 8-bit and 16-bit multi-PHY modes and a direct dual 8-bit mode.

•

Provides a generic 8-bit microprocessor bus interface for configuration,

•

control, and status monitoring.

Provides a 4-bit output port for external alarms and control.

•

Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan

•

test purposes.

Low power, +5 Volt, CMOS technology.

•

160 pin high performance plastic quad flat pack (MQFP) 28 mm x 28 mm

•

package.

Each receiver section:

Provides a serial interface at 155.52 or 51.84 Mbit/s

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

Recovers the clock and data; frames to the recovered data stream;

•

descrambles the received data; interprets the received payload pointer (H1,

H2); and extracts the STS-3c or STS-1 synchronous payload envelope (VC4)

and path overhead.

Extracts ATM cells from the synchronous payload envelope using ATM cell

•

delineation and provides optional ATM cell payload descrambling, header

check sequence (HCS) error detection and error correction, and

idle/unassigned cell filtering.

Provides a synchronous 8-bit or 16-bit wide, four cell FIFO buffer.

•

Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line

•

alarm indication signal (LAIS), line remote defect indication (LRDI), loss of

pointer (LOP), path alarm indication signal (PAIS), loss of cell delineation

(LCD) and path remote defect indication (PRDI).

Detects signal degrade (SD) or signal fail (SF) threshold crossing

•

alarms based on received B2 errors.

Counts received section BIP-8 (B1) errors, received line BIP-8/24 (B2) errors,

•

line far end block errors (M0 or M1), received path BIP-8 (B3) errors and path

far end block errors (G1).

Filters and captures the automatic protection switch channel (K1, K2) bytes in

•

readable registers and detects APS byte failure.

Captures the synchronization status (S1) byte in a readable register.

•

Counts received cells with uncorrectable HCS errors and received cells with

•

correctable HCS errors.

Counts the total number of valid received cells (i.e. cells with an error-free

•

HCS and cells with a correctable HCS error).

Each transmitter section:

Provides a synchronous 8-bit or 16-bit wide, four cell FIFO buffer.

•

Provides idle/unassigned cell insertion, HCS generation/insertion, and ATM

•

cell payload scrambling; inserts ATM cells into the transmitted STS-3c (STM-

1) or STS-1 synchronous payload envelope using H4 framing.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

Generates the transmit payload pointer (H1, H2) and inserts the path

•

overhead; scrambles the transmitted STS-3c (STM-1) or STS-1 stream and

inserts framing bytes (A1, A2).

Synthesizes the 155.52 MHz or 51.84 MHz transmit clock from a one-eighth

•

frequency reference.

Provides a serial interface at 155.52 or 51.84 Mbit/s

•

Inserts path alarm indication signal (PAIS), path remote defect indication

•

(PRDI), line alarm indication signal (LAIS) and line remote defect indication

(LRDI).

Inserts path BIP-8 codes (B3), path far end block error (G1) indications, line

•

BIP-8/24 codes (B2), line far end block error (M0 or M1) indications, section

BIP-8 codes (B1) to allow performance monitoring at the far end.

Optionally inserts register programmable APS (K1, K2) and synchronization

•

status (S1) bytes.

Allows forced insertion of all zeros data (after scrambling) or corruption of

•

framing byte or section, line, or path BIP-8 codes for diagnostic purposes.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

2

APPLICATIONS

Workstations and Personal Computers

•

Switches and Hubs

•

Routers

•

SONET or SDH ATM Interfaces

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

3

REFERENCES

•

•

CCITT Recommendation G.709, "Synchronous Multiplexing Structure," 1990.

CCITT Recommendation I.432, "B-ISDN User-Network Interface - Physical

Interface Specification," June 1990.

Bell Communications Research, "SONET Transport Systems: Common

•

Generic Criteria, GR-253-CORE," Issue 1, December 1994.

ATM Forum, "ATM User-Network Interface Specification," V3.1, September

•

1994.

T1.105, "American National Standard for Telecommunications - Digital

•

Hierarchy - Optical Interface Rates and Formats Specifications (SONET),"

1991

IEEE 1149.1, "Standard Test Access Port and Boundary Scan Architecture,"

•

May 1990.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

4

APPLICATION EXAMPLES

The PM5348 S/UNI-DUAL is typically used to implement the core of an ATM

User Network Interface by which an ATM terminal is linked to an ATM switching

system using SONET/SDH compatible transport. The S/UNI-DUAL is intended

as a cost effective replacement for two PM5346 S/UNI-LITEs.

The S/UNI-DUAL finds application at either end of terminal-to-switch links or

switch-to-switch links, typically in private network (LAN) situations. The S/UNIDUAL may be loop timed internally (the recovered clock is used in the transmit

direction) or source timed (separate transmit and receive clocks using one

common reference clock).

In these applications, the S/UNI-DUAL interfaces on its line side with an optical

transceiver. The drop side interfaces directly with ATM layer processors or an

ATM Multi-PHY controller. The initial configuration and ongoing control and

monitoring of the S/UNI-DUAL is provided via a generic microprocessor interface.

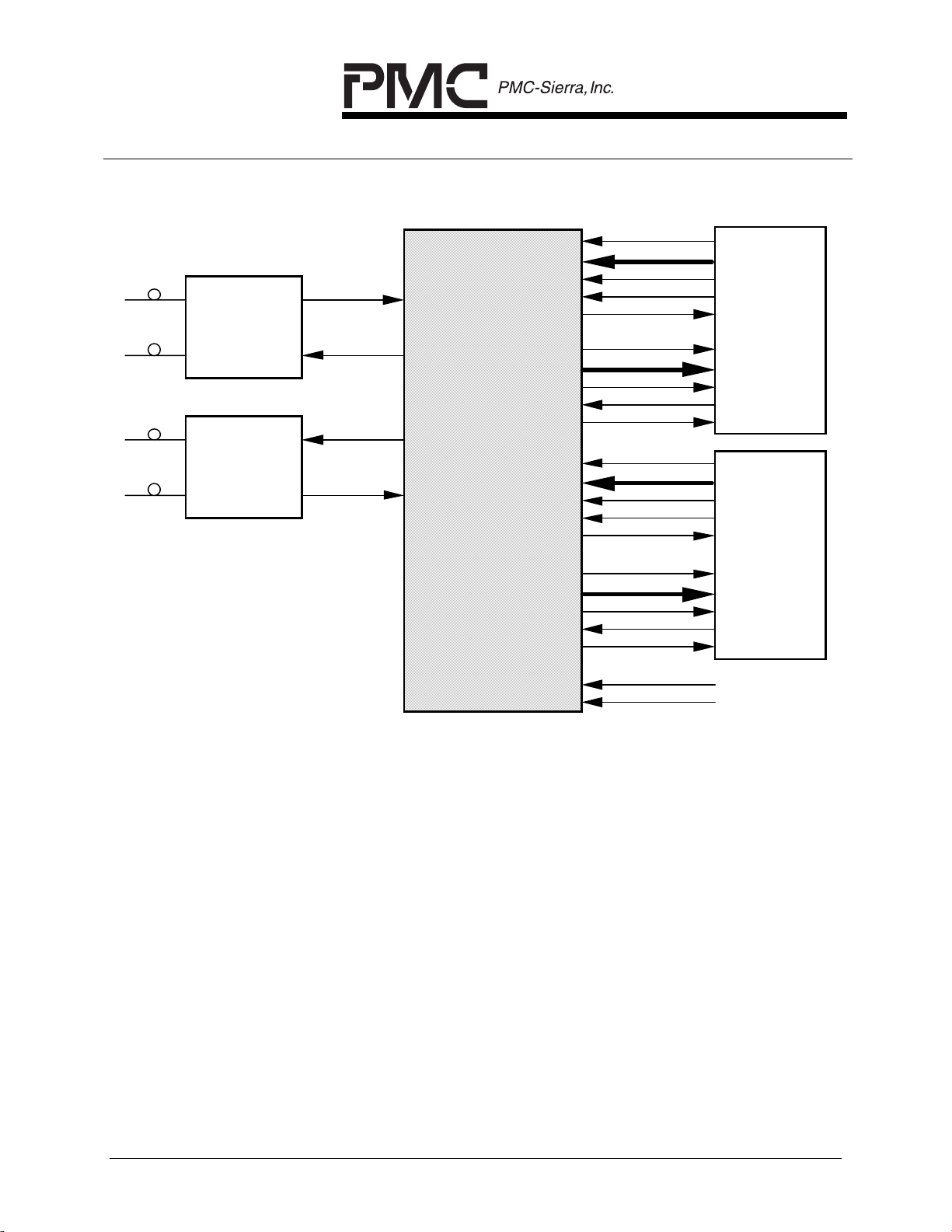

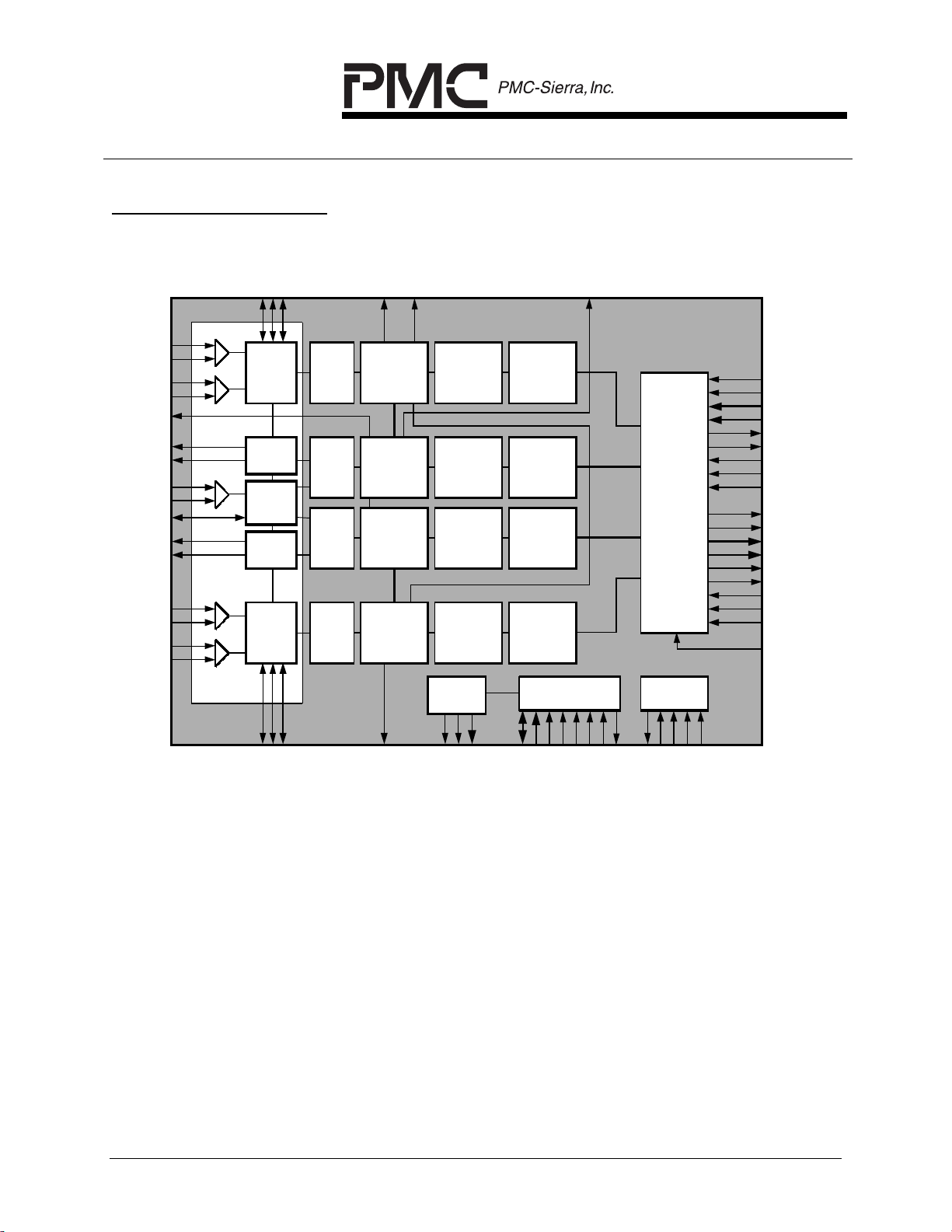

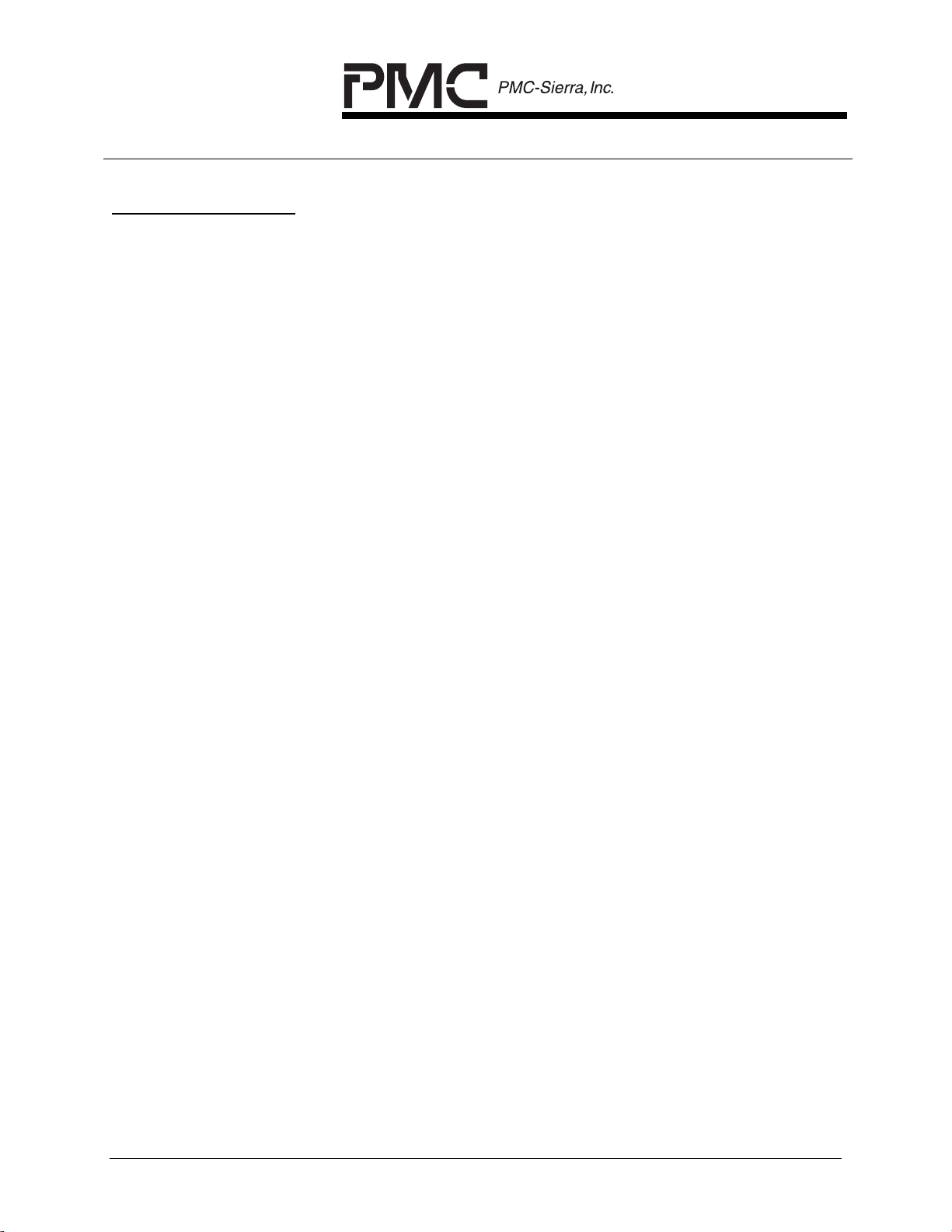

The applications are shown in Figure 1 and Figure 2.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

Figure 1 - Split-Bus 8-bit Direct-PHY ATM Switch Interface

TXPRTY[0]

TDAT[7:0]

TSOC1

TWRENB1

TCA1

RXPRTY[0]

RDAT[7:0]

RSOC1

RRDENB1

RCA1

TXPRTY[1]

TDAT[15:8]

TSOC2

TWRENB2

TCA2

ATM

Processor

#1

ATM

Optical

Transceiver

Optical

Transceiver

RXD1+/-

TXD1+/-

TXD2+/-

RXD2+/-

PM5348

S/UNI-DUAL

SATURN

USER NETWORK

INTERFACE

Processor

RXPRTY[1]

RDAT[15:8]

RSOC2

RRDENB2

RCA2

#2

RFCLK

TFCLK

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

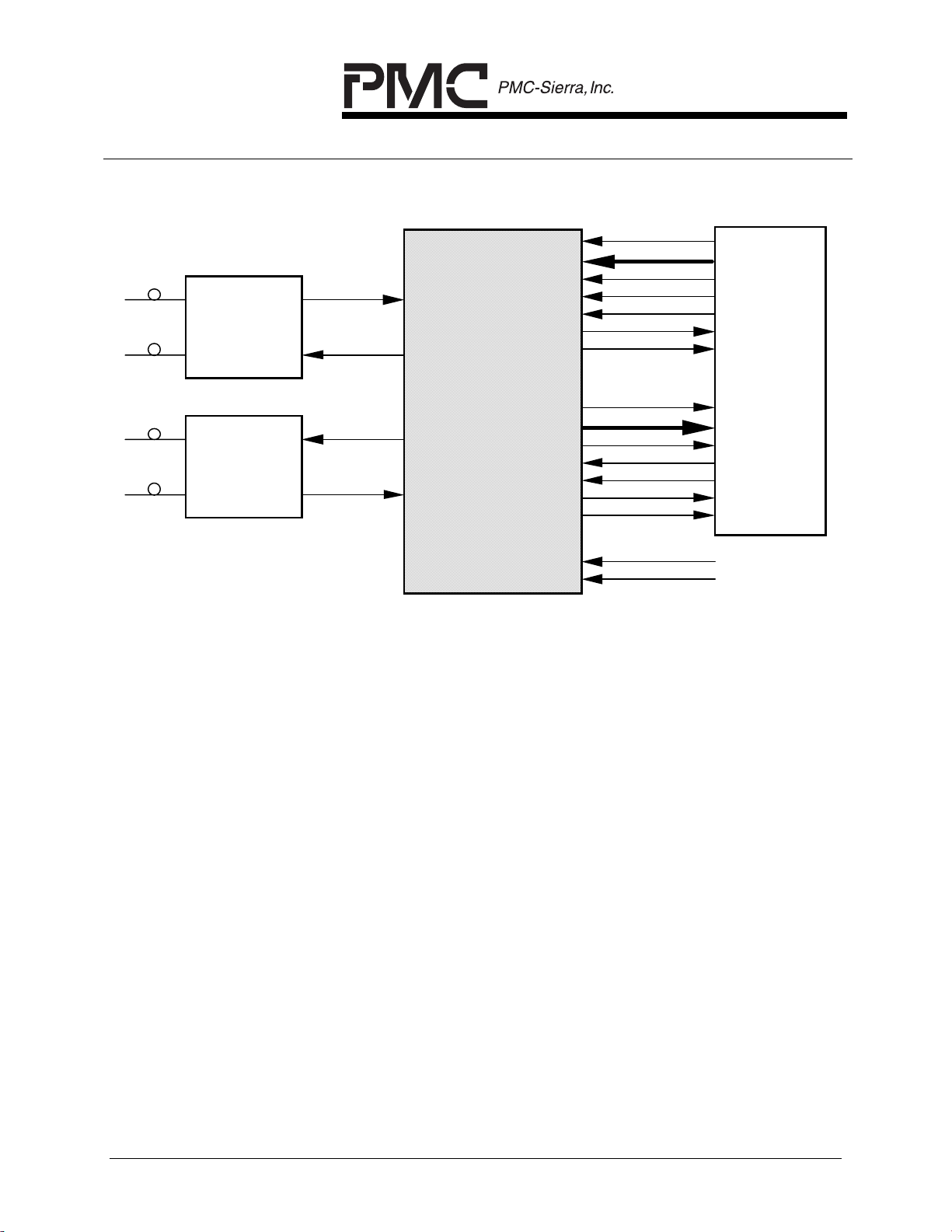

Figure 2 - Direct 8-bit or 16-bit Multi-PHY ATM Switch Interface

TXPRTY[1:0]

TDAT[15:0]

TSOC1

TWRENB1

TWRENB2

TCA1

TCA2

RXPRTY[1:0]

RDAT[15:0]

RSOC1

RRDENB1

RRDENB2

RCA1

RCA2

Multi-

PHY

Controller

Optical

Transceiver

Optical

Transceiver

RXD1+/-

TXD1+/-

TXD2+/-

RXD2+/-

PM5348

S/UNI-DUAL

SATURN

USER NETWORK

INTERFACE

RFCLK

TFCLK

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

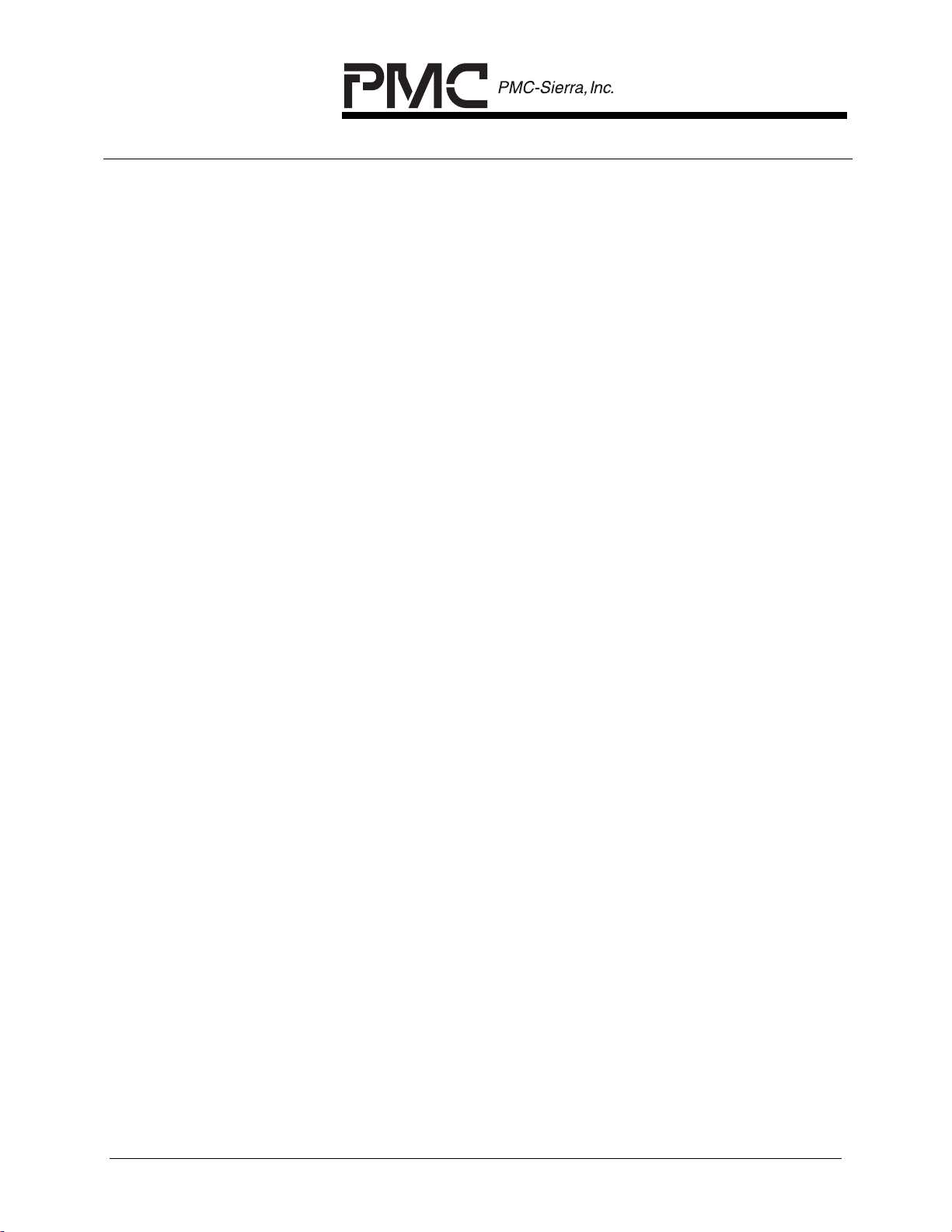

5

RXD1+

RXD1-

ALOS1+

ALOS1-

TXD1+

TXD1-

REFCLK-

TATP

TXD2+

TXD2-

RXD2+

RXD2-

ALOS2+

ALOS2-

BLOCK DIAGRAM

LF1+

Clock

& Data

Recovery

TFP

Driver

Clk Gen.

Driver

Clock

& Data

Recovery

1

LF1-

LFO1

Serial

Parallel

Framer &

to

Overhead

Process or

RFP

RCLK

Rx

Rx ATM Cell

Process or

Rx ATM

4 Cell

FIFO

TCLK

TSOC2

TSOC1

TXPRTY[1:0]

TDA T[15 :0]

TCA2

P arallel

to

Serial

Para llel

to

Serial

Tx

Fram er &

Over head

Processor

Tx

Fram er &

Over head

Processor

Tx ATM Cell

Process or

Tx ATM Cell

Process or

Tx ATM

4 Cell

FIFO

Tx ATM

4 Cell

FIFO

SCI-PHY

In te rfa ce

TCA1

TWRENB2

TWRENB1

TFCLK REFCLK+

RSOC2

RSOC1

RX PRTY[1:0 ]

RDAT[15:0]

RCA2

RCA1

RRDENB2

RRDENB1

RFCLK

TSEN

Serial

to

Para llel

Rx

Framer &

Overhead

Processor

Rx ATM Cell

Processor

Rx ATM

4 Cell

FIFO

Analog Ed ge

LF2+

Output

Port

2

LF2-

LFO2

RCLK

M1

RAL

M2

RAL

]

:0

[1

T

U

O

Microprocessor I/F

]

]

:0

7

D[

B

B

:0

LE

R

S

8

A

C

RDB

W

A[

JTAG

B

B

O

T

T

D

S

T

IN

R

I

B

S

D

T

M

T

S

TCK

T

R

T

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

6

DESCRIPTION

The PM5348 Dual SATURN User Network Interface (S/UNI-DUAL) is a

monolithic integrated circuit that implements SONET/SDH processing and ATM

mapping functions for two 155 Mbit/s or 51Mbit/s ATM User Network Interfaces.

It is compliant with SONET and SDH requirements and ATM Forum User

Network Interface specifications. The S/UNI-DUAL is software configurable,

allowing feature selection without changes to external wiring.

The S/UNI-DUAL receives two SONET/SDH channels via separate bit serial

interfaces, recovers their corresponding clock and data, and processes section,

line and path overhead for each channel. Each channel performs framing (A1,

A2), descrambling, detects alarm conditions, and monitors section, line, and path

bit interleaved parity (B1, B2, B3), accumulating error counts at each level for

performance monitoring purposes. Line and path far end block error indications

(M0 or M1, G1) are also accumulated for each channel. Each channel of the

S/UNI-DUAL interprets the received payload pointers (H1, H2) and extracts the

synchronous payload envelope which carries the received ATM cell payload.

Each channel of the S/UNI-DUAL frames to the ATM payload using cell

delineation. HCS error correction is provided. Idle/unassigned cells may be

dropped according to a programmable filter. Cells are also dropped upon

detection of an uncorrectable header check sequence error. The ATM cell

payloads are descrambled. Legitimate ATM cells are written to a four cell FIFO

buffer.

The ATM cells are read from each channel's FIFO via a synchronous interface

with cell-based handshake using either a split 8 bit wide datapath, a direct 8 bit

wide datapath or a direct 16 bit wide datapath. Counts of received ATM cell

headers that are errored and uncorrectable, those that are errored and

correctable, and all passed cells are accumulated independently for each

channel's performance monitoring purposes.

The S/UNI-DUAL transmits two SONET/SDH channels via separate bit serial

interfaces and formats section, line, and path overhead for each channel. Each

channel performs framing pattern insertion (A1, A2), scrambling, alarm signal

insertion, and creates section, line, and path bit interleaved parity (B1, B2, B3)

as required to allow performance monitoring at the far end. Line and path far end

block error indications (M0 or M1, G1) are also inserted.

Each channel of the S/UNI-DUAL generates the payload pointer (H1, H2) and

inserts the synchronous payload envelope which carries the ATM cell payload. It

supports the insertion of a variety of errors into the transmit stream, such as

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

framing pattern errors, bit interleaved parity errors, and illegal pointers, which are

useful for system diagnostics.

ATM cells are written to each channel's internally programmable-length 4-cell

FIFO via a synchronous interface using either a split 8 bit wide datapath, a direct

8 bit wide datapath, or a direct 16 bit wide datapath. Idle/unassigned cells are

automatically inserted when the internal FIFO contains less than one cell.

Each channel of the S/UNI-DUAL generates the header check sequence and

scrambles the payload of the ATM cells. Payload scrambling can be disabled.

No line rate clocks are required directly by the S/UNI-DUAL as it synthesizes the

transmit clock and recovers the receive clocks using a single 19.44 MHz or 6.48

MHz reference clock.

The S/UNI-DUAL is configured, controlled and monitored via a generic 8-bit

microprocessor bus interface. It is implemented in low power, +5 Volt CMOS

technology. It has TTL and pseudo-ECL (PECL) compatible inputs and

TTL/CMOS compatible outputs and is packaged in a 160 pin MQFP package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

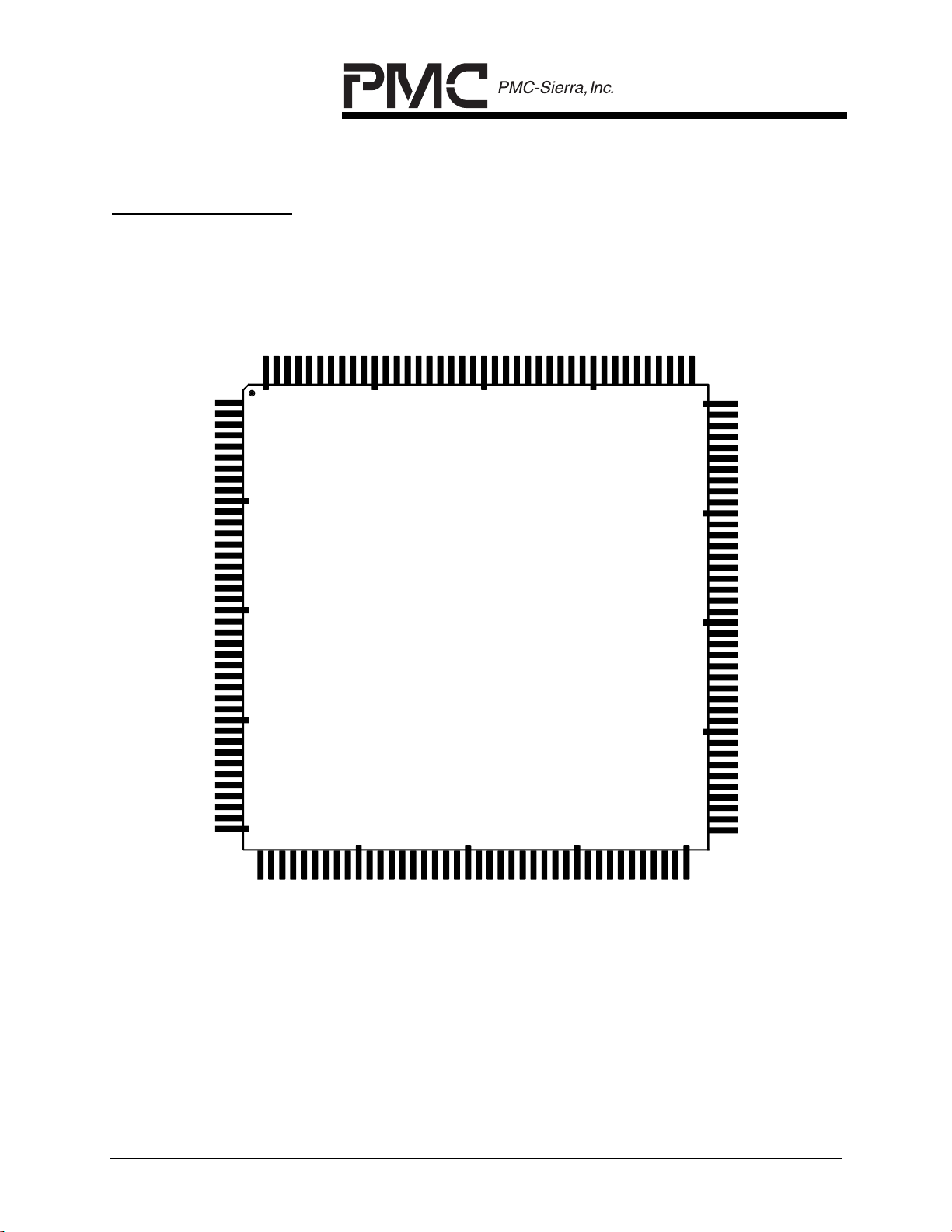

7

PIN DIAGRAM

The S/UNI-DUAL is packaged in a 160 pin MQFP package having a body size of

28mm by 28mm and a pin pitch of 0.65 mm.

C

DC

VS2

]

]

]

D_D

OS1AL

INT B

D[0

R1A

VSS_

VD

D[2

D[1

120

110

100

90

80

R1AVD2

ALOS1+

LF1+

LF1-

LFO 1

R1AVS1

R1AVD1

REFAVS

REFCLKREFCLK+

REFAVD

R1AVSQ 3

RXD1+

RXD1R1AVDQ3

TAVS2

TAVD2

TAVD1

TAVS1

VSS_DC

VDD_DC

TXD1TXD1+

TXVS_AC

R2AVSQ 3

RXD2+

RXD2R2AVDQ3

TXVD_AC

TXD2TXD2+

NC

TATP

R2AVD1

R2AVS1

LFO 2

LF2LF2+

ALOS2+

R2AVD2

PIN 1

TDAT[11]

TDAT[10]

TDAT[9]

TDAT[8]

TDAT[7]

TDAT[6]

TDAT[5]

VDD_DC

TFCLK

VSS_DC

TDAT[4]

TDAT[3]

TDAT[2]

TDAT[1]

TDAT[0]

TSOC2

TSOC1

TCA2

TCA1

VDD_DC

VSS_DC

TW RENB2

TW RENB1

VDD_AC

RFCLK

VSS_AC

RXPRTY[1]

RXPRTY[0]

VDD_DC

VSS_DC

RDAT[15]

RDAT[14]

RDAT[13]

VDD_AC

VSS_AC

RDAT[12]

RDAT[11]

RDAT[10]

RDAT[9]

RDAT[8]

PIN

160

Index

10

20

30

40

12]

TDAT[

13]

TDAT[

14]

TDAT[

15]

TDAT[

TY[0]

TXPR

C

DC

D_D

VSS_

VD

TY[1]

TXPR

C

DC

[0]

[1]

O

LM2

LM1

TD

OUT

TRSTB

TMS

RA

TDI

TCK

RA

150

P

D_D

TSEN

RF

OUT

VSS_

VD

140

LK2

RC

LK1

RC

_AC

K

]

]

]

]

]

D[6

D[4

D[5

D[3

D[7

TFP

VDD

TCL

VSS_AC

130

PM 5348

S/UNI-DUAL

50

60

70

B

C

C

DC

D_D

VSS_

VD

C

[5]

[4]

[3]

[6]

[7]

_AC

RDAT

RDAT

RDAT

VDD

VSS_AC

[2]

[1]

[0]

DC

RDAT

RDAT

VSS_

D_D

VD

_AC

RDAT

RDAT

RDAT

VDD

VSS_AC

OC2

RS

OC1

RS

A2

RC

A1

RC

ENB2

RRD

ENB1

D_D

VD

RRD

DC

RD

VSS_

B

WR

A[2]

A[3]

A[0]

A[4]

A[6]

A[7]

A[8]

ALE

CSB

A[1]

A[5]

VS2

OS2-

RSTB

AL

R2A

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

8

PIN DESCRIPTION

Pin Name Type Pin

Function

No.

RXD1+

RXD1-

PECL

Input

108

107

The receive differential data inputs (RXD1+,

RXD1-) contain the NRZ bit serial receive

stream for channel #1. The receive clock for

channel #1 is recovered from the RXD1+/bit stream. RXD1+/- must be connected to a

differential data source, single ended

operation is not supported for these inputs.

See note 11.

RXD2+

RXD2-

PECL

Input

95

94

The receive differential data inputs (RXD2+,

RXD2-) contain the NRZ bit serial receive

stream for channel #2. The receive clock for

channel #2 is recovered from the RXD2+/-

bit stream. RXD2+/- must be connected to a

differential data source, single ended

operation is not supported for these inputs.

See note 11.

REFCLK+

REFCLK-

ALOS1+

ALOS1-

PECL

Input

PECL

Input

111

112

119

121

The differential reference clock inputs

(REFCLK+, REFCLK-) contain a jitter-free

19.44 MHz or 6.48 MHz reference clock.

See note 11.

The channel #1 analog loss of signal

(ALOS1+/-) differential inputs are used to

indicate a loss of receive signal power.

When ALOS1+/- is asserted, the data on the

channel #1 receive data (RXD1+/-) pins is

forced to all zeros and the phase locked

loop switches to the reference clock

(REFCLK+/-) to keep the recovered clock in

range. These inputs must be DC coupled.

See note 11.RATP may be bonded to pin

119 or may be accessed accessable during

wafer probe. Channel #1 receive analog test

point (RATP1) is provided for production test

purposes. RATP1 is only available while the

device is in Analog Test Mode.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

ALOS2+

ALOS2-

PECL

Input

82

80

The channel #2 analog loss of signal

(ALOS2+/-) differential inputs are used to

indicate a loss of receive signal power.

When ALOS2+/- is asserted, the data on the

channel #2 receive data (RXD2+/-) pins is

forced to all zeros and the phase locked

loop switches to the reference clock

(REFCLK+/-) to keep the recovered clock in

range. These inputs must be DC coupled.

See note 11.

RATP may be bonded to pin 82 or may be

accessed accessable during wafer

probe.Channel #2 receive analog test point

(RATP2) is provided for production test

purposes. RATP2 is only available while the

device is in Analog Test Mode.

RCLK1 Output 138 The receive clock (RCLK1) output provides

a timing reference for S/UNI-DUAL channel

#1 receive outputs. RCLK1 is a divide by

eight of the recovered clock. RALM1 is

updated on the rising edge of RCLK1.

RCLK2 Output 139 The receive clock (RCLK2) output provides

a timing reference for S/UNI-DUAL channel

#2 receive outputs. RCLK2 is a divide by

eight of the recovered clock. RALM2 is

updated on the rising edge of RCLK2.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

RALM1 Output 146 The channel #1 receive alarm (RALM1)

output indicates the state of the receive

framing. RALM1 is low if no receive alarms

are active. RALM1 is high if line AIS, path

AIS, loss of signal (LOS), loss of frame

(LOF), loss of pointer (LOP) or loss of cell

delineation (LCD) is detected in channel #1.

RALM1 is updated on the rising edge of

RCLK1.

RALM1 can be configured to control the

operation of external devices. In this

configuration, the signal levels on RALM1

correspond to register settings.

RALM2 Output 147 The channel #2 receive alarm (RALM2)

output indicates the state of the receive

framing. RALM2 is low if no receive alarms

are active. RALM2 is high if line AIS, path

AIS, loss of signal (LOS), loss of frame

(LOF), loss of pointer (LOP) or loss of cell

delineation (LCD) is detected in channel #2.

RALM2 is updated on the rising edge of

RCLK2.

RALM2 can be configured to control the

operation of external devices. In this

configuration, the signal levels on RALM2

correspond to register settings.

OUT[1]

OUT[0]

Output 145

144

The parallel output port (OUT[1:0]) output is

used to control the operation of external

devices. The signal levels on the parallel

output port correspond to register settings.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

15

PM5348 S/UNI-DUAL

DATA SHEET

PMC-950919 ISSUE 7 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

RFP Output 140 The receive frame pulse (RFP) output is a

selectable 8 kHz signal derived from either

the channel #1 or the channel #2 receive

line clock. RFP pulses high for one

corresponding RCLK cycle every 2430

RCLK cycles for STS-3c (STM-1) TC mode

or every 810 RCLK cycles for STS-1 TC

mode. RFP is updated on the rising edge of

the corresponding RCLK.

TXD1+

TXD1-

TXD2+

TXD2-

Output 98

99

Output 90

91

The transmit differential data outputs

(TXD1+, TXD1-) contain NRZ encoded data

for channel #1.

The transmit differential data outputs

(TXD2+, TXD2-) contain NRZ encoded data

for channel #2.

TFP Output 137 The active high transmit framing pulse (TFP)

output is an 8 kHz timing marker for the

transmitters.

Upon reset the TFP output is held in high

impedance. TFP is enabled as an output

using the TFP_TS bit of register 8.

When enabled, TFP pulses high for one

TCLK cycle every 2430 TCLK cycles for

STS-3c (STM-1) TC mode or every 810

TCLK cycles for STS-1 TC mode. See the

Transmit Section Overhead Processor

section of the Functional Description for

more details on this output.

TFP is updated on the rising edge of TCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

Loading...

Loading...