PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

PM5347

TM

S/

UNI-

155-PLUS

SATURN USER NETWORK INTERFACE

(155.52 MBIT/S & 51.84 MBIT/S, "PLUS")

DATA SHEET

ISSUE 6: JUNE 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

PUBLIC REVISION HISTORY

Issue No. Issue Date Details of Change

6 June, 1998

Data Sheet Reformatted — No Change in

Technical Content.

Generated R6 data sheet from PMC940306, P8

5 Sept 24,

Revision to Eng Doc P7

1996

4 Sept 29,

Revision to Eng Doc P5

1995

3 June 1995

2 Nov. 1994

1 April, 1994 Creation of Document

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................1

3 REFERENCES.........................................................................................1

4 APPLICATION EXAMPLES......................................................................1

5 BLOCK DIAGRAM....................................................................................1

6 DESCRIPTION.........................................................................................1

7 PIN DIAGRAM..........................................................................................1

8 PIN DESCRIPTION..................................................................................1

9 FUNCTIONAL DESCRIPTION.................................................................1

9.1 CLOCK RECOVERY......................................................................1

9.2 SERIAL TO PARALLEL CONVERTER...........................................1

9.3 RECEIVE SECTION OVERHEAD PROCESSOR..........................1

9.4 RECEIVE LINE OVERHEAD PROCESSOR .................................1

9.5 TRANSPORT OVERHEAD EXTRACT PORT................................1

9.6 RECEIVE PATH OVERHEAD PROCESSOR.................................1

9.7 PATH OVERHEAD EXTRACT........................................................1

9.8 RECEIVE ATM CELL PROCESSOR .............................................1

9.9 CLOCK SYNTHESIS.....................................................................1

9.10 PARALLEL TO SERIAL CONVERTER...........................................1

9.11 TRANSMIT SECTION OVERHEAD PROCESSOR.......................1

9.12 TRANSMIT LINE OVERHEAD PROCESSOR...............................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

9.13 TRANSPORT OVERHEAD INSERT PORT...................................1

9.14 TRANSMIT PATH OVERHEAD PROCESSOR..............................1

9.15 PATH OVERHEAD INSERT...........................................................1

9.16 TRANSMIT ATM CELL PROCESSOR...........................................1

9.17 SONET/SDH SECTION AND PATH TRACE BUFFERS................. 1

9.17.1RECEIVE TRACE BUFFER (RTB)......................................1

9.17.2TRANSMIT TRACE BUFFER (TTB)....................................1

9.18 DROP SIDE INTERFACE..............................................................1

9.18.1RECEIVE INTERFACE........................................................1

9.18.2TRANSMIT INTERFACE.....................................................1

9.19 PARALLEL I/O PORT.....................................................................1

9.20 JTAG TEST ACCESS PORT..........................................................1

9.21 MICROPROCESSOR INTERFACE ...............................................1

9.22 REGISTER MEMORY MAP...........................................................1

10 NORMAL MODE REGISTER DESCRIPTION..........................................1

11 TEST FEATURES DESCRIPTION...........................................................1

11.1 TEST MODE REGISTER MEMORY MAP.....................................1

11.2 TEST MODE 0 DETAILS................................................................1

11.3 JTA G TEST POR T..........................................................................1

12 OPERATION.............................................................................................1

12.1 BOARD DESIGN RECOMMENDATIONS......................................1

12.2 INTERFACING TO ECL OR PECL DEVICES................................1

12.3 DRIVING DIFFERENTIAL INPUTS SINGLE ENDED ....................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

12.4 CLOCK RECOVERY......................................................................1

12.5 ATM MAPPING AND OVERHEAD BYTE USAGE.........................1

12.6 CELL DATA STRUCTURE..............................................................1

12.7 BIT ERROR RATE MONITOR........................................................1

12.8 JTAG SUPPORT............................................................................1

13 FUNCTIONAL TIMING .............................................................................1

13.1 OVERHEAD ACCESS ...................................................................1

13.2 GFC ACCESS................................................................................1

13.3 DROP SIDE RECEIVE INTERFACE..............................................1

13.4 DROP SIDE TRANSMIT INTERFACE ...........................................1

14 ABSOLUTE MAXIMUM RATINGS............................................................1

15 D.C. CHARACTERISTICS ........................................................................1

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS..........1

17 S/UNI-PLUS TIMING CHARA CTERISTICS..............................................1

18 ORDERING AND THERMAL INFORMATION ..........................................1

19 MECHANICAL INFORMATION.................................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

LIST OF REGISTERS

REGISTER 0X00: S/UNI-PLUS MASTER RESET AND IDENTITY / LOAD

PERFORMANCE METERS......................................................................1

REGISTER 0X01: S/UNI-PLUS MASTER CONFIGURATION ............................1

REGISTER 0X02: S/UNI-PLUS MASTER INTERRUPT STATUS .......................1

REGISTER 0X03: S/UNI-PLUS MASTER CONTROL ........................................1

REGISTER 0X04: S/UNI-PLUS MASTER AUTO ALARM/MONITOR.................1

REGISTER 0X05: S/UNI-PLUS CLOCK SYNTHESIS CONTROL AND STATUS1

REGISTER 0X06: S/UNI-PLUS CLOCK RECOVERY CONTROL AND STATUS1

REGISTER 0X07: S/UNI-PLUS PARALLEL I/O PORT .......................................1

REGISTER 0X08: S/UNI-PLUS PARALLEL INPUT PORT INTERRUPT............1

REGISTER 0X09: S/UNI-PLUS PARALLEL INPUT PORT ENABLE ..................1

REGISTER 0X0A: S/UNI-PLUS TRANSMIT J0/Z0 .............................................1

REGISTER 0X0B: S/UNI-PLUS APS CONTROL/STATUS..................................1

REGISTER 0X0C: S/UNI-PLUS RECEIVE K1....................................................1

REGISTER 0X0D: S/UNI-PLUS RECEIVE K2....................................................1

REGISTER 0X0E: S/UNI-PLUS RECEIVE S1 ....................................................1

REGISTER 0X0F: S/UNI-PLUS TRANSMIT S1..................................................1

REGISTER 0X10: RSOP CONTROL/INTERRUPT ENABLE..............................1

REGISTER 0X11: RSOP STATUS/INTERRUPT STATUS ...................................1

REGISTER 0X12: RSOP SECTION BIP-8 LSB..................................................1

REGISTER 0X13: RSOP SECTION BIP-8 MSB.................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

REGISTER 0X14: TSOP CONTROL...................................................................1

REGISTER 0X15: TSOP DIAGNOSTIC..............................................................1

REGISTER 0X18: RLOP CONTROL/STATUS.....................................................1

REGISTER 0X19: RLOP INTERRUPT ENABLE/INTERRUPT STATUS.............1

REGISTER 0X1A: RLOP LINE BIP-24/8 LSB.....................................................1

REGISTER 0X1B: RLOP LINE BIP-24/8.............................................................1

REGISTER 0X1C: RLOP LINE BIP-24/8 MSB....................................................1

REGISTER 0X1D: RLOP LINE FEBE LSB .........................................................1

REGISTER 0X1E: RLOP LINE FEBE .................................................................1

REGISTER 0X1F: RLOP LINE FEBE MSB.........................................................1

REGISTER 0X20: TLOP CONTROL...................................................................1

REGISTER 0X21: TLOP DIAGNOSTIC ..............................................................1

REGISTER 0X22: TLOP TRANSMIT K1 .............................................................1

REGISTER 0X23: TLOP TRANSMIT K2 .............................................................1

REGISTER 0X28: SSTB CONTROL...................................................................1

REGISTER 0X29: SSTB SECTION TRACE IDENTIFIER STATUS.....................1

REGISTER 0X2A: SSTB INDIRECT ADDRESS REGISTER..............................1

REGISTER 0X2B: SSTB INDIRECT DATA REGISTER.......................................1

REGISTER 0X30: RPOP STATUS/CONTROL....................................................1

REGISTER 0X31: RPOP INTERRUPT STATUS .................................................1

REGISTER 0X32: RPOP POINTER INTERRUPT STATUS ................................1

REGISTER 0X33: RPOP INTERRUPT ENABLE................................................1

REGISTER 0X34: RPOP POINTER INTERRUPT ENABLE ...............................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

REGISTER 0X35: RPOP POINTER LSB............................................................1

REGISTER 0X36: RPOP POINTER MSB AND RDI FILTER CONTROL............1

REGISTER 0X37: RPOP PATH SIGNAL LABEL.................................................1

REGISTER 0X38: RPOP PATH BIP-8 LSB .........................................................1

REGISTER 0X39: RPOP PATH BIP-8 MSB ........................................................1

REGISTER 0X3A: RPOP PATH FEBE LSB.........................................................1

REGISTER 0X3B: RPOP PATH FEBE MSB........................................................1

REGISTER 0X3C: RPOP AUXILIARY RDI..........................................................1

REGISTER 0X3D: RPOP ERROR EVENT CONTROL.......................................1

REGISTER 0X40: TPOP CONTROL/DIAGNOSTIC............................................1

REGISTER 0X41: TPOP POINTER CONTROL..................................................1

REGISTER 0X43: TPOP CURRENT POINTER LSB..........................................1

REGISTER 0X44: TPOP CURRENT POINTER MSB.........................................1

REGISTER 0X45: TPOP ARBITRARY POINTER LSB .......................................1

REGISTER 0X46: TPOP ARBITRARY POINTER MSB ......................................1

REGISTER 0X47: TPOP PATH TRACE...............................................................1

REGISTER 0X48: TPOP PATH SIGNAL LABEL .................................................1

REGISTER 0X49: TPOP PATH STATUS..............................................................1

REGISTER 0X4A: TPOP PATH USER CHANNEL ..............................................1

REGISTER 0X4B: TPOP PATH GROWTH #1 (Z3)..............................................1

REGISTER 0X4C: TPOP PATH GROWTH #2 (Z4)..............................................1

REGISTER 0X4D: TPOP PATH GROWTH #3 (Z5)..............................................1

REGISTER 0X50: RACP CONTROL...................................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

REGISTER 0X51: RACP INTERRUPT STATUS..................................................1

REGISTER 0X52: RACP INTERRUPT ENABLE/CONTROL..............................1

REGISTER 0X53: RACP MATCH HEADER PATTERN .......................................1

REGISTER 0X54: RACP MATCH HEADER MASK.............................................1

REGISTER 0X55: RACP CORRECTABLE HCS ERROR COUNT (LSB) ...........1

REGISTER 0X56: RACP CORRECTABLE HCS ERROR COUNT (MSB) ..........1

REGISTER 0X57: RACP UNCORRECTABLE HCS ERROR COUNT (LSB)......1

REGISTER 0X58: RACP UNCORRECTABLE HCS ERROR COUNT (MSB).....1

REGISTER 0X59: RACP RECEIVE CELL COUNTER (LSB) .............................1

REGISTER 0X5A: RACP RECEIVE CELL COUNTER .......................................1

REGISTER 0X5B: RACP RECEIVE CELL COUNTER (MSB)............................1

REGISTER 0X5C: RACP GFC CONTROL AND MISCELLANEOUS CONTROL1

REGISTER 0X60: TACP CONTROL/STATUS......................................................1

REGISTER 0X61: TACP IDLE/UNASSIGNED CELL HEADER PATTERN......1

REGISTER 0X62: TACP IDLE/UNASSIGNED CELL PAYLOAD OCTET

PATTERN..................................................................................................1

REGISTER 0X63: TACP FIFO CONTROL...........................................................1

REGISTER 0X64: TACP TRANSMIT CELL COUNTER (LSB)............................1

REGISTER 0X65: TACP TRANSMIT CELL COUNTER ......................................1

REGISTER 0X66: TACP TRANSMIT CELL COUNTER (MSB)...........................1

REGISTER 0X67: TACP FIXED STUFF / GFC ...................................................1

REGISTER 0X68: SPTB CONTROL...................................................................1

REGISTER 0X69: SPTB PATH TRACE IDENTIFIER STATUS............................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

REGISTER 0X6A: SPTB INDIRECT ADDRESS REGISTER..............................1

REGISTER 0X6B: SPTB INDIRECT DATA REGISTER.......................................1

REGISTER 0X6C: SPTB EXPECTED PATH SIGNAL LABEL.............................1

REGISTER 0X6D: SPTB PATH SIGNAL LABEL STATUS...................................1

REGISTER 0X70: BERM CONTROL..................................................................1

REGISTER 0X71: BERM INTERRUPT...............................................................1

REGISTER 0X72: BERM LINE BIP ACCUMULATION PERIOD LSB.................1

REGISTER 0X73: BERM LINE BIP ACCUMULATION PERIOD MSB................1

REGISTER 0X74: BERM LINE BIP THRESHOLD LSB......................................1

REGISTER 0X75: BERM LINE BIP THRESHOLD MSB.....................................1

REGISTER 0X80: MASTER TEST......................................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

LIST OF FIGURES

FIGURE 1 - TYPICAL STS-3C ATM SWITCH PORT INTERFACE....................1

FIGURE 2 - APPLICATION WITH CLOCK RECOVERY & CLOCK SYNTHESIS

BYPASSED .........................................................................................................1

FIGURE 3 - STS-3C/STM-1 AND STS-1 JITTER TOLERANCE........................1

FIGURE 4 - POINTER INTERPRETATION STATE DIAGRAM...........................1

FIGURE 5 - CELL DELINEATION STATE DIAGRAM.........................................1

FIGURE 6 - HCS VERIFICATION STATE DIAGRAM .........................................1

FIGURE 7 - STS-3C DEFAULT TRANSPORT OVERHEAD VALUES................1

FIGURE 8 - STS-1 DEFAULT TRANSPORT OVERHEAD VALUES...................1

FIGURE 9 - DEFAULT PATH OVERHEAD VALUES...........................................1

FIGURE 10- INTERFACING S/UNI-PLUS TO ECL OR PECL............................1

FIGURE 11- SINGLE ENDED DRIVING DIFFERENTIAL INPUTS....................1

FIGURE 12-........................................................................................................1

FIGURE 13- STS-1 MAPPING............................................................................1

FIGURE 14- STS-3C (STM-1) MAPPING...........................................................1

FIGURE 15- 16-BIT WIDE, 27 WORD STRUCTURE..........................................1

FIGURE 16- 8-BIT WIDE, 53 WORD STRUCTURE............................................1

FIGURE 17- BOUNDARY SCAN ARCHITECTURE............................................1

FIGURE 18- TAP CONTROLLER FINITE STATE MACHINE ..............................1

FIGURE 19- INPUT OBSERVATION CELL (IN_CELL).......................................1

FIGURE 20- OUTPUT CELL (OUT_CELL).........................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

FIGURE 21- BIDIRECTIONAL CELL (IO_CELL)................................................1

FIGURE 22- TRANSPORT OVERHEAD EXTRACTION.....................................1

FIGURE 23- TRANSPORT OVERHEAD ORDERWIRE AND USER CHANNEL

EXTRACTION.....................................................................................................1

FIGURE 24- TRANSPORT OVERHEAD DATA LINK CLOCK AND DATA

EXTRACTION.....................................................................................................1

FIGURE 25- PATH OVERHEAD EXTRACTION..................................................1

FIGURE 26- TRANSPORT OVERHEAD INSERTION ........................................1

FIGURE 27- TRANSPORT OVERHEAD ORDERWIRE AND USER CHANNEL

INSERTION.........................................................................................................1

FIGURE 28- TRANSPORT OVERHEAD DATA LINK CLOCK AND DATA

INSERTION.........................................................................................................1

FIGURE 29- PATH OVERHEAD INSERTION......................................................1

FIGURE 30- GFC EXTRACTION PORT.............................................................1

FIGURE 31- GFC INSERTION PORT.................................................................1

FIGURE 32- RECEIVE SYNCHRONOUS FIFO, TSEN=0..................................1

FIGURE 33- RECEIVE SYNCHRONOUS FIFO, TSEN=1..................................1

FIGURE 34- TRANSMIT SYNCHRONOUS FIFO...............................................1

FIGURE 35- MICROPROCESSOR INTERFACE READ TIMING........................1

FIGURE 36- MICROPROCESSOR INTERFACE WRITE TIMING ......................1

FIGURE 37- LINE SIDE RECEIVE INTERFACE TIMING...................................1

FIGURE 38- RECEIVE ALARM OUTPUT TIMING .............................................1

FIGURE 39- RECEIVE OVERHEAD ACCESS TIMING......................................1

FIGURE 40- RECEIVE GFC ACCESS TIMING..................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

FIGURE 41- LINE SIDE TRANSMIT INTERFACE TIMING.................................1

FIGURE 42- TRANSMIT ALARM INPUT TIMING...............................................1

FIGURE 43- TRANSMIT OVERHEAD ACCESS TIMING....................................1

FIGURE 44- TRANSMIT GFC ACCESS TIMING................................................1

FIGURE 45- DROP SIDE RECEIVE INTERFACE TIMING, TSEN = 0 ...............1

FIGURE 46- DROP SIDE RECEIVE INTERFACE TIMING, TSEN = 1 ...............1

FIGURE 47- DROP SIDE TRANSMIT INTERFACE............................................1

FIGURE 48- JTAG PORT INTERFACE TIMING..................................................1

FIGURE 49- 208 PIN PLASTIC QUAD FLAT PACK (R SUFFIX):.......................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

LIST OF TABLES

TABLE 1 - ........................................................................................................1

TABLE 2 - ........................................................................................................1

TABLE 3 - ........................................................................................................1

TABLE 5 - ........................................................................................................1

TABLE 6 - ........................................................................................................1

TABLE 7 - ........................................................................................................1

TABLE 8 - ........................................................................................................1

TABLE 9 - ........................................................................................................1

TABLE 10 - INSTRUCTION REGISTER............................................................1

TABLE 11 - ........................................................................................................1

TABLE 12 - S/UNI-PLUS ABSOLUTE MAXIMUM RATINGS ............................1

TABLE 13 - S/UNI-PLUS D.C. CHARACTERISTICS.........................................1

TABLE 14 - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 35) .

.........................................................................................................1

TABLE 15 - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 36)

.........................................................................................................1

TABLE 16 - LINE SIDE RECEIVE INTERFACE (FIGURE 37)...........................1

TABLE 17 - RECEIVE ALARM OUTPUT (FIGURE 38).....................................1

TABLE 18 - RECEIVE OVERHEAD ACCESS (FIGURE 39) .............................1

TABLE 19 - RECEIVE GFC ACCESS (FIGURE 40)..........................................1

TABLE 20 - LINE SIDE TRANSMIT INTERFACE (FIGURE 41)........................1

TABLE 21 - TRANSMIT ALARM INPUT (FIGURE 42) ......................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

TABLE 22 - TRANSMIT OVERHEAD ACCESS (FIGURE 43)...........................1

TABLE 23 - TRANSMIT GFC ACCESS (FIGURE 44).......................................1

TABLE 24 - DROP SIDE RECEIVE INTERFACE (FIGURE 45, FIGURE 46)....1

TABLE 25 - DROP SIDE TRANSMIT INTERFACE (FIGURE 47)......................1

TABLE 26 - JTAG PORT INTERFACE (FIGURE 48).........................................1

TABLE 27 - S/UNI-PLUS ORDERING INFORMATION .....................................1

TABLE 28 - S/UNI-PLUS THERMAL INFORMATION........................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiii

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiv

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

1

FEATURES

Monolithic Saturn User Network Interface that implements the ATM physical

•

layer for Broadband ISDN according to ANSI, ITU, and ATM Forum

specifications.

Processes duplex 155.52 Mbit/s STS-3c/STM-1 or 51.84 Mbit/s STS-1 data

•

streams with on-chip clock and data recovery and clock synthesis.

Provides Saturn Compliant Inte rface - PHYsical layer (SCI-PHY™) FIFO

•

buffers in both transmit and receive paths with parity support.

Provides a generic 8-bit microprocessor bus interface for configuration,

•

control, and status monitoring.

Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan

•

board test purposes.

Low power, +5 Volt, CMOS technology.

•

208 pin high performance plastic quad flat pack (PQFP) 28 mm x 28 mm

•

package.

Industrial temperature range operation (-40°C to +85°C).

•

The receiver section:

Provides a serial interface at 155.52 or 51.84 Mbit/s.

•

Recovers the clock and data.

•

Frames to and descrambles the recovered stream.

•

Filters and captures the automatic protection switch channel (K1, K2) bytes in

•

readable registers and detects APS byte failure.

Captures the synchronization status (S1) byte in a readable register.

•

Interprets the received payload pointer (H1, H2) and extracts the STS-3c/1

•

(STM-1) synchronous payload envelope and path overhead.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

Extracts ATM cells from the received STS-3c/1 (STM-1) synchronous payload

•

envelope using ATM cell delineation and provides optional ATM cell payload

descrambling, header check sequence (HCS) error detection and correction,

and idle/unassigned cell filtering.

Provides a generic 16 bit or 8 bit wide datapath interface to read extracted

•

cells from an internal four cell FIFO buffer.

Extracts all transport overhead bytes and serializes them at 5.184 Mbit/s for

•

optional external processing.

Extracts the section user channel (F1) and the orderwire channels (E1, E2)

•

and serializes them into three independent 64 kbit/s streams for optional

external processing.

Extracts the data communication channels (D1-D3, D4-D12) and serializes

•

them at 192 kbit/s (D1-D3) and 576 kbit/s (D4-D12) for optional external

processing.

Extracts all path overhead bytes and serializes them at 576 kbit/s for optional

•

external processing.

Extracts the 16 or 64 byte section trace (J0) sequence and the 16 or 64 byte

•

path trace (J1) sequence into internal register banks.

Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line

•

alarm indication signal (LAIS), line remote defect indication (LRDI), loss of

pointer (LOP), path alarm indication signal (PAIS), path remote defect

indication signal (PRDI) and loss of cell delineation (LCD).

Counts received section BIP-8 (B1) errors, received line BIP-24/8 (B2) errors,

•

line far end block errors (M0 or M1), received path BIP-8 (B3) errors and path

far end block errors (G1) for performance monitoring purposes.

Counts received cells written into the receive FIFO, received HCS errored

•

cells that are discarded, and received HCS errored cells that are corrected

and passed through the receive FIFO.

Extracts and serializes the GFC field from all received cells (including

•

idle/unassigned cells) for external processing.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

The transmitter section:

Provides an internal four cell FIFO into which cells are written using a generic

•

16-bit or 8-bit wide datapath interface.

Inserts the generic flow control (GFC) bits via a simple serial interface and

•

provides a transmit XOFF function to allow fo r local flow control.

Counts transmit cells read from the transmit FIFO.

•

Provides idle/unassigned cell insertion, HCS generation/insertion, and ATM

•

cell payload scrambling.

Inserts ATM cells into the transmitted STS-3c/1 (STM-1) synchronous

•

payload envelope.

Inserts a register programmable path signal label (C2).

•

Generates the transmit payload pointer (H1, H2) and inserts the path

•

overhead.

Optionally inserts the 16 or 64 byte section trace (J0) sequence and the 16 or

•

64 byte path trace (J1) sequence from internal register banks.

Optionally inserts externally generated path overhead bytes received via a

•

576 kbit/s serial interface.

Optionally inserts externally generated data communication channels (D1-D3,

•

D4-D12) via a 192 kbit/s (D1-D3) serial stream and a 576 kbit/s (D4-D12)

serial stream.

Optionally inserts externally generated section user channel (F1) and

•

externally generated orderwire channels (E1, E2) via three 64 kbit/s serial

interfaces.

Optionally inserts externally generated transport overhead bytes received via

•

a 5.184 Mbit/s serial interface.

Scrambles the transmitted STS-3c/1 (STM-1) stream and inserts the framing

•

bytes (A1, A2).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

Synthesizes the 155.52 MHz or 51.84 MHz transmit clock from a 19.44 MHz

•

or 6.48 MHz reference.

Provides a serial interface at 155.52 Mbit/s or 51.84 Mbit/s.

•

Optionally inserts path alarm indication signal (PAIS), path remote defect

•

indication (PRDI), line alarm indication signal (LAIS) and line remote defect

indication (LRDI) indication.

Optionally inserts register programmable APS (K1, K2) and synchronization

•

status (S1) bytes.

Inserts path BIP-8 codes (B3), path far end block error (G1) indications, line

•

BIP-24/8 codes (B2), line fa r end block error (M0 or M1) indications, section

BIP-8 codes (B1) to allow performance monitoring at the far end.

Allows forced insertion of all zero s data (after scrambling), the corruption of

•

the framing bytes or the corruption of the section, line, or path BIP-8 codes for

diagnostic purposes.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

2

APPLICATIONS

SONET/SDH Based ATM Switching Systems

•

SONET/SDH Based ATM Terminals

•

B-ISDN User Network Interfaces

•

B-ISDN Test Equipment

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

3

REFERENCES

1. ITU Recommendation G.709 DRAFT - "Synchronous Multiplexing Structure",

COM XVIII-R 105-E.

2. ITU Recommendation I.432 DRAFT - "B-ISDN User-Network

Interface-Physical Interface Specification", COM XVIII-R 80-E.

3. Bell Communications Research - SONET Transport Systems: Common

Generic Criteria, GR-253-CORE, Issue 1, December 1994.

4. ATM Forum - ATM User-Network Interface Specification, V3.0, October, 1993.

5. ATM Forum - BISDN Inter Carr ier Interface Specification, V1.0, August, 1993.

6. IEEE 1149.1 - Standard Test Access Port and Boundary Scan Architecture,

May 21, 1990.

7. T1.105, American National Standard for Telecommunications - Digital

Hierarchy - Optical Interface Rates and Formats Specifications (SONET),

1991

8. T1X1.3/93-006R3, Draft American National Standard for Telecommunications,

Synchronous Optical Network (SONET): Jitter at Network Interfaces

9. T1E1.2/94-002R1, Draft American National Standard for Telecommunications,

Broadband ISDN and DS1/ATM User Network Interfaces: Physical Layer

Specification

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

4

APPLICATION EXAMPLES

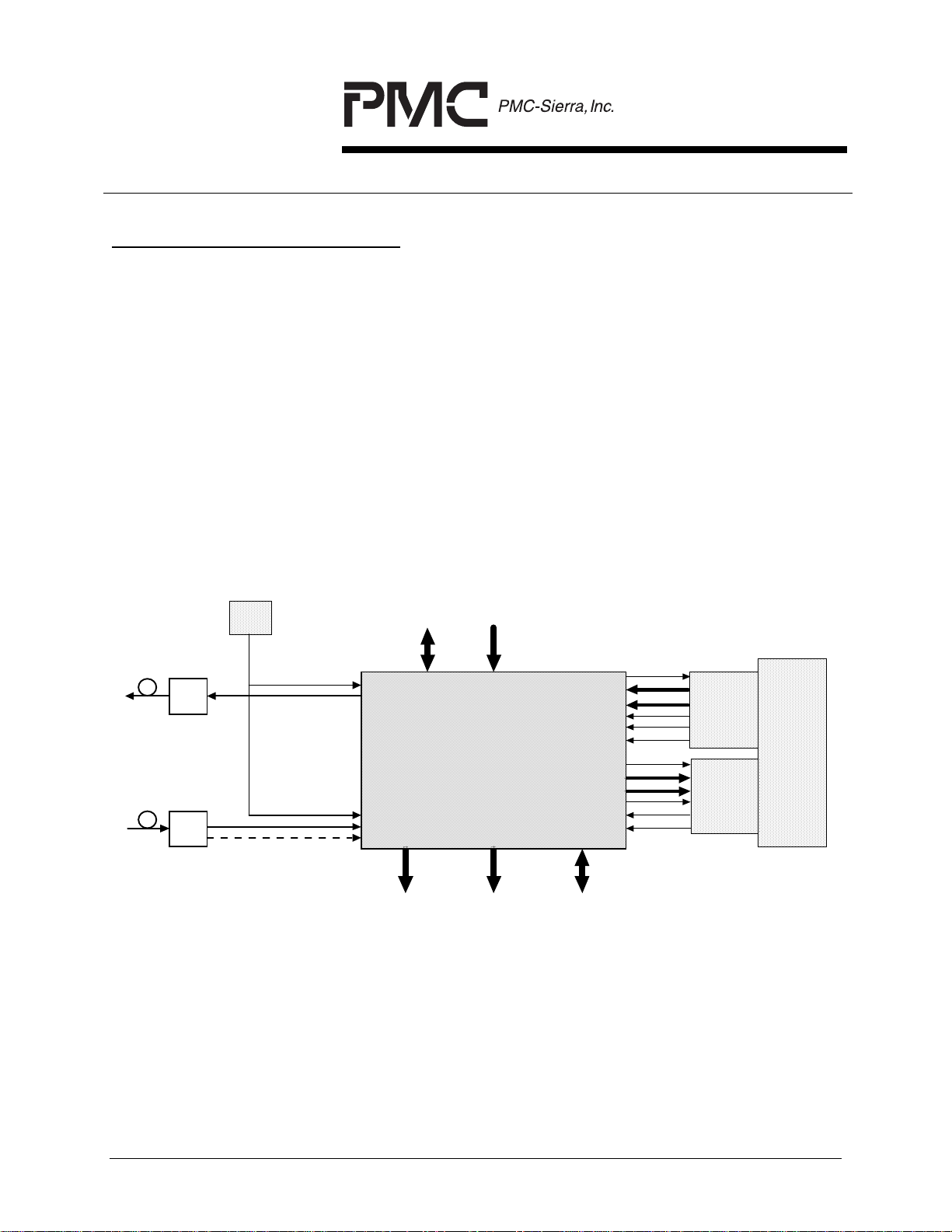

The S/UNI-PLUS is used to implement the core physical layer functions of an

ATM User Network Interface or BISDN Inter Carrier Interface. The S/UNI-PLUS

may find application at either end of switch-to-switch links or switch-to-terminal

links, both in public network (WAN) and private network (LAN) situations. In a

typical STS-3c (STM-1) application, the S/UNI-PLUS perfo rms clock and data

recovery for the receive direction and clock synthesis for the transmit direction of

the line interface. On the drop side, the S/UNI-PLUS interfaces directly with ATM

layer processors and switching or adaptation functions using a SCI-PHY™

synchronous FIFO style interface. The initial configuration and ongoing control

and monitoring of the S/UNI-PLUS are normally provided via a generic

microprocessor interface. This application is shown in Figure 1.

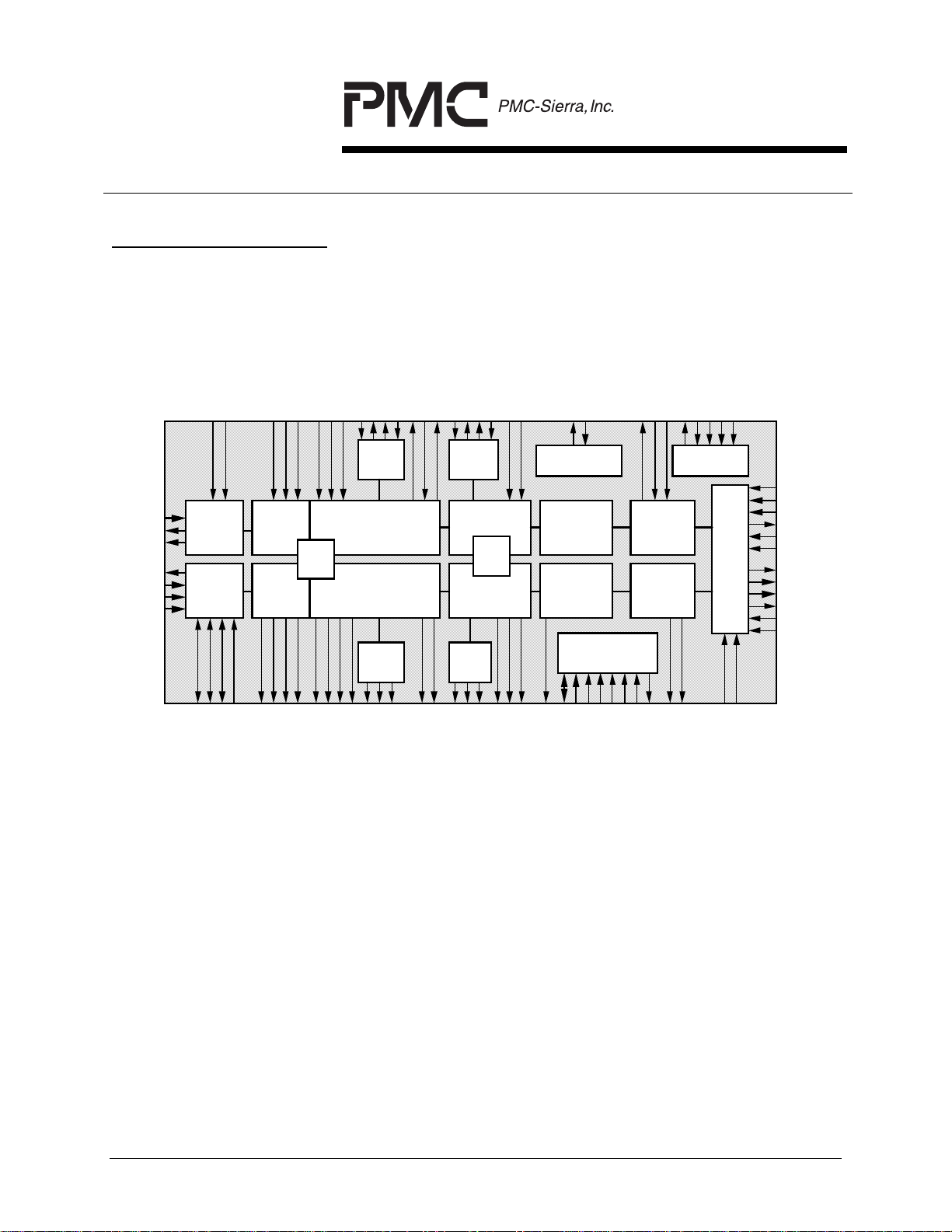

Figure 1 - Typical STS-3c ATM Switch Port Interface

TRANSMIT

ALARM INSERT

SIGNALS

PM5347 S/UNI-PLUS

SONET/SDH

TCA

TXPRTY[1:0]

TDAT[15:0]

TSOC

TWRENB

TFCLK

RCA

RXPRTY[1:0]

RDAT[15:0]

RSOC

RRDENB

RFCLK

TRANSMIT

ATM

PROCESS

RECEIVE

ATM

PROCESS

SWITCHING

NETWORK

E/O

O/E

Ref.

Clock

19.44 MHz

TRCLK+/-

TXD+/-

RRCLK+/-

RXD+/-

ALOS+/-

TRANSMIT

OVERHEAD

INSERT

USER NETWORK INTERFACE

RECEIVE

OVERHEAD

EXTRACT

RECEIVE

ALARM DETECT

SIGNALS

MICRO BUS

FOR CONFIG, STATUS

AND CONTROL

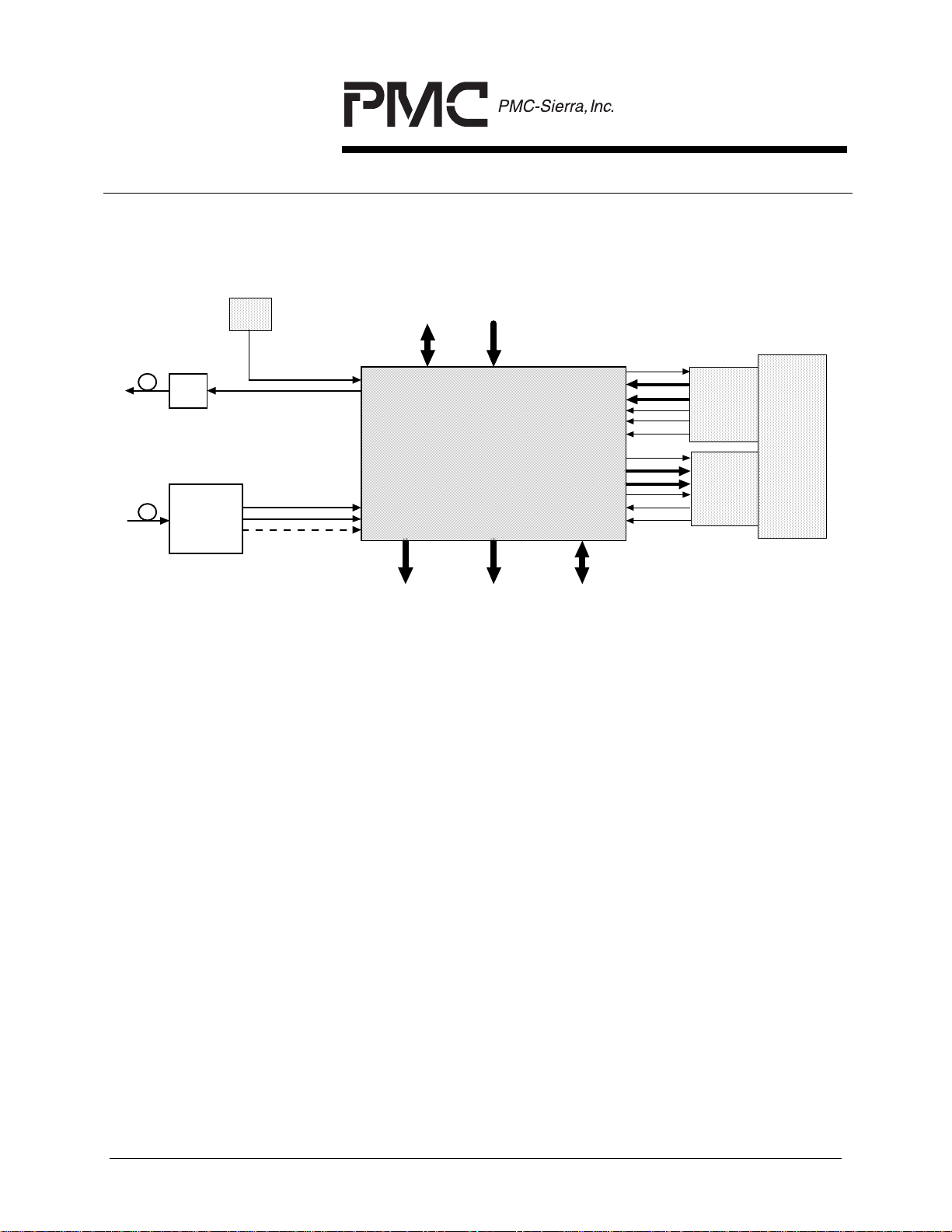

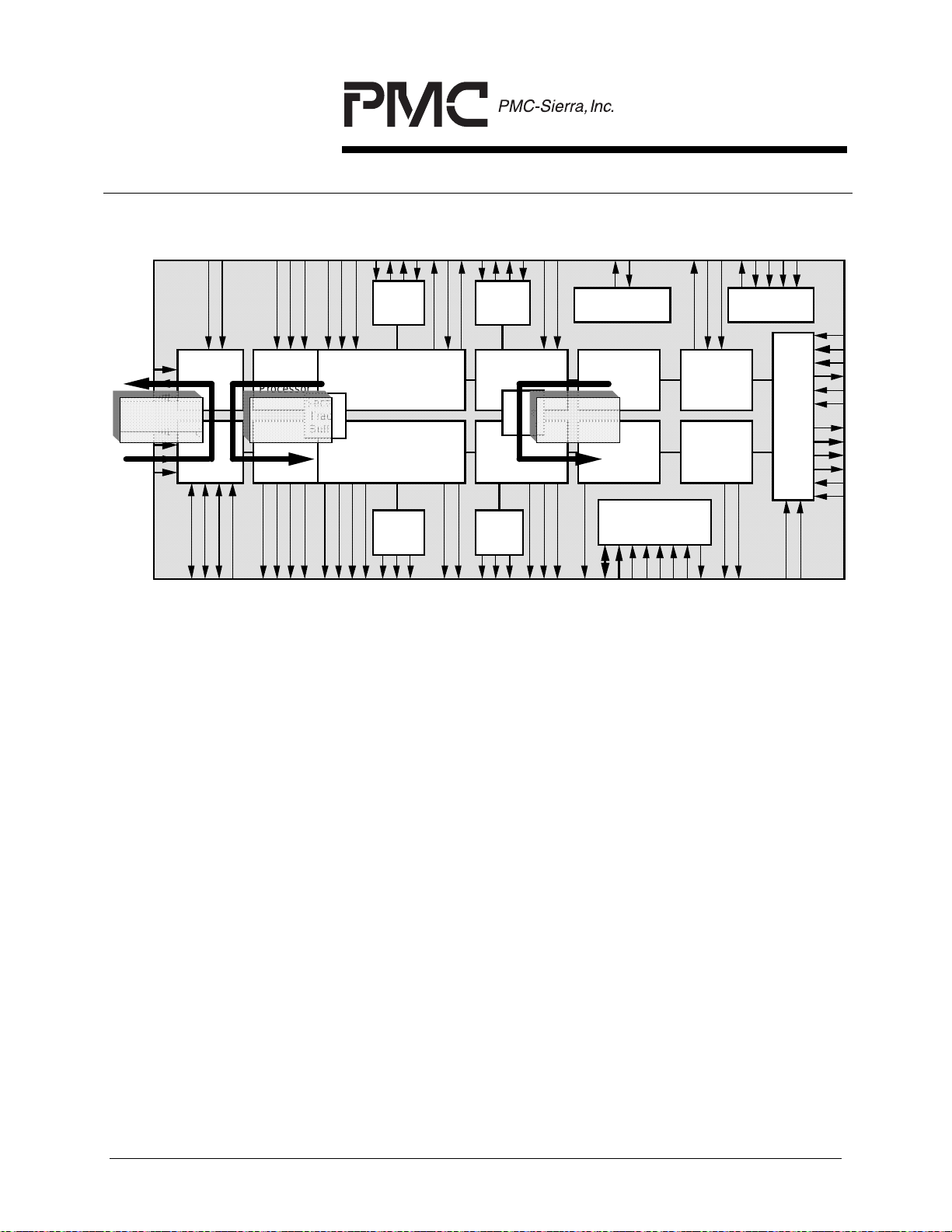

The clock recovery function of the S/UNI-PLUS may by bypassed. This is useful

in applications where clock recovery is not required such as when optical

receivers are utilized that have integral clock recovery. Similarly, the clock

synthesis function of the S/UNI-PLUS may be bypassed. This is useful in

applications where clock synthesis is not required, for example where a 155 MHz

transmit clock source is available. An example of an application where clock

recovery and clock synthesis are bypassed is shown in Figure 2.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

Figure 2 - Application With Clock Recovery & Clock Synthesis

Bypassed

E/O

O/E

With

Clock

Recovery

Ref.

Clock

155.52 MHz

TRCLK+/-

TXD+/-

RRCLK+/-

RXD+/-

ALOS+/-

TRANSMIT

OVERHEAD

INSERT

TRANSMIT

ALARM INSERT

SIGNALS

PM5347 S/UNI-PLUS

SONET/SDH

USER NETWORK INTERFACE

RECEIVE

OVERHEAD

EXTRACT

RECEIVE

ALARM DETECT

SIGNALS

TCA

TXPRTY[1:0]

TDAT[15:0]

TSOC

TWRENB

TFCLK

RCA

RXPRTY[1:0]

RDAT[15:0]

RSOC

RRDENB

RFCLK

MICRO BUS

FOR CONFIG, STATUS

AND CONTROL

TRANSMIT

ATM

PROCESS

RECEIVE

ATM

PROCESS

SWITCHING

NETWORK

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

PM5347 S/UNI-PLUS

K

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

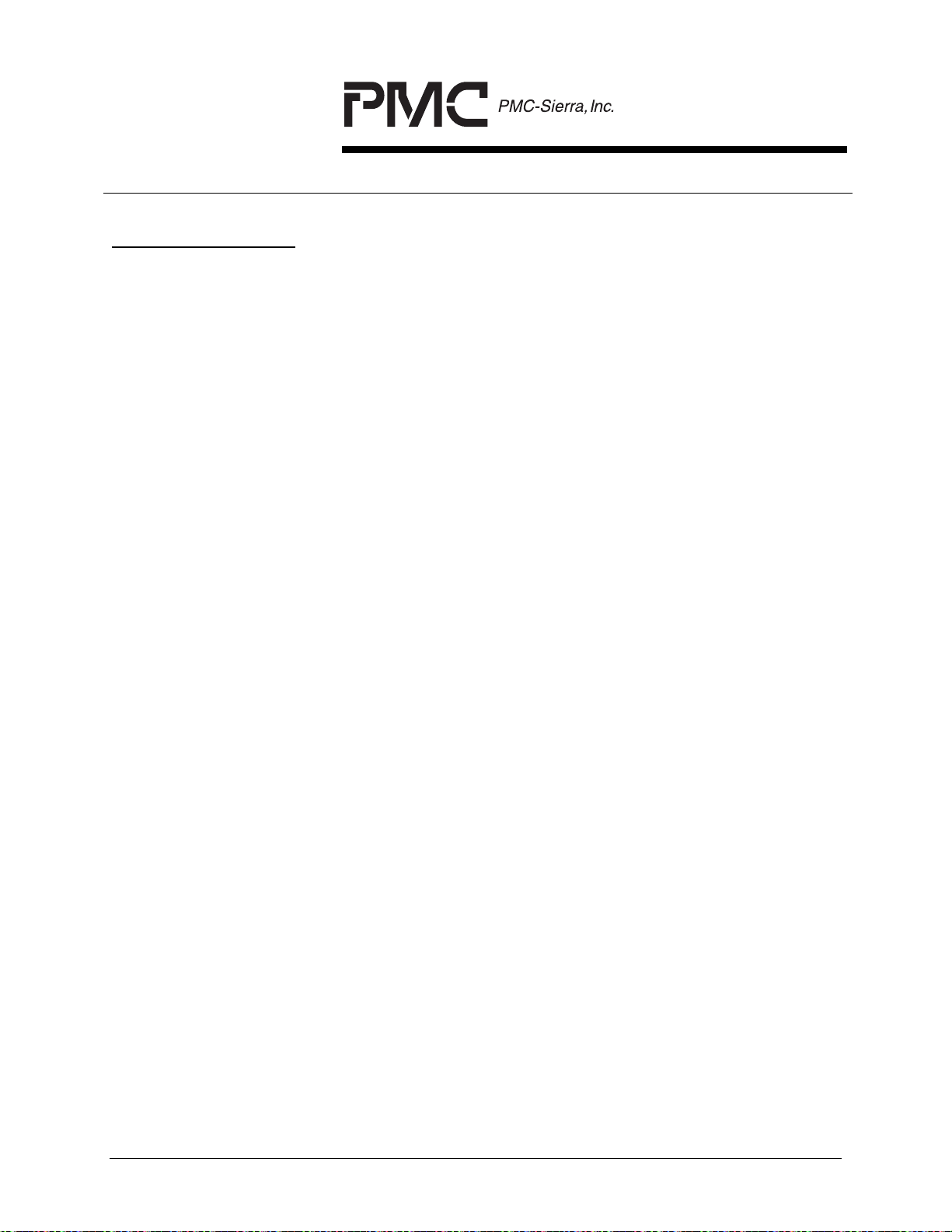

5

TRCLK+/-

TXD+/TXC+/-

RXDO+/-

RXD+/-

ALOS+/-

RRCLK+/-

BLOCK DIAG RAM

Normal Operating Mode

TLAIS

TSDCLK,TOWCL

TLDCLK

TATP

TBYP

Clock

Synthesizer

PISO

Clock

Recovery

SIPO

Section O/H

Processor

Section O/H

Processor

TLRDI

TSD,TSOW,TSUC

Tx

Section

Trace

Buffer

Rx

TLD,TLOW

TTOH

Transport

Insert

Line O/H

Processor

Rx

Line O/H

Processor

Transport

Extract

TTOHCLK

TTOHFP

O/H

Tx

O/H

TOHFP

TTOHEN

TFP

GTOCLK

TPOHCLK

TPOHFP

Path

O/H

Insert

Tx Path O/H

Processor

Path

Trace

Buffer

Rx Path O/H

Processor

Path

O/H

Extract

TPOHEN

TPAIS

TPRDI

POP[3:0]

Parallel

Input/Output Port

Tx ATM Cell

Processor

Rx ATM Cell

Processor

Microprocessor I/F

PIP[3:0]

TCP

XOFF

TGFC

Tx ATM

4 Cell

FIFO

Rx ATM

4 Cell

FIFO

TDO

TMS

TCK

TDI

JTAG Test

Access Port

Drop

Side

I/F

TRSTB

TSOC

TDAT[15:0]

TXPRTY[1:0]

TCA

TWRENB

TFCLK

RSOC

RDAT[15:0]

RXPRTY[1:0]

RCA

RRDENB

RFCLK

RBYP

LOF

LOS

RSD,RSOW,RSUC

RSDCLK,ROWCLK

LAIS

LRDI

RLDCLK

RTOH

RTOHFP

RTOHCLK

RLD,RLOW

ROHFP

GROCLK

RPOH TPOH

RPOHFP

LOP

PRDI

RPOHCLK

PAIS

LFO

LF+/-

RATP

LCD

A[7:0]

D[7:0]

ALE

CSB

RDB

WRB

INTB

RSTB

RCP

RGFC

TSEN

BUS8

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

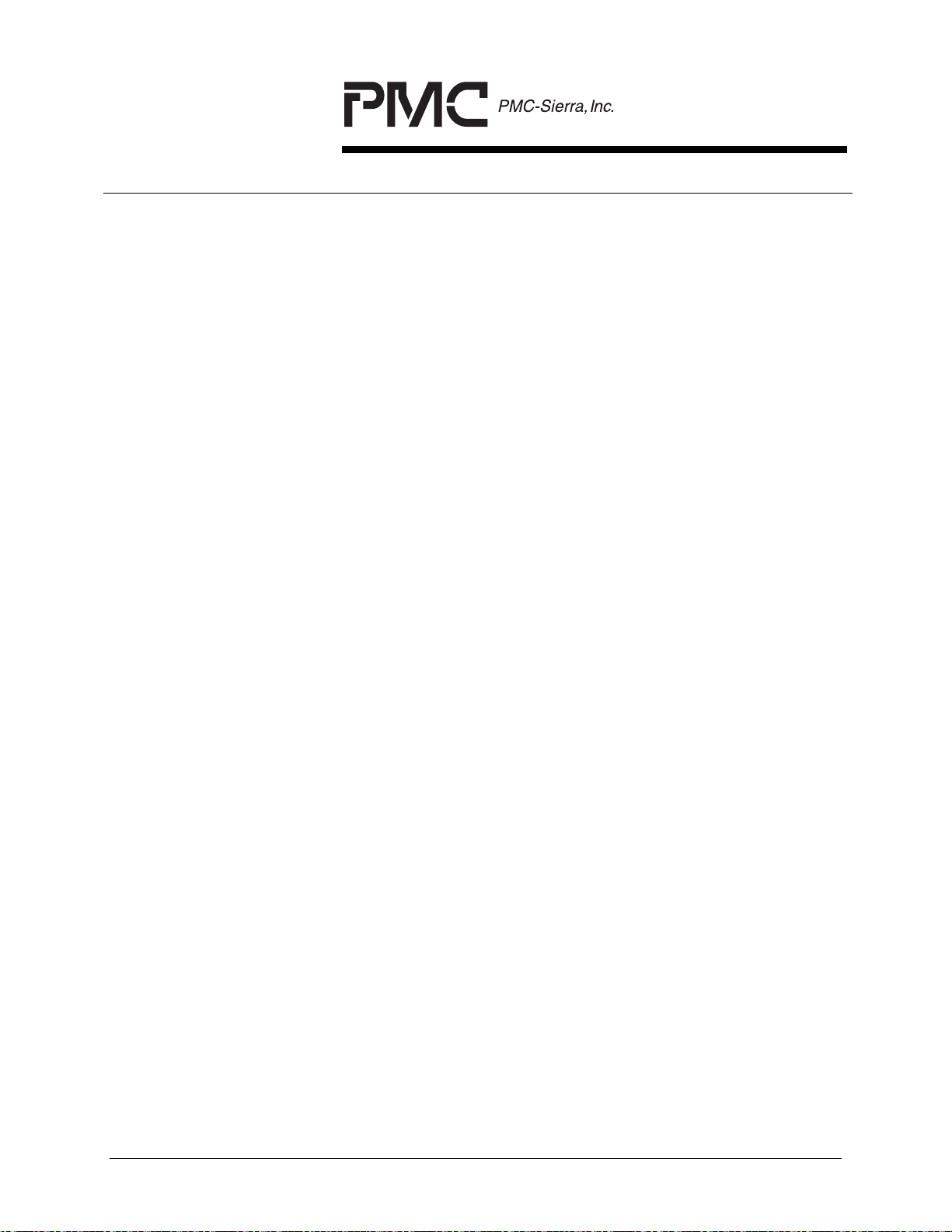

Loopback Modes

Synthesizer

SERIAL

LINE

LOOPBACK

Clock

PISO

Clock

Recovery

SIPO

Tx

Section O/H

Processor

DIAGNOSTIC

LOOPBACK

Section O/H

Processor

SERIAL

Rx

Section

Trace

Buffer

Transport

O/H

Insert

Tx

Line O/H

Processor

Rx

Line O/H

Processor

Transport

O/H

Extract

Path

O/H

Insert

Tx Path O/H

Processor

Path

Trace

Buffer

Rx Path O/H

Processor

Path

O/H

Extract

Parallel

Input/Output Port

Tx ATM Cell

Processor

PARALLEL

DIAGNOSTIC

LOOPBACK

Rx ATM Cell

Processor

Microprocessor I/F

Tx ATM

4 Cell

FIFO

Rx ATM

4 Cell

FIFO

JTAG Test

Access Port

Drop

Side

I/F

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

6

DESCRIPTION

The PM5347 S/UNI-PLUS SATURN User Network Interface is a monolithic

integrated circuit that implements the SONET/SDH processing and ATM mapping

functions of a 155 or 51 Mbit/s ATM User Network Interface.

The S/UNI-PLUS receives SONET/SDH streams using a bit serial interface,

recovers the clock and data and processes section, line, and path overhead. It

performs framing (A1, A2), descrambling, detects alarm conditions, and monitors

section, line, and path bit interleaved parity (B1, B2, B3), accumulating error

counts at each level for performance monitoring purposes. Line and path far end

block erro r indications (M0 or M1, G1) are also accumulated. The S/UNI-PLUS

interprets the received payload pointers (H1, H2) and extracts the synchronous

payload envelope which carries the received ATM cell payload. In addition to its

basic processing of the received SONET/SDH overhead, the S/UNI-PLUS

provides convenient access to all overhead bytes, which are extracted and

serialized on lower rate interfaces, allowing additional external processing of

overhead, if desired.

The S/UNI-PLUS frames to the ATM payload using cell delineation. HCS error

correction is provided. Idle/unassigned cells may be dropped according to a

programmable filter. Cells are also dropped upon detection of an uncorrectable

header check sequence error. The ATM cell payloads are descrambled. The

ATM cells that are passed are written to a four cell FIFO buffer. The received

cells are read from the FIFO using a generic 16- or 8-bit wide datapath interface.

Counts of received ATM cell headers that are errored and uncorrectable and also

those that are errored and correctable are accumulated independently for

performance monitoring purposes.

The S/UNI-PLUS transmits SONET/SDH streams using a bit serial interface and

formats section, line, and path overhead appropriately. It synthesizes the

transmit clock from a lower frequency reference and performs framing pattern

insertion (A1, A2), scrambling, alarm signal insertion, and creates section, line,

and path bit interleaved parity (B1, B2, B3) as required to allow performance

monitoring at the far end. Line and path far end block error indications (M0 or

M1, G1) are also inserted. The S/UNI-PLUS generates the payload pointer (H1,

H2) and inserts the synchronous payload envelope which carries the ATM cell

payload. In addition to its basic formatting of the transmitted SONET/SDH

overhead, the S/UNI-PLUS provides convenient access to all overhead bytes,

which are optionally inserted from lower rate serial interfaces, allowing external

sourcing of overhead, if desired. The S/UNI-PLUS also supports the insertion of

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

a large variety of errors into the transmit stream, such as framing pattern errors,

bit interleaved parity errors, and illegal pointers, which are useful for system

diagnostics and tester applications.

ATM cells are written to an internal four cell FIFO using a generic 16- or 8-bit

wide datapath interface. Idle/unassigned cells are automatically inserted when

the internal FIFO contains less than one cell. The S/UNI-PLUS provides

generation of the header check sequence and scrambles the payload of the ATM

cells. Each of these transmit ATM cell processing functions can be enabled or

bypassed.

No line rate clocks are required directly by the S/UNI-PLUS as it synthesizes the

transmit clock and recovers the receive clock using a 19.44 MHz or 6.48 MHz

reference clock. Optionally, receive clock recovery or transmit clock synthesis

may be bypassed.

The S/UNI-PLUS is configured, controlled and monitored via a generic 8-bit

microprocessor bus interface. The S/UNI-PLUS also provides a standard 5

signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

The S/UNI-PLUS is implemented in low power, +5 Volt, CMOS technology. It has

TTL and pseudo-ECL (PECL) compatible inputs and TTL/CMOS compatible

outputs and is packaged in a 208 pin PQFP package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

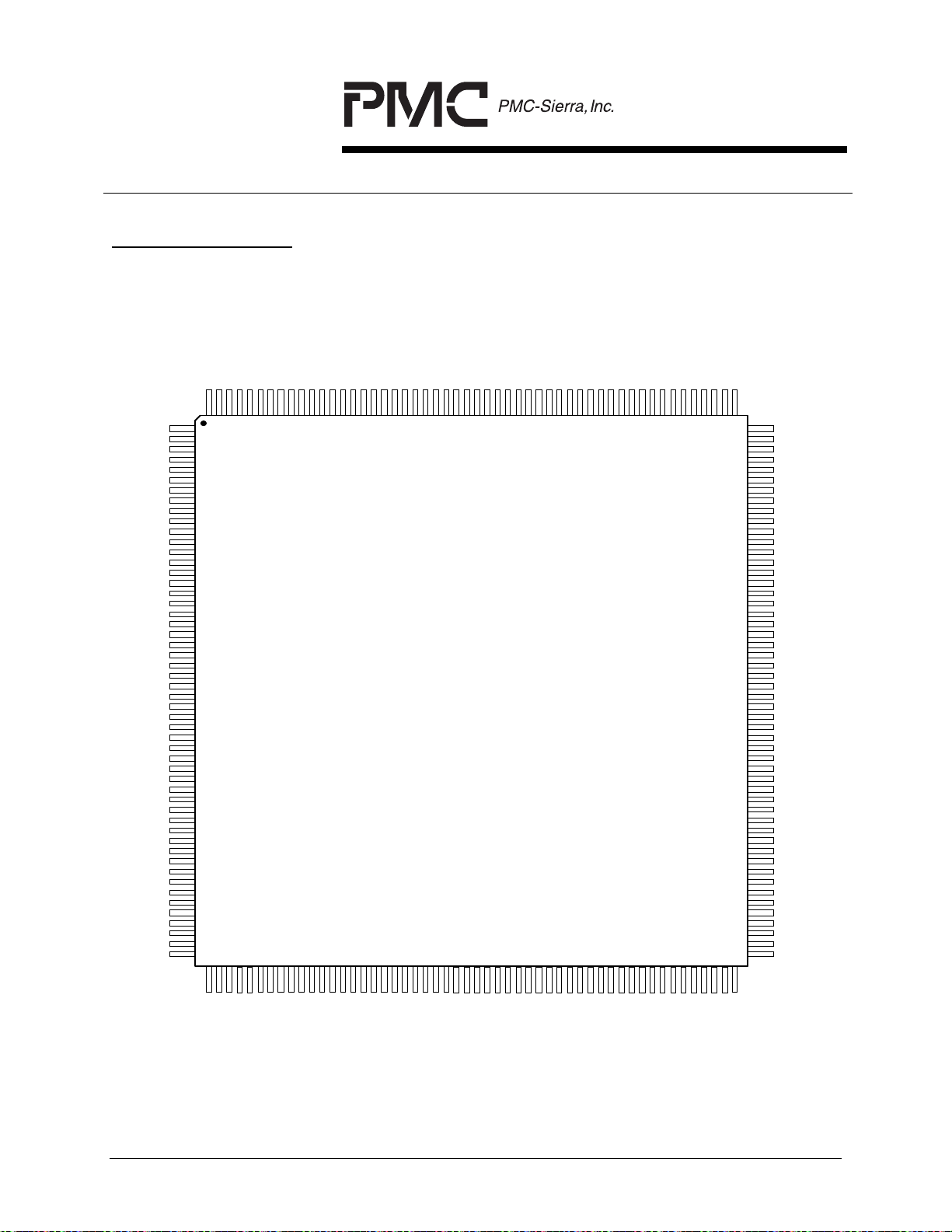

7

PIN DIAG RAM

The S/UNI-PLUS is packaged in a 208 pin plastic QFP package having a body

size of 28 mm by 28 mm and a pin pitch of 0.5 mm.

PIN 1

RDAT[9]

RDAT[10]

RDAT[11]

VDD_AC

VSS_AC

RDAT[12]

VDD_DC

VSS_DC

RDAT[13]

RDAT[14]

RDAT[15]

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

ALE

RSTB

CSB

WRB

RDB

INTB

TRSTB

D[0]

D[1]

VDD_DC

VSS_DC

D[2]

D[3]

VDD_AC

VSS_AC

D[4]

D[5]

VDD_DC

VSS_DC

D[6]

D[7]

TDO

TDI

TMS

TSEN

BUS8

TCK

TDAT[0]

TDAT[1]

TDAT[2]

TDAT[3]

TDAT[4]

TDAT[5]

PIN 52

VSS_DC

RDAT[8]

PIN 208

Index

RDAT[7]

VDD_DC

RDAT[6]

RDAT[5]

RDAT[4]

VSS_AC

RDAT[3]

VDD_AC

VSS_DC

RDAT[2]

VDD_DC

RDAT[0]

RDAT[1]

RXPRTY[1]

RRDENB

RXPRTY[0]

RFCLK

RSOC

VSS_AC

RCA

GROCLK

LOS

LOF

LOP

VDD_AC

LCD

PM5347

S/UNI-PLUS

PAIS

PRDI

VSS_DC

LAIS

VDD_DC

LRDI

RCP

RGFC

ROHFP

RPOH

RPOHFP

RTOHFP

RTOH

RPOHCLK

RTOHCLK

VDD_AC

VSS_AC

RSOW

RSUC

RLD

VSS_DC

VDD_DC

RLDCLK

RSD

PIN 157

PIN 156

RSDCLK

ROWCLK

RLOW

RBYP

RATP

LF+

LFLFO

RAVS1

RAVD1

RAVS2

RAVD2

RAVS4

RRCLKRRCLK+

RAVD4

RAVD3

RAVS3

ALOSALOS+

RXDRXD+

VSS_AC

VDD_AC

RXDORXDO+

VSS_DC

VDD_DC

TXVSS

TXDTXD+

TXCTXC+

TXVDD

TAVS3

TRCLKTRCLK+

TAVD3

TAVS2

TAVD2

TAVS1

TAVD1

TATP

TBYP

PIP[0]

PIP[1]

PIP[2]

PIP[3]

POP[0]

POP[1]

POP[2]

POP[3]

PIN 105

TDAT[6]

TDAT[7]

PIN 53

TDAT[8]

TDAT[9]

TDAT[12]

TDAT[10]

TDAT[11]

VSS_DC

TDAT[13]

VDD_DC

TDAT[14]

TDAT[15]

TXPRTY[0]

TSOC

TFCLK

TWRENB

TXPRTY[1]

TCA

XOFF

GTOCLK

TPAIS

TPRDI

TLAIS

TLRDI

TCP

TGFC

TFP

VSS_DC

VDD_DC

TOHFP

VSS_AC

VDD_AC

TPOH

TPOHFP

TPOHEN

TPOHCLK

TTOH

TTOHFP

TSOW

TTOHEN

TTOHCLK

TSUC

TLOW

TOWCLK

VSS_DC

VDD_DC

VDD_AC

TLD

VSS_AC

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

TSD

TSDCLK

TLDCLK

PIN 104

13

PM5347 S/UNI-PLUS

DATA SHEET

PMC-941033 ISSUE 6 SATURN USER NETWORK INTERFACE PLUS

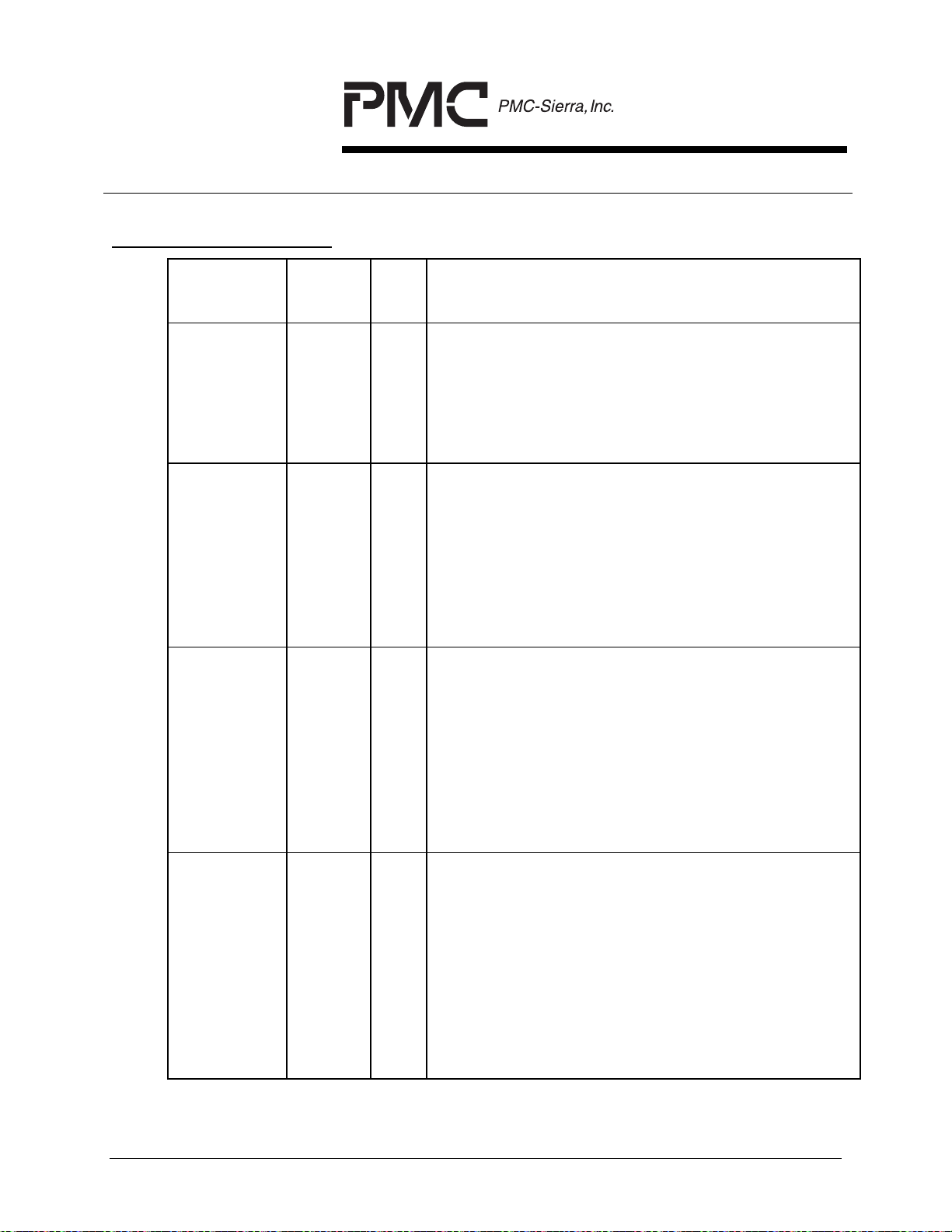

8

PIN DESCRIPTION

Pin Name Type Pin

Function

No.

RBYP Input 153 The receive bypass (RBYP) input disables clock

recovery. If RBYP is high, RXD+/- is sampled on

the rising edge of RRCLK+/-. If RBYP is low, the

receive clock is recovered from the RXD+/- bit

stream. RBYP requires an external pull-down

resistor.

RXD+

RXD-

PECL

Input

135

136

The receive differential data inputs (RXD+, RXD-)

contain the NRZ bit serial receive stream. RXD+/-

is sampled on the rising edge of RRCLK+/- when

clock recovery is bypassed (the falling edge may

be used by reversing RRCLK+/-), otherwise the

receive clock is recovered from the RXD+/- bit

stream. Please refer to the Operation section for

a discussion of PECL interfacing issues.

RXDO+

RXDO-

Output 131

132

The receive differential data outputs (RXDO+,

RXDO-) are sliced versions of the RXD+ and

RXD- inputs. These outputs are provided to allow

decision feedback equalization (DFE) to correct

baseline wander. It is intended that these outputs

be low pass filtered and attenuated to create an

appropriate correction signal that is summed with

incoming data to recover the low frequency

components.

RRCLK+

RRCLK-

PECL

Input

142

143

The receive differential reference clock inputs

(RRCLK+, RRCLK-) must be a jitter-free 19.44

MHz or 6.48 MHz reference clock when clock

recovery is enabled. When clock recovery is

bypassed, RRCLK+/- is nominally a 155.52 MHz

or 51.84 MHz 50% duty cycle clock and provides

timing for the S/UNI-PLUS receive functions. In

this case, RXD+/- is sampled on the rising edge of

RRCLK+/-. Please refer to the Operation section

for a discussion of PECL interfacing issues.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

Loading...

Loading...