PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

PM5345

S/UNI-155

SATURN USER NETWORK INTERFACE

TELECOM STANDARD PRODUCT

DATA SHEET

ISSUE 4: JUNE 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

PUBLIC REVISION HISTORY

Issue No. Issue Date Details of Change

4 June 1998 Data Sheet Reformatted — No

Change in Technical Content.

Generated R4 data sheet from

PMC-920404, R11.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

CONTENTS

1 FEATURES...............................................................................................1

1.1 THE RECEIVER SECTION: ..........................................................1

1.2 THE TRANSMITTER SECTION:....................................................1

2 APPLICATIONS........................................................................................1

3 REFERENCES.........................................................................................1

4 APPLICATION INFORMATION.................................................................1

5 INTERFACE EXAMPLES .........................................................................1

6 BLOCK DIAGRAM....................................................................................1

7 DESCRIPTION.........................................................................................1

8 PIN DIAGRAM..........................................................................................1

9 PIN DESCRIPTION..................................................................................1

10 FUNCTIONAL DESCRIPTION.................................................................1

10.1 SERIAL TO PARALLEL CONVERTER...........................................1

10.2 RECEIVE SECTION OVERHEAD PROCESSOR..........................1

10.2.1FRAMER.............................................................................1

10.2.2DESCRAMBLE ...................................................................1

10.2.3ERROR MONITOR..............................................................1

10.2.4LOSS OF SIGNAL ..............................................................1

10.2.5LOSS OF FRAME...............................................................1

10.3 RECEIVE LINE OVERHEAD PROCESSOR .................................1

10.3.1FERF DETECT ...................................................................1

10.3.2LINE AIS DETECT..............................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

10.3.3ERROR MONITOR..............................................................1

10.4 TRANSPORT OVERHEAD EXTRACT PORT................................1

10.5 RECEIVE PATH OVERHEAD PROCESSOR.................................1

10.5.1POINTER INTERPRETER..................................................1

10.5.2SPE TIMING........................................................................1

10.5.3ERROR MONITOR..............................................................1

10.5.4PATH FERF DETECT..........................................................1

10.6 PATH OVERHEAD EXTRACT........................................................1

10.7 RECEIVE ATM CELL PROCESSOR .............................................1

10.7.1CELL DELINEATION...........................................................1

10.7.2DESCRAMBLER.................................................................1

10.7.3CELL FILTER AND HCS VERIFICATION............................1

10.7.4PERFORMANCE MONITOR...............................................1

10.7.5RECEIVE FIFO ...................................................................1

10.8 PARALLEL TO SERIAL CONVERTER...........................................1

10.9 TRANSMIT SECTION OVERHEAD PROCESSOR.......................1

10.9.1LINE AIS INSERT ...............................................................1

10.9.2BIP-8 INSERT.....................................................................1

10.9.3FRAMING AND IDENTITY INSERT....................................1

10.9.4SCRAMBLER......................................................................1

10.10 TRANSMIT LINE OVERHEAD PROCESSOR...............................1

10.10.1 BIP-24 CALCULATE.........................................................1

10.10.2 LINE FERF INSERT..........................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

10.10.3 LINE FEBE INSERT .........................................................1

10.11 TRANSPORT OVERHEAD INSERT PORT...................................1

10.12 TRANSMIT PATH OVERHEAD PROCESSOR..............................1

10.12.1 POINTER GENERATOR...................................................1

10.12.2 BIP-8 CALCULATE...........................................................1

10.12.3 FEBE CALCULATE...........................................................1

10.12.4 ATH FERF INSERT...........................................................1

10.12.5 SPE MULTIPLEXER.........................................................1

10.13 PATH OVERHEAD INSERT...........................................................1

10.14 TRANSMIT ATM CELL PROCESSOR...........................................1

10.14.1 IDLE/UNASSIGNED CELL GENERATOR ........................1

10.14.2 SCRAMBLER....................................................................1

10.14.3 HCS GENERATOR ...........................................................1

10.14.4 TRANSMIT FIFO...............................................................1

10.15 LINE SIDE INTERFACE.................................................................1

10.15.1 RECEIVE INTERFACE.....................................................1

10.15.2 TRANSMIT INTERFACE...................................................1

10.16 DROP SIDE INTERFACE..............................................................1

10.16.1 RECEIVE INTERFACE.....................................................1

10.16.2 TRANSMIT INTERFACE...................................................1

10.17 MICROPROCESSOR INTERFACE ...............................................1

10.18 JTAG TEST ACCESS PORT..........................................................1

10.19 REGISTER MEMORY MAP...........................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

11 NORMAL MODE REGISTER DESCRIPTION..........................................1

12 TEST FEATURES DESCRIPTION...........................................................1

12.1 TEST MODE REGISTER MEMORY MAP.....................................1

12.2 TEST MODE 0 DETAILS...............................................................1

12.3 JTA G TEST POR T..........................................................................1

13 OPERATION.............................................................................................1

14 FUNCTIONAL TIMING .............................................................................1

14.1 LINE SIDE RECEIVE INTERFACE................................................1

14.2 OVERHEAD ACCESS ...................................................................1

14.3 LINE SIDE TRANSMIT INTERFACE..............................................1

14.4 DROP SIDE RECEIVE INTERFACE..............................................1

14.5 DROP SIDE TRANSMIT INTERFACE ...........................................1

15 ABSOLUTE MAXIMUM RATINGS............................................................1

16 D.C. CHARACTERISTICS ........................................................................1

17 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS..........1

18 S/UNI TIMING CHARA CTERISTICS........................................................1

19 ORDERING AND THERMAL INFORMATION ..........................................1

20 MECHANICAL INFORMATION.................................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

LIST OF REGISTERS

REGISTER 0X00: S/UNI MASTER RESET AND IDENTITY...............................1

REGISTER 0X01: S/UNI MASTER CONFIGURATION.......................................1

REGISTER 0X02: S/UNI MASTER INTERRUPT STATUS..................................1

REGISTER 0X04: S/UNI MASTER CLOCK MONITOR ......................................1

REGISTER 0X05: S/UNI MASTER CONTROL...................................................1

REGISTER 0X10: RSOP CONTROL/INTERRUPT ENABLE..............................1

REGISTER 0X11: RSOP STATUS/INTERRUPT STATUS ...................................1

REGISTER 0X12: RSOP SECTION BIP-8 LSB..................................................1

REGISTER 0X13: RSOP SECTION BIP-8 MSB.................................................1

REGISTER 0X14: TSOP CONTROL...................................................................1

REGISTER 0X15: TSOP DIAGNOSTIC..............................................................1

REGISTER 0X18: RLOP CONTROL/STATUS.....................................................1

REGISTER 0X19: RLOP INTERRUPT ENABLE/INTERRUPT STATUS.............1

REGISTER 0X1A: RLOP LINE BIP-24 LSB........................................................1

REGISTER 0X1B: RLOP LINE BIP-24................................................................1

REGISTER 0X1C: RLOP LINE BIP-24 MSB.......................................................1

REGISTER 0X1D: RLOP LINE FEBE LSB .........................................................1

REGISTER 0X1E: RLOP LINE FEBE .................................................................1

REGISTER 0X1F: RLOP LINE FEBE MSB.........................................................1

REGISTER 0X20: TLOP CONTROL...................................................................1

REGISTER 0X21: TLOP DIAGNOSTIC ..............................................................1

REGISTER 0X30: RPOP STATUS/CONTROL....................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

REGISTER 0X31: RPOP INTERRUPT STATUS .................................................1

REGISTER 0X33: RPOP INTERRUPT ENABLE................................................1

REGISTER 0X37: RPOP PATH SIGNAL LABEL.................................................1

REGISTER 0X38: RPOP PATH BIP-8 LSB / LOAD METERS.............................1

REGISTER 0X39: RPOP PATH BIP-8 MSB ........................................................1

REGISTER 0X3A: RPOP PATH FEBE LSB.........................................................1

REGISTER 0X3B: RPOP PATH FEBE MSB........................................................1

REGISTER 0X40: TPOP CONTROL/DIAGNOSTIC............................................1

REGISTER 0X41: TPOP POINTER CONTROL..................................................1

REGISTER 0X42: TPOP SOURCE CONTROL...................................................1

REGISTER 0X45: TPOP ARBITRARY POINTER LSB .......................................1

REGISTER 0X46: TPOP ARBITRARY POINTER MSB ......................................1

REGISTER 0X48: TPOP PATH SIGNAL LABEL .................................................1

REGISTER 0X49: TPOP PATH STATUS..............................................................1

REGISTER 0X50: RACP CONTROL/STATUS ....................................................1

REGISTER 0X51: RACP INTERRUPT ENABLE/STATUS ..................................1

REGISTER 0X52: RACP MATCH HEADER PATTERN .......................................1

REGISTER 0X53: RACP MATCH HEADER MASK.............................................1

REGISTER 0X54: RACP CORRECTABLE HCS ERROR COUNT......................1

REGISTER 0X55: RACP UNCORRECTABLE HCS ERROR COUNT ................1

REGISTER 0X60: TACP CONTROL/STATUS......................................................1

REGISTER 0X61: TACP IDLE/UNASSIGNED CELL HEADER PATTERN..........1

REGISTER 0X62: TACP IDLE/UNASSIGNED CELL PAYLOAD

OCTET PATTERN.....................................................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

REGISTER 0X80: MASTER TEST......................................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

LIST OF FIGURES

FIGURE 1 - EXAMPLE 1. OPTICAL ATM ADAPTER INTERFACE...................1

FIGURE 2 - EXAMPLE 2. UTP-5 ATM ADAPTER INTERFACE........................1

FIGURE 3 - EXAMPLE 3. OC-12 ATM SWITCH PORT CARD INTERFACE....1

FIGURE 4 - RECOMMENDED INTERFACE WITH CY7B951 ...........................1

FIGURE 5 - RECOMMENDED INTERFACE WITH AD802................................1

FIGURE 6 - CELL DELINEATION STATE DIAGRAM.........................................1

FIGURE 7 - HCS VERIFICATION STATE DIAGRAM .........................................1

FIGURE 8 - DEFAULT TRANSPORT OVERHEAD VALUES..............................1

FIGURE 9 - DEFAULT PATH OVERHEAD VALUES...........................................1

FIGURE 10- OVERHEAD BYTE USAGE............................................................1

FIGURE 11- 16-BIT WORD WIDTH DATA STRUCTURE....................................1

FIGURE 12- 8-BIT WORD WIDTH DATA STRUCTURE......................................1

FIGURE 13- LOOPBACK OPERATION..............................................................1

FIGURE 14- BOUNDARY SCAN ARCHITECTURE............................................1

FIGURE 15- TAP CONTROLLER FINITE STATE MACHINE ..............................1

FIGURE 16- IN FRAME DECLARATION (BIT SERIAL

INTERFACE, RSER=1).......................................................................................1

FIGURE 17- IN FRAME DECLARATION (BYTE SERIAL

INTERFACE, RSER=0).......................................................................................1

FIGURE 18- OUT OF FRAME DECLARATION ..................................................1

FIGURE 19- LOSS OF SIGNAL DECLARATION/REMOVAL..............................1

FIGURE 20- LOSS OF FRAME DECLARATION/REMOVAL ..............................1

FIGURE 21- LINE AIS AND LINE FERF DECLARATION/REMOVAL.................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

FIGURE 22- LOSS OF POINTER DECLARATION/REMOVAL...........................1

FIGURE 23- PATH AIS DECLARATION/REMOVAL............................................1

FIGURE 24- PATH YELLOW ALARM DECLARATION/REMOVAL......................1

FIGURE 25- TRANSPORT OVERHEAD EXTRACTION.....................................1

FIGURE 26- PATH OVERHEAD EXTRACTION..................................................1

FIGURE 27- TRANSPORT OVERHEAD INSERTION........................................1

FIGURE 28- PATH OVERHEAD INSERTION......................................................1

FIGURE 29- FRAME ALIGNMENT.....................................................................1

FIGURE 30- RECEIVE FIFO ..............................................................................1

FIGURE 31- TRANSMIT FIFO............................................................................1

FIGURE 32-........................................................................................................1

FIGURE 33- MICROPROCESSOR INTERFACE READ TIMING........................1

FIGURE 34- MICROPROCESSOR INTERFACE WRITE TIMING ......................1

FIGURE 35- LINE SIDE RECEIVE INTERFACE TIMING...................................1

FIGURE 36- RECEIVE ALARM OUTPUT TIMING .............................................1

FIGURE 37- RECEIVE OVERHEAD ACCESS TIMING......................................1

FIGURE 38- LINE SIDE TRANSMIT INTERFACE TIMING.................................1

FIGURE 39- TRANSMIT ALARM INPUT TIMING...............................................1

FIGURE 40- TRANSMIT OVERHEAD ACCESS TIMING....................................1

FIGURE 41- DROP SIDE RECEIVE INTERFACE TIMING (TSEN = 0)..............1

FIGURE 42- DROP SIDE RECEIVE INTERFACE TIMING (TSEN = 1)..............1

FIGURE 43- DROP SIDE TRANSMIT INTERFACE............................................1

FIGURE 44- JTAG PORT INTERFACE TIMING..................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

LIST OF TABLES

TABLE 1 - ........................................................................................................1

TABLE 2 - ........................................................................................................1

TABLE 3 - ........................................................................................................1

TABLE 4 - ........................................................................................................1

TABLE 5 - ........................................................................................................1

TABLE 6 - INSTRUCTION REGISTER............................................................1

TABLE 7 - IDENTIFICATION REGISTER........................................................1

TABLE 8 - BOUNDARY SCAN REGISTER.....................................................1

TABLE 9 - ........................................................................................................1

TABLE 10 - ........................................................................................................1

TABLE 11 - MICROPROCESSOR INTERFACE READ ACCESS

(FIGURE 33) .......................................................................................................1

TABLE 12 - MICROPROCESSOR INTERFACE WRITE ACCESS

(FIGURE 34) .......................................................................................................1

TABLE 13 - LINE SIDE RECEIVE INTERFACE (FIGURE 35)...........................1

TABLE 14 - RECEIVE ALARM OUTPUT (FIGURE 36).....................................1

TABLE 15 - RECEIVE OVERHEAD ACCESS (FIGURE 37).............................1

TABLE 16 - LINE SIDE TRANSMIT INTERFACE (FIGURE 38)........................1

TABLE 17 - TRANSMIT ALARM INPUT (FIGURE 39) ......................................1

TABLE 18 - TRANSMIT OVERHEAD ACCESS (FIGURE 40)...........................1

TABLE 19 - DROP SIDE RECEIVE INTERFACE (FIGURE 41)........................1

TABLE 20 - DROP SIDE RECEIVE INTERFACE (FIGURE 42)........................1

TABLE 21 - DROP SIDE TRANSMIT INTERFACE (FIGURE 43)......................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

TABLE 22 - JTAG PORT INTERFACE (FIGURE 44).........................................1

TABLE 23 - ........................................................................................................1

TABLE 24 - ........................................................................................................1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

1

FEATURES

Monolithic Saturn Network Interface that implements the ATM physical layer

•

for Broadband ISDN according to the ATM Forum User Network Interface

Specification and CCITT Recommendation I.432.

Operates at 155.52 MHz in conjunction with an external clock and data

•

recovery device. Provides on-chip parallel to serial and serial to parallel

circuits with pseudo ECL interfaces to process a duplex 155.52 Mbit/s STS3c/STM-1 data stream.

Supports a 19.44 Mbyte/s line interface option for devices requiring a byte-

•

serial STS-3c/STM-1 interface.

Provides 4 cell deep FIFO buffers in both transmit and receive paths with a

•

byte-wide or word-wide system side datapath interface.

Provides a generic 8-bit microprocessor bus interface for configuration,

•

control, and status monitoring.

Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

•

test purposes.

Low power, +5 Volt, CMOS technology.

•

160 pin high performance plastic quad flat pack (PQFP) package.

•

1.1 The receiver section:

Frames to the recovered 155.52 Mbit/s stream or to an 19.44 Mbyte/s stream

•

and descrambles the received STS-3c (STM-1) stream.

Interprets the received payload pointer (H1, H2), extracting the STS-3c

•

synchronous payload envelope (VC4) and path overhead.

Extracts ATM cells from the received STS-3c synchronous payload envelope

•

using ATM cell delineation and provides optional ATM cell payload

descrambling, header check sequence (HCS) error detection and error

correction, and idle/unassigned cell filtering.

Provides a generic 8 bit wide or 16 bit wide datapath interface to read

•

extracted cells from an internal four cell FIFO buffer.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Extracts all transport overhead bytes and serializes them at 5.184 Mbit/s for

•

optional external processing.

Extracts all path overhead bytes and serializes them at 576 kbit/s for optional

•

external processing.

Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line

•

alarm indication signal (AIS), line far end receive failure (FERF), loss of

pointer (LOP), path alarm indication signal (AIS), and path yellow alarm.

Counts received section BIP-8 (B1) errors, received line BIP-24 (B2) errors,

•

line far end block errors (FEBE), received path BIP-8 (B3) errors and path far

end block erro rs (FEBE) for performance monitoring purposes.

Counts received HCS errored cells that are discarded, and received HCS

•

errored cells that are corrected and passed on for performance monitoring

purposes.

1.2 The transmitter section:

Provides an internal four cell FIFO into which cells are written using a generic

•

8 bit wide or 16 bit wide datapath interface

Provides idle/unassigned cell insertion, HCS generation/insertion, and ATM

•

cell payload scrambling.

Inserts ATM cells into the transmitted STS-3c (STM-1) synchronous payload

•

envelope using H4 framing.

Generates the transmit payload pointer (H1, H2) and inserts the path

•

overhead.

Optionally inserts externally generated path overhead bytes received via a

•

576 kbit/s serial interface.

Scrambles the transmitted STS-3c (STM-1) stream and inserts framing bytes

•

(A1, A2) and the identity byte (C1).

Optionally inserts externally generated transport overhead bytes received via

•

a 5.184 Mbit/s serial interface.

Interfaces to a downstream physical media device at 155.52 Mbit/s using

•

differential outputs. Alternately, the S/UNI can interface to a parallel to serial

converter at 19.44 Mbyte/s

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Optionally inserts path alarm indication signal (AIS), path yellow alarm

•

indication (PYEL), line alarm indication signal (AIS) and line far end receive

failure (FERF) indication.

Inserts path BIP-8 codes (B3), path far end block error (FEBE) indications,

•

line BIP-24 codes (B2), line far end block error (FEBE) indications, section

BIP-8 codes (B1) to allow performance monitoring at the far end.

Allows forced insertion of all zero s data (after scrambling) or corruption of

•

framing byte or section, line, or path BIP-8 codes for diagnostic purposes.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

2

APPLICATIONS

SONET/SDH Based ATM Switching Systems

•

SONET/SDH Based ATM Terminals

•

B-ISDN User-Network Interfaces

•

B-ISDN Network Node Interfaces

•

B-ISDN Test Equipment

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

3

REFERENCES

•

ITU-T Recommendation I.432 - "B-ISDN User-Network Interface - Physical

Layer Specification", March 1993.

ANSI T1.624-1993 - "Broadband ISDN User-Network Interfaces - Rates and

•

Formats Specifications".

ATM Forum - ATM User-Network Interface Specification, V3.0, 1993.

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

4

APPLICATION INFORMATION

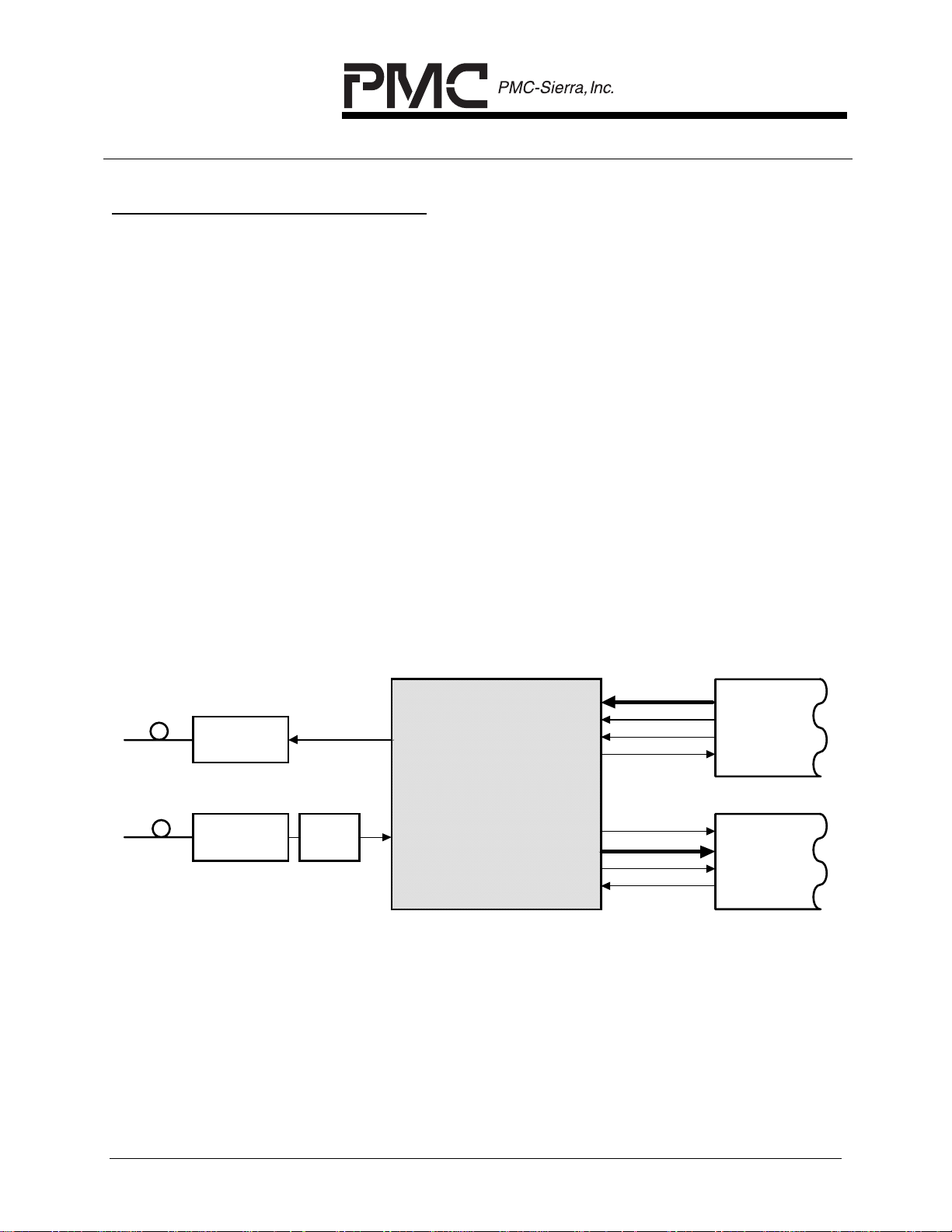

The S/UNI is typically used to implement the core of an ATM User Network

Interface by which an ATM terminal is linked to an ATM switching system or ATM

switching systems are linked together using SONET/SDH compatible transport.

The S/UNI may find application at either end of terminal to switch links or switch

to switch links, both in private network (LAN) and public network (WAN)

situations.

In this application the S/UNI typically connects on its line side with a twisted pair

line receiver or optical receiver, plus a clock and data recovery device and a

twisted pair line driver or laser for the transmitter. In this application, the S/UNI is

loop timed internally (the recovered 155.52 MHz clock is used in the transmit

direction). The drop side interfaces directly with ATM adaptation layer

processors. The initial configuration and ongoing control and monitoring of the

S/UNI are normally provided via a generic microprocessor interface. The S/UNI

supports a "hardware-only" operating mode where an external microprocessor is

not required. Typical ATM Adapter card applications are shown in Figure 1 and

Figure 2.

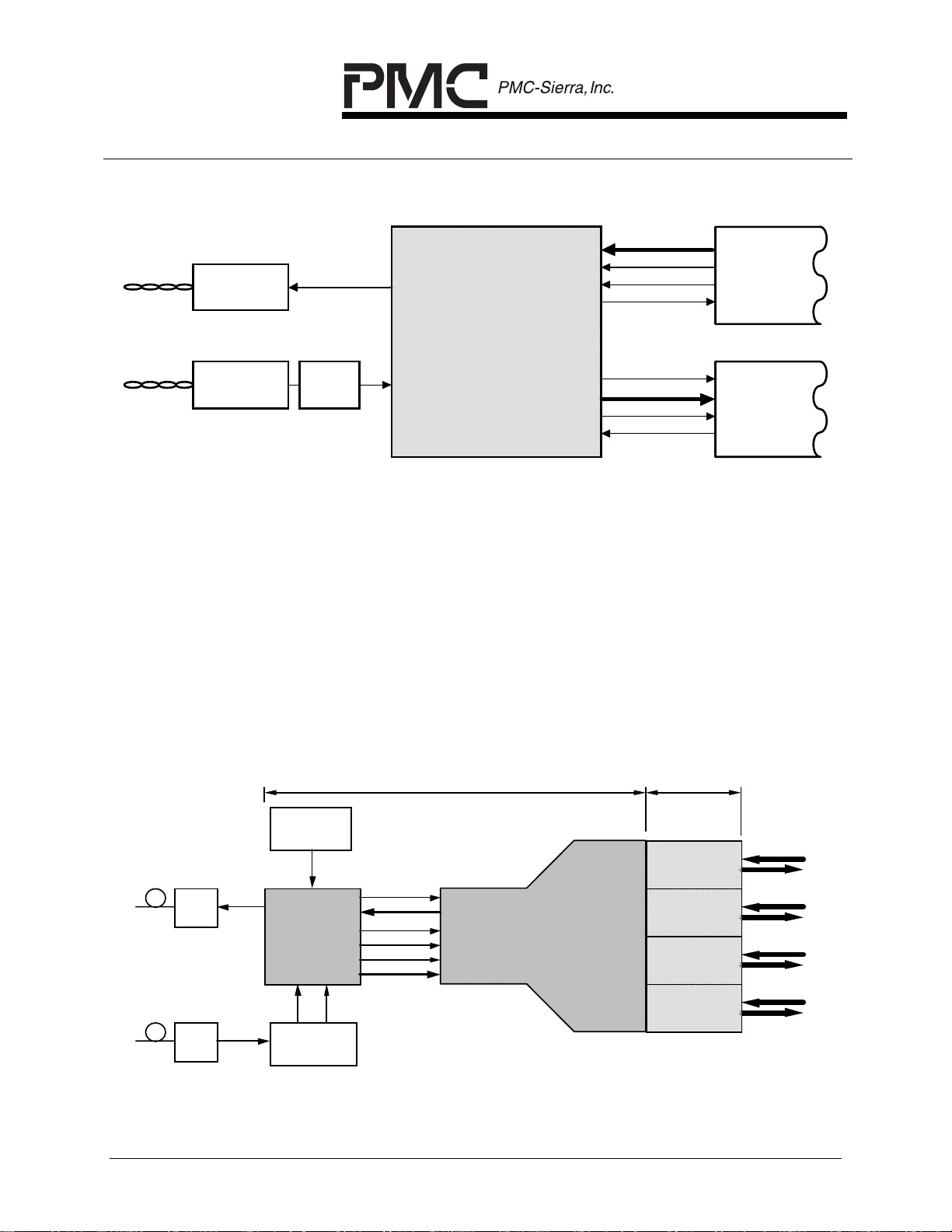

Figure 1 - Example 1. Optical ATM Adapter Interface

Optical

Transmitter

Optical

Receiver

Clock

Recovery

PM5345

S/UNI

SATURN

USER NETWORK

INTERFACE

TDAT[15:0]

TSOC

TWRB

TCA

RCA

RDAT[7:0]

RSOC

RRDB

Transmit

AAL

Processor

ATM Terminal

Receive

AAL

Processor

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Figure 2 - Example 2. UTP-5 ATM Adapter Interface

Line Driver

&

Transformer

TDAT[15:0]

TSOC

TWRB

TCA

PM5345

Transmit

AAL

Processor

S/UNI

ATM Terminal

Receive

AAL

Processor

Transformer

&

Line Receiver

Clock

Recovery

SATURN

USER NETWORK

INTERFACE

RCA

RDAT[7:0]

RSOC

RRDB

Figure 3 shows a configuration in which the PM5345 S/UNI is used with a

PM5312 SONET/SDH Transport Overhead Terminating Transceiver (STTX) and a

PM5318 622 Mbit/s Serial/Parallel Converter (SIPO) to implement an ATM

backbone interface.

In this application, four STS-3/STM-1 ATM streams are multiplexed into a single

STS-12/STM-4 stream for transport over fiber optic cables. The function of the

PM5312, PM5318, clock recovery and clock synthesis are also available in the

PM5712B 622 Mbit/s SONET/SDH Line Interface Module (SLIM).

Figure 3 - Example 3. OC-12 ATM Switch Port Card Interface

STS-3c (STM-1)

ATM Termination

PM5345

S/UNI-155

OPTICAL

FACILITY

E/O

O/E

Clock

Synthesis

Serial /

Parallel

Conversion

Clock

Recovery

STS-3(STM-1) To STS-12 (STM-4) MUX

OOF

TOUT[7:0]

TCLK

RICLK

RIFP

RIN[7:0]

PM5312

STTX

#1

#2

#3

#4

ATM

SWITCH

CORE

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

5

INTERFACE EXAMPLES

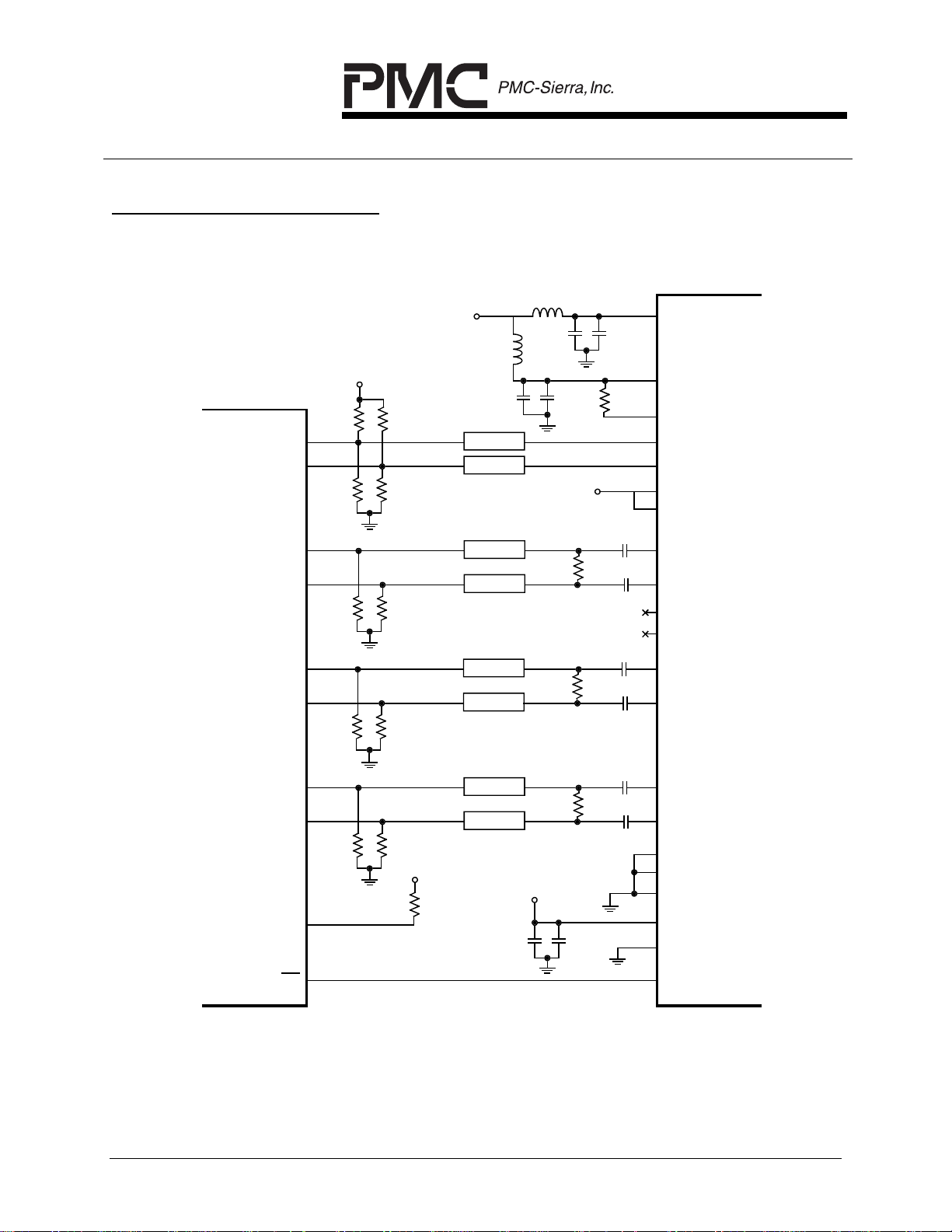

Figure 4 - Recommended Interface with CY7B951

FB

Ω

Ω

Ω

Ω

Ω

Ω

Ω

Ω

Vcc

FB

10µF

0.1µF

Vcc

0.1µF

0.01µF

100

0.01µF

0.01µF

100

0.01µF

0.01µF

100

0.01µF

0.1µF

630

Ω

Ω

Ω

RAVD (141)

TAVD1 (15)

Ω

VT2 (24)

TXD+ (22)

TXD- (23)

TSER (26)

RSER (25)

TXCI+ (14)

TXCI- (13)

TXCO+ (19)

TXCO- (1 8 )

RXD+ (143)

RXD- (142)

PM 5345

RXC+ (139)

RXC- (138)

RAVS (140)

TAVS1 (16)

TAVS2 (21)

TAVD2 (20)

VT1 (17)

(14) TSER+

(13) TSER-

(15) TCLK+

(16) TCLK-

(21) R S E R +

(22) R S E R -

CY7B 951

(23) RCLK+

(24) RCLK-

(5) M ODE

59

312

330

330

330

V

REF

Vcc

10µF

Ω

59

Ω

Z0 = 50

Z0 = 50

Ω

312

Ω

Z0 = 50

Z0 = 50

Ω

330

Ω

Z0 = 50

Z0 = 50

Ω

330

Ω

Z0 = 50

Z0 = 50

Ω

330

Ω

Vcc

4.7k

Ω

10µF

(20) L FI

GPIN (8 1)

In Figure 4, the interface between the S/UNI and the Cypress CY7B951 is

shown.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

For optimal performance, the following guidelines should be followed:

• All power pins should be well decoupled, with the capacitors placed as close

as possible to the S/UNI power pins.

• Termination resistors and capacitors should be placed as close as possible to

the end of the transmission line.

• Source pull-down resistors should be placed as close as possible to the start

of the transmission line.

• Traces marked "Zo=50Ω" should be controlled impedance traces. These

traces should be kept as short as possible. Other controlled impedances can

be used. Contact PMC-Sierra's applications department for information on

using the S/UNI in "non-50Ω" controlled impedance environments.

• All inductors are Fair-Rite Products Corp #274-3019-446.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

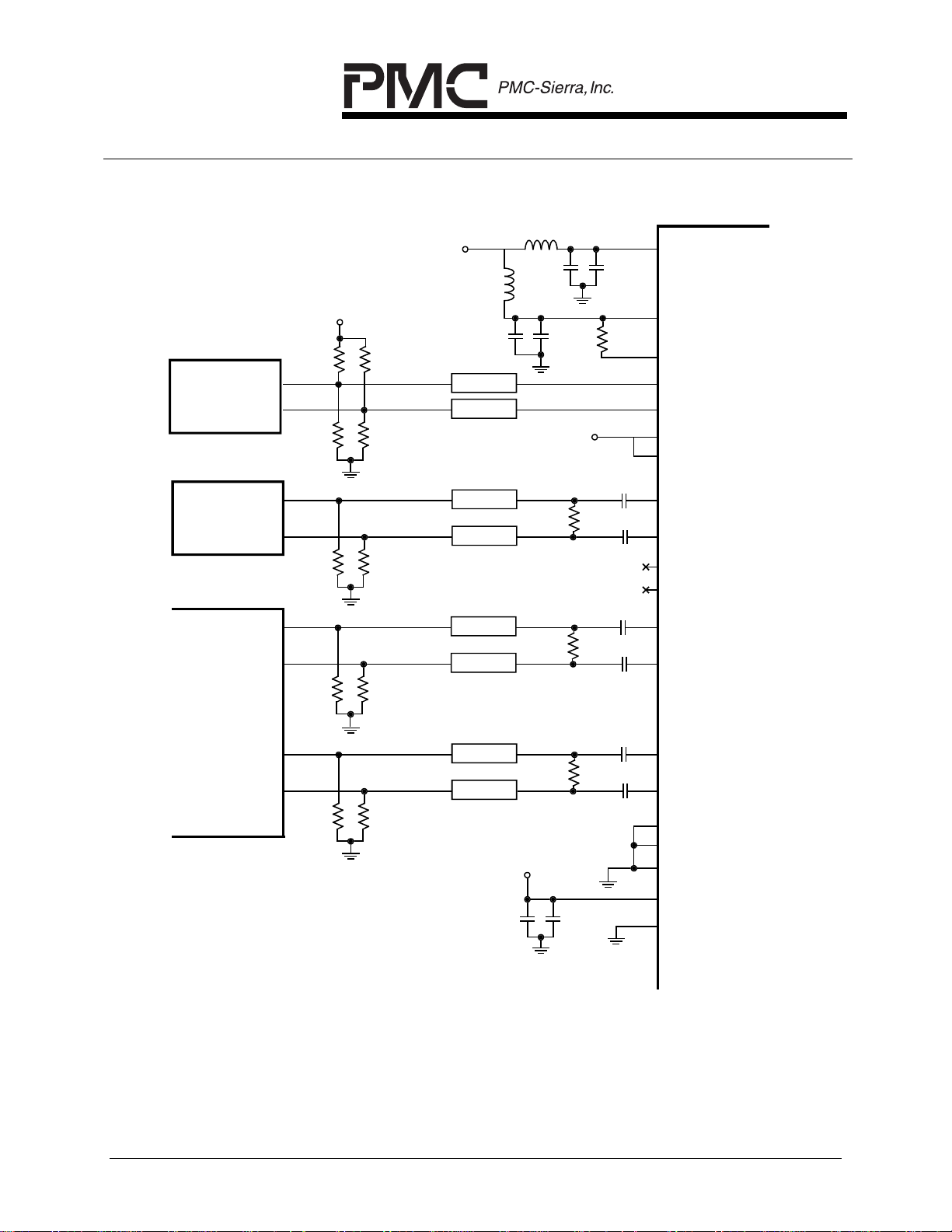

Figure 5 - Recommended Interface with AD802

Transm it

PMD

155.52 MHz

Oscillator

(2) D ATAOU T+

(1) D ATAOU T-

AD802

(5) C L KOUT+

(4) C L KOUT-

59

312

330

330

330

REF

V

10µF

0.1µF

RAVD (141)

FB

FB

Vcc

10µF

Ω

Ω

59

312

Ω

Z0 = 50

Z0 = 50

Ω

Ω

Ω

0.1µF

Vcc

630

TAVD1 (15)

Ω

VT2 (24)

TXD+ (22)

TXD- (23)

TSER (26)

RSER (25)

0.01µF

Z0 = 50

Z0 = 50

Ω

330

Ω

Ω

Ω

100

Ω

0.01µF

TXCI+ (14)

TX C I- (1 3 )

TXCO+ (19)

TX C O- (18 )

0.01µF

Z0 = 50

Z0 = 50

Ω

330

Ω

Ω

Ω

100

Ω

RXD+ (14 3)

RXD- (142)

0.01µF

PM 5345

0.01µF

Z0 = 50

Z0 = 50

Ω

330

Ω

Ω

Ω

Vcc

Ω

100

0.01µF

RXC+ (13 9)

RXC- (138)

RAVS (140)

TAVS1 (16)

TAVS2 (21)

TAVD2 (20)

10µF

0.1µF

VT1 (17)

In Figure 5, the interface between the S/UNI and the Analog Devices AD802 is

shown. In addition to the AD802, a 155.52 MHz oscillator provides the transmit

clock to the S/UNI. Oscillator vendors include CTS Corporation, C-MAC Quartz

Crystals Ltd., and Connor Winfield.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

For optimal performance, the following guidelines should be followed:

• All power pins should be well decoupled, with the capacitors placed as close

as possible to the S/UNI power pins.

• Termination resistors and capacitors should be placed as close as possible to

the end of the transmission line.

• Source pull-down resistors should be placed as close as possible to the start

of the transmission line.

• Traces marked "Zo=50Ω" should be controlled impedance traces. These

traces should be kept as short as possible. Other controlled impedances can

be used. Contact PMC-Sierra's applications department for information on

using the S/UNI in "non-50Ω" controlled impedance environments.

• All inductors are Fair-Rite Products Corp #274-3019-446.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

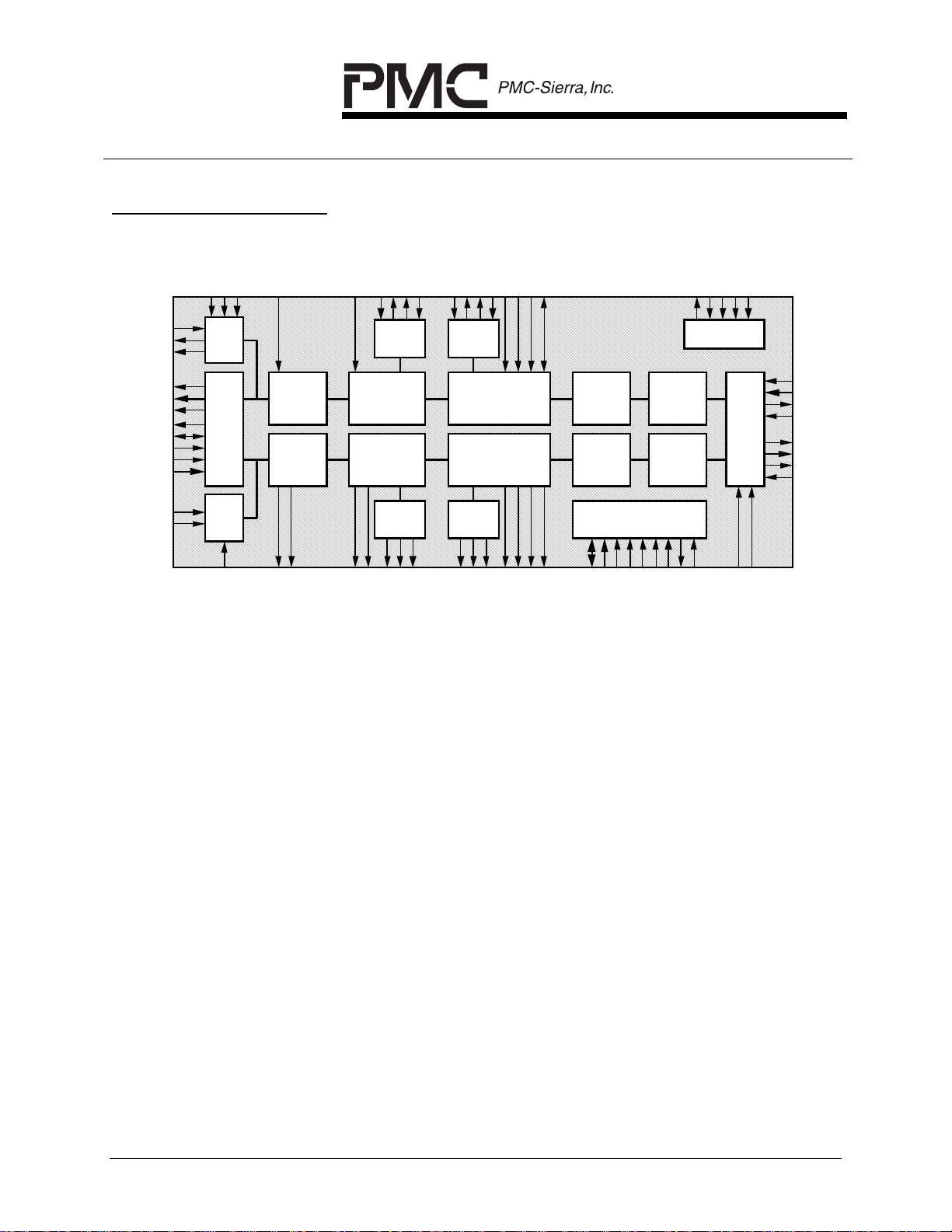

6

POUT[7:0]

BLOCK DIAG RAM

VT2

VT1

TSER

TLAIS

TXCI+/-

TXCO+/-

TXD+/-

FPOUT Tx ATM

POCLK

OOF

PICLK

FPIN

FPOS

PIN[7:0]

RXC+/RXD+/-

Par/

Ser

L ine

Side

I/F

Ser/

Par

RSER

Tx

Section

O/H

Processor

Rx

Section

O/H

Processor

LOF

LOS

TFERFLAIS

Transport

Overhead

Line O/H

Processor

Line O/H

Processor

Transport

Overhead

FERF

TTOH

TTOHFP

Insert

Tx

Rx

Extract

RTOH

TTOHEN

TTOHCLK

RTOHFP

RTOHCLK

TPOH

TPOHCLK

TPOHFP

Path

Overhead

Insert

Processor

Processor

Path

Overhead

Extract

RPOH

RPOHFP

TPOHEN

Tx

Path

O/H

Rx

Path

O/H

RPOHCLK

TFP

LOP

TPAIS

PAIS

TPYEL

PYEL

RCLK

TCLK

Cell

Processor

Rx ATM

Cell

Processor

Microprocessor

A[7:0]

D[7:0]

ALE

I/F

CSB

WRB

Tx ATM

4 Cell

FIFO

Rx ATM

4 Cell

FIFO

RDB

RSTB

TDO

JTAG Test

Access Port

INTB

GPIN

TDI

TCK

TMS

Drop

Side

I/F

BUS8

TRSTB

TSEN

TSOC

TDAT[15:0]

TCA

TWRB

RSOC

RDAT[15:0]

RCA

RRDB

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

7

DESCRIPTION

The PM5345 S/UNI SATURN User Network Interface is a monolithic integrated

circuit that implements the SONET/SDH processing and ATM mapping functions

of a 155 Mbit/s ATM User-Network Interface.

The S/UNI receives SONET/SDH frames, via a bit serial or byte serial interface,

and processes section, line, and path overhead. It performs framing (A1, A2),

descrambling, detects alarm conditions, and monitors section, line, and path bit

interleaved parity (B1, B2, B3), accumulating error counts at each level for

performance monitoring purposes. Line and path far end block error indications

(Z2, G1) are also accumulated. The S/UNI interprets the received payload

pointers (H1, H2) and extracts the synchronous payload envelope which carries

the received ATM cell payload. In addition to its basic processing of the received

SONET/SDH overhead, the S/UNI provides convenient access to all overhead

bytes, which are extracted and serialized on lower rate interfaces, allowing

additional external processing of overhead.

The S/UNI frames to the ATM payload using cell delineation. HCS error

correction is provided. Idle/unassigned cells may be dropped according to a

programmable filter. Cells are also dropped upon detection of an uncorrectable

header check sequence error. The ATM cell payloads are descrambled. The

ATM cells that are passed are written to a four cell FIFO buffer. The received

cells are read from the FIFO using a generic 9 bit wide or 17 bit wide datapath

interface. Counts of received ATM cell headers that are errored and

uncorrectable and also those that are errored and correctable are accumulated

independently for performance monitoring purposes.

The S/UNI transmits SONET/SDH frames, via a bit serial or a byte serial

interface, and formats section, line, and path overhead appropriately. It performs

framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and

creates section, line, and path bit interleaved parity (B1, B2, B3) as required to

allow performance monitoring at the far end. Line and path far end block error

indications (Z2, G1) are also inserted. The S/UNI generates the payload pointer

(H1, H2) and inserts the synchronous payload envelope which carries the ATM

cell payload. In addition to its basic formatting of the transmitted SONET/SDH

overhead, the S/UNI provides convenient access to all overhead bytes, which are

optionally inserted from lower rate serial interfaces, allowing external sourcing of

overhead. The S/UNI also supports the insertion of a large variety of errors into

the transmit stream, such as framing pattern errors, bit interleaved parity errors,

and illegal pointers, which are useful for system diagnostics and tester

applications.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

ATM cells are written to an internal four cell FIFO using a generic 9 bit wide or 17

bit wide datapath interface. Idle/unassigned cells are automatically inserted

when the internal FIFO contains less than one cell. The S/UNI provides

generation of the header check sequence and scrambles the payload of the ATM

cells. Each of these transmit ATM cell processing functions can be enabled or

bypassed.

No auxiliary clocks are required directly by the S/UNI as it operates from two

155.52 MHz clocks (bit serial line interface) or two 19.44 MHz clocks (byte serial

interface). The S/UNI is configured, controlled and monitored via a generic 8-bit

microprocessor bus interface. The S/UNI also provides a standard 5 signal

P1149.1 JTAG test port for boundary scan board test purposes.

The S/UNI is implemented in low power, +5 Volt, CMOS technology. It has TTL

and pseudo ECL (PECL) compatible inputs and outputs and is packaged in a

160 pin PQFP package.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

PM5345 S/UNI-155

5

2

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

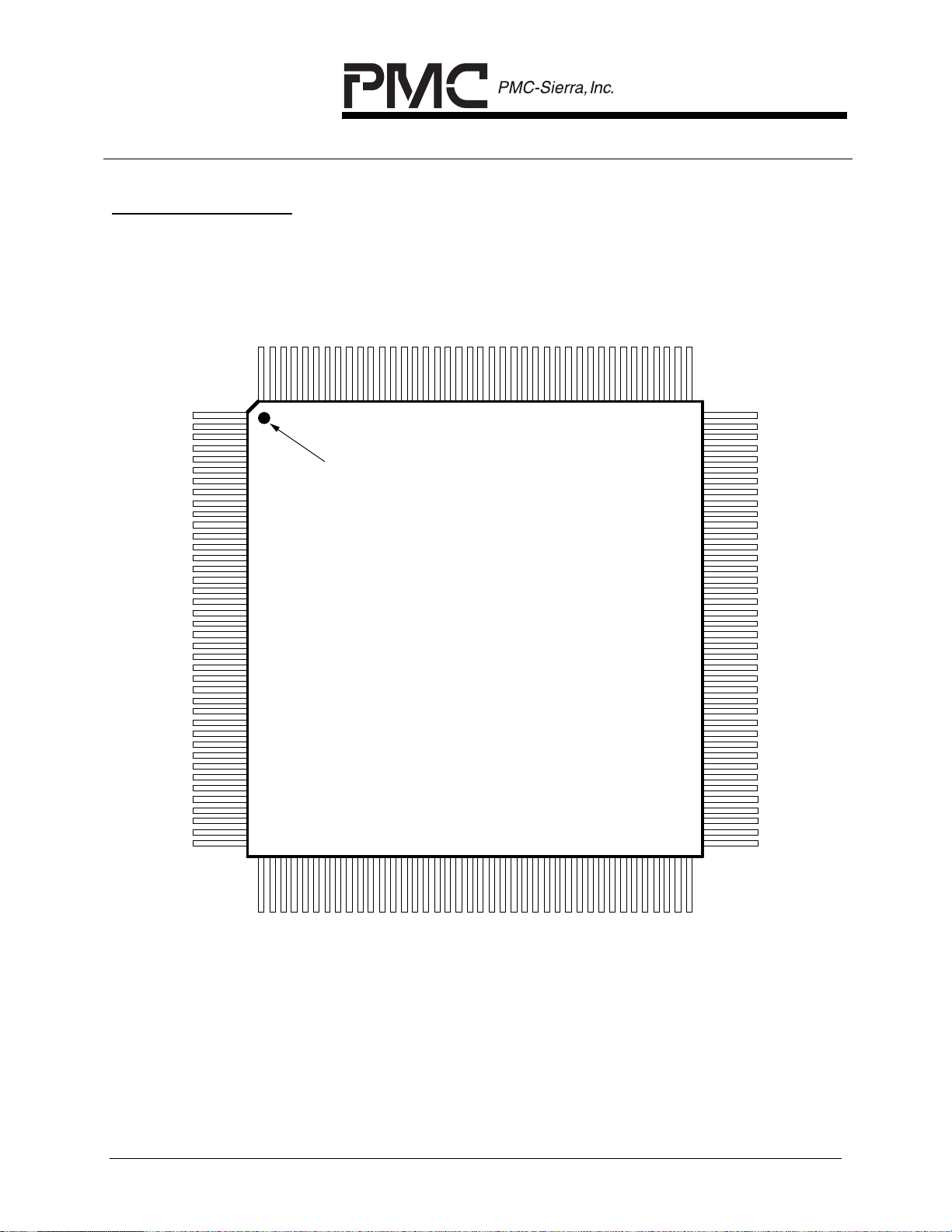

8

PIN DIAG RAM

The S/UNI is packaged in an 160 pin PQFP package having a body size of

28 mm by 28 mm and a pin pitch of 0.65 mm.

PIN3

PIN 160

POUT1

POUT2

POUT0

FPIN

RCLK

VSSO

VDDI

VDDO

PICLK

PIN7

PIN6

PIN5

PIN4

PIN2

PIN1

PIN0

RXD+

RXD-

RAVS

RAVD

RXC+

RXC-

RDAT1

VSSO

RDAT14

RDAT13

VDDO

RDAT1

RDAT11

VSSI

RDAT10

VSSO

RDAT9

RDAT8

RDAT7

VDDO

RDAT5

RDAT6

PIN 1

POUT3

POUT4

POUT5

POUT6

POUT7

VSSO

TCLK

VDDO

POCLK

FPOUT

FPOS/MLT

VSSI

TXCI-

TXCI+

TAVD1

TAVS1

VT1

TXCOTXCO+

TAVD2

TAVS2

TXD+

TXD-

VT2

RSER

TSER

TFP

TPAIS

TLAIS

TPYEL

TFERF

OOF

LOS

LOF

LOP

VSSO

PAIS

LAIS

PYEL

FERF

Index

PM5345

S/UNI

(Top View)

VSSO

PIN 121

PIN 120

RDAT4

RDAT3

RDAT2

RDAT1

VDDO

RDAT0

VSSO

RSOC

RCA

RRDB

BUS8

TSEN

RDB

WRB

D7

D6

D5

D4

VDDO

VDDI

TCK

VSSO

D3

D2

D1

D0

INTB

A7

A6

A5

A4

A3

A2

A1

A0

CSB

ALE

RSTB

TRSTB

GPIN

PIN 40

PIN 41 PIN 80

RTOHFP

TTOHEN

TPOHEN

TPOH

TPOHFP

VDDO

TPOHCLK

RPOHFP

RPOH

VSSO

RPOHCLK

TTOH

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

RTOH

TTOHFP

TTOHCLK

RTOHCLK

TWRB

VDDI

TCA

TSOC

TDAT0

TDAT1

TDAT2

TDAT3

TDAT4

TDAT5

TDAT6

TDAT7

VSSI

TDAT8

TDAT9

TDAT11

TDAT10

TDAT13

TDAT12

TDAT15

TDAT14

TDO

TDI

TMS

PIN 81

15

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

9

PIN DESCRIPTION

Table 1 -

Pin Name Type Pin

Function

No.

RSER Input 25 The receive serial input (RSER) selects the

receive line interface. RSER is tied high to

select the 155.52 Mbit/s interface (on pins

RXC+, RXC-, RXD+, and RXD-). RSER is tied

low to select the 19.44 Mbyte/s interface (on

pins PICLK, PIN[7:0], and FPIN).

RXD+

RXD-

Input 143

142

The receive differential data inputs (RXD+,

RXD-) contain the 155.52 Mbit/s receive STS-

3c (STM-1) stream when the bit serial interface

is selected (RSER is tied high). RXD+/- is

sampled on the rising edge of RXC+/- (the

falling edge may be used by reversing RXC+/-

).

RXC+

RXC-

Input 139

138

The receive differential clock inputs (RXC+,

RXC-) contain the receive clock when the bit

serial interface is selected (RSER is tied high).

RXC+/- is nominally a 155.52 MHz, 50% duty

cycle clock. This clock is divided by eight

internally to produce RCLK when the bit serial

interface is selected and provide timing for the

S/UNI receive functions. RXD+/- is sampled

on the rising edge of RXC+/-.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

PICLK I/O 153 The parallel input clock (PICLK) provides

timing for sampling the received SONET STS-

3c (STM-1) stream that is input by the S/UNI

when the byte serial interface is selected

(RSER is tied low). This clock provides timing

for S/UNI receive function operation. PICLK is

nominally a 19.44 MHz, 50% duty cycle clock.

PIN[7:0] and FPIN are sampled on the rising

edge of PICLK. RCLK is a buffered version of

PICLK when the byte serial interface is

selected. When the 155 Mbit/s serial interface

is selected (RSER is tied high), PICLK

becomes an output and must not be driven.

RX_VCLK The test vector clock (RX_VCLK) signal is

used during S/UNI production testing to verify

internal functionality.

PIN[0]

PIN[1]

PIN[2]

PIN[3]

Input 144

145

146

147

The data input (PIN[7:0]) bus carries the STS-

3c (STM-1) stream when the byte serial

interface is selected (RSER is tied low).

PIN[7:0] is sampled on the rising edge of

PICLK. PIN[7] is the most significant bit

(corresponding to bit 1 of each serial word, the

PIN[4]

PIN[5]

148

149

first bit transmitted). PIN[0] is the least

significant bit (corresponding to bit 8 of each

word, the last bit transmitted).

PIN[6]

150

PIN[7]

151

FPOS/MLT Input 11 The dual function input (FPOS/MLT) selects

both the transmit encoding scheme and the

receive frame pulse location depending on the

line side interface selected using inputs TSER

and RSER.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

17

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

No.

Function

When the byte serial receive interface is

selected (RSER=0), the FPOS/MLT input

selects the frame byte position in the SONET

frame indicated by the FPIN input. When

FPOS/MLT is tied high, a pulse on FPIN ma rks

the third A2 framing byte position on the

PIN[7:0] bus. When FPOS/MLT is tied low, a

pulse on FPIN marks the first synchronous

payload envelope byte position after the three

C1 bytes on PIN[7:0].

When the bit serial transmit interface is

selected (TSER=1), the FPOS/MLT input

selects MLT-3 encoding of the transmit stream.

When FPOS/MLT is tied high, an MLT-3

encoded data stream is transmitted on the

TXCO+/- and TXD+/- outputs. When

FPOS/MLT is tied low, 155 Mbit/s clock and

data are inserted on the TXCO+/- and TXD+/-

outputs.

FPIN Input 157 The active high framing position input (FPIN)

signal indicates the SONET frame position on

the PIN[7:0] bus. The byte position indicated

by FPIN is selected by the FPOS/MLT input as

described above. FPIN is sampled on the

rising edge of PICLK.

OOF Output 32 The out of frame (OOF) signal is high while the

S/UNI is out of frame. OOF is low while the

S/UNI is in-frame. An out of frame occurs

when 4 consecutive errored framing patterns

(A1 and A2 bytes) have been received. OOF

is intended to be used to enable an upstream

framing pattern detector to search for the

framing pattern when the byte serial interface

is selected. This alarm indication is also

available via register access. OOF is updated

on the falling edge of RCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

18

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

RCLK Output 156 The receive clock (RCLK) output provides a

timing reference for S/UNI receive outputs.

RCLK is a 19.44 MHz, nominally 50% duty

cycle clock. RCLK is a buffered version of

PICLK when the byte serial interface is

selected (RSER is tied low). RCLK is a divide

by eight of RXC+/- when the bit serial interface

is selected (RSER is tied high).

TSER Input 26 The transmit serial input (TSER) selects the

transmit line interface. TSER is tied high to

select the 155.52 Mbit/s interface (on pins

TXCI+, TXCI-, TXCO+, TXCO-, TXD+, and

TXD-). TSER is tied low to select the 19.44

Mbyte/s interface (on pins TCLK, FPOUT, and

POUT[7:0]).

TXD+

TXD-

Output 22

23

The transmit differential data/positive pulse

outputs (TXD+, TXD-) contain either NRZ or

MLT-3 encoded data when the bit serial

interface is selected (TSER is tied high).

TXCI+

TXCI-

Input 14

13

When NRZ encoding is selected (FPOS/MLT is

tied low), the 155.52 Mbit/s transmit STS-3c

(STM-1) stream TXD+/- is updated on the

falling edge of TXCO+/-.

When MLT-3 encoding is selected (FPOS/MLT

is tied high), the TXD+/- outputs contain the

positive pulses of the MLT-3 encoded stream.

The transmit differential clock inputs (TXCI+,

TXCI-) contain the transmit clock when the bit

transmit serial interface is selected. TXCI+/- is

nominally a 155.52 MHz, 50% duty cycle clock.

This clock provides timing for the S/UNI

transmit functions. TXCI+/- may be left

unconnected when S/UNI loop timing is

enabled (using the S/UNI Master Control

Register).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

19

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TXCO+

TXCO-

Output 19

18

The transmit differential clock/negative pulse

outputs (TXCO+, and TXCO-) contain either

the transmit output clock or MLT-3 encoded

data when the bit serial interface is selected

(TSER is tied high).

When NRZ encoding is selected (FPOS/MLT is

tied low), TXCO+/- is a buffered version of

TXCI+/-. TXD+/- is updated on the falling edge

of TXCO+/-.

When MLT-3 encoding is selected (FPOS/MLT

is tied high), the TXCO+/- outputs contain the

negative pulses of the MLT-3 encoded stream.

POCLK Output 9 The parallel output clock (POCLK) signal

provides timing for processing of the data that

is output by the S/UNI. POCLK is nominally a

19.44 MHz, 50% duty cycle clock. POCLK is a

buffered version of TCLK when the byte serial

interface is selected (TSER is tied low).

POCLK is a divide by eight of TXCI+/- when

the bit serial interface is selected (TSER is tied

high).

POUT[0]

POUT[1]

POUT[2]

POUT[3]

Output 158

159

160

1

The scrambled data output (POUT[7:0]) bus

carries data when the byte serial interface is

selected (TSER is tied low). POUT[7:0] is

updated on the rising edge of TCLK. POUT[7]

is the most significant bit (corresponding to bit

1 of each serial word, the first bit transmitted).

POUT[4]

POUT[5]

2

3

POUT[0] is the least significant bit

(corresponding to bit 8 of each serial word, the

last bit transmitted).

POUT[6]

POUT[7]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

5

20

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

FPOUT Output 10 The active high framing position output

(FPOUT) signal marks the frame alignment on

the POUT[7:0] bus. FPOUT goes high for a

single TCLK period while the first synchronous

payload envelope byte after the three C1 bytes

is present on POUT[7:0]. FPOUT is updated

on the rising edge of TCLK.

LOS Output 33 The loss of signal (LOS) signal is set high

when loss of signal is declared. This occurs

when a violating period (20 ± 3 µs) of

consecutive all zeros bytes is detected on the

incoming STS-3c(STM-1) signal (before

descrambling). LOS is removed when two

valid framing words (A1, A2) are detected and

during the intervening time, no violating period

of consecutive all zeros patterns is detected.

This alarm indication is also available via

register access. LOS is updated on the falling

edge of RCLK.

LOF Output 34 The loss of frame (LOF) signal is set high

when loss of frame is declared. This occurs

when an out-of-frame condition (as indicated

by a high level on the OOF output) persists for

a period of 3 ms. LOF is removed when an in-

frame condition (as indicated by a low level on

the OOF output) persists for a period of 3 ms.

This alarm indication is also available via

register access. LOF is updated on the falling

edge of RCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

21

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

LAIS Output 38 The line alarm indication signal (LAIS) is set

high when line AIS is declared. This occurs

when a 111 binary pattern is detected in bits

6,7,8 of the K2 byte for five consecutive

frames. LAIS is removed when any pattern

other than 111 is detected in bits 6, 7, and 8 of

the K2 byte for five consecutive frames. This

alarm indication is also available via register

access. LAIS is updated on the falling edge of

RCLK.

FERF Output 40 The line far end receive failure (FERF) signal is

set high when line FERF is declared. This

occurs when a 110 binary pattern is detected

in bits 6, 7, and 8 of the K2 byte for five

consecutive frames. FERF is removed when

any pattern other than 110 is detected in bits

6, 7, and 8 of the K2 byte for five consecutive

frames. This alarm indication is also available

via register access. FERF is updated on the

falling edge of RCLK.

LOP Output 35 The loss of pointer (LOP) signal is set high

when loss of pointer is declared. This occurs

when a valid pointer (H1, H2) is not found in

eight consecutive frames, or if eight

consecutive new data flags are detected. LOP

is removed when the same valid and normal

pointer with a normal new data flag is detected

in three consecutive frames. The loss of

pointer state is not entered if the incoming

stream contains path AIS. This alarm

indication is also available via register access.

LOP is updated on the falling edge of RCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

22

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

PAIS Output 37 The path AIS (PAIS) signal is set high when

STS-path AIS is declared. This occurs when

an all ones pattern is observed in the pointer

bytes (H1, H2) for three consecutive frames.

Path AIS is removed when the same valid and

normal pointer is detected for three

consecutive frames or a legal pointer with an

active NDF is received. This alarm indication is

also available via register access. PAIS is

updated on the falling edge of RCLK.

PYEL Output 39 The path yellow (PYEL) signal is set high when

STS-path yellow alarm is declared. This

occurs when bit 5 of the path status byte (G1)

is set high for ten consecutive frames. Path

yellow is removed when bit 5 of the G1 byte is

set low for ten consecutive frames. This alarm

indication is also available via register access.

PYEL is updated on the falling edge of RCLK.

TLAIS Input 29 The active high transmit line alarm indication

(TLAIS) signal controls the insertion of line

AIS. Line AIS is inserted by overwriting the

SONET/SDH frame contents with all ones

(before scrambling). The section overhead is

not overwritten. This function can also be

performed via register access. Line AIS

insertion is internally synchronized to frame

boundaries. The TLAIS input takes

precedence over the TTOH and TTOHEN

inputs. TLAIS is samp led on the rising edge of

POCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

23

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TFERF Input 31 The active high transmit line far end receive

failure (TFERF) signal controls the insertion of

line FERF. Line FERF is inserted by

transmitting the code 110 (binary) in bit

positions 6,7, and 8 of the K2 byte. This

function can also be performed via register

access, or be enabled to occur automatically

upon detection of receive line AIS, loss of

signal, or loss of frame. The TFERF input

takes precedence over the TTOH and TTOHEN

inputs. TFERF is sampled on the r ising edge

of POCLK.

TPAIS Input 28 The active high transmit path alarm indication

(TPAIS) signal controls the insertion of STS-

path AIS. A high level on TPAIS forces the

insertion of an all ones pattern into the

complete synchronous payload envelope, and

the payload pointer bytes (H1, H2). Path AIS

insertion is internally synchronized to SPE

frame boundaries. This function can also be

performed via register access. TPAIS is

sampled on the rising edge of POCLK.

TPYEL Input 30 The transmit path yellow alarm (TPYEL) signal

controls the insertion of path yellow alarm. A

high level on TPYEL forces a logic one to be

inserted in the path yellow bit position in the

path status byte (G1). This function can also

be performed via register access, or be

enabled to occur automatically upon detection

of receive line AIS, loss of frame, loss of

signal, loss of pointer, or STS-path AIS. The

TPOH and TPOHEN inputs take precedence

over the TPYEL input. TPYEL is sampled on

the rising edge of POCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

24

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TSEN Input 109 The tristate enable (TSEN) input selects the

configuration of the receive datapath

(RDAT[15:0]). When TSEN is tied high,

RDAT[15:0] normally operates as a tristate bus

controlled by RRDB. When RRDB is high,

RDAT[15:0] is tristated. When RRDB is low,

RDAT[15:0] is enabled. When TSEN is tied

low, RDAT[15:0] normally operates as an

output bus, and is always enabled, regardless

of the state of RRDB

BUS8 Input 110 The bus width select (BUS8) input sele cts the

transmit and receive datapath widths. When

BUS8 is tied high, a 9-bit interface consisting

of a start of cell indication, and an 8-bit octet

bus is selected. When BUS8 is tied low, a 17-

bit interface consisting of a start of cell

indication, and a 16-bit word bus is selected.

RRDB Input 111 The active low receive read strobe (RRDB) is

used to read ATM cells from the receive FIFO.

When active, RRDB must cycle at a 25 MHz or

lower instantaneous rate, but at a high enough

rate to avoid FIFO overflow. RSOC is updated

on the rising edge of RRDB. RDAT[15:0] are

updated on the falling edge of RRDB.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

25

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

No.

RDAT[0]

RDAT[1]

RDAT[2]

RDAT[3]

RDAT[4]

RDAT[5]

RDAT[6]

RDAT[7]

RDAT[8]

RDAT[9]

RDAT[10]

RDAT[11]

RDAT[12]

Tristate 115

117

118

119

120

122

123

125

``•`

````

`ü``

```•

````

Function

```ü`````•``````ü`````•``````ü`````•``````ü`````•``````ü

`````````••••at are read from the receive FIFO.

When the 17-bit datapath is selected (BUS8 is

tied low), RDAT[15:0] contains the 16-bit wide

word bus. When the 9-bit datapath is selected

(BUS8 is tied high), RDAT[7:0] contains the 8-

bit wide word bus (RDAT[15:8] is not used).

The RDAT[15:0] bus is tristate d while RRDB is

high, and TSEN is high. The RDAT[15:0] bus is

always driven when TSEN is low, regardless of

the leve l of RRDB. RDAT[15:0] is updated on

the falling edge of RRDB.

RDAT[13]

RDAT[14]

RDAT[15]

``ü`

````

•```

RSOC Output 113 The receive start of cell (RSOC) signal marks

the start of cell on the RDAT[15:0] bus. When

RSOC is high, the first word of the selected

data structure is present on the RDAT[15:0]

stream. RSOC is updated on the rising edge

of RRDB.

RCA Output 112 The receive cell available (RCA) signal

indicates when a cell is available in the receive

FIFO. The low to high transition of RCA

(indicating that the receive FIFO is not empty)

occurs on the falling edge of RCLK. The high

to low transition of RCA (indicating that the

receive FIFO is empty) occurs on the falling

edge of RRDB. The active polarity of this

signal is programmable and defaults to active

high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

26

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TCLK I/O 7 The transmit clock (TCLK) provides timing for

S/UNI transmit function operation when the

byte serial interface is selected (TSER is tied

low). TCLK must be a 19.44 MHz, nominally

50% duty cycle clock. POCLK is a buffered

version of TCLK when byte serial interface is

selected.

When the 155 Mbit/s serial interface is

selected (TSER is tied high), TCLK becomes

an output and should not be driven.

TX_VCLK The test vector clock (TX_VCLK) signal is used

during S/UNI production testing to verify

internal functionality.

TFP Input 27 The active high transmit frame pulse (TFP)

signal is used to align the SONET/SDH

transport frame generated by the S/UNI device

to a system reference when the byte serial

interface is selected (TSER is low). TFP

should be brought high for a single TCLK

period every 2430 TCLK cycles or a multiple

thereof. TFP may be tied low if such

synchronization is not required. The offset

between an active TFP input and the resultant

FPOUT pulse is 24 TCLK periods. TFP is

sampled on the rising edge of TCLK.

TWRB Input 58 The transmit write strobe (TWRB) is used to

write ATM cells to the four cell transmit FIFO.

When active, TWRB cycles at a 25 MHz or

lower instantaneous rate. A complete 53 octet

cell must be written to the FIFO before being

inserted in the STS-3c (STM-1) SPE.

Idle/unassigned cells are inserted when a

complete cell is not available. TDAT[15:0] and

TSOC are sampled on the rising edge of

TWRB.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

27

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

No.

TDAT[0]

TDAT[1]

TDAT[2]

TDAT[3]

TDAT[4]

TDAT[5]

TDAT[6]

TDAT[7]

TDAT[8]

TDAT[9]

TDAT[10]

TDAT[11]

TDAT[12]

Input 61

62

63

64

65

66

67

68

70

71

72

73

74

Function

The transmit cell data (TDAT[15:0]) bus carries

the ATM cell octets that are written to the

transmit FIFO. When the 17-bit datapath is

selected (BUS8 is tied low), TDAT[15:0]

contains the 16-bit wide word bus. When the

9-bit datapath is selected (BUS8 is tied high),

TDAT[7:0] contains the 8-bit wide octet bus

(TDAT[15:8] is not used). TDAT[15:0] is

sampled on the rising edge of TWRB.

TDAT[13]

TDAT[14]

TDAT[15]

75

76

77

TSOC Input 60 The transmit start of cell (TSOC) signal marks

the start of cell on the TDAT[15:0] bus. When

TSOC is high, the first word of the selected

data structure is present on the TDAT[15:0]

stream. It is not necessary for TSOC to be

present at each cell. An interrupt may be

generated if TSOC is high during any word

other than the first word of the selected data

structure. TSOC is sampled on the rising edge

of TWRB.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

28

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TCA Output 59 The transmit cell available (TCA) signal

indicates when a cell is available in the

transmit FIFO. The low to high transition of

TCA (indicating that the transmit FIFO is not

full) occurs on the falling edge of POCLK. The

high to low transition of TCA (indicating that

the transmit FIFO is full) occurs on the falling

edge of TWRB. The active polarity of this

signal is programmable and defaults to active

high.

RTOH Output 54 The receive transport overhead data (RTOH)

signal contains the receive transport overhead

bytes (A1, A2, C1, B1, E1, F1, D1-D3, H1-H3,

B2, K1, K2, D4-D12, Z1, Z2, and E2) extracted

from the received SONET/SDH frame. RTOH

is updated on the falling edge of RTOHCLK.

RTOHCLK Output 56 The receive transport overhead clock

(RTOHCLK) is nominally a 5.184 MHz clock

which provides timing to process the extracted

receive transport overhead. RTOHCLK is a

gapped 6.48 MHz clock. RTOHCLK is updated

on the falling edge of RCLK.

RTOHFP Output 55 The receive transport overhead frame position

(RTOHFP) signal may be used to locate the

individual receive transport overhead bits in

the transport overhead data stream, RTOH.

RTOHFP is logic one while bit 1 (the most

significant bit) of the first framing byte (A1) is

present in the RTOH stream. RTOHFP is

updated on the falling edge of RTOHCLK.

RPOH Output 46 The receive path overhead data (RPOH) signal

contains the path overhead bytes (J1, B3, C2,

G1, F2, H4, Z3, Z4, and Z5) extracted from the

received STS-3c (STM-1) frame. RPOH is

updated on the falling edge of RPOHCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

29

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

RPOHCLK Output 48 The receive path overhead clock (POHCLK) is

nominally a 576 kHz clock which provides

timing to process the extracted receive path

overhead. RPOHCLK is a gapped 2.16 MHz

clock. RPOHCLK is updated on the falling

edge of RCLK.

RPOHFP Output 47 The receive path overhead frame position

(RPOHFP) signal may be used to locate the

individual receive path overhead bits in the

path overhead data stream, RPOH. RPOHFP

is logic one while bit 1 (the most significant bit)

of the path trace byte (J1) is present in the

RPOH stream. RPOHFP is updated on the

falling edge of RPOHCLK.

TTOH Input 51 The transmit transport overhead data (TTOH)

signal contains the transport overhead bytes

(A1, A2, C1, E1, F1, D1-D3, K1, K2, D4-D12,

Z1, Z2, and E2) and error masks (B1, B2, H1,

and H2) which may be inserted, or used to

insert section/line BIP or payload pointer bit

errors into the transport overhead byte

positions transmit STS-3c (STM-1) stream.

Insertion is controlled by the TTOHEN input, or

by bits in internal registers. TTOH is sampled

on the rising edge of TTOHCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

30

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TTOHEN Input 49 The transmit transport overhead insert enable

(TTOHEN) signal, together with internal

register bits, controls the source of the

transport overhead data which is transmitted.

While TTOHEN is high, values sampled on the

TTOH input are inserted into the

corresponding transport overhead bit position

(for the A1, A2, C1, E1, F1, D1-D3, K1, K2,

H3, D4-D12, Z1, Z2, and E2 bytes). While

TTOHEN is low, default values are inserted

into these transport overhead bit positions. A

high level on TTOHEN during the B1, B2 or

H1-H2 bit positions enables an error mask.

While the error mask is enabled, a high level

on input TTOH causes the corresponding B1,

B2 or H1-H2 bit position to be inverted. A low

level on TTOH allows the corresponding bit

position to pass through the S/UNI

uncorrupted. TTOHEN is sampled on the

rising edge of TTOHCLK.

TTOHCLK Output 53 The transmit transport overhead clock

(TTOHCLK) is nominally a 5.184 MHz clock

which provides timing for upstream circuitry

that sources the transport overhead stream,

TTOH. TTOHCLK is a gapped 6.48 MHz clock.

TTOHCLK is updated in the falling edge of

POCLK.

TTOHFP Output 52 The transmit transport overhead frame position

(TTOHFP) signal may be used to locate the

individual transport overhead bits in the

transport overhead data stream, TTOH.

TTOHFP is logic one while bit 1 (the most

significant bit) of the first framing byte (A1) is

expected in the TTOH stream. TTOHFP is

updated on the falling edge of TTOHCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

31

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TPOH Input 42 The transmit path overhead data (TPOH)

signal contains the path overhead bytes (J1,

C2, G1, F2, Z3, Z4, and Z5) and error masks

(B3, and H4) which may be inserted, or used

to insert path BIP-8 or multiframe bit errors into

the path overhead byte positions in the STS-3c

(STM-1) stream. Insertion is controlled by the

TPOHEN input, or by bits in internal registers.

TPOH is sampled on the rising edge of

TPOHCLK.

TPOHEN Input 41 The transmit path overhead insert enable

(TPOHEN) signal, together with internal

register bits, controls the source of the path

overhead data which is inserted in the

POUT[7:0] stream. While TPOHEN is high,

values sampled on the TPOH input are

inserted into the corresponding path overhead

bit position (for the J1, C2, G1, F2, Z3, Z4, and

Z5 bytes). While TPOHEN is low, values

obtained from internal registers are inserted

into these path overhead bit positions. A high

level on TPOHEN during the H4 or B3 bit

positions enables an error mask. While the

error mask is enabled, a high level on input

TPOH causes the corresponding B3 or H4 bit

position to be inverted. A low level on TPOH

allows the corresponding bit position to pass

through the S/UNI uncorrupted. TPOHEN is

sampled on the rising edge of TPOHCLK.

TPOHCLK Output 44 The transmit path overhead clock (TPOHCLK)

is nominally a 576 kHz clock which provides

timing for upstream circuitry that sources the

path overhead stream, TPOH. TPOHCLK is a

gapped 2.16 MHz clock. TPOHCLK is updated

in the falling edge of POCLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

32

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

Function

No.

TPOHFP Output 43 The transmit path overhead frame position

(TPOHFP) signal may be used to locate the

individual path overhead bits in the path

overhead data stream, TPOH. TPOHFP is

logic one while bit 1 (the most significant bit) of

the path trace byte (J1) is expected in the

TPOH stream. TPOHFP is updated on the

falling edge of TPOHCLK.

GPIN Input 81 The general purpose input (GPIN) signal may

be used to monitor the state of an external

alarm or status point (such as a lock detect

alarm from an external PMD). An interrupt may

be enabled when this signal changes state.

GPIN may be asynchronous but should be

glitch free. GPIN has an integral pull down

resistor.

CSB Input 85 The active low chip select (CSB) signal is low

during S/UNI register accesses. If register

accesses are controlled using only the RDB

and WRB signals, CSB should be connected to

an inverted version of the RSTB input.

RDB Input 108 The active low read enable (RDB) signal is low

during S/UNI register read accesses. The

S/UNI drives the D[7:0] bus with the contents

of the addressed register while RDB and CSB

are low.

WRB Input 107 The active low write strobe (WRB) signal is low

during a S/UNI register write accesses. The

D[7:0] bus contents are clocked into the

addressed register on the rising WRB edge

while CSB is low.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

33

PM5345 S/UNI-155

DATA SHEET

PMC-930305 ISSUE 4 SATURN USER NETWORK INTERFACE

Pin Name Type Pin

No.

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

A[0]

A[1]

A[2]

A[3]

A[4]

I/O 95

96

97

98

103

104

105

106

Input 86

87

88

89

90

Function

The bidirectional data bus D[7:0] is used

during S/UNI register read and write accesses.

The address bus A[7:0] selects specific

registers during S/UNI register accesses.

A[5]

A[6]

91

92

A[7]/TRS 93 The test register select (TRS) signal selects

between normal and test mode register

accesses. TRS is high during test mode

register accesses, and is low during normal

mode register accesses. TRS has an integral

pull down resistor.

RSTB Input 83 The active low reset (RSTB) signal provides an

asynchronous S/UNI reset. RSTB is a Schmitt

triggered input with an integral pull up resistor.