PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

PM5342

SPECTRA-155

SONET/SDH PAYLOAD

EXTRACTOR/ALIGNER

DATA SHEET

PROPRIET A R Y A ND CONFIDENTIAL

ISSUE 4: AUGUST 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

CONTENTS

1 FEATURES ..........................................................................................1

2 APPLICATIONS ...................................................................................6

3 REFERENCES.....................................................................................6

4 APPLICATION EXAMPLE....................................................................8

5 BLOCK DIAGRAM .............................................................................13

6 DESCRIPTION ..................................................................................17

7 PIN DIAGRAMS.................................................................................19

8 PIN DESCRIPTION (256) ..................................................................27

9 FUNCTIONAL DESCRIPTION.........................................................108

10 REGISTER DESCRIPTION .............................................................144

11 TEST FEATURES DESCRIPTION ..................................................410

12 OPERATION ....................................................................................425

13 FUNCTIONAL TIMING.....................................................................441

14 ABSOLUTE MAXIMUM RATINGS...................................................486

15 D.C. CHARACTERISTICS ...............................................................487

16 MICROPROCESSOR INTERFACE TIMING

CHARACTERISTICS .......................................................................492

17 SPECTRA-155 TIMING CHARACTERISTICS.................................500

18 ORDERING AND THERMAL INFORMATION..................................533

19 MECHANICAL INFORMATION ........................................................534

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE i

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

LIST OF REGISTERS

REGISTER ADDRESS 00H: SPECTRA-155 CONFIGURATION ...............153

REGISTER ADDRESS 01H: SPECTRA-155 SECTION/LINE

CONTROL/ENABLE ........................................................................155

REGISTER ADDRESS 02H: SPECTRA-155 SECTION/LINE

INTERRUPT STATUS......................................................................157

REGISTER ADDRESS 03H: SPECTRA-155 RESET, IDENTITY,

ACCUMULATION TRIGGER ...........................................................159

REGISTER ADDRESS 04H: TLOP CONTROL..........................................161

REGISTER ADDRESS 05H: TLOP DIAGNOSTIC .....................................162

REGISTER ADDRESS 06H: TLOP TRANSMIT K1....................................163

REGISTER ADDRESS 07H: TLOP TRANSMIT K2....................................164

REGISTER ADDRESS 08H: RLOP CONTROL/STATUS...........................165

REGISTER ADDRESS 09H: RLOP INTERRUPT ENABLE AND

STATUS ...........................................................................................168

REGISTER ADDRESS 0AH: RLOP B2 ERROR COUNT #1......................170

REGISTER ADDRESS 0DH: RLOP REI ERROR COUNT #1....................171

REGISTER ADDRESS 10H: RSOP CONTROL .........................................172

REGISTER ADDRESS 11H: RSOP INTERRUPT STATUS........................174

REGISTER ADDRESS 12H: RSOP B1 ERROR COUNT #1......................176

REGISTER ADDRESS 14H: SPECTRA-155 OUTPUT PORT...................177

REGISTER ADDRESS 15H: SPECTRA-155 INPUT PORT

INTERRUPT ENABLE .....................................................................178

REGISTER ADDRESS 17H: SPECTRA-155 RING CONTROL .................179

REGISTER 18H: TSOP CONTROL............................................................181

REGISTER 19H: TSOP DIAGNOSTIC.......................................................182

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER 1AH: SPECTRA-155 TRANSMIT Z1/S1..................................183

REGISTER 1BH: TSOP TRANSMIT Z0 .....................................................184

REGISTER 1CH: SPECTRA-155 OVERHEAD UNUSED BYTES

CONTROL .......................................................................................185

REGISTER ADDRESS 1DH: SPECTRA-155 RECEIVE LINE AIS

CONTROL .......................................................................................187

REGISTER ADDRESS 1EH: SPECTRA-155 LINE RDI CONTROL...........189

REGISTER ADDRESS 1FH: SPECTRA-155 INPUT PORT

STATUS/VALUE...............................................................................191

REGISTER 20H: RASE INTERRUPT ENABLE .........................................193

REGISTER 21H: RASE INTERRUPT STATUS ..........................................194

REGISTER 22H: RASE CONFIGURATION/CONTROL.............................196

REGISTER 23H: RASE SF ACCUMULATION PERIOD.............................198

REGISTER 26H: RASE SF SATURATION THRESHOLD..........................199

REGISTER 28H: RASE SF DECLARING THRESHOLD............................200

REGISTER 2AH: RASE SF CLEARING THRESHOLD..............................201

REGISTER 2CH: RASE SD ACCUMULATION PERIOD............................202

REGISTER 2FH: RASE SD SATURATION THRESHOLD .........................203

REGISTER 31H: RASE SD DECLARING THRESHOLD ...........................204

REGISTER 33H: RASE SD CLEARING THRESHOLD..............................205

REGISTER ADDRESS 35H: RASE RECEIVE K1......................................206

REGISTER ADDRESS 36H: RASE RECEIVE K2......................................207

REGISTER 37H: RASE RECEIVE Z1/S1...................................................208

REGISTER 38H: SSTB SECTION TRACE CONTROL..............................209

REGISTER 39H: SSTB SECTION TRACE STATUS..................................211

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER 3AH: SSTB SECTION TRACE INDIRECT ADDRESS ............213

REGISTER 3BH: SSTB SECTION TRACE INDIRECT DATA ....................214

REGISTER 40H: CRSI CLOCK RECOVERY CONTROL, STATUS

AND INTERRUPT ............................................................................215

REGISTER 41H: CRSI PHASE LOCK LOOP MODE SELECT..................217

REGISTER 42H: CSPI CLOCK SYNTHESIS CONTROL, STATUS

AND INTERRUPT ............................................................................218

REGISTER 78H: SPECTRA-155 PRS GENERATOR CONTROL .............220

REGISTER 79H: SPECTRA-155 PRS MONITOR DROP

CONTROL .......................................................................................222

REGISTER 7AH: SPECTRA-155 PRS MONITOR ADD CONTROL ..........224

REGISTER 7BH: SPECTRA-155 PRS MONITOR INTERRUPT

STATUS ...........................................................................................226

REGISTER 7CH: SPECTRA-155 PRS MONITOR DROP COUNT............227

REGISTER 7EH: SPECTRA-155 PRS MONITOR ADD COUNT ...............228

REGISTER 80H: SPECTRA-155 CLOCK CONTROL................................229

REGISTER 81H: SPECTRA-155 RECEIVE OVERHEAD OUTPUT

CONTROL .......................................................................................231

REGISTER 82H: SPECTRA-155 TRANSMIT OVERHEAD INPUT

CONTROL .......................................................................................233

REGISTER 83H: SPECTRA-155 SECTION ALARM OUTPUT

CONTROL .......................................................................................235

REGISTER 84H: SPECTRA-155 RALM[1] OUTPUT CONTROL...............236

REGISTER 85H: SPECTRA-155 RALM[2] OUTPUT CONTROL ..............237

REGISTER 86H: SPECTRA-155 RALM[3] OUTPUT CONTROL ..............238

REGISTER 87H: SPECTRA-155 DATA MODE CONFIGURATION ...........239

REGISTER 88H: SPECTRA-155 PATH AND DS3 RECEIVE AIS

CONTROL #1...................................................................................241

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iv

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER 89H: SPECTRA-155 PATH AND DS3 RECEIVE AIS

CONTROL #2...................................................................................243

REGISTER 8AH: SPECTRA-155 PATH AND DS3 RECEIVE AIS

CONTROL #3...................................................................................245

REGISTER 90H, 98H, A0H: D3MD CONTROL..........................................247

REGISTER 91H, 99H, A1H: D3MD INTERRUPT STATUS ........................248

REGISTER 92H, 9AH, A2H: D3MD INTERRUPT ENABLE .......................249

REGISTER 94H, 9CH, A4H: D3MA CONTROL..........................................250

REGISTER 95H, 9DH, A5H: D3MA INTERRUPT STATUS ........................251

REGISTER 96H, 9EH, A6H: D3MA INTERRUPT ENABLE........................252

REGISTER B0H, C0H, D0H: TPIP STATUS AND CONTROL

(EXTD=0).........................................................................................253

REGISTER B0H, C0H, D0H: TPIP STATUS AND CONTROL

(EXTD=1).........................................................................................255

REGISTER B1H, C1H, D1H: TPIP ALARM INTERRUPT STATUS

(EXTD=0).........................................................................................256

REGISTER B2H, C2H, D2H: TPIP POINTER INTERRUPT

STATUS ...........................................................................................257

REGISTER B3H, C3H, D3H: TPIP ALARM INTERRUPT ENABLE

(EXTD=0).........................................................................................259

REGISTER B3H, C3H, D3H: TPIP ALARM INTERRUPT ENABLE

(EXTD=1).........................................................................................261

REGISTER B4H, C4H, D4H: TPIP POINTER INTERRUPT

ENABLE...........................................................................................262

REGISTER B5H, C5H, D5H: TPIP POINTER LSB.....................................264

REGISTER B6H, C6H, D6H: TPIP POINTER MSB....................................265

REGISTER B8H, C8H, D8H: TPIP PATH BIP-8 LSB .................................267

REGISTER BCH, CCH, DCH: TPIP TRIBUTARY MULTIFRAME

STATUS AND CONTROL ................................................................268

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE v

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER BDH, CDH, DDH: TPIP BIP CONTROL ..................................270

REGISTER E0H: SPECTRA-155 CLOCK SYNTHESIS SOURCE

SELECT ...........................................................................................272

REGISTER E1H: SPECTRA-155 CLOCK RECOVERY SOURCE

SELECT ...........................................................................................273

REGISTER E3H: SPECTRA-155 TRANSMIT PATH AIS CONTROL

#1 .....................................................................................................274

REGISTER E4H: SPECTRA-155 TRANSMIT PATH AIS CONTROL

#2 .....................................................................................................276

REGISTER E5H: SPECTRA-155 TRANSMIT PATH AIS CONTROL

#3 / AUXILIARY SIGNAL INTERRUPT STATUS..............................278

REGISTER E6H: SPECTRA-155 AUXILIARY SECTION/LINE

INTERRUPT STATUS......................................................................280

REGISTER E7H: SPECTRA-155 AUXILIARY PATH INTERRUPT

STATUS #1 ......................................................................................282

REGISTER E8H: SPECTRA-155 AUXILIARY PATH INTERRUPT

STATUS #2 ......................................................................................284

REGISTER E9H: SPECTRA-155 AUXILIARY PATH INTERRUPT

STATUS #3 ......................................................................................286

REGISTER EAH: SPECTRA-155 AUXILIARY PATH ENHANCED

INTERRUPT STATUS......................................................................288

REGISTER EBH: SPECTRA-155 TRACE MESSAGE MODE 2

INTERRUPT STATUS......................................................................289

REGISTER ECH: SPECTRA-155 TRACE MESSAGE MODE 2

STATUS ...........................................................................................291

REGISTER EDH: SPECTRA-155 AUTO TRACE MESSAGE MODE

1/2 CONTROL .................................................................................292

REGISTER EFH: SPECTRA-155 RECEIVE CONCAT PATH AIS,

RDI AND ENHANCED RDI CONTROL #1......................................294

REGISTER F0H: SPECTRA-155 RECEIVE PATH AIS CONTROL

#2 .....................................................................................................296

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vi

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER F1H: SPECTRA-155 RECEIVE PATH AIS CONTROL

#3 .....................................................................................................299

REGISTER F2H: SPECTRA-155 PATH REI/RDI CONTROL #2................302

REGISTER F3H: SPECTRA-155 PATH REI/RDI CONTROL #3................304

REGISTER F4H: SPECTRA-155 ENHANCED PATH RDI

CONTROL #1...................................................................................306

REGISTER F5H: SPECTRA-155 ENHANCED PATH RDI

CONTROL #2...................................................................................309

REGISTER F6H: SPECTRA-155 ENHANCED PATH RDI

CONTROL #3...................................................................................312

REGISTER F7H: SPECTRA-155 AUXILIARY SECTION/LINE

INTERRUPT ENABLE .....................................................................315

REGISTER F8H: SPECTRA-155 AUXILIARY PATH INTERRUPT

ENABLE #1......................................................................................316

REGISTER F9H: SPECTRA-155 AUXILIARY PATH INTERRUPT

ENABLE #2......................................................................................317

REGISTER FAH: SPECTRA-155 AUXILIARY PATH INTERRUPT

ENABLE #3......................................................................................318

REGISTER FBH: SPECTRA-155 AUXILIARY PATH ENHANCED

INTERRUPT ENABLE .....................................................................319

REGISTER FCH: SPECTRA-155 AUXILIARY PATH STATUS #1..............320

REGISTER FDH: SPECTRA-155 AUXILIARY PATH STATUS #2..............321

REGISTER FEH: SPECTRA-155 AUXILIARY PATH STATUS #3 ..............322

REGISTER 100H: SPECTRA-155 PATH/MAPPER

CONFIGURATION ...........................................................................323

REGISTER 101H: SPECTRA-155 RECEIVE PATH AIS CONTROL

#1 .....................................................................................................325

REGISTER 102H: SPECTRA-155 PATH REI/RDI CONTROL #1 ..............328

REGISTER 103H: SPECTRA-155 PATH/MAPPER INTERRUPT

STATUS ...........................................................................................330

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER 104H: SPECTRA-155 PATH INTERRUPT STATUS #1 ..........331

REGISTER 105H: SPECTRA-155 PATH INTERRUPT STATUS #2 ..........332

REGISTER 106H: SPECTRA-155 PATH TRANSMIT CONTROL..............333

REGISTER 107H: SPECTRA-155 PATH LOOPBACK, ADD BUS

CONTROL .......................................................................................334

REGISTER 108H: SPECTRA-155 SIGNAL ACTIVITY MONITOR.............335

REGISTER 109H: SPECTRA-155 PARITY CONFIGURATION .................337

REGISTER 110H, 150H, 190H: RPOP STATUS AND CONTROL

(EXTD=0).........................................................................................339

REGISTER 110H, 150H, 190H: RPOP STATUS AND CONTROL

(EXTD=1).........................................................................................341

REGISTER 111H, 151H, 191H: RPOP ALARM INTERRUPT

STATUS (EXTD=0) .........................................................................343

REGISTER 111H, 151H, 191H: RPOP ALARM INTERRUPT

STATUS (EXTD=1) .........................................................................344

REGISTER 112H, 152H, 192H: RPOP POINTER INTERRUPT

STATUS ...........................................................................................345

REGISTER 113H, 153H, 193H: RPOP ALARM INTERRUPT

ENABLE (EXTD=0)..........................................................................347

REGISTER 113H, 153H, 193H: RPOP ALARM INTERRUPT

ENABLE (EXTD=1)..........................................................................349

REGISTER 114H, 154H, 194H: RPOP POINTER INTERRUPT

ENABLE...........................................................................................350

REGISTER 115H, 155H, 195H: RPOP POINTER LSB..............................352

REGISTER 116H, 156H, 196H: RPOP POINTER MSB .............................353

REGISTER 117H, 157H, 197H: RPOP PATH SIGNAL LABEL...................355

REGISTER 118H, 158H, 198H: RPOP PATH BIP-8 LSB...........................356

REGISTER 11AH, 15AH, 19AH: RPOP PATH REI LSB.............................357

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE viii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER 11CH, 15CH, 19CH: RPOP TRIBUTARY MULTIFRAME

STATUS AND CONTROL ................................................................358

REGISTER 11DH, 15DH, 19DH: RPOP TANDEM CONNECTION

AND RING CONTROL .....................................................................360

REGISTER 11EH, 15EH, 19EH: RPOP TANDEM CONNECTION

IEC COUNT LSB..............................................................................363

REGISTER 124H, 164H, 1A4H: PMON RECEIVE POSITIVE

POINTER JUSTIFICATION COUNT................................................364

REGISTER 125H, 165H, 1A5H: PMON RECEIVE NEGATIVE

POINTER JUSTIFICATION COUNT................................................365

REGISTER 126H, 166H, 1A6H: PMON TRANSMIT POSITIVE

POINTER JUSTIFICATION COUNT................................................366

REGISTER 127H, 167H, 1A7H: PMON TRANSMIT NEGATIVE

POINTER JUSTIFICATION COUNT................................................367

REGISTER 128H, 168H, 1A8H: RTAL CONTROL .....................................368

REGISTER 129H, 169H, 1A9H: RTAL INTERRUPT STATUS AND

CONTROL .......................................................................................370

REGISTER 12AH, 16AH, 1AAH: RTAL ALARM AND DIAGNOSTIC

CONTROL .......................................................................................373

REGISTER 130H, 170H, 1B0H: TPOP CONTROL ....................................375

REGISTER 131H, 171H, 1B1H: TPOP GENERATED BUS

CONTROL .......................................................................................377

REGISTER 133H, 173H, 1B3H: TPOP CURRENT POINTER LSB ...........380

REGISTER 135H, 175H, 1B5H: TPOP PAYLOAD POINTER LSB ............381

REGISTER 137H, 177H, 1B7H: TPOP PATH TRACE ...............................383

REGISTER 138H, 178H, 1B8H: TPOP PATH SIGNAL LABEL ..................384

REGISTER 139H, 179H, 1B9H: TPOP PATH STATUS..............................385

REGISTER 13AH, 17AH, 1BAH: TPOP PATH USER CHANNEL ..............388

REGISTER 13BH, 17BH, 1BBH: TPOP PATH GROWTH #1 .....................389

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ix

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

REGISTER 13CH, 17CH, 1BCH: TPOP PATH GROWTH #2 ....................390

REGISTER 13DH, 17DH, 1BDH: TPOP TANDEM CONNECTION

MAINTENANCE...............................................................................391

REGISTER 13EH: TPOP CONCATENATION LSB ....................................392

REGISTER 140H, 180H, 1C0H: TTAL CONTROL .....................................394

REGISTER 141H, 181H, 1C1H: TTAL INTERRUPT STATUS AND

CONTROL .......................................................................................396

REGISTER 142H, 182H, 1C2H: TTAL ALARM AND DIAGNOSTIC

CONTROL .......................................................................................399

REGISTER 148H, 188H, 1C8H: SPTB CONTROL ....................................401

REGISTER 149H, 189H, 1C9H: SPTB PATH TRACE IDENTIFIER

STATUS ...........................................................................................403

REGISTER 14AH, 18AH, 1CAH: SPTB INDIRECT ADDRESS

REGISTER.......................................................................................405

REGISTER 14BH, 18BH, 1CBH: SPTB INDIRECT DATA

REGISTER.......................................................................................406

REGISTER 14CH, 18CH, 1CCH: SPTB EXPECTED PATH SIGNAL

LABEL..............................................................................................407

REGISTER 14DH, 18DH, 1CDH: SPTB PATH SIGNAL LABEL

STATUS ...........................................................................................408

REGISTER ADDRESS 200H: SPECTRA-155 MASTER TEST..................413

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE x

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

LIST OF FIGURES

FIGURE 1 - STS-3 (STM-1/AU3), STS-3C (STM-1/AU4)

APPLICATION .........................................................................8

FIGURE 2 - DS3 APPLICATION ...............................................................9

FIGURE 3 - SERIAL HDLC APPLICATION.............................................10

FIGURE 4 - STS-3/STM-1 AGGREGATE/TRIBUTARY/CROSS-

CONNECT APPLICATION.....................................................11

FIGURE 5 - STS-3/STM-1 AGGREGATE/TRIBUTARY/CROSS-

CONNECT CARD..................................................................11

FIGURE 6 - PACKET OVER SONET APPLICATION..............................12

FIGURE 7 - PACKET OVER SONET ROUTER WAN CARD .................12

FIGURE 8 - NORMAL MODE..................................................................13

FIGURE 9 - LOOPBACK MODES...........................................................14

FIGURE 10 - PIN DIAGRAM: BYTE TELECOMBUS MODE

(SMODE[2:0]=000) ................................................................20

FIGURE 11 - PIN DIAGRAM: NIBBLE TELECOMBUS MODE

(SMODE[2:0]=001) ................................................................21

FIGURE 12 - PIN DIAGRAM: SERIAL TELECOMBUS MODE

(SMODE[2:0]=010) ................................................................22

FIGURE 13 - PIN DIAGRAM: BYTE DATA MODE

(SMODE[2:0]=011) ................................................................23

FIGURE 14 - PIN DIAGRAM: NIBBLE DATA MODE

(SMODE[2:0]=100) ................................................................24

FIGURE 15 - PIN DIAGRAM: SERIAL DATA MODE

(SMODE[2:0]=101) ................................................................25

FIGURE 16 - PIN DIAGRAM: SERIAL DS3 MODE

(SMODE[2:0]=110) ................................................................26

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xi

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

FIGURE 17 - SPECTRA-155 TYPICAL JITTER TOLERANCE AT

155 MBIT/S..........................................................................109

FIGURE 18 - POINTER INTERPRETATION STATE DIAGRAM ............. 116

FIGURE 19 - POINTER GENERATION STATE DIAGRAM ....................125

FIGURE 20 - INPUT OBSERVATION CELL (IN_CELL)..........................422

FIGURE 21 - OUTPUT CELL (OUT_CELL) ............................................423

FIGURE 22 - BIDIRECTIONAL CELL (IO_CELL) ...................................423

FIGURE 23 - LAYOUT OF OUTPUT ENABLE AND

BIDIRECTIONAL CELLS.....................................................424

FIGURE 24 - INTERFACING SPECTRA-155 TO ECL OR PECL...........432

FIGURE 25 - SINGLE ENDED DRIVING DIFFERENTIAL

ALOS+/- INPUTS.................................................................433

FIGURE 26 - SINGLE ENDED DRIVING DIFFERENTIAL

RRCLK+/- OR TRCLK+/- INPUTS.......................................434

FIGURE 27 - BOUNDARY SCAN ARCHITECTURE...............................435

FIGURE 28 - TAP CONTROLLER FINITE STATE MACHINE ................437

FIGURE 29 - RECEIVE OVERHEAD CLOCK AND DATA

ALIGNMENT (R64SEL=0)...................................................441

FIGURE 30 - RECEIVE OVERHEAD CLOCK AND DATA

ALIGNMENT (R64SEL=1)...................................................441

FIGURE 31 - RECEIVE SELECTABLE OVERHEAD CLOCK

AND DATA ALIGNMENT (R64SEL=0).................................442

FIGURE 32 - RECEIVE SELECTABLE OVERHEAD CLOCK

AND DATA ALIGNMENT (R64SEL=1).................................443

FIGURE 33 - RECEIVE SECTION/LINE DCC CLOCK AND DATA

ALIGNMENT........................................................................444

FIGURE 34 - RECEIVE LINE DCC CLOCK AND DATA

ALIGNMENT........................................................................445

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

FIGURE 35 - TRANSMIT OVERHEAD CLOCK AND DATA

ALIGNMENT (T64SEL=0) ...................................................446

FIGURE 36 - TRANSMIT OVERHEAD CLOCK AND DATA

ALIGNMENT (T64SEL=1) ...................................................446

FIGURE 37 - TRANSMIT SELECTABLE OVERHEAD CLOCK

AND DATA ALIGNMENT (T64SEL=0) .................................447

FIGURE 38 - TRANSMIT SELECTABLE OVERHEAD CLOCK

AND DATA ALIGNMENT (T64SEL=1) .................................448

FIGURE 39 - TRANSMIT DATA LINK CLOCK AND DATA

ALIGNMENT........................................................................449

FIGURE 40 - TRANSPORT OVERHEAD EXTRACTION (STS-

3/3C)....................................................................................450

FIGURE 41 - TRANSPORT OVERHEAD INSERTION (STS-

3/3C)....................................................................................451

FIGURE 42 - RECEIVE PATH OVERHEAD EXTRACTION

TIMING ................................................................................452

FIGURE 43 - RECEIVE TANDEM CONNECT MAINTENANCE

INSERTION TIMING............................................................453

FIGURE 44 - TRANSMIT PATH OVERHEAD INSERTION

TIMING ................................................................................454

FIGURE 45 - RECEIVE RING CONTROL PORT....................................455

FIGURE 46 - RECEIVE PATH ALARM PORT TIMING ...........................457

FIGURE 47 - TRANSMIT RING CONTROL PORT .................................459

FIGURE 48 - TRANSMIT ALARM PORT TIMING...................................460

FIGURE 49 - STS-1 (STM-0/AU3) BYTE MODE DROP BUS

TIMING ................................................................................461

FIGURE 50 - STS-1 (STM-0/AU3) NIBBLE MODE DROP BUS

TIMING ................................................................................462

FIGURE 51 - STS-1/3 (STM-0/AU3, STM-1/AU3) SERIAL MODE

DROP BUS TIMING.............................................................463

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xiii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

FIGURE 52 - STS-3 (STM-1/AU3) BYTE MODE DROP BUS

TIMING ................................................................................464

FIGURE 53 - STS-3 (STM-1/AU3) NIBBLE MODE DROP BUS

TIMING ................................................................................465

FIGURE 54 - STS-3C (STM-1/AU4) BYTE MODE DROP BUS

TIMING ................................................................................466

FIGURE 55 - STS-3C (STM-1/AU4) NIBBLE MODE DROP BUS

TIMING ................................................................................467

FIGURE 56 - STS-1 (STM-0/AU3) BYTE MODE GENERATED

BUS TIMING........................................................................468

FIGURE 57 - STS-1 (STM-0/AU3) NIBBLE MODE GENERATED

BUS TIMING........................................................................469

FIGURE 58 - STS-3 (STM-1/AU3) BYTE MODE GENERATED

BUS TIMING........................................................................470

FIGURE 59 - STS-3 (STM-1/AU3) NIBBLE MODE GENERATED

BUS TIMING........................................................................471

FIGURE 60 - STS-3C (STM-1/AU4) BYTE MODE GENERATED

BUS TIMING........................................................................472

FIGURE 61 - STS-3C (STM-1/AU4) NIBBLE MODE

GENERATED BUS TIMING.................................................473

FIGURE 62 - STS-1 (STM-0/AU3) BYTE MODE ADD BUS

TIMING ................................................................................474

FIGURE 63 - STS-1 (STM-0/AU3) NIBBLE MODE ADD BUS

TIMING ................................................................................475

FIGURE 64 - STS-1/3 (STM-0/AU3, STM-1/AU3) SERIAL MODE

ADD BUS TIMING ...............................................................476

FIGURE 65 - STS-3 (STM-1/AU3) BYTE MODE ADD BUS

TIMING ................................................................................477

FIGURE 66 - STS-3 (STM-1/AU3) NIBBLE MODE ADD BUS

TIMING ................................................................................478

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xiv

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

FIGURE 67 - STS-3C (STM-1/AU4) BYTE MODE ADD BUS

TIMING ................................................................................479

FIGURE 68 - STS-3C (STM-1/AU4) NIBBLE MODE ADD BUS

TIMING ................................................................................480

FIGURE 69 - STS-1/3C (STM-0/AU3, STM-1/AU4) BYTE DATA

MODE RECEIVE BUS TIMING ...........................................481

FIGURE 70 - STS-1/3C (STM-0/AU3, STM-1/AU4) NIBBLE

DATA MODE RECEIVE BUS TIMING..................................481

FIGURE 71 - STS-1/3 (STM-0/AU3, STM-1/AU3) SERIAL DATA

MODE RECEIVE BUS TIMING ...........................................482

FIGURE 72 - STS-1/3C (STM-0/AU3, STM-1/AU4) BYTE DATA

MODE TRANSMIT BUS TIMING.........................................483

FIGURE 73 - STS-1/3C (STM-0/AU3, STM-1/AU4) NIBBLE

DATA MODE TRANSMIT BUS TIMING...............................483

FIGURE 74 - STS-1/3 (STM-0/AU3, STM-1/AU3) SERIAL DATA

MODE TRANSMIT BUS TIMING.........................................484

FIGURE 75 - STS-1/3 (STM-0/AU3, STM-1/AU3) DS3 MODE

RECEIVE BUS TIMING .......................................................485

FIGURE 76 - STS-1/3 (STM-0/AU3, STM-1/AU3) DS3 MODE

TRANSMIT BUS TIMING.....................................................485

FIGURE 77 - MICROPROCESSOR INTERFACE READ

ACCESS TIMING (INTEL MODE) .......................................493

FIGURE 78 - MICROPROCESSOR INTERFACE READ

ACCESS TIMING (MOTOROLA MODE) .............................494

FIGURE 79 - MICROPROCESSOR INTERFACE WRITE

ACCESS TIMING (INTEL MODE) .......................................497

FIGURE 80 - MICROPROCESSOR INTERFACE WRITE

ACCESS TIMING (MOTOROLA MODE) .............................498

FIGURE 81 RECEIVE LINE INPUT INTERFACE TIMING......................501

FIGURE 82 - RECEIVE LINE OUTPUT TIMING.....................................503

FIGURE 83 - RECEIVE ALARM SIGNAL OUTPUT TIMING ..................504

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xv

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

FIGURE 84 - RECEIVE PATH OVERHEAD AND ALARM PORT

OUTPUT TIMING ................................................................505

FIGURE 85 - RING CONTROL PORT OUTPUT TIMING .......................506

FIGURE 86 - RECEIVE TANDEM CONNECTION INPUT

TIMING. ...............................................................................507

FIGURE 87 - TELECOM DROP BUS (BYTE AND NIBBLE)

INPUT TIMING ....................................................................508

FIGURE 88 - TELECOM DROP BUS (SERIAL) INPUT TIMING ............509

FIGURE 89 - TELECOM DROP BUS (BYTE AND NIBBLE)

OUTPUT TIMING ................................................................510

FIGURE 90 - TELECOM DROP BUS (SERIAL) OUTPUT TIMING ........511

FIGURE 91 - DATA MODE RECEIVE BUS (BYTE AND NIBBLE)

OUTPUT TIMING ................................................................513

FIGURE 92 - DS3 AND DATA MODE RECEIVE BUS (SERIAL)

OUTPUT TIMING ................................................................515

FIGURE 93 - GENERATED BUS INPUT TIMING...................................516

FIGURE 94 - GENERATED BUS (BYTE AND NIBBLE) OUTPUT

TIMING ................................................................................517

FIGURE 95 - TELECOM ADD BUS (BYTE AND NIBBLE) INPUT

TIMING ................................................................................519

FIGURE 96 - TELECOM ADD BUS (SERIAL) INPUT TIMING ...............520

FIGURE 97 - DATA MODE TRANSMIT BUS (BYTE AND

NIBBLE) INPUT TIMING......................................................521

FIGURE 98 - DATA MODE TRANSMIT BUS NIBBLE OUTPUT

TIMING ................................................................................522

FIGURE 99 - DS3 AND DATA MODE TRANSMIT BUS (SERIAL)

INPUT TIMING ....................................................................523

FIGURE 100 - TRANSMIT PATH OVERHEAD INPUT TIMING................524

FIGURE 101 - TRANSMIT ALARM PORT INPUT TIMING .......................525

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xvi

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

FIGURE 102 - TRANSMIT TRANSPORT OVERHEAD INPUT

TIMING ................................................................................527

FIGURE 103 - TRANSMIT RING CONTROL PORT INPUT

TIMING ................................................................................528

FIGURE 104 - TRANSMIT OVERHEAD OUTPUT TIMING ......................529

FIGURE 105 - LINE SIDE TRANSMIT INTERFACE TIMING ...................530

FIGURE 106 - JTAG PORT INTERFACE TIMING ....................................531

FIGURE 107 - 256 PIN SUPER BALL GRID ARRAY (B SUFFIX): ...........534

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xvii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

LIST OF TABLES

TABLE 1 - SYSTEM SIDE MODES AND SS[34:0] BUS

MAPPINGS............................................................................15

TABLE 2 - LINE SIDE INTERFACE SIGNALS (20) ..............................27

TABLE 3 - SECTION AND LINE STATUS/OVERHEAD

INTERFACE SIGNALS (36)...................................................32

TABLE 4 - PATH STATUS/OVERHEAD INTERFACE

SIGNALS (37)........................................................................47

TABLE 5 - SYSTEM SIDE INTERFACE SIGNALS (38) .......................59

TABLE 6 - BYTE TELECOMBUS MODE (SMODE[2:0]=000) ..............62

TABLE 7 - NIBBLE TELECOMBUS MODE (SMODE[2:0]=001)...........69

TABLE 8 - SERIAL TELECOMBUS MODE (SMODE[2:0]=010)...........76

TABLE 9 - BYTE DATA MODE (SMODE[2:0]=011) ..............................83

TABLE 10 - NIBBLE DATA MODE (SMODE[2:0]=100) ..........................87

TABLE 11 - SERIAL DATA MODE (SMODE[2:0]=101) ..........................91

TABLE 12 - SERIAL DS3 MODE (SMODE[2:0]=110) .............................95

TABLE 13 - MICROPROCESSOR INTERFACE SIGNALS (25).............98

TABLE 14 - MISCELLANEOUS INTERFACE SIGNALS (11) ...............100

TABLE 15 - POWER SIGNALS (89).....................................................102

TABLE 16 - PATH SIGNAL LABEL MATCH/MISMATCH STATE

TABLE. ................................................................................122

TABLE 17 - ASYNCHRONOUS DS3 MAPPING TO STS-1

(STM-0/AU3)........................................................................127

TABLE 18 - DS3 AIS FORMAT. ............................................................128

TABLE 19 - DS3 DESYNCHRONIZER CLOCK GAPPING

ALGORITHM. ......................................................................130

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xviii

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

TABLE 20 - DS3 SYNCHRONIZER BIT STUFFING

ALGORITHM. ......................................................................131

TABLE 21 - SYSTEM SIDE ADD BUS CONFIGURATION

OPTIONS ............................................................................141

TABLE 22 - SYSTEM SIDE DROP BUS CONFIGURATION

OPTIONS ............................................................................141

TABLE 23 - NORMAL MODE REGISTER MEMORY MAP...................144

TABLE 24 - RECEIVE SONET/SDH MODE SETTING. ........................153

TABLE 25 - TRANSMIT SONET/SDH MODE SETTING. .....................154

TABLE 26 - TRANSPORT OVERHEAD NATIONAL AND

UNUSED BYTES.................................................................186

TABLE 27 - ROHSEL[2:0] CODEPOINTS. ...........................................232

TABLE 28 - TOHSEL[2:0] CODEPOINTS.............................................234

TABLE 29 - RXSEL[1:0] CODEPOINTS FOR STS-1 #2. .....................298

TABLE 30 - RXSEL[1:0] CODEPOINTS FOR STS-1 #3. .....................301

TABLE 31 - RXSEL[1:0] CODEPOINTS FOR STS-1 #1 AND

STS-3C................................................................................327

TABLE 32 - RECEIVE ESD[1:0] CODEPOINTS...................................371

TABLE 33 - TRANSMIT ESD[1:0] CODEPOINTS. ...............................397

TABLE 34 - TEST MODE REGISTER ADDRESS MAP. .......................410

TABLE 35 - TEST MODE 0 PRIMARY INPUT READ

REGISTERS. .......................................................................414

TABLE 36 - TEST MODE 0 PRIMARY OUTPUT WRITE

REGISTERS. .......................................................................416

TABLE 37 - JTAG INSTRUCTION REGISTER LENGTH - 3

BITS.....................................................................................418

TABLE 38 - BOUNDARY SCAN REGISTER. .......................................419

TABLE 39 - RASE-BERM CONFIGURATION FOR SDH STM-0..........429

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xix

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

TABLE 40 - RASE-BERM CONFIGURATION FOR SDH STM-1..........429

TABLE 41 - RASE-BERM CONFIGURATION FOR SONET

STS-1 ..................................................................................430

TABLE 42 - RASE-BERM CONFIGURATION FOR SONET

STS-3 ..................................................................................430

TABLE 43 - D.C. CHARACTERISTICS. ...............................................487

TABLE 44 - MICROPROCESSOR INTERFACE READ

ACCESS..............................................................................492

TABLE 45 - MICROPROCESSOR INTERFACE WRITE

ACCESS..............................................................................496

TABLE 46 - RECEIVE LINE INPUT INTERFACE TIMING....................500

TABLE 47 - RECEIVE LINE OUTPUT TIMING.....................................502

TABLE 48 - RECEIVE ALARM SIGNAL OUTPUT TIMING ..................504

TABLE 49 - RECEIVE PATH OVERHEAD AND ALARM PORT

OUTPUT TIMING ................................................................505

TABLE 50 - RECEIVE RING CONTROL PORT OUTPUT

TIMING ................................................................................506

TABLE 51 - RECEIVE TANDEM CONNECTION INPUT TIMING.........507

TABLE 52 - TELECOM DROP BUS (BYTE AND NIBBLE)

INPUT TIMING ....................................................................508

TABLE 53 - TELECOM DROP BUS (SERIAL) INPUT TIMING ............509

TABLE 54 - TELECOM DROP BUS (BYTE AND NIBBLE)

OUTPUT TIMING ................................................................510

TABLE 55 - TELECOM DROP BUS (SERIAL) OUTPUT TIMING ........511

TABLE 56 - DATA MODE RECEIVE BUS (BYTE AND NIBBLE)

OUTPUT TIMING ................................................................512

TABLE 57 - DS3 RECEIVE BUS INPUT TIMING .................................514

TABLE 58 - DS3 AND DATA MODE RECEIVE BUS (SERIAL)

OUTPUT TIMING ................................................................515

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xx

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

TABLE 59 - GENERATED BUS INPUT TIMING ...................................516

TABLE 60 - GENERATED BUS (BYTE AND NIBBLE) OUTPUT

TIMING ................................................................................517

TABLE 61 - TELECOM ADD BUS (BYTE AND NIBBLE) INPUT

TIMING ................................................................................518

TABLE 62 - TELECOM ADD BUS (SERIAL) INPUT TIMING ...............520

TABLE 63 - DATA MODE TRANSMIT BUS (BYTE AND

NIBBLE) INPUT TIMING......................................................521

TABLE 64 - DATA MODE TRANSMIT BUS NIBBLE OUTPUT

TIMING ................................................................................522

TABLE 65 - DS3 AND DATA MODE TRANSMIT BUS (SERIAL)

INPUT TIMING ....................................................................523

TABLE 66 - TRANSMIT PATH OVERHEAD INPUT TIMING................524

TABLE 67 - TRANSMIT ALARM PORT INPUT TIMING .......................525

TABLE 68 - TRANSMIT TRANSPORT OVERHEAD INPUT

TIMING ................................................................................526

TABLE 69 - TRANSMIT RING CONTROL PORT INPUT

TIMING ................................................................................528

TABLE 70 - TRANSMIT OVERHEAD OUTPUT TIMING ......................529

TABLE 71 - LINE SIDE TRANSMIT INTERFACE TIMING ...................530

TABLE 72 - JTAG PORT INTERFACE..................................................531

TABLE 73 - ORDERING INFORMATION. ............................................533

TABLE 74 - THERMAL INFORMATION................................................533

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE xxi

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

1 FEATURES

• Monolithic SONET/SDH PAYLOAD EXTRACTOR/ALIGNER for use in STS-1

(STM-0/AU3), STS-3 (STM-1/AU3) or STS-3c (STM-1/AU4) interface

applications, operating at serial interface speeds of up to 155.52 Mbit/s.

• Provides integrated clock recovery and clock synthesis to allow a direct

interface to optical modules.

• Provides termination for SONET Section and Line, SDH Regenerator Section

and Multiplexer Section transport overhead, and path overhead of one or

three STS-1 (STM-0/AU3) paths or a single STS-3c (STM-1/AU4) path.

• Maps one or three STS-1 (STM-0/AU3) payloads or a single STS-3c

(STM-1/AU4) payload to system timing reference, accommodating

plesiochronous timing offsets between the references through pointer

processing.

• Maps a DS3 bit stream into a STS-1 (STM-0/AU3) frame or three DS3 bit

streams into a STS-3 (STM-1/AU3) frame.

• Provides clear-channel mapping of three 49.536 Mbit/s or 48.384 Mbit/s

arbitrary data streams into an STS-3 (STM-1/AU3) frame or a single arbitrary

data stream into an STS-1 (STM-0/AU3) frame. Provides clear-channel

mapping of a single 149.76 Mbit/s arbitrary data stream into an STS-3c

(STM-1/AU4) frame.

• Provides versatile datamode interface and optional x^43+1 payload

scrambling/descrambling to support Packet Over SONET applications.

• Supports line loopback from the line side receive stream to the transmit

stream and diagnostic loopback from a Telecom ADD bus interface to a

Telecom DROP bus interface.

• Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

test purposes.

• Provides a generic 8-bit microprocessor bus interface for configuration,

control, and status monitoring.

• Low power +5 Volt CMOS. Device has PECL and TTL compatible inputs and

TTL outputs.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 1

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

• 256 pin Super BGA package. Supports Industrial Temperature Range (-40°C

to 85°C) operation.

1.1 SONET Section and Line / SDH Regenerator and Multiplexer Section

• Frames to the STS-1 (STM-0/AU3) or STS-3/3c (STM-1/AU3/AU4) receive

stream and inserts the framing bytes (A1, A2) and the STS identification byte

(J0) into the transmit stream; descrambles the receive stream and scrambles

the transmit stream.

• Calculates and compares the bit interleaved parity (BIP) error detection codes

(B1, B2) for the receive stream and calculates and inserts B1 and B2 in the

transmit stream; accumulates near end errors (B1, B2) and far end errors

(M1) and inserts line remote error indications (REI) into the Z2 (M1) growth

byte based on received B2 errors.

• Detects signal degrade (SD) and signal fail (SF) threshold crossing alarms

based on received B2 errors.

• Extracts and serializes the order wire channels (E1, E2), the data

communication channels (D1-D3, D4-D12) and the section user channel (F1)

from the receive stream, and inserts the corresponding signals into the

transmit stream.

• Extracts and serializes the automatic protection switch (APS) channel (K1,

K2) bytes, filtering and extracting them into internal registers for the receive

stream. Inserts the APS channel into the transmit stream.

• Extracts and filters the synchronization status message (Z1/S1) byte into an

internal register for the receive stream. Inserts the synchronization status

message (Z1/S1) byte into the transmit stream.

• Extracts a 64 byte or 16 byte section trace (J0) message using an internal

register bank for the receive stream. Detects an unstable section trace

message or mismatch with an expected message, and optionally inserts Line

and Path AIS on the system DROP side upon either of these conditions.

Inserts a 64 byte or 16 byte section trace (J0) message using an internal

register bank for the transmit stream.

• Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line

remote defect indication (RDI), line alarm indication signal (AIS), and

protection switching byte failure alarms on the receive stream. Optionally

returns line RDI in the transmit stream.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 2

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

• Provides a transmit and receive ring control port, allowing alarm and

maintenance signal control and status to be passed between mate

SPECTRA-155s for ring-based add drop multiplexer and line multiplexer

applications.

• Configurable to force Line AIS in the transmit stream.

1.2 SONET Path / SDH High Order Path

• Accepts a multiplex of three STS-1 (STM-0/AU3) streams or a single STS-3c

(STM-1/AU4) stream, interprets the STS (AU) pointer bytes (H1, H2, and H3),

extracts the synchronous payload envelope(s) and processes the path

overhead for the receive stream.

• Constructs a byte serial multiplex of three STS-1 (STM-0/AU3) streams or an

STS-3c (STM-1/AU4) stream on the transmit side.

• Detects loss of pointer (LOP), loss of tributary multiframe (LOM), path alarm

indication signal (PAIS) and path (auxiliary and enhanced) remote defect

indication (RDI) for the receive stream. Optionally inserts path alarm

indication signal (PAIS), path remote defect indication (RDI) and path remote

anomaly indication (RAI) in the transmit stream.

• Extracts and serializes the entire path overhead from the three STS-1

(STM-0/AU3) or the single STS-3c (STM-1/AU4) receive streams. Inserts the

path overhead bytes in the three STS-1 (STM-0/AU3) or single STS-3c

(STM-1/AU4) stream for the transmit stream. The path overhead bytes may

be sourced from internal registers or from bit serial path overhead input

streams. Path overhead insertion may also be disabled.

• Extracts the received path signal label (C2) byte into an internal register and

detects for path signal label unstable and for signal label mismatch with the

expected signal label that is downloaded by the microprocessor. Inserts the

path signal label (C2) byte from an internal register for the transmit stream.

• Extracts a 64 byte or 16 byte path trace (J1) message using an internal

register bank for the receive stream. Detects an unstable path trace message

or mismatch with an expected message, and inserts Path RAI upon either of

these conditions. Inserts a 64 byte or 16 byte path trace (J1) message using

an internal register bank for the transmit stream.

• Detects received path BIP-8 and counts received path BIP-8 errors for

performance monitoring purposes. BIP-8 errors are selectable to be treated

on a bit basis or block basis. Optionally calculates and inserts path BIP-8

error detection codes for the transmit stream.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 3

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

• Counts received path remote error indications (REIs) for performance

monitoring purposes. Optionally inserts the path REI count into the path

status byte (G1) basis on bit or block BIP-8 errors detected in the receive

path. Reporting of BIP-8 errors is on a bit or block bases independent of the

accumulation of BIP-8 errors.

• Supports tandem connection origination applications by sourcing a new

tandem path maintenance byte (Z5) reporting the received BIP-8 errors and

the data link message and correcting subsequent path BIP-8 bytes (B3) to

reflect the change in Z5.

• Supports tandem connection termination applications by accumulating the

incoming error count (IEC) and extracting the tandem connection data link

carried in the tandem path maintenance byte (Z5).

• Maintains existing pointer value during incoming signal failures in tandem

path terminating mode.

• Maintains the existing tributary multiframe sequence on the H4 byte until a

new phase alignment has been verified.

• Provides a serial alarm port communication of path REI and path RDI alarms

to the transmit stream of a mate SPECTRA-155 in the returning direction.

1.3 System Side Interfaces

• Supports Telecombus interfaces by indicating/accepting the location of the

STS identification byte (C1), optionally the path trace byte(s) (J1), optionally

the first tributary overhead byte(s) (V1), and all synchronous payload

envelope bytes in the byte serial stream.

• Supports serial and nibble "Telecombus" interfaces by indicating/accepting

the location of the STS identification byte (C1), the path trace byte(s) (J1),

optionally the first tributary overhead byte(s) (V1), and all synchronous

payload envelope bytes in the stream.

• For Telecombus interfaces, accommodates phase and frequency differences

between the receive/transmit streams and the DROP/ADD busses via pointer

adjustments.

• Supports serial, nibble and byte data mode interfaces by sourcing the

appropriate clock.

• For data mode interfaces, optionally applies a X

43

+1 scrambler/descrambler

to the stream.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 4

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

• Supports a bit serial DS3 data interface for mapping into and out of STS-1

(STM-0/AU3) or STS-3 (STM-1/AU3) SPEs.

• For the DS3 interface, provides optional insertion of framed DS3 AIS in both

the ADD and DROP directions.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 5

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

2 APPLICATIONS

• SONET/SDH Add Drop Multiplexers

• SONET/SDH Terminal Multiplexers

• SONET/SDH Line Multiplexers

• SONET/SDH Cross Connects

• SONET/SDH Tandem Path Termination Equipment

• SONET/SDH Test Equipment

• Switches and Hubs

• Routers

3 REFERENCES

• American National Standard for Telecommunications - Digital Hierarchy -

Optical Interface Rates and Formats Specification, ANSI T1.105-1991.

• American National Standard for Telecommunications - Layer 1 In-Service

Digital Transmission Performance Monitoring, T1X1.3/93-005R1, April 1993.

• American National Standard for Telecommunications – Synchronous Optical

Network (SONET) – Tandem Connection Maintenance, ANSI T1.105.05-

1994.

• Committee T1 Contribution, "Draft of T1.105 - SONET Rates and Formats",

T1X1.5/94-033R2-1994.

• Bell Communications Research - SONET Transport Systems: Common

Generic Criteria, GR-253-CORE Issue 2, December 1995.

• ETS 300 417-1-1, "Generic Functional Requirements for Synchronous Digital

Hierarchy (SDH) Equipment", January, 1996.

• ITU, Recommendation G.707 - "Network Node Interface For The

Synchronous Digital Hierarchy", 1996.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 6

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

• ITU Recommendation G.781, - “Structure of Recommendations on Equipment

for the Synchronous Digital Hierarchy (SDH)”, January, 1994.

• ITU Recommendation G.783, “Characteristics of Synchronous Digital

Hierarchy (SDH) Equipment Functional Blocks”, 28 October, 1996.

• ITU Recommendation O.151, “Error Performance measuring Equipment

Operating at the Primary Rate and Above”, October, 1992.

• ITU Study Group XVII - Contribution D2166 - "Tandem Connection / Tandem

Connection Bundle Maintenance - Working Solution", June 1992.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 7

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

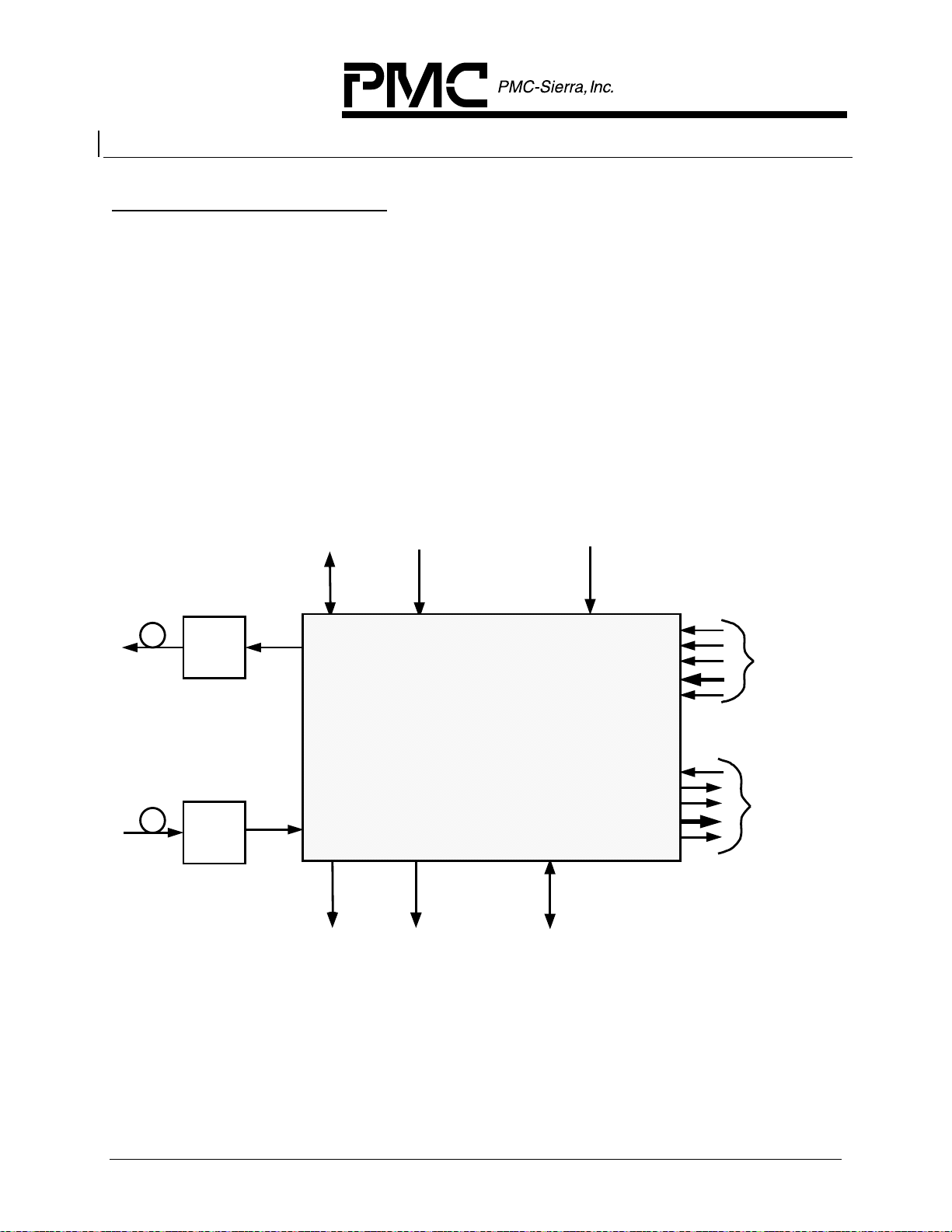

4 APPLICATION EXAMPLE

The SPECTRA-155 is used to implement an STS-1 (STM-0/AU3), STS-3

(STM-1/AU3) or STS-3c (STM-1/AU4) line Interface. The SPECTRA-155 may

find application in many different types of SONET/SDH network elements

including switches, terminal multiplexers, and add-drop multiplexers. In such

applications, on the line side the SPECTRA-155 typically interfaces directly to

electrical optical modules. On the system side, the SPECTRA-155 can directly

interface to an Telecombus, a DS3 signal source or a data source (i.e. HDLC

controller).

Figure 1 - STS-3 (STM-1/AU3), STS-3c (STM-1/AU4) Application

TRANSMIT

TRANSPORT

AND PATH

OVERHEAD

ACCESS

TRANSMIT SECTION,

LINE, PATH ALARM

INSERT SIGNALS

SMODE[2:0]="000"

E/O

O/E

TXD+/-

RXD+/-

RECEIVE

TRANSPORT

AND PATH

OVERHEAD

ACCESS

PM5342

SPECTRA-155

RECEIVE

SECTION, LINE,

PATH ALARM

DETECT SIGNALS

MICRO BUS

FOR CONFIG,

STATUS

AND CONTROL

ACK

AC1J1V1

APL

AD[7:0]

ADP

DCK

DC1J1V1

DPL

DD[7:0]

DDP

Telecombus

Add

Interface

Telecombus

Drop

Interface to

PM5362,

TUPP-PLUS

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 8

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

Figure 2 - DS3 Application

TRANSMIT

TRANSPORT

AND PATH

OVERHEAD

ACCESS

TRANSMIT SECTION,

LINE, PATH ALARM

INSERT SIGNALS

SMODE[2:0]="110"

44.736 MHz*

E/O

O/E

TXD+/-

RXD+/-

RECEIVE

TRANSPORT

AND PATH

OVERHEAD

ACCESS

PM5342

SPECTRA-155

RECEIVE

SECTION, LINE,

PATH ALARM

DETECT SIGNALS

DS3TICLK[3:1]

DS3TDAT[3:1]

DS3ROCLK[3:1]

DS3RDAT[3:1]

DS3RICLK[3:1]

MICRO BUS

FOR CONFIG,

STATUS

AND CONTROL

TICLK

TCLK

TDAT

3 * PM7345 SUNI-PDH

3 * PM8313 D3MX

RCLK

RDAT

44.928 MHz

* For the PM7345, the 44.736

MHz clock can be fed

directly to the DS3TICLK input

or

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 9

PM5342 SPECTRA-155

A

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

Figure 3 - Serial HDLC Application

TRANSMIT

TRANSPORT

AND PATH

OVERHEAD

ACCESS

TRA NSMIT SECTIO N,

LINE, PATH ALARM

INSERT SIGNALS

SMODE[2:0]="101"

E/O

O/E

TXD+/-

RXD+/-

RECEIVE

TRANSPORT

AND PATH

OVERHEAD

CCESS

PM5342

SPECTRA-155

RECEIVE

SEC TION, L INE,

PATH ALARM

DETECT SIGNALS

SDM TOCL K[3:1]

SDM TICLK [3:1]

SDMTDAT[3:1]

SDM ROCL K[3:1]

SDMRDAT[3:1]

MICRO BUS

FOR CONFIG,

STATUS

AND CONTROL

TCLK[0]

TDA T[0]

3 * PM7364 FREEDM

RCLK[0]

RDAT[0]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 10

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

Figure 4 - STS-3/STM-1 Aggregate/Tributary/Cross-Connect Application

TRANSMIT

TRANSPORT A ND

PATH OVERHE AD

ACCESS

TRANSMIT

SECTION, LINE

PATH ALARM

INSERT SIGNALS

SMODE[2:0]="000"

8 BIT

TELECOMBUS

INTERFACE

19.44 CLK REF

OPT. TX

OPT. RX

19.44 CLK REF

TRCLK+/-

TXD+ /-

RXD+/-

RRCLK+/-

RECEIVE

TRANSPORT A ND

PATH OVERHE AD

ACCESS

PM5342

SPECTRA-155

RECEIVE

SECTION, LINE

PATH ALARM

DETECT SIGNALS

ACK

AD[7:0 ], ADP

AC1J1

APL

DD[7:0], DDP

DC1J1

DPL

DCK

MICROBUS

FOR CONFIG,

STATUS

AND CONTROL

TUPP-PLUS

ID[7:0 ], IDP

IC1J 1

IPL

SCLK

PM5362

OD[7 :0], ODP

OTV5

OTPL

TPOH

Figure 5 - STS-3/STM-1 Aggregate/Tributary/Cross-Connect Card

PM5342

SPECTRA-155

PM5362

TUPP

Plus

PM5371

TUDX

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 11

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

Figure 6 - Packet Over SONET Application

19.44 CLK REF

OPT. TX

OPT. RX

19.44 CLK REF

TRANSMIT

TRANSPORT AND

PATH OVERHEAD

ACCESS

TRCLK+/-

TXD+/-

RXD+/-

RRCLK+/-

RECEIVE

TRANSPORT AND

PATH OVERHEAD

ACCESS

TRANSMIT

SECTION, LINE

PATH ALARM

INSERT SIGNALS

PM5342

SPECTRA-155

RECEIVE

SECTION, LINE

PATH ALARM

DETECT SIGNALS

SMODE[2:0]="011"

DMTOCLK

DMTICLK

DMTDAT[7::0]

DMROC LK

DMRDAT[7:0]

MICROBUS

FOR CONFIG,

STATUS

AND CONTROL

TCLKI

TDATO [7:0]

RCLKI

RDATI[7:0]

Figure 7 - Packet Over SONET Router WAN Card

TDAT[ 15:0]

Packet

Over

SONET

HDLC

Processor

RDAT[15:0]

INTERFACE

INTERFACE)

TFCLK

TENB

TDA

TSOP

TPRTY

TMOD

TEOP

TERR

RFCLK

RENB

RDA

RSOP

RPRTY

RMOD

REOP

RERR

PACKET

OVER

SONET

(TO BUS

PM534 2

SAR

SPECTR A-155

Packet Over

SONET HDLC

Processor

BUS

Interface

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 12

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

5 BLOCK DIAGRAM

Figure 8 - NORMAL MODE

TLRDI/TRCPFP

RLAIS/TRCPCLK

TLAIS/TRCPDAT

TSLDCLK, TOWCLK

TSLD, TSOW, TSUC

TLD, TLOW, TOH

TLDCLK, TOHCLK

TTOH

TTOHFP

TTOHCLK

TTOHEN

TCLK, TFP

TPOH[3:1]

TPOHFP[3:1]

TPOHCLK[3:1]

TPOHEN[3:1]

TAD, TAFP, TACK

SCPO[1:0]

SCPI[1:0]

TDO

TDI

TCK

TMS

TRSTB

TRCLK+

TRCLK-

TXC

TXD+

TXD-

TBYP

TATP

RATP

RBYP

RXD-

RXD+

RRCLK+

RRCLK-

ALOS+

ALOS-

Tx Line

I/F

Rx Line

I/F

C1, C2

Tx Ring

Control Port

Clock

Synthesis

(CSPI)

Clock and

Data

Recovery

(CRSI)

Rx Ring

Control Port

LOS/RRCPFP

LAIS/RRCPDAT

LRDI/RRCPCLK

Tx

Section O/H

Processor

(TSOP)

Section

Trace

Buffer

(SSTB)

Rx

Section O/H

Processor

(RSOP)

LOF, SALM

RSLDCLK,ROWCLK

RSLD, RSOW, RSUC

Path

Trace

RPOHCLK[3:1]

RALM[3:1]

RTCEN[3:1]

Serial

Control

Port

Path

Trace

Buffer #3

(SPTB #3)

RTCOH[3:1]

JTAG Test

Access Port

Tx Telecom

Aligner #1

(TTAL #1)

Tx Telecom

Aligner #2

(TTAL #2)

Tx Telecom

Aligner #3

(TTAL #3)

Rx Telecom

Aligner #1

(RTAL #1)

Rx Telecom

Aligner #2

(RTAL #2)

Rx Telecom

Aligner #3

(RTAL #3)

Microprocessor

RAD

D[7:0]

B3E[3:1]

3

ADD Bus

PRBS

Generator/

3

3

3

3

3

3

I/F

ALE

CSB

INTB

RSTB

A[7:0]

MBEB

RDB/E

WRB/RWB

Monitor

DS3 Mapper

Add Side #1

(D3MA #1)

DS3 Mapper

Add Side #2

(D3MA #2)

DS3 Mapper

Add Side #3

(D3MA #3)

Tx Pointer

Interpreter #1

(TPIP #1)

Tx Pointer

Interpreter #2

(TPIP #2)

Tx Pointer

Interpreter #3

(TPIP #3)

DROP Bus

PRBS

Generator/

Monitor

DS3 Mapper

Add Side #1

(D3MA #1)

DS3 Mapper

Add Side #2

(D3MA #2)

DS3 Mapper

Add Side #3

(D3MA #3)

System

Side

I/F

SMODE[2:0]

SS[34:0]

Transport

O/H

Insert

Tx Path O/H

Processor #1

Path

Trace

Buffer #1

(SPTB #1)

RXC, RCLK, RFP

(TPOP #1)

Tx Path O/H

Processor #2

(TPOP #2)

Tx Path O/H

Processor #3

(TPOP #3)

Buffer #2

(SPTB #2)

Rx Path O/H

Processor #1

(RPOP #1)

Rx Path O/H

Processor #2

(RPOP #2)

Rx Path O/H

Processor #3

(RPOP #3)

RPOH[3:1]

RPOHFP[3:1]

Tx

Line O/H

Processor

(TLOP)

Rx

Line O/H

Processor

(RLOP)

Transport

O/H

Extract

RTOH

RTOHFP

TRIS_OHB

RLDCLK, ROHCLK

RTOHCLK

RLD, RLOW, ROH

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 13

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

Figure 9 - LOOPBACK MODES

LINE

LOOPBACK

(LLE=1)

Tx Line

I/F

Rx Line

I/F

Tx Ring

Control Port

Clock

Synthesis

(CSPI)

Clock and

Data

Recovery

(CRSI)

Rx Ring

Control Port

Tx

Section O/H

Processor

(TSOP)

Section

DIAGNOSTIC

Trace

LOOPBACK

Buffer

(SSTB)

(DLE=1)

Rx

Section O/H

Processor

(RSOP)

Tx

Line O/H

Processor

(TLOP)

Rx

Line O/H

Processor

(RLOP)

Transport

O/H

Insert

Transport

O/H

Extract

Path

Trace

Buffer #1

(SPTB #1)

Tx Path O/H

Processor #1

(TPOP #1)

Tx Path O/H

Processor #2

(TPOP #2)

Tx Path O/H

Processor #3

(TPOP #3)

Path

SYSTEM SIDE

Trace

LINE LOOPBACK

Buffer #2

Buffer #3

(SPTB #2)

(SPTB #3)

Rx Path O/H

Processor #1

(RPOP #1)

Rx Path O/H

Processor #2

(RPOP #2)

Rx Path O/H

Processor #3

(RPOP #3)

Serial

Control

Path

Trace

(SLLBEN=1)

Port

JTAG Test

Access Port

Tx Telecom

Aligner #1

(TTAL #1)

Tx Telecom

Aligner #2

(TTAL #2)

Tx Telecom

Aligner #3

(TTAL #3)

Rx Telecom

Aligner #1

(RTAL #1)

Rx Telecom

Aligner #2

(RTAL #2)

Rx Telecom

Aligner #3

(RTAL #3)

Microprocessor

I/F

3

ADD Bus

PRBS

Generator/

3

Monitor

DS3 Mapper

Add Side #1

(D3MA #1)

DS3 Mapper

Add Side #2

(D3MA #2)

3

DS3 Mapper

Add Side #3

(D3MA #3)

Tx Pointer

Interpreter #1

(TPIP #1)

Tx Pointer

Interpreter #2

(TPIP #2)

3

Tx Pointer

Interpreter #3

(TPIP #3)

3

DROP Bus

PRBS

Generator/

3

Monitor

DS3 Mapper

Add Side #1

(D3MA #1)

DS3 Mapper

Add Side #2

(D3MA #2)

3

DS3 Mapper

Add Side #3

(D3MA #3)

System

Side

I/F

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 14

PM5342 SPECTRA-155

]

]

]DD[0]

]

]

]DD[1]

]

]

]DD[2]

]

]DD[3]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]AD[0]

]

]

]AD[1]

]

]

]AD[2]

]

]AD[3]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]

]GD[0]

]

]GD[1]

]

]

]

]

]

]

]

]

]

]

]

]

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

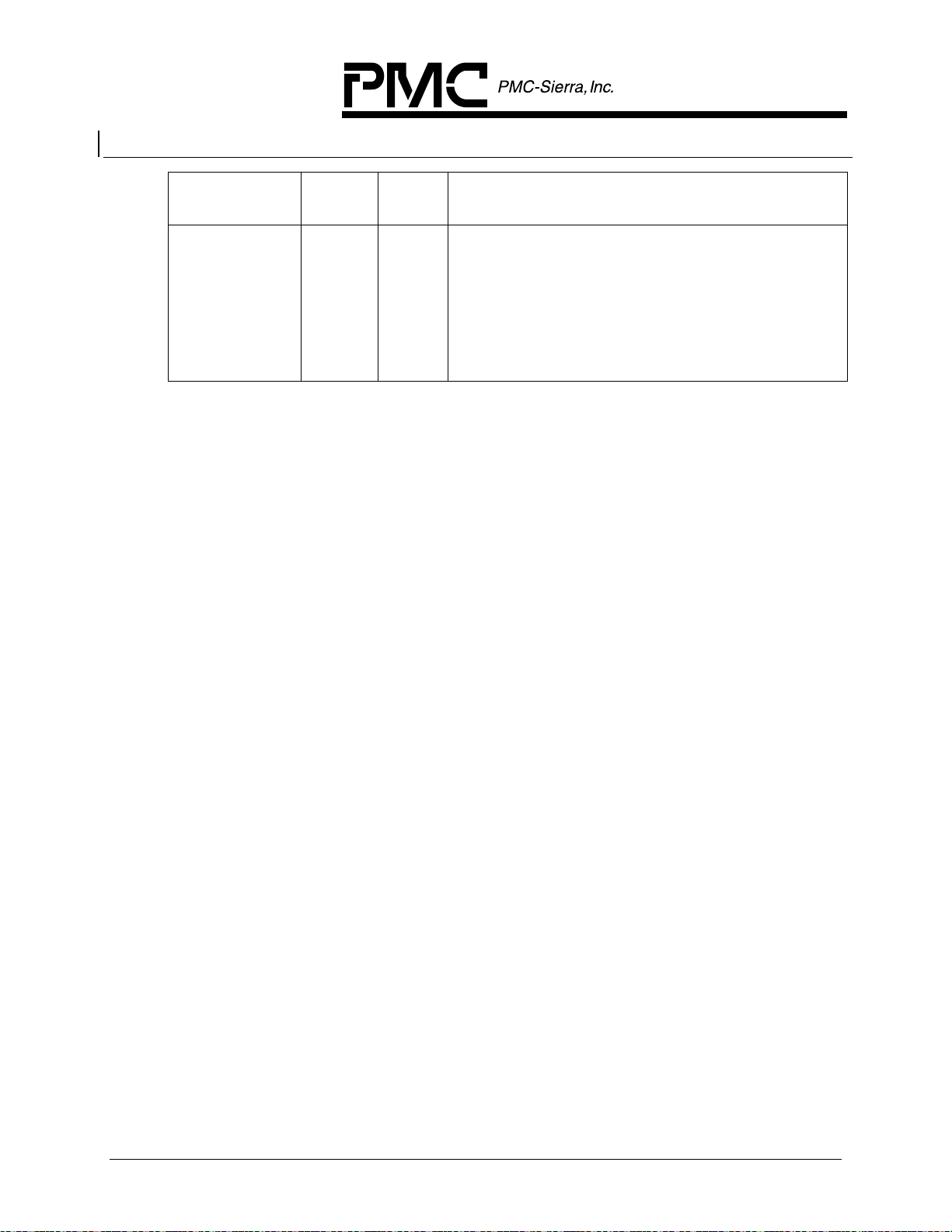

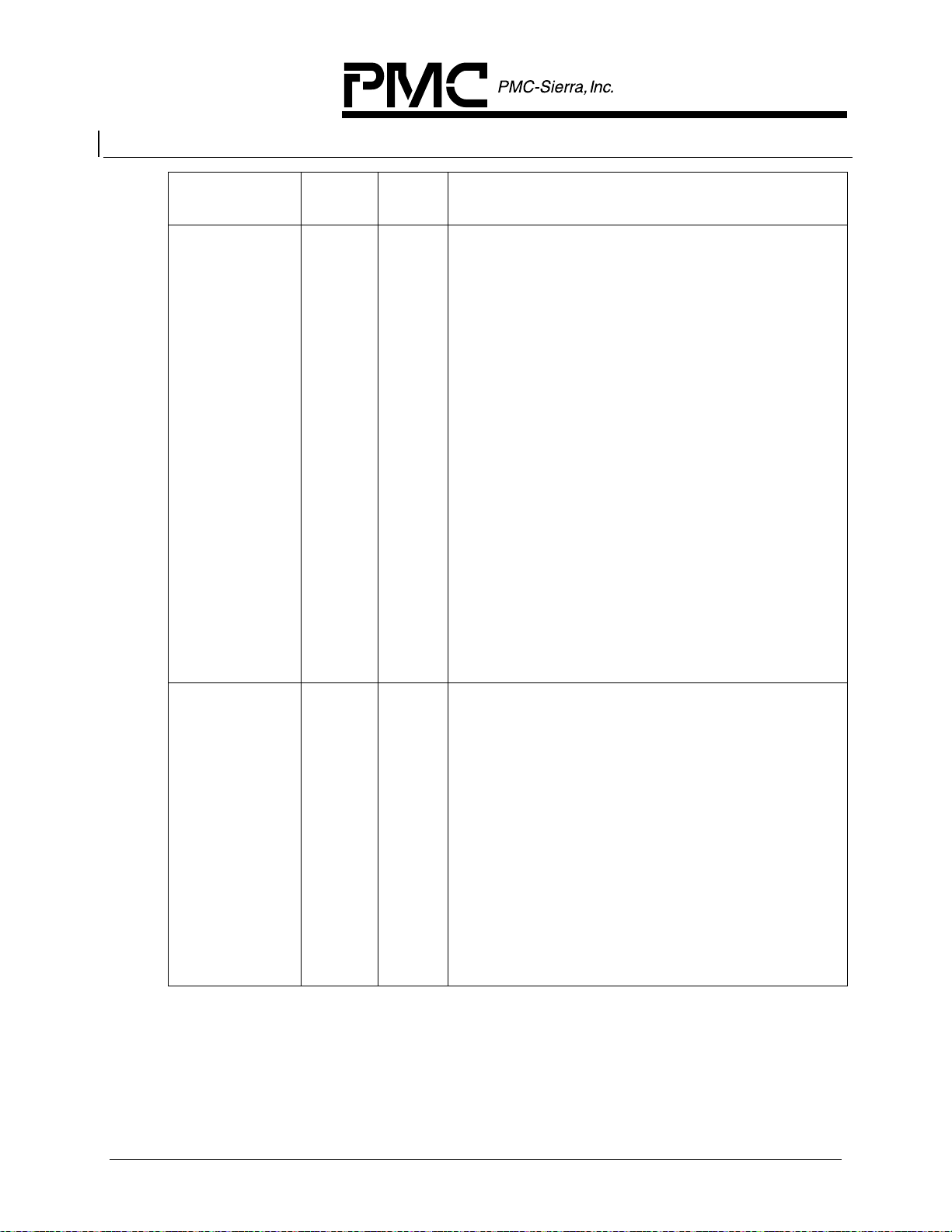

Table 1 - System side modes and SS[34:0] bus mappings.

Signal Byte

Telecombus

Mode

SMODE=000 SMODE=001 SMODE=010 SMODE=011 SMODE=100 SMODE=101 SMODE=110

SS[0]DCK DCK SDCK[1

SS[1]DFP DFP Res. Input Res. Input Res. Input Res. Input Res. Input

SS[2]DD[0

SS[3]DD[1

SS[4]DD[2

SS[5]DD[3

SS[6]DD[4

SS[7]DD[5

SS[8]DD[6

SS[9]DD[7

SS[10]DPL DPL SDPL[1

SS[11]DC1J1V1 DC1J1V1 SDPL[2

SS[12]DDP DDP SDPL[3

SS[13]ACK ACK SACK[1

SS[14]AD[0

SS[15]AD[1

SS[16]AD[2

SS[17]AD[3

SS[18]AD[4

SS[19]AD[5

SS[20]AD[6

SS[21]AD[7

SS[22]APL APL SAPL[1

SS[23]AC1J1V1 AC1J1V1 SAPL[2

SS[24]ADP ADP SAPL[3

SS[25]GFP GFP SDFP[1

SS[26]GMFP GMFP SDFP[2

SS[27]GD[0

SS[28]GD[1

SS[29]GPL GPL Res. Output Res. Output Res. Output SDMTOCLK[3]Res. Output

SS[30]GC1J1V1 GC1J1V1 Res. Output Res. Output Res. Output Res. Output Res. Output

SS[31]GDP GDP Res. Output Res. Output Res. Output Res. Output Res. Output

SS[32]DTPAIS[1

SS[33]DTPAIS[2

SS[34]DTPAIS[3

Nibble

Telecombus

Mode

Res. Output SDC1J1V1[3]DMRDAT[4]Res. Output SDMROCLK[3]DS3ROCLK[3

Res. Output SDD[1

Res. Output SDD[2

Res. Output SDD[3

Res. Input SAC1J1V1[3]DMTDAT[4]Res. Input Res. Input DS3RAIS[3

Res. Input SAD[1

Res. Input SAD[2

Res. Input SAD[3

DTPAIS[1

DTPAIS[2

DTPAIS[3

Serial

Telecombus

Mode

SDCK[2

SDCK[3

SDC1J1V1[1]DMRDAT[2]DMRDAT[2]SDMROCLK[1]DS3ROCLK[1

SDC1J1V1[2]DMRDAT[3]DMRDAT[3]SDMROCLK[2]DS3ROCLK[2

SACK[2

SACK[3

SAC1J1V1[1]DMTDAT[2]DMTDAT[2]Res. Input DS3RAIS[1

SAC1J1V1[2]DMTDAT[3]DMTDAT[3]Res. Input DS3RAIS[2

SDFP[3

Res. Output DMTOCLK DMTOCLK SDMTOCLK[2]Res. Output

SDTPAIS[1

SDTPAIS[2

SDTPAIS[3

Byte Data

Mode

DMROCLK DMROCLK Res. Input DS3RICLK[1

DMRDAT[0]DMRDAT[0]Res. Input DS3RICLK[2

DMRDAT[1]DMRDAT[1]Res. Input DS3RICLK[3

DMRDAT[5]Res. Output SDMRDAT[1

DMRDAT[6]Res. Output SDMRDAT[2

DMRDAT[7]Res. Output SDMRDAT[3

Res. Output Res. Output Res. Output Res. Output

Res. Output Res. Output Res. Output Res. Output

Res. Output Res. Output Res. Output Res. Output

DMTICLK DMTICLK SDMTICLK[1]DS3TICLK[1

DMTDAT[0]DMTDAT[0]SDMTICLK[2]DS3TICLK[2

DMTDAT[1]DMTDAT[1]SDMTICLK[3]DS3TICLK[3

DMTDAT[5]Res. Input SDMTDAT[1

DMTDAT[6]Res. Input SDMTDAT[2

DMTDAT[7]Res. Input SDMTDAT[3

Res. Input Res. Input Res. Input Res. Input

Res. Input Res. Input Res. Input Res. Input

Res. Input Res. Input Res. Input Res. Input

Res. Input DMTMSN Res. Input Res. Input

Res. Input Res. Input Res. Input Res. Input

Res. Input Res. Input SDMTOCLK[1]Res. Output

Res. Input Res. Input Res. Input DS3TAIS[1

Res. Input Res. Input Res. Input DS3TAIS[2

Res. Input Res. Input Res. Input DS3TAIS[3

Nibble Data

Mode

Serial Data

Mode

Serial DS3

Mode

DS3RDAT[1

DS3RDAT[2

DS3RDAT[3

DS3TDAT[1

DS3TDAT[2

DS3TDAT[3

Notes on System Side Modes and SS[34:0] bus mappings:

1. Res. Input pins are Reserved Input pins which must be strapped low. Failure to

connect these pins may cause malfunction or damage to the SPECTRA-155.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 15

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

2. Res. Output pins are Reserved Output pins which must be left unconnected.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 16

PM5342 SPECTRA-155

DATA SHEET

PMC-970133 ISSUE 4 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

6 DESCRIPTION

The PM5342 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER (SPECTRA-155)

terminates the transport and path overhead of STS-1 (STM-0/AU3) and

STS-3/3c (STM-1/AU3/AU4) streams at 51.84 Mbit/s and 155.52 Mbit/s

respectively. The SPECTRA-155 implements significant functions for a

SONET/SDH compliant line interface.

The SPECTRA-155 receives SONET/SDH frames via a bit serial interface,

recovers clock and data, and terminates the SONET/SDH section (regenerator

section), line (multiplexer section), and path. It performs framing (A1, A2),

descrambling, detects alarm conditions, and monitors section and line bit

interleaved parity (BIP) (B1, B2), accumulating error counts at each level for

performance monitoring purposes. B2 errors are also monitored to detect signal

fail and signal degrade threshold crossing alarms. Line remote error indications

(M1) are also accumulated. A 16 or 64 byte section trace (J0) message may be

buffered and compared against an expected message. In addition, the

SPECTRA-155 interprets the received payload pointers (H1, H2), detects path

alarm conditions, detects and accumulates path BIPs (B3), monitors and

accumulates path Remote Error Indications (REIs), accumulates and compares

the 16 or 64 byte path trace (J1) message against an expected result and

extracts the synchronous payload envelope (virtual container). All transport and

path overhead bytes are extracted and serialized on lower rate interfaces,

allowing additional external processing of overhead, if desired.

The extracted SPE (VC) is either placed on a Telecombus DROP bus, serialized

into DS3 streams, or serialized into data streams. For Telecombus applications,

frequency offsets (e.g., due to plesiochronous network boundaries, or the loss of

a primary reference timing source) and phase differences (due to normal network

operation) between the received data stream and the DROP bus are

accommodated by pointer adjustments in the DROP bus. For the DS3

application, the SPECTRA-155 demaps the three DS3s from the STS-3

(STM-1/AU3) SPE and provides serialized bit streams with derived clocks. For

data applications, the SPECTRA-155 either presents the extracted SPE (VC) as

a byte/nibble serial stream with an associated clock or presents the STS-3

(STM-1/AU3) SPE into three bit serial streams with associated clocks.

The SPECTRA-155 transmits SONET/SDH frames, via a bit serial interface, and

formats section (regenerator section), line (multiplexer section), and path

overhead appropriately. The SPECTRA-155 provides transmit path origination

for a SONET/SDH STS-1 (STM-0/AU3), STS-3 (STM-1/AU3) or STS-3c