PMC PM5316-BI Datasheet

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

PM5316

Production

SPECTRA 4x155

SONET/SDH Payload Extractor/Aligner

4 x 155 Mbit/s

Datasheet

Proprietary and Confidential

Production

Issue 4: March 2001

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 1

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Issue

No.

Issue 4 Mar

Issue 3 Jan

Issue 2 Sept

Issue 1 June

Issue

Date

2001

2001

2000

2000

Details of Change

De-documented all Transport Path Overhead port (TPOH) functionality

Added Overhead byte processing information in operation section.

• Removed TIU2E and TIU2I registers bits from registers 1n2Dh and 1n31h

respectively.

• DOPJ[1:0] register bit in the TTAL block (register 1nD1h) have been removed.

• DOPJ[1:0] register bit in the RTAL block (register 1n59h) have been redefined.

• PRBS monitoring mode needs two bits to be programmed. Mode setting in

both the DPGM (register 1n7Ah) and APGM (register 1nFAh) is now defined via

two mode bits MON_GMODE[1:0].

• RSOP Section B1 error counters (0m16h and Om17h registers) may also be

transferred upon a write to either register.

• Master test register bit 3 to 7 are defined as R/W instead of just W.

• Pin out diagram has changed format to improve readibility but the pinout

remains the SAME.

• Due to clear on write auxiliary interrupts, tZint timing is specified for

microprocessor writes to clear device interrupt pin.

• Analog supplies AVD/AVS are specified at 5% instead of 10%.

• Consistent naming or STM1-CONCAT to STM1_CONCAT (underscore) register

bit in registers 1n00h and 1n80h.

• Power supply board recommendations have been changed in section 13.8.

Separate supplies are no longer recommended.

• Specific PECL input currents are given in section 17, D.C. Characteristics.

• RAD does not contain transmitted K1/K2 bytes under generation of AIS-L on

the transmit stream.

• TAD port is limited to accumulating a maximum of 15 REI

• Additional feature explanations/ clarifications

• Timing Change on drop interface in 19.44 Mhz mode

• Addition of register bits CONCAT, TPOH_DIS, ATSI_FORCE and ATSI_RESET

• Definition changes of LOPCONRALM and PAISCONRALM.

• Added Section describing loopbacks

• DC Characteristics up to date and complete

• Added RTC_EN register bit.

Preliminary release of datasheet

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 2

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

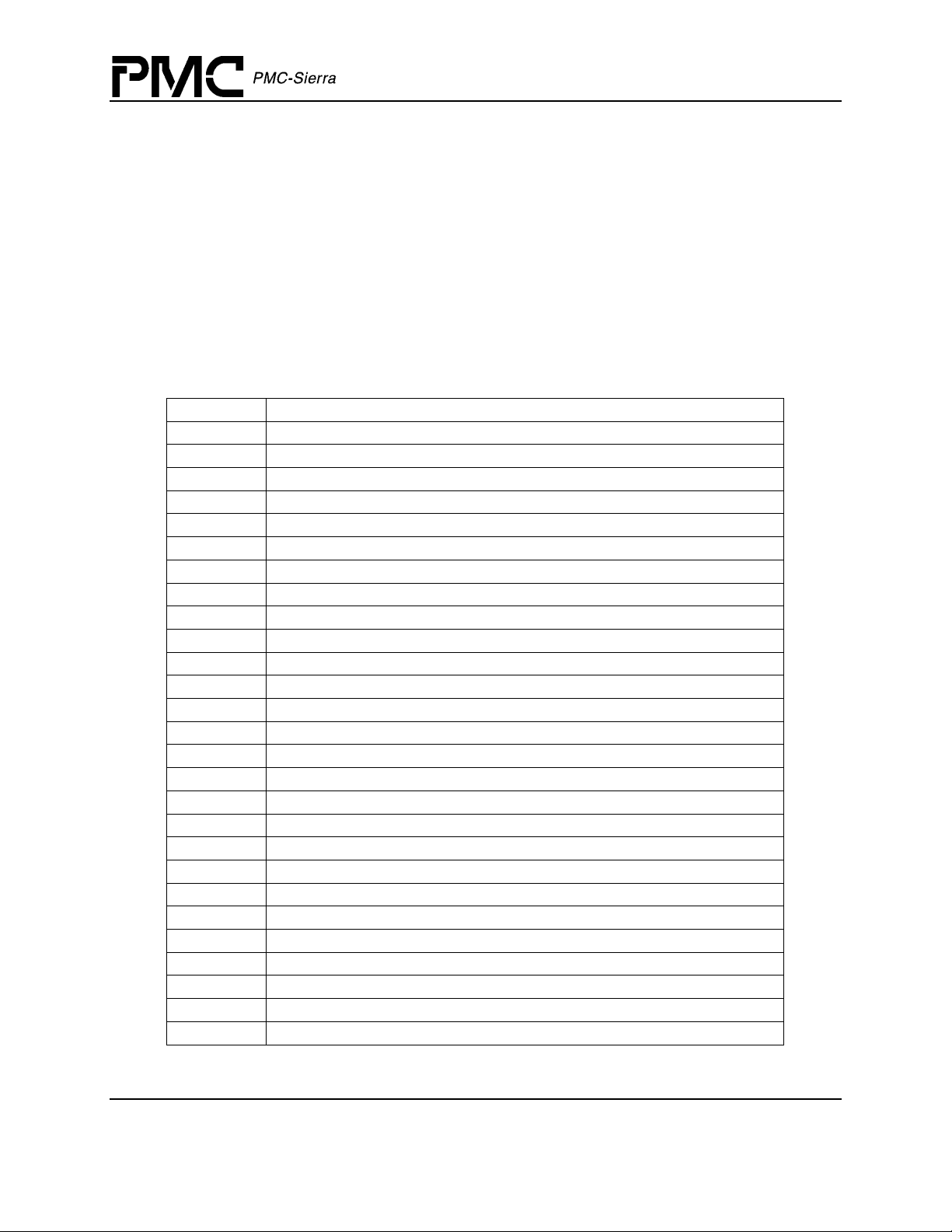

Table of Contents

Revision History...................................................................................................................2

Table of Contents.................................................................................................................. i

List of Registers.................................................................................................................. iv

List of Tables......................................................................................................................xiii

List of Figures .................................................................................................................... xv

1 Features ........................................................................................................................1

1.1 General ...............................................................................................................1

1.2 SONET Section and Line/SDH Regenerator and Multiplexer Section ...............1

1.3 SONET Path / SDH High Order Path..................................................................2

1.4 System Side Interfaces .......................................................................................3

2 Applications...................................................................................................................4

3 References....................................................................................................................5

4 Document Conventions & Definitions ...........................................................................6

5 Application Examples....................................................................................................8

6 Block Diagram.............................................................................................................10

7 Functional Description ................................................................................................ 11

8 Pin Diagrams ..............................................................................................................13

9 Pin Description (SBGA 520)........................................................................................17

9.1 Serial Line side Interface Signals......................................................................17

9.2 Section/Line/Path Status and Alarm Signals..................................................... 19

9.3 Receive Section/Line/Path Overhead Extraction Signals .................................23

9.4 Transmit Section/Line/Path Overhead Insertion Signals ..................................27

9.5 Receive Section/Line DCC Extraction Signals .................................................29

9.6 Transmit Section/Line DCC Insertion Signals................................................... 29

9.7 Transmit Path AIS Insertion Signals .................................................................30

9.8 Drop Bus Telecom Interface Signals .................................................................31

9.9 Add Bus Telecom Interface Signals ..................................................................36

9.10 Microprocessor Interface Signals......................................................................43

9.11 Analog Miscellaneous Signals .......................................................................... 44

9.12 JTAG Test Access Port (TAP) Signals...............................................................44

9.13 Power and Ground ............................................................................................45

10 Functional Description ................................................................................................48

10.1 Receive Line Interface and CRSI......................................................................48

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use i

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

10.2 Receive Section Overhead Processor (RSOP) ................................................49

10.3 Receive Section Trace Buffer (SSTB)...............................................................51

10.4 Receive Line Overhead Processor (RLOP) ......................................................52

10.5 The Receive APS, Synchronization Extractor and Bit Error Monitor (RASE)...54

10.6 Receive Transport Overhead Controller (RTOC).............................................. 55

10.7 Ring Control Port............................................................................................... 55

10.8 Receive De-multiplexer (RX_DEMUX) .............................................................56

10.9 Receive Path Processing Slice (RPPS)............................................................56

10.10 Transmit Path Processing Slice (TPPS) ...........................................................70

10.11 Transmit Multiplexer (TX_REMUX)...................................................................76

10.12 Transmit Transport Overhead Controller (TTOC) .............................................76

10.13 Transmit Line Overhead Processor (TLOP) .....................................................78

10.14 Transmit Section Overhead Processor (TSOP)................................................ 79

10.15 Transmit Section Trace Buffer (SSTB)..............................................................80

10.16 Transmit Line Interface .....................................................................................80

10.17 Add/Drop Bus Time-Slot Interchange (TSI) ......................................................80

10.18 System Side Interfaces .....................................................................................82

10.19 JTAG Test Access Port Interface ......................................................................83

10.20 Microprocessor Interface ..................................................................................83

11 Normal Mode Register Descriptions ...........................................................................94

12 Test Features Description .........................................................................................382

12.1 Master Test and Test Configuration Registers ................................................382

12.2 JTAG Test Port ................................................................................................386

13 Operation ..................................................................................................................393

13.1 Software Initialization Sequence..................................................................... 393

13.2 SONET/SDH Overhead Byte Processing ....................................................... 393

13.3 Path Processing Slice Configuration Options .................................................399

13.4 Time Slot Interchange (Grooming) Configuration Options.............................. 401

13.5 System Interface Configuration Options ......................................................... 403

13.6 Bit Error Rate Monitor (BERM) .......................................................................403

13.7 Clocking Options ............................................................................................. 404

13.8 Loopback Modes.............................................................................................406

13.9 Loopback Operation........................................................................................409

13.10 JTAG Support.................................................................................................. 410

13.11 Board Design Recommendations ...................................................................415

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use ii

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

13.12 Analog Power Supply Filtering ........................................................................416

13.13 Power Supplies Sequencing ........................................................................... 418

13.14 Interfacing to ECL or PECL Devices ...............................................................419

13.15 Clock Recovery ...............................................................................................421

14 Functional Timing......................................................................................................422

14.1 Receive Transport Overhead Extraction .........................................................422

14.2 Transmit Transport Overhead Insertion ..........................................................424

14.3 Receive Path Overhead Extraction .................................................................426

14.4 Mate SPECTRA-4x155 Interfaces ..................................................................429

14.5 Telecom Bus System Side ..............................................................................434

14.6 System Side Path AIS Control Port.................................................................443

15 Absolute Maximum Ratings ......................................................................................445

16 D.C. Characteristics ..................................................................................................446

17 Microprocessor Interface Timing Characteristics ......................................................448

18 A.C. Timing Characteristics.......................................................................................455

18.1 System Reset Timing ...................................................................................... 455

18.2 Receive Timing................................................................................................455

18.3 Telecom Drop Bus Timing ...............................................................................459

18.4 System-side Path Alarm Input Timing.............................................................461

18.5 Telecom Add Bus Timing.................................................................................462

18.6 Transmit Timing...............................................................................................463

18.7 JTAG Timing.................................................................................................... 466

19 Ordering and Thermal Information............................................................................468

20 Mechanical Information .............................................................................................470

Notes 471

Contacting PMC-Sierra Inc..................................................................................................1

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use iii

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

List of Registers

Register 0000H: SPECTRA-4x155 Reset, Identity and Accumulation Trigger .................95

Register 0001H: Master Clock Activity Monitor .................................................................96

Register 0002H: Master Clock Control.............................................................................. 97

Register 0003H: Master Interrupt Status...........................................................................99

Register 0004H: Path Processing Slice Interrupt Status #1............................................ 101

Register 0005H: Path Processing Slice Interrupt Status #2............................................ 101

Register 0006H: Path Processing Slice Interrupt Status #3............................................ 101

Register 0007H: Path Reset............................................................................................103

Register 000AH: FREE.................................................................................................... 104

Register 0010H: CSPI Control and Status ......................................................................105

Register 0011H: CSPI Reserved.....................................................................................106

Register 0100H, 0200H, 0300H, 0400H: Channel Reset, Identity and

Accumulation Trigger ................................................................................................107

Register 0101H, 0201H, 0301H, 0401H: Line Configuration #1 .....................................108

Register 0102H, 0202H, 0302H, 0402H: Line Configuration #2 .....................................110

Register 0103H, 0203H, 0303H, 0403H: Receive Line AIS Control ............................... 111

Register 0104H, 0204H, 0304H, 0404H: Ring Control ................................................... 113

Register 0105H, 0205H, 0305H, 0405H: Transmit Line RDI Control.............................. 115

Register 0106H, 0206H, 0306H, 0406H: Section Alarm Output Control #1.................... 117

Register 0107H, 0207H, 0307H, 0407H: Section Alarm Output Control #2.................... 119

Register 0108H, 0208H, 0308H, 0408H: Section/Line Block Interrupt Status ................120

Register 0109H, 0209H, 0309H, 0409H: Auxiliary Section/Line Interrupt Enable ..........122

Register 010AH, 020AH, 030AH, 040AH: Auxiliary Section/Line Interrupt Status..........124

Register 010BH, 020BH, 030BH, 040BH: Auxiliary Signal Interrupt Enable................... 126

Register 010CH, 020CH, 030CH, 040CH: Auxiliary Signal Status/Interrupt Status ........127

Registers 0110H, 0210H, 0310H, 0410H: CRSI Configuration and Interrupt

Status ........................................................................................................................128

Registers 0111H, 0211H, 0311H, 0411H: CRSI Reserved..............................................130

Registers 0114H, 0214H, 0314H, 0414H: RSOP Control and Interrupt Enable .............131

Registers 0115H, 0215H, 0315H, 0415H: RSOP Status and Interrupt ...........................133

Registers 0116H, 0216H, 0316H, 0416H: RSOP Section BIP (B1) Error Count #1 .......135

Register 0118H, 0218H, 0318H, 0418H: RLOP Control and Status ...............................136

Registers 0119H, 0219H, 0319H, 0419H: RLOP Interrupt Enable and Status ...............139

Registers 011AH, 021AH, 031AH, 041AH: RLOP Line BIP (B2) Error Count #1 ...........141

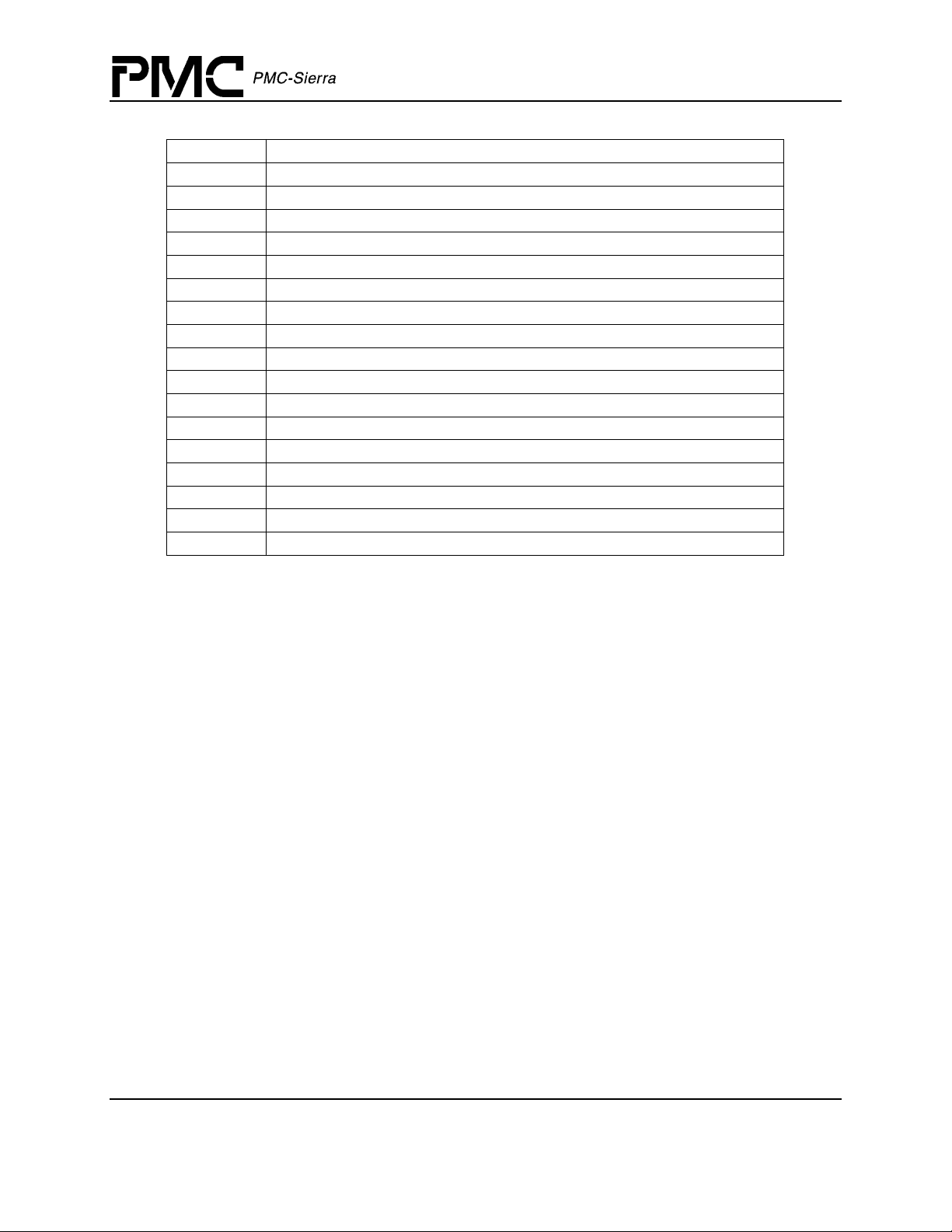

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use iv

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Registers 011BH, 021BH, 031BH, 041BH: RLOP Line BIP (B2) Error Count #2 ...........141

Registers 011CH, 021CH, 031CH, 041CH: RLOP Line BIP (B2) Error Count #3...........141

Registers 011DH, 021DH, 031DH, 041DH: RLOP REI Error Count #1..........................143

Registers 011EH, 021EH, 031EH, 041EH: RLOP REI Error Count #2 ...........................143

Registers 011FH, 021FH, 031FH, 041FH: RLOP REI Error Count #3............................143

Registers 0120H, 0220H, 0320H, 0420H: SSTB Section Trace Control ........................145

Registers 0121H, 0221H, 0321H, 0421H: SSTB Section Trace Status ..........................148

Registers 0122H, 0222H, 0322H, 0422H: SSTB Section Trace Indirect Address ..........150

Registers 0123H, 0223H, 0323H, 0423H: SSTB Section Trace Indirect Data................ 151

Registers 0124H, 0224H, 0324H, 0424H: SSTB Reserved............................................152

Registers 0125H, 0225H, 0325H, 0425H: SSTB Reserved............................................153

Registers 0126H, 0226H, 0326H, 0426H: SSTB Section Trace Operation ....................154

Registers 0130H, 0230H, 0330H, 0430H: RTOC Overhead Control .............................. 155

Registers 0131H, 0231H, 0331H, 0431H: RTOC AIS Control ........................................ 156

Registers 0140H, 0240H, 0340H, 0440H: RASE Interrupt Enable .................................157

Registers 0141H, 0241H, 0341H, 0441H: RASE Interrupt Status ..................................158

Registers 0142H, 0242H, 0342H, 0442H: RASE Configuration/Control.........................160

Registers 0143H, 0243H, 0343H, 0443H: RASE SF Accumulation Period ....................162

Registers 0144H, 0244H, 0344H, 0444H: RASE SF Accumulation Period ....................162

Registers 0145H, 0245H, 0345H, 0445H: RASE SF Accumulation Period ....................162

Registers 0146H, 0246H, 0346H, 0446H: RASE SF Saturation Threshold....................163

Registers 0147H, 0247H, 0347H, 0447H: RASE SF Saturation Threshold....................163

Registers 0148H, 0248H, 0348H, 0448H: RASE SF Declaring Threshold..................... 164

Registers 0149H, 0249H, 0349H, 0449H: RASE SF Declaring Threshold..................... 164

Registers 014AH, 024AH, 034AH, 044AH: RASE SF Clearing Threshold.....................165

Registers 014BH, 024BH, 034BH, 044BH: RASE SF Clearing Threshold.....................165

Registers 014CH, 024CH, 034CH, 044CH: RASE SD Accumulation Period .................166

Registers 014DH, 024DH, 034DH, 044DH: RASE SD Accumulation Period .................166

Registers 014EH, 024EH, 034EH, 044EH: RASE SD Accumulation Period ..................166

Registers 014FH, 024FH, 034FH, 044FH: RASE SD Saturation Threshold ..................167

Registers 0150H, 0250H, 0350H, 0450H: RASE SD Saturation Threshold ................... 167

Registers 0151H, 0251H, 0351H, 0451H: RASE SD Declaring Threshold ....................168

Registers 0152H, 0252H, 0352H, 0452H: RASE SD Declaring Threshold ....................168

Registers 0153H, 0253H, 0353H, 0453H: RASE SD Clearing Threshold ...................... 169

Registers 0154H, 0254H, 0354H, 0454H: RASE SD Clearing Threshold ...................... 169

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use v

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Registers 0155H, 0255H, 0355H, 0455H: RASE Receive K1 ........................................170

Registers 0156H, 0256H, 0356H, 0456H: RASE Receive K2 ........................................171

Registers 0157H, 0257H, 0357H, 0457H: RASE Receive Z1/S1 ...................................172

Registers 0180H, 0280H, 0380H, 0480H: TSOP Control ...............................................173

Registers 0181H, 0281H, 0381H, 0481H: TSOP Diagnostic .......................................... 174

Registers 0184H, 0284H, 0384H, 0484H: TLOP Control................................................ 175

Registers 0185H, 0285H, 0385H, 0485H: TLOP Diagnostic ..........................................176

Registers 0186H, 0286H, 0386H, 0486H: TLOP Transmit K1........................................177

Registers 0187H, 0287H, 0387H, 0487H: TLOP Transmit K2........................................178

Registers 0188H, 0288H, 0388H, 0488H: TTOC Transmit Overhead Output

Control.......................................................................................................................179

Registers 0189H, 0289H, 0389H, 0489H: TTOC Transmit Overhead Byte Control .......180

Registers 018AH, 028AH, 038AH, 048AH: TTOC Transmit Z0 ...................................... 183

Registers 018BH, 028BH, 038BH, 048BH: TTOC Transmit S1 ......................................184

Registers 0190H, 0290H, 0390H, 0490H: Reserved .....................................................185

Registers 0199H, 0299H, 0399H, 0499H: Reserved ......................................................186

Registers 019AH, 029AH, 039AH, 049AH: Reserved.................................................... 186

Registers 019BH, 029BH, 039BH, 049BH: Reserved..................................................... 187

Registers 019CH, 029CH, 039CH, 049CH: Reserved....................................................187

Registers 019DH, 029DH, 039DH, 049DH: Reserved....................................................188

Register 1001H: Drop Bus STM-1 #1 AU-3 #1 Select ....................................................189

Register 1002H: Drop Bus STM-1 #2 AU-3 #1 Select ....................................................190

Register 1003H: Drop Bus STM-1 #3 AU-3 #1 Select ....................................................191

Register 1004H: Drop Bus STM-1 #4 AU-3 #1 Select ....................................................192

Register 1005H: Drop Bus STM-1 #1 AU-3 #2 Select ....................................................193

Register 1006H: Drop Bus STM-1 #2 AU-3 #2 Select ....................................................194

Register 1007H: Drop Bus STM-1 #3 AU-3 #2 Select ....................................................195

Register 1008H: Drop Bus STM-1 #4 AU-3 #2 Select ....................................................196

Register 1009H: Drop Bus STM-1 #1 AU-3 #3 Select ....................................................197

Register 100AH: Drop Bus STM-1 #2 AU-3 #3 Select....................................................198

Register 100BH: Drop Bus STM-1 #3 AU-3 #3 Select....................................................199

Register 100CH: Drop Bus STM-1 #4 AU-3 #3 Select.................................................... 200

Register: Register 1020H: Drop Bus DLL Configuration.................................................201

Register 1021H: Drop Bus DLL Reserved ......................................................................202

Register 1022H: Drop Bus DLL Reset Register ..............................................................203

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use vi

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Register 1023H: Drop Bus DLL Control Status ...............................................................204

Register 1030H: Drop Bus Configuration ........................................................................ 206

Register 1081H: SPECTRA-4x155 Add Bus STM-1 #1 AU-3 #1 Select .........................208

Register 1082H: SPECTRA-4x155 Add Bus STM-1 #2 AU-3 #1 Select .........................209

Register 1083H: SPECTRA-4x155 Add Bus STM-1 #3 AU-3 #1 Select .........................210

Register 1084H: SPECTRA-4x155 Add Bus STM-1 #4 AU-3 #1 Select ......................... 211

Register 1085H: SPECTRA-4x155 Add Bus STM-1 #1 AU-3 #2 Select .........................212

Register 1086H: SPECTRA-4x155 Add Bus STM-1 #2 AU-3 #2 Select......................... 213

Register 1087H: SPECTRA-4x155 Add Bus STM-1 #3 AU-3 #2 Select .........................214

Register 1088H: SPECTRA-4x155 Add Bus STM-1 #4 AU-3 #2 Select .........................215

Register 1089H: SPECTRA-4x155 Add Bus STM-1 #1 AU-3 #3 Select .........................216

Register 108AH: SPECTRA-4x155 Add Bus STM-1 #2 AU-3 #3 Select ........................217

Register 108BH: SPECTRA-4x155 Add Bus STM-1 #3 AU-3 #3 Select ........................218

Register 108CH: SPECTRA-4x155 Add Bus STM-1 #4 AU-3 #3 Select ........................219

Register 10B0H: SPECTRA-4x155 Add Bus Configuration #1 .......................................220

Register 10B1H: SPECTRA-4x155 Add Bus Configuration #2 .......................................222

Register 10B2H: SPECTRA-4x155 Add Bus Parity Interrupt Enable .............................223

Register 10B4H: SPECTRA-4x155 Add Bus Parity Interrupt Status...............................224

Register 10B6H: SPECTRA-4x155 System Side Clock Activity Monitor ........................225

Register 10B7H: SPECTRA-4x155 Add Bus Signal Activity Monitor ..............................226

Registers 1100H, 1200H, 1300H, 1400H, 1500H, 1600H, 1700H, 1800H, 1900H,

1A00H, 1B00H, 1C00H: RPPS Configuration & Slice ID .........................................227

Registers 1102H, 1202H, 1302H, 1402H, 1502H, 1602H, 1702H, 1802H, 1902H,

1A02H, 1B02H, 1C02H: RPPS Path Configuration ..................................................228

Registers 1110H, 1210H, 1310H, 1410H, 1510H, 1610H, 1710H, 1810H, 1910H,

1A10H, 1B10H, 1C10H: RPPS Path AIS Control #1 ................................................230

Regist ers 1111 H, 12 11H, 1 311H, 1411H, 15 11H, 1 611H, 1711H , 1811 H, 1911H,

1A11H, 1B11H, 1C11H: RPPS Path AIS Control #2.................................................233

Registers 1114H, 1214H, 1314H, 1414H, 1514H, 1614H, 1714H, 1814H, 1914H,

1A14H, 1B14H, 1C14H: RPPS Path REI/RDI Control #1 ........................................235

Registers 1115H, 1215H, 1315H, 1415H, 1515H, 1615H, 1715H, 1815H, 1915H,

1A15H, 1B15H, 1C15H: RPPS Path REI/RDI Control #2 ........................................237

Registers 1116H, 1216H, 1316H, 1416H, 1516H, 1616H, 1716H, 1816H, 1916H,

1A16H, 1B16H, 1C16H: Reserved ...........................................................................239

Registers 1118H, 1218H, 1318H, 1418H, 1518H, 1618H, 1718H, 1818H, 1918H,

1A18H, 1B18H, 1C18H: RPPS Path Enhanced RDI Control #1 ..............................240

Registers 1119H, 1219H, 1319H, 1419H, 1519H, 1619H, 1719H, 1819H, 1919H,

1A19H, 1B19H, 1C19H: RPPS Path Enhanced RDI Control #2 ..............................242

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use vii

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Registers 111CH, 121CH, 131CH, 141CH, 151CH, 161CH, 171CH, 181CH,

191CH, 1A1CH, 1B1CH, 1C1CH: RPPS RALM Output Control #1 .........................244

Registers 111DH, 121DH, 131DH, 141DH, 151DH, 161DH, 171DH, 181DH,

191DH, 1A1DH, 1B1DH, 1C1DH: RPPS RALM Output Control #2 .........................247

Registers 111EH, 121EH, 131EH, 141EH, 151EH, 161EH, 171EH, 181EH,

191EH, 1A1EH, 1B1EH, 1C1EH: RPPS Reserved ..................................................249

Registers 1128H, 1228H, 1328H, 1428H, 1528H, 1628H, 1728H, 1828H, 1928H,

1A28H, 1B28H, 1C28H: RPPS Path Interrupt Status............................................... 250

Registers 112CH, 122CH, 132CH, 142CH, 152CH, 162CH, 172CH, 182CH,

192CH, 1A2CH, 1B2CH, 1C2CH: RPPS Auxiliary Path Interrupt Enable #1 ...........251

Registers 112DH, 122DH, 132DH, 142DH, 152DH, 162DH, 172DH, 182DH,

192DH, 1A2DH, 1B2DH, 1C2DH: RPPS Auxiliary Path Interrupt Enable #2 ...........253

Registers 1130H, 1230H, 1330H, 1430H, 1530H, 1630H, 1730H, 1830H, 1930H,

1A30H, 1B30H, 1C30H: RPPS Auxiliary Path Interrupt Status #1 ...........................255

Registers 1131H, 1231H, 1331H, 1431H, 1531H, 1631H, 1731H, 1831H, 1931H,

1A31H, 1B31H, 1C31H: RPPS Auxiliary Path Interrupt Status #2 ...........................257

Registers 1134H, 1234H, 1334H, 1434H, 1534H, 1634H, 1734H, 1834H, 1934H,

1A34H, 1B34H, 1C34H: RPPS Auxiliary Path Status............................................... 258

Production

Registers 1140H, 1240H, 1340H, 1440H, 1540H, 1640H, 1740H, 1840H, 1940H,

1A40H, 1B40H, 1C40H: RPOP Status and Control (EXTD=0)................................. 259

Registers 1140H, 1240H, 1340H, 1440H, 1540H, 1640H, 1740H, 1840H, 1940H,

1A40H, 1B40H, 1C40H: RPOP Status and Control (EXTD=1)................................. 261

Registers 1141H, 1241H, 1341H, 1441H, 1541H, 1641H, 1741H, 1841H, 1941H,

1A41H, 1B41H, 1C41H: RPOP Alarm Interrupt Status (EXTD=0)............................262

Registers 1141H, 1241H, 1341H, 1441H, 1541H, 1641H, 1741H, 1841H, 1941H,

1A41H, 1B41H, 1C41H: RPOP Alarm Interrupt Status (EXTD=1)............................264

Registers 1142H, 1242H, 1342H, 1442H, 1542H, 1642H, 1742H, 1842H, 1942H,

1A42H, 1B42H, 1C42H: RPOP Pointer Interrupt Status...........................................265

Registers 1143H, 1243H, 1343H, 1443H, 1543H, 1643H, 1743H, 1843H, 1943H,

1A43H, 1B43H, 1C43H: RPOP Alarm Interrupt Enable (EXTD=0) ..........................267

Registers 1143H, 1243H, 1343H, 1443H, 1543H, 1643H, 1743H, 1843H, 1943H,

1A43H, 1B43H, 1C43H: RPOP Alarm Interrupt Enable and Concat Pointer

Status (EXTD=1).......................................................................................................269

Registers 1144H, 1244H, 1344H, 1444H, 1544H, 1644H, 1744H, 1844H, 1944H,

1A44H, 1B44H, 1C44H: RPOP Pointer Interrupt Enable .........................................270

Registers 1145H, 1245H, 1345H, 1445H, 1545H, 1645H, 1745H, 1845H, 1945H,

1A45H, 1B45H, 1C45H: RPOP Pointer LSB ............................................................ 272

Registers 1146H, 1246H, 1346H, 1446H, 1546H, 1646H, 1746H, 1846H, 1946H,

1A46H, 1B46H, 1C46H: RPOP Pointer MSB ........................................................... 273

Registers 1147H, 1247H, 1347H, 1447H, 1547H, 1647H, 1747H, 1847H, 1947H,

1A47H, 1B47H, 1C47H: RPOP Path Signal Label ...................................................275

Registers 1148H, 1248H, 1348H, 1448H, 1548H, 1648H, 1748H, 1848H, 1948H,

1A48H, 1B48H, 1C48H: RPOP Path BIP-8 LSB ......................................................276

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use viii

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Registers 1149H, 1249H, 1349H, 1449H, 1549H, 1649H, 1749H, 1849H, 1949H,

1A49H, 1B49H, 1C49H: RPOP Path BIP-8 MSB .....................................................276

Registers 114AH, 124AH, 134AH, 144AH, 154AH, 164AH, 174AH, 184AH,

194AH, 1A4AH, 1B4AH, 1C4AH: RPOP Path REI LSB ...........................................277

Registers 114BH, 124BH, 134BH, 144BH, 154BH, 164BH, 174BH, 184BH,

194BH, 1A4BH, 1B4BH, 1C4BH: RPOP Path REI MSB ..........................................277

Registers 114CH, 124CH, 134CH, 144CH, 154CH, 164CH, 174CH, 184CH,

194CH, 1A4CH, 1B4CH, 1C4CH: RPOP Tributary Multiframe Status and

Control.......................................................................................................................278

Registers 114DH, 124DH, 134DH, 144DH, 154DH, 164DH, 174DH, 184DH,

194DH, 1A4DH, 1B4DH, 1C4DH: RPOP Ring Control ............................................280

Registers 1154H, 1254H, 1354H, 1454H, 1554H, 1654H, 1754H, 1854H, 1954H,

1A54H, 1B54H, 1C54H: PMON Receive Positive Pointer Justification Count .........282

Registers 1155H, 1255H, 1355H, 1455H, 1555H, 1655H, 1755H, 1855H, 1955H,

1A55H, 1B55H, 1C55H: PMON Receive Negative Pointer Justification Count .......283

Registers 1156H, 1256H, 1356H, 1456H, 1556H, 1656H, 1756H, 1856H, 1956H,

1A56H, 1B56H, 1C56H: PMON Transmit Positive Pointer Justification Count ........284

Production

Registers 1157H, 1257H, 1357H, 1457H, 1557H, 1657H, 1757H, 1857H, 1957H,

1A57H, 1B57H, 1C57H: PMON Transmit Negative Pointer Justification Count.......285

Registers 1158H, 1258H, 1358H, 1458H, 1558H, 1658H, 1758H, 1858H, 1958H,

1A58H, 1B58H, 1C58H: RTAL Control .....................................................................286

Registers 1159H, 1259H, 1359H, 1459H, 1559H, 1659H, 1759H, 1859H, 1959H,

1A59H, 1B59H, 1C59H: RTAL Interrupt Status and Control.....................................288

Registers 115AH, 125AH, 135AH, 145AH, 155AH, 165AH, 175AH, 185AH,

195AH, 1A5AH, 1B5AH, 1C5AH: RTAL Alarm and Diagnostic Control....................290

Registers 1160H, 1260H, 1360H, 1460H, 1560H, 1660H, 1760H, 1860H, 1960H,

1A60H, 1B60H, 1C60H: SPTB Control.....................................................................292

Registers 1161H, 1261H, 1361H, 1461H, 1561H, 1661H, 1761H, 1861H, 1961H,

1A61H, 1B61H, 1C61H: SPTB Path Trace Identifier Status.....................................295

Registers 1162H, 1262H, 1362H, 1462H, 1562H, 1662H, 1762H, 1862H, 1962H,

1A62H, 1B62H, 1C62H: SPTB Indirect Address Register........................................297

Registers 1163H, 1263H, 1363H, 1463H, 1563H, 1663H, 1763H, 1863H, 1963H,

1A63H, 1B63H, 1C63H: SPTB Indirect Data Register .............................................298

Registers 1164H, 1264H, 1364H, 1464H, 1564H, 1664H, 1764H, 1864H, 1964H,

1A64H, 1B64H, 1C64H: SPTB Expected Path Signal Label....................................299

Registers 1165H, 1265H, 1365H, 1465H, 1565H, 1665H, 1765H, 1865H, 1965H,

1A65H, 1B65H, 1C65H: SPTB Path Signal Label Control and Status .....................300

Registers 1166H, 1266H, 1366H, 1466H, 1566H, 1666H, 1766H, 1866H, 1966H,

1A66H, 1B66H, 1C66H: SPTB Path Trace Operation Trigger..................................302

Registers 1170H, 1270H, 1370H, 1470H, 1570H, 1670H, 1770H, 1870H, 1970H,

1A70H, 1B70H, 1C70H: DPGM Generator Control #1.............................................303

Registers 1171H, 1271H, 1371H, 1471H, 1571H, 1671H, 1771H, 1871H, 1971H,

1A71H, 1B71H, 1C71H: Reserved ...........................................................................305

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use ix

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Registers 1172H, 1272H, 1372H, 1472H, 1572H, 1672H, 1772H, 1872H, 1972H,

1A72H, 1B72H, 1C72H: DPGM Generator Concatenate Control ............................306

Registers 1173H, 1273H, 1373H, 1473H, 1573H, 1673H, 1773H, 1873H, 1973H,

1A73H, 1B73H, 1C73H: DPGM Generator Status....................................................307

Registers 1178H, 1278H, 1378H, 1478H, 1578H, 1678H, 1778H, 1878H, 1978H,

1A78H, 1B78H, 1C78H: DPGM Monitor Control #1 ................................................. 308

Eng Registers 1179H, 1279H, 1379H, 1479H, 1579H, 1679H, 1779H, 1879H,

1979H, 1A79H, 1B79H, 1C79H: Reserved...............................................................310

Registers 117AH, 127AH, 137AH, 147AH, 157AH, 167AH, 177AH, 187AH,

197AH, 1A7AH, 1B7AH, 1C7AH: DPGM Monitor Concatenate Control .................. 311

Registers 117BH, 127BH, 137BH, 147BH, 157BH, 167BH, 177BH, 187BH,

197BH, 1A7BH, 1B7BH, 1C7BH: DPGM Monitor Status .........................................313

Registers 117CH, 127CH, 137CH, 147CH, 157CH, 167CH, 177CH, 187CH,

197CH, 1A7CH, 1B7CH, 1C7CH: DPGM Monitor Error Count #1 ...........................315

Registers 117DH, 127DH, 137DH, 147DH, 157DH, 167DH, 177DH, 187DH,

197DH, 1A7DH, 1B7DH, 1C7DH: DPGM Monitor Error Count #2 ...........................315

Registers 1180H, 1280H, 1380H, 1480H, 1580H, 1680H, 1780H, 1880H, 1980H,

1A80H, 1B80H, 1C80H: SPECTRA-4x155 TPPS Configuration..............................316

Production

Registers 1182H, 1282H, 1382H, 1482H, 1582H, 1682H, 1782H, 1882H, 1982H,

1A82H, 1B82H, 1C82H: TPPS Path Configuration ..................................................318

Registers 1186H, 1286H, 1386H, 1486H, 1586H, 1686H, 1786H, 1886H, 1986H,

1A86H, 1B86H, 1C86H: TPPS Path Transmit Control .............................................320

Registers 1190H, 1290H, 1390H, 1490H, 1590H, 1690H, 1790H, 1890H, 1990H,

1A90H, 1B90H, 1C90H: TPPS Path AIS Control......................................................322

Registers 11A8H, 12A8H, 13A8H, 14A8H, 15A8H, 16A8H, 17A8H, 18A8H,

19A8H, 1AA8H, 1BA8H, 1CA8H: TPPS Path Interrupt Status .................................324

Registers 11ACH, 12ACH, 13ACH, 14ACH, 15ACH, 16ACH, 17ACH, 18ACH,

19ACH, 1AACH, 1BACH, 1CACH: TPPS Auxiliary Path Interrupt Enable ...............325

Registers 11B0H, 12B0H, 13B0H, 14B0H, 15B0H, 16B0H, 17B0H, 18B0H,

19B0H, 1AB0H, 1BB0H, 1CB0H: SPECTRA-4x155 TPPS Auxiliary Path

Interrupt Status..........................................................................................................327

Registers 11C0H, 12C0H, 13C0H, 14C0H, 15C0H, 16C0H, 17C0H, 18C0H,

19C0H, 1AC0H, 1BC0H, 1CC0H: TPOP Control ..................................................... 329

Registers 11C1H, 12C1H, 13C1H, 14C1H, 15C1H, 16C1H, 17C1H, 18C1H,

19C1H, 1AC1H, 1BC1H, 1CC1H: TPOP Pointer Control......................................... 331

Registers 11C3H, 12C3H, 13C3H, 14C3H, 15C3H, 16C3H, 17C3H, 18C3H,

19C3H, 1AC3H, 1BC3H, 1CC3H: TPOP Current Pointer LSB.................................332

Registers 11C4H, 12C4H, 13C4H, 14C4H, 15C4H, 16C4H, 17C4H, 18C4H,

19C4H, 1AC4H, 1BC4H, 1CC4H: TPOP Current Pointer MSB................................332

Registers 11C5H, 12C5H, 13C5H, 14C5H, 15C5H, 16C5H, 17C5H, 18C5H,

19C5H, 1AC5H, 1BC5H, 1CC5H: TPOP Payload Pointer LSB................................333

Registers 11C6H, 12C6H, 13C6H, 14C6H, 15C6H, 16C6H, 17C6H, 18C6H,

19C6H, 1AC6H, 1BC6H, 1CC6H: TPOP Payload Pointer MSB...............................333

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use x

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Registers 11C7H, 12C7H, 13C7H, 14C7H, 15C7H, 16C7H, 17C7H, 18C7H,

19C7H, 1AC7H, 1BC7H, 1CC7H: TPOP Path Trace ...............................................334

Registers 11C8H, 12C8H, 13C8H, 14C8H, 15C8H, 16C8H, 17C8H, 18C8H,

19C8H, 1AC8H, 1BC8H, 1CC8H: TPOP Path Signal Label.....................................335

Registers 11C9H, 12C9H, 13C9H, 14C9H, 15C9H, 16C9H, 17C9H, 18C9H,

19C9H, 1AC9H, 1BC9H, 1CC9H: TPOP Path Status ..............................................336

Registers 11CAH, 12CAH, 13CAH, 14CAH, 15CAH, 16CAH, 17CAH, 18CAH,

19CAH, 1ACAH, 1BCAH, 1CCAH: TPOP Path User Channel.................................338

Registers 11CBH, 12CBH, 13CBH, 14CBH, 15CBH, 16CBH, 17CBH, 18CBH,

19CBH, 1ACBH, 1BCBH, 1CCBH: TPOP Path Growth #1 ......................................339

Registers 11CCH, 12CCH, 13CCH, 14CCH, 15CCH, 16CCH, 17CCH, 18CCH,

19CCH, 1ACCH, 1BCCH, 1CCCH: TPOP Path Growth #2 .....................................340

Registers 11CDH, 12CDH, 13CDH, 14CDH, 15CDH, 16CDH, 17CDH, 18CDH,

19CDH, 1ACDH, 1BCDH, 1CCDH: TPOP Tandem Connection Maintenance.........341

Registers 11D0H, 12D0H, 13D0H, 14D0H, 15D0H, 16D0H, 17D0H, 18D0H,

19D0H, 1AD0H, 1BD0H, 1CD0H: TTAL Control.......................................................342

Registers 11D1H, 12D1H, 13D1H, 14D1H, 15D1H, 16D1H, 17D1H, 18D1H,

19D1H, 1AD1H, 1BD1H, 1CD1H: TTAL Interrupt Status and Control ......................344

Production

Registers 11D2H, 12D2H, 13D2H, 14D2H, 15D2H, 16D2H, 17D2H, 18D2H,

19D2H, 1AD2H, 1BD2H, 1CD2H: TTAL Alarm and Diagnostic Control ...................346

Registers 11E0H, 12E0H, 13E0H, 14E0H, 15E0H, 16E0H, 17E0H, 18E0H,

19E0H, 1AE0H, 1BE0H, 1CE0H: TPIP Status and Control (EXTD=0)..................... 348

Registers 11E0H, 12E0H, 13E0H, 14E0H, 15E0H, 16E0H, 17E0H, 18E0H,

19E0H, 1AE0H, 1BE0H, 1CE0H: TPIP Status and Control (EXTD=1)..................... 350

Registers 11E1H, 12E1H, 13E1H, 14E1H, 15E1H, 16E1H, 17E1H, 18E1H,

19E1H, 1AE1H, 1BE1H, 1CE1H: TPIP Alarm Interrupt Status (EXTD=0) ...............351

Registers 11E2H, 12E2H, 13E2H, 14E2H, 15E2H, 16E2H, 17E2H, 18E2H,

19E2H, 1AE2H, 1BE2H, 1CE2H: TPIP Pointer Interrupt Status...............................353

Registers 11E3H, 12E3H, 13E3H, 14E3H, 15E3H, 16E3H, 17E3H, 18E3H,

19E3H, 1AE3H, 1BE3H, 1CE3H: TPIP Alarm Interrupt Enable (EXTD=0) ..............355

Registers 11E3H, 12E3H, 13E3H, 14E3H, 15E3H, 16E3H, 17E3H, 18E3H,

19E3H, 1AE3H, 1BE3H, 1CE3H: TPIP Alarm Interrupt Enable (EXTD=1) ..............357

Registers 11E4H, 12E4H, 13E4H, 14E4H, 15E4H, 16E4H, 17E4H, 18E4H,

19E4H, 1AE4H, 1BE4H, 1CE4H: TPIP Pointer Interrupt Enable .............................358

Registers 11E5H, 12E5H, 13E5H, 14E5H, 15E5H, 16E5H, 17E5H, 18E5H,

19E5H, 1AE5H, 1BE5H, 1CE5H: TPIP Pointer LSB ................................................360

Registers 11E6H, 12E6H, 13E6H, 14E6H, 15E6H, 16E6H, 17E6H, 18E6H,

19E6H, 1AE6H, 1BE6H, 1CE6H: TPIP Pointer MSB ...............................................361

Registers 11E8H, 12E8H, 13E8H, 14E8H, 15E8H, 16E8H, 17E8H, 18E8H,

19E8H, 1AE8H, 1BE8H, 1CE8H: TPIP Path BIP-8 LSB ..........................................363

Registers 11E9H, 12E9H, 13E9H, 14E9H, 15E9H, 16E9H, 17E9H, 18E9H,

19E9H, 1AE9H, 1BE9H, 1CE9H: TPIP Path BIP-8 MSB .........................................363

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use xi

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Registers 11ECH, 12ECH, 13ECH, 14ECH, 15ECH, 16ECH, 17ECH, 18ECH,

19ECH, 1AECH, 1BECH, 1CECH: TPIP Tributary Multiframe Status and

Control.......................................................................................................................364

Registers 11EDH, 12EDH, 13EDH, 14EDH, 15EDH, 16EDH, 17EDH, 18EDH,

19EDH, 1AEDH, 1BEDH, 1CEDH: TPIP BIP Control...............................................366

Registers 11F0H, 12F0H, 13F0H, 14F0H, 15F0H, 16F0H, 17F0H, 18F0H,

19F0H, 1AF0H, 1BF0H, 1CF0H: APGM Generator Control #1................................ 368

Registers 11F1H, 12F1H, 13F1H, 14F1H, 15F1H, 16F1H, 17F1H, 18F1H,

19F1H, 1AF1H, 1BF1H, 1CF1H: APGM Generator Control #2................................ 370

Registers 11F2H, 12F2H, 13F2H, 14F2H, 15F2H, 16F2H, 17F2H, 18F2H,

19F2H, 1AF2H, 1BF2H, 1CF2H: APGM Generator Concatenate Control ...............371

Registers 11F3H, 12F3H, 13F3H, 14F3H, 15F3H, 16F3H, 17F3H, 18F3H,

19F3H, 1AF3H, 1BF3H, 1CF3H: APGM Generator Status ......................................373

Registers 11F8H, 12F8H, 13F8H, 14F8H, 15F8H, 16F8H, 17F8H, 18F8H,

19F8H, 1AF8H, 1BF8H, 1CF8H: APGM Monitor Control #1....................................374

Registers 11F9H, 12F9H, 13F9H, 14F9H, 15F9H, 16F9H, 17F9H, 18F9H,

19F9H, 1AF9H, 1BF9H, 1CF9H: APGM Monitor Control #2....................................376

Production

Registers 11FAH, 12FAH, 13FAH, 14FAH, 15FAH, 16FAH, 17FAH, 18FAH,

19FAH, 1AFAH, 1BFAH, 1CFAH:APGM Monitor Concatenate Control ...................377

Registers 11FBH, 12FBH, 13FBH, 14FBH, 15FBH, 16FBH, 17FBH, 18FBH,

19FBH, 1AFBH, 1BFBH, 1CFBH:APGM Monitor Status.......................................... 379

Registers 11FCH, 12FCH, 13FCH, 14FCH, 15FCH, 16FCH, 17FCH, 18FCH,

19FCH, 1AFCH, 1BFCH, 1CFCH: APGM Monitor Error Count #1...........................381

Registers 11FDH, 12FDH, 13FDH, 14FDH, 15FDH, 16FDH, 17FDH, 18FDH,

19FDH, 1AFDH, 1BFDH, 1CFDH:APGM Monitor Error Count #2 ...........................381

Register 2000H: Master Test ...........................................................................................383

Register Address 2001H: Master Test Slice Select .........................................................385

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use xii

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

List of Tables

Table 1 Pointer Interpreter Event (Indications) Description ............................................59

Table 2 Pointer Interpreter Transition Description ..........................................................60

Table 3 Path Signal Label Match/Mismatch State Table. ...............................................64

Table 4 Pointer Generator Event (Indications) Description .............................................67

Table 5 Pointer Generator Transition Description ...........................................................68

Table 6 Columns and STS-1 (STM-0/AU-3) Streams Association. ................................81

Table 7 System Side Add Bus Configuration Options.....................................................83

Table 8 System Side Drop Bus Configuration Options ...................................................83

Table 9 Register Memory Map........................................................................................84

Table 10 Correspondence between Channel and Path Processing Slice Number ......108

Table 11 Transport overhead National and Unused bytes............................................181

Table 12 Receive ESD[1:0] Codepoints........................................................................289

Table 13 RXSEL[1:0] Codepoints for STS-1 and STS-3c.............................................319

Table 14 Transmit RDI Control......................................................................................336

Table 15 Transmit ESD[1:0] Codepoints.......................................................................345

Table 16 Test Mode Register Memory Map ..................................................................382

Table 17 TSTADDSEL[3:0] Codepoints When Addressing Transport Channels. ........385

Table 18 TSTADDSEL[3:0] Codepoints When Address RPPS/TPPS Slices ...............385

Table 19 Instruction Register (Length - 3 bits) .............................................................. 386

Table 20 Identification Register.....................................................................................387

Table 21 Boundary Scan Register ................................................................................387

Table 22 Transport Overhead Bytes .............................................................................395

Table 23 Path Overhead Bytes ..................................................................................... 398

Table 24 Slice Configuration for SDH STM-1 Path Processing ....................................399

Table 25 Slice Configuration for SONET STS-3/3c Path Processing ...........................399

Table 26 Valid Master/Slave Slice Configurations within a Channel ............................400

Table 27 Telecom Bus STS-1 (STM-0/AU-3) Time-slots (Streams).............................402

Table 28 Recommended BERM settings ......................................................................404

Table 29 Absolute Maximum Ratings............................................................................445

Table 30 D.C Characteristics ........................................................................................446

Table 31 Microprocessor Interface Read Access .........................................................448

Table 32 Microprocessor Interface Write Access.......................................................... 451

Table 33 RSTB Timing (Figure 52) ...............................................................................455

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use xiii

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Table 34 Receive Line Input Interface Timing............................................................... 455

Table 35 Receive Line Overhead and Alarm Output Timing ........................................455

Table 36 Receive Path Overhead and Alarm Port Output Timing ................................456

Table 37 Receive Ring Control Port Output Timing ...................................................... 458

Table 38 Receive Tandem Connection Input Timing ....................................................458

Table 39 Telecom Drop Bus Input Timing.....................................................................459

Table 40 Telecom Drop Bus Output Timing at 77.76 MHz DCK...................................460

Table 41 Telecom Drop Bus Output Timing at 19.44 Mhz DCK ...................................460

Table 42 System DROP-side Path Alarm Input Timing ................................................461

Table 43 System ADD-side Path Alarm Input Timing ...................................................461

Table 44 Telecom Add Bus Input Timing ......................................................................462

Table 45 Transmit Alarm Port Input Timing ..................................................................463

Table 46 Transmit Transport Overhead Input Timing ...................................................464

Table 47 Transmit Ring Control Port Input Timing ........................................................465

Table 48 Transmit Overhead Output Timing .................................................................465

Table 49 JTAG Port Interface........................................................................................466

Table 50 Ordering information.......................................................................................468

Table 51 Thermal information – Theta Jc .....................................................................468

Table 52 Maximum Junction Temperature.................................................................... 468

Table 53 Thermal information – Theta Ja vs. Airflow....................................................468

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use xiv

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

List of Figures

Figure 1 STS-3 (STM-0/AU-3) or STS-3c (STM-1/AU-4) Application with 19.44

MHz Byte TelecomBus Interface ......................................................................8

Figure 2 STS-3 (STM-1/AU-3) or STS-3c (STM-1/AU-4) Application with 77.76

MHz Byte TelecomBus Interface ......................................................................9

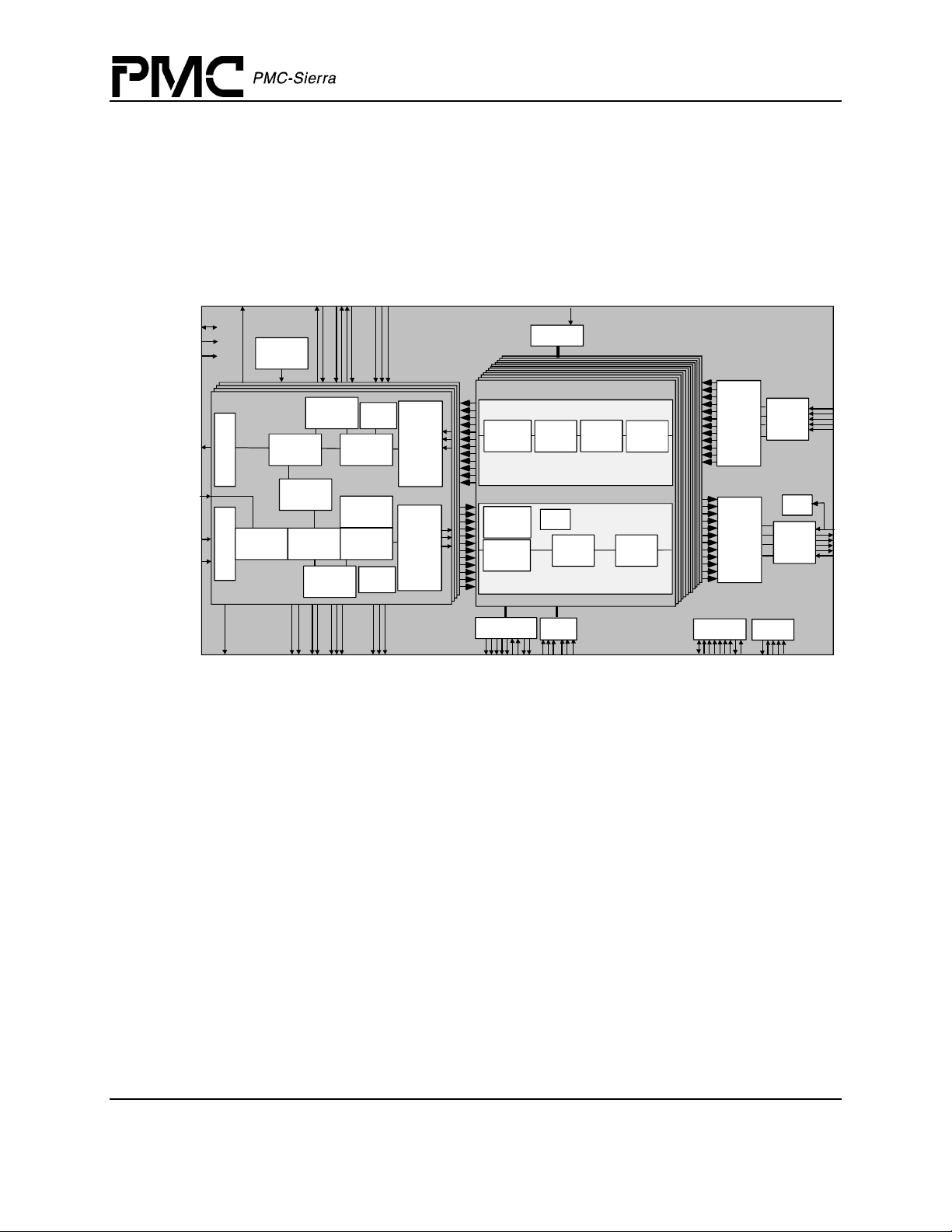

Figure 3 Block Diagram ................................................................................................... 10

Figure 4 Pin diagram of SPECTRA-4x155 (Bottom Top right going clockwise) .............13

Figure 5 SPECTRA-4x155 Typical Jitter Tolerance........................................................49

Figure 6 Pointer Interpretation State Diagram ................................................................59

Figure 7 Pointer Generation State Diagram ....................................................................67

Figure 8 Unused and National Use Bytes .........................................................................77

Figure 9 - Path Processing Slices and Order of Transmission .........................................93

Figure 10 Input Observation Cell (IN_CELL) ................................................................391

Figure 11 Output Cell (OUT_CELL) .............................................................................. 391

Figure 12 Bi-directional Cell (IO_CELL) ........................................................................392

Figure 13 Layout of Output Enable and Bi-directional Cells .........................................392

Figure 14 Conceptual Clocking Structure......................................................................405

Figure 15 Line Loopback...............................................................................................406

Figure 16 System Side Line Loopback .........................................................................407

Figure 17 Serial Diagnostic Loopback ..........................................................................408

Figure 18 Parallel Diagnostic Loopback........................................................................ 409

Figure 19 Boundary Scan Architecture .........................................................................411

Figure 20 TAP Controller Finite State Machine............................................................. 413

Figure 21 Analog Power Filters with 3.3V Supply (1).................................................... 417

Figure 22 Power Sequencing Circuit.............................................................................419

Figure 23 Interfacing to ECL or PECL Devices.............................................................420

Figure 24 Clock Recovery External Components .........................................................421

Figure 25 Receive Tranport Overhead Extraction........................................................422

Figure 26 RX Section DCC Timing................................................................................423

Figure 27 RX Line DCC Timing..................................................................................... 423

Figure 28 Transmit Transport Overhead Insertion ........................................................ 424

Figure 29 TX Section DCC Output Timing For D1-D3 ..................................................425

Figure 30 TX Line DCC Output Timing For D4-D12 .....................................................425

Figure 31 Receive Path Overhead Extraction/Alarm Timing ........................................ 426

Figure 32 Receive Tandem Connect Maintenance Insertion Timing ............................428

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use xv

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Figure 33 Receive Ring Control Port.............................................................................429

Figure 34 Receive Path Alarm Port Timing ...................................................................431

Figure 35 Transmit Ring Control Port............................................................................432

Figure 36 Transmit Alarm Port Timing ..........................................................................433

Figure 37 STS-3 (STM-1/AU-3) 19.44 MHz Byte Drop Bus Timing ..............................434

Figure 38 STS-3c (STM-1/AU-4) 19.44 MHz Byte Drop Bus Timing ............................ 435

Figure 39 STS-12 (STM-4/AU-3) 77.76 MHz Byte Drop Bus Timing ............................436

Figure 40 STS-3 (STM-1/AU-3) 19.44 MHz Byte Add Bus Timing ...............................437

Figure 41 STS-3 (STM-1/AU-3) 19.44 MHz Byte Add Bus (AFP) Timing .....................438

Figure 42 STS-3c (STM-1/AU-4) 19.44 MHz Byte Add Bus Timing .............................439

Figure 43 STS-3c (STM-1/AU-4) 19.44 MHz Byte Add Bus (AFP) Timing...................440

Figure 44 STS-12 (STM-12/AU-3) 77.76 MHz Byte Add Bus Timing ........................... 441

Figure 45 STS-12 (STM-12/AU-3) 77.76 MHz Byte Add Bus (AFP) Timing.................442

Figure 46 System Drop Side Path AIS Control Port Timing..........................................443

Figure 47 System Add Side Path AIS Control Port Timing ...........................................444

Figure 48 Microprocessor Interface Read Access Timing (Intel Mode) ........................449

Figure 49 Microprocessor Interface Read Access Timing (Motorola Mode).................450

Figure 50 Microprocessor Interface Write Access Timing (Intel Mode) ........................452

Figure 51 Microprocessor Interface Write Access Timing (Motorola Mode).................453

Figure 52 - RSTB Timing Diagram ..................................................................................455

Figure 53 Receive Line Output Timing.......................................................................... 456

Figure 54 Receive Path Overhead and Alarm Port Output Timing...............................457

Figure 55 Ring Control Port Output Timing...................................................................458

Figure 56 Receive Tandem Connection Input Timing. ..................................................459

Figure 57 Telecom Drop Bus Input Timing ...................................................................459

Figure 58 Telecom Drop Bus Output Timing................................................................. 460

Figure 59 System DROP-side Path Alarm Input Timing ...............................................461

Figure 60 System ADD-side Path Alarm Input Timing ..................................................462

Figure 61 Telecom Add Bus Input Timing .....................................................................463

Figure 62 Transmit Alarm Port Input Timing .................................................................464

Figure 63 Transmit Transport Overhead Input Timing .................................................. 464

Figure 64 Transmit Ring Control Port Input Timing....................................................... 465

Figure 65 Transmit Overhead Output Timing................................................................ 466

Figure 66 JTAG Port Interface Timing...........................................................................467

Figure 67 Theta Ja vs. Airflow Plot................................................................................469

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use xvi

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Figure 68 Mechanical Drawing 520 Pin Super Ball Grid Array (SBGA)........................470

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use xvii

Document ID: PMC-1990822, Issue 4

1 Features

1.1 General

• Monolithic four channel SONET/SDH Payload Extractor/Aligner for use in STS-3 (STM-

1/AU-3) or STS-3c (STM-1/AU-4) interface applications, operating at serial interface speeds

of 155.52 Mbit/s.

• Provides integrated clock recovery and clock synthesis for direct interfacing with optical

modules.

• On each channel, provides termination for SONET section and line, SDH Regenerator

Section and Multiplexer Section transport overhead, and path overhead of three STS-1 (STM0/AU-3) paths or a single STS-3c (STM-1/AU-4) path.

• On each channel, maps three STS-1 (STM-0/AU-3) payloads or a single STS-3c (STM-

1/AU-4) payload to the system timing reference, accommodating plesiochronous timing

offsets between the references through pointer processing.

• Provides Time Slot Interchange (TSI) function at the Telecom Add and Drop buses for

grooming 12 STS-1 (STM-0/AU-3) paths.

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

• On each channel, provides clear-channel mapping of three 49.536 Mbit/s or 48.384 Mbit/s

arbitrary data streams into an STS-3 (STM-1/AU-3) frame. Provides clear-channel mapping

of a single 149.76 Mbit/s arbitrary data stream into an STS-3c (STM-1/AU-4) frame.

• Supports line loopback from the line side receive stream to the transmit stream and diagnostic

loopback from a Telecom Add bus interface to a Telecom Drop bus interface.

• Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

• Provides a generic 8-bit microprocessor bus interface for configuration, control, and status

monitoring.

• Low power 3.3 V CMOS with TTL compatible digital inputs and CMOS/TTL digital outputs.

PECL inputs and outputs are 3.3 V and 5 V compatible.

• Industrial temperature range (-40 °C to +85 °C).

• 520 pin Super BGA package.

• Complies with Telcordia GR-253-CORE (1995) jitter tolerance, jitter transfer and intrinsic

jitter criteria.

1.2 SONET Section and Line/SDH Regenerator and Multiplexer

Section

• Frames to the STS-3/3c (STM-1/AU-3/AU-4) receive stream and inserts the framing bytes

(A1, A2) and the STS identification byte (J0) into the transmit stream; descrambles the

receive stream and scrambles the transmit stream.

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 1

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

• Calculates and compares the bit interleaved parity (BIP) error detection codes (B1, B2) for

the receive stream and calculates and inserts B1 and B2 in the transmit stream; accumulates

near end errors (B1, B2) and far end errors (M1) and inserts line remote error indications

(REI) into the Z2 (M1) growth byte based on received B2 errors.

• Detects signal degrade (SD) and signal fail (SF) threshold crossing alarms based on received

B2 errors.

• Extracts and serializes the order wire channels (E1, E2), the data communication channels

(D1-D3, D4-D12) and the section user channel (F1) from the receive stream, and inserts the

corresponding signals into the transmit stream.

• Extracts and serializes the automatic protection switch (APS) channel (K1, K2) bytes,

filtering and extracting them into internal registers for the receive stream. Inserts the APS

channel into the transmit stream.

• Extracts and filters the synchronization status message (Z1/S1) byte into an internal register

for the receive stream. Inserts the synchronization status message (Z1/S1) byte into the

transmit stream.

• Extracts a 64-byte or 16-byte section trace (J0) message using an internal register bank for the

receive stream. Detects an unstable section trace message or mismatch with an expected

message, and optionally inserts Line and Path AIS on the system Drop side upon either of

these conditions. Inserts a 64-byte or 16-byte section trace (J0) message using an internal

register bank for the transmit stream.

• Detects loss of signal (LOS), out-of-frame (OOF), loss-of-frame (LOF), line remote defect

indication (RDI), line alarm indication signal (LAIS), and protection switching byte failure

alarms on the receive stream. Optionally returns line RDI in the transmit stream.

• Provides a transmit and receive ring control port, allowing alarm and maintenance signal

control and status to be passed between mate SPECTRA-155s for ring-based Add/Drop

multiplexer and line multiplexer applications.

• Configurable to force Line AIS in the transmit stream.

1.3 SONET Path / SDH High Order Path

• Accepts a multiplex of three STS-1 (STM-0/AU-3) streams or a single STS-3c (STM-1/AU-

4) stream, interprets the STS (AU) pointer bytes (H1, H2, and H3), extracts the synchronous

payload envelope(s) and processes the path overhead for the receive stream.

• Constructs a byte serial multiplex of three STS-1 (STM-0/AU-3) streams or an STS-3c

(STM-1/AU-4) stream on the transmit side.

• Detects loss of pointer (LOP), loss of tributary multiframe (LOM), path alarm indication

signal (PAIS) and path (auxiliary and enhanced) remote defect indication (RDI) for the

receive stream. Optionally inserts PAIS, path RDI in the transmit stream.

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 2

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

• Extracts and serializes the entire path overhead from the three STS-1 (STM-0/AU-3) or the

single STS-3c (STM-1/AU-4) receive streams. Inserts the path overhead bytes in the three

STS-1 (STM-0/AU-3) or single STS-3c (STM-1/AU-4) stream for the transmit stream. The

path overhead bytes may be sourced from internal registers or from bit serial path overhead

input streams. Path overhead insertion may also be disabled.

• Extracts the received path signal label (C2) byte into an internal register and detects for path

signal label unstable and for signal label mismatch with the expected signal label that is

downloaded by the microprocessor. Inserts the path signal label (C2) byte from an internal

register for the transmit stream.

• Extracts a 64-byte or 16-byte path trace (J1) message using an internal register bank for the

receive stream. Detects an unstable path trace message or mismatch with an expected

message, and inserts Path RAI upon either of these conditions. Inserts a 64-byte or 16-byte

path trace (J1) message using an internal register bank for the transmit stream.

• Detects received path BIP-8 and counts received path BIP-8 errors for performance

monitoring purposes. BIP-8 errors are selectable to be treated on a bit basis or block basis.

Optionally calculates and inserts path BIP-8 error detection codes for the transmit stream.

• Counts received path REIs for performance monitoring purposes. Optionally inserts the path

REI count into the path status byte (G1) basis on bit or block BIP-8 errors detected in the

receive path. Reporting of BIP-8 errors is on a bit or block bases independent of the

accumulation of BIP-8 errors.

• Maintains the existing tributary multiframe sequence on the H4 byte until a new phase

alignment has been verified.

• Provides a serial alarm port communication of path REI and path RDI alarms to the transmit

stream of a mate SPECTRA-4x155 in the returning direction.

• Maintains the existing tributary multiframe sequence on the H4 byte until a new phase

alignment has been verified.

1.4 System Side Interfaces

• Supports TelecomBus interfaces by indicating/accepting the location of the STS identification

byte (C1), optionally the path trace byte(s) (J1), optionally the first tributary overhead byte(s)

(V1), and all synchronous payload envelope (SPE) bytes in the byte serial stream.

• Configurable to support four 19.44 MHz byte TelecomBus interfaces or a single 77.76 MHz

byte TelecomBus interface.

• For TelecomBus interface, accommodates phase and frequency differences between the

receive/transmit streams and the Add/Drop buses via pointer adjustments.

• Provides TSI function to interchange or groom 12 STS-1 (STM-0/AU-3) paths or four STS-

3/3c (STM-1/AU-3/AU-4) paths at the Telecom Add/Drop buses.

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 3

Document ID: PMC-1990822, Issue 4

2 Applications

• SONET/SDH Add Drop Multiplexers

• SONET/SDH Terminal Multiplexers

• SONET/SDH Line Multiplexers

• SONET/SDH Cross Connects

• SONET/SDH Test Equipment

• Switches and Hubs

• Routers

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 4

Document ID: PMC-1990822, Issue 4

3 References

• American National Standard for Telecommunications - Digital Hierarchy - Optical Interface

Rates and Formats Specification, ANSI T1.105-1991.

• American National Standard for Telecommunications - Layer 1 In-Service Digital

Transmission Performance Monitoring, T1X1.3/93-005R1, April 1993.

• Committee T1 Contribution, "Draft of T1.105 - SONET Rates and Formats", T1X1.5/94-

033R2-1994.

• Telcordia - GR-253-CORE “SONET Transport Systems: Common Generic Criteria”, Issue 2

Revision 1, January 1995.

• Telcordia - GR-436-CORE “Digital Network Synchronization Plan”, Issue 1 Revision 1, June

1996.

• ETS 300 417-1-1, "Generic Functional Requirements for Synchronous Digital Hierarchy

(SDH) Equipment", January, 1996.

• ITU-T Recommendation G.703 - "Physical/Electrical Characteristics of Hierarchical Digital

Interfaces", 1991.

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

• ITU-T Recommendation G.704 - "General Aspects of Digital Transmission Systems;

Terminal Equipment - Synchronous Frame Structures Used At 1544, 6312, 2048, 8488 and 44

736 kbit/s Hierarchical Levels", July, 1995.

• ITU, Recommendation G.707 - "Network Node Interface For The Synchronous Digital

Hierarchy", 1996.

• ITU Recommendation G.781, - “Structure of Recommendations on Equipment for the

Synchronous Digital Hierarchy (SDH)”, January, 1994.

• ITU Recommendation G.783, “Characteristics of Synchronous Digital Hierarchy (SDH)

Equipment Functional Blocks”, 28 October, 1996.

• ITU Recommendation O.151, “Error Performance measuring Equipment Operating at the

Primary Rate and Above”, October, 1992.

• ITU Recommendation I.432, “ISDN User Network Interfaces”, March 93.

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 5

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

4 Document Conventions & Definitions

The following conventions are used along this document:

SIGNAL1-4: designated equivalent signals, either input our output. Each of these signals

applies to the corresponding device channel.

SIGNAL±:: designate a differential signal.

SIGNAL[N:0]: designate a bus of N+1 bit wide, bit N being the MSB, bit 0 the LSB.

The following table defines the abbreviations used in this document:

APGM Add Bus PRBS Generator/Monitor

BIP Bit Interleaved Parity

CRSI CRU and SIPO

CRU Clock Recovery Unit

CSPI CSU and PISO

CSU Clock Synthesis Unit

DPGM Drop Bus PRBS Generator/Monitor

LAIS Line Alarm Indication Signal

LOF Loss of Frame

LOM Loss of Tributary Multiframe

LOP Loss of Pointer

LOS Loss of Signal

MSB Most Significant Bit

OOF Out-Of-Frame

OOM Out-Of-Multiframe State

PAIS Path Alarm Indication Signal

PDLE Parallel Diagnostic Loop

PLL Phase Locked Loop

PISO Parallel to Serial Converter

PRBS Pseudo Random Bit/Byte Sequence

RASE Receive APS, Synchronization Extractor and Bit Error Monitor

RDI Remote Defect Indication

REI Remote Error Indication

RLOP Receive Line Overhead Processor

RTOC Receive Transport Overhead Controller

RPOP Receive Path Overhead Processor

RSOP Receive Section Overhead Processor

RTAL Receive Telecom Aligner

Production

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 6

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

SD Signal Degrade

SF Signal Fail

SDLE Serial Diagnostic Loopback

SIPO Serial-to-parallel Converter

SLLB System Side Line Loopback

SPE Synchronized Payload Envelope

SPTB SONET/SDH Path Trace Buffer

SSTB SONET/SDH Section Trace Buffer

TAP Test Access Port

TLOP Transmit Line Overhead Processor

TPOP Transmit Path Overhead Processor

TPPS Transmit Path Processing Slice

TPIP Transmit Pointer Interpreter

TSI Timeslot Interchange

TSOP Transmit Section Overhead Processor

TTAL Transmit Telecom Aligner

TTOC Transmit Transport Overhead Controller

WANS Wide Area Network Synchronization Controller

Production

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 7

Document ID: PMC-1990822, Issue 4

5 Application Examples

The PM5316 SPECTRA-4x155 is designed for use in various SONET/SDH network elements

including switches, terminal multiplexers, and Add/Drop multiplexers. In these applications, the

line interface of the SPECTRA-4x155 typically interfaces directly with the electrical optical

modules and the system side interface connects directly with a TelecomBus.

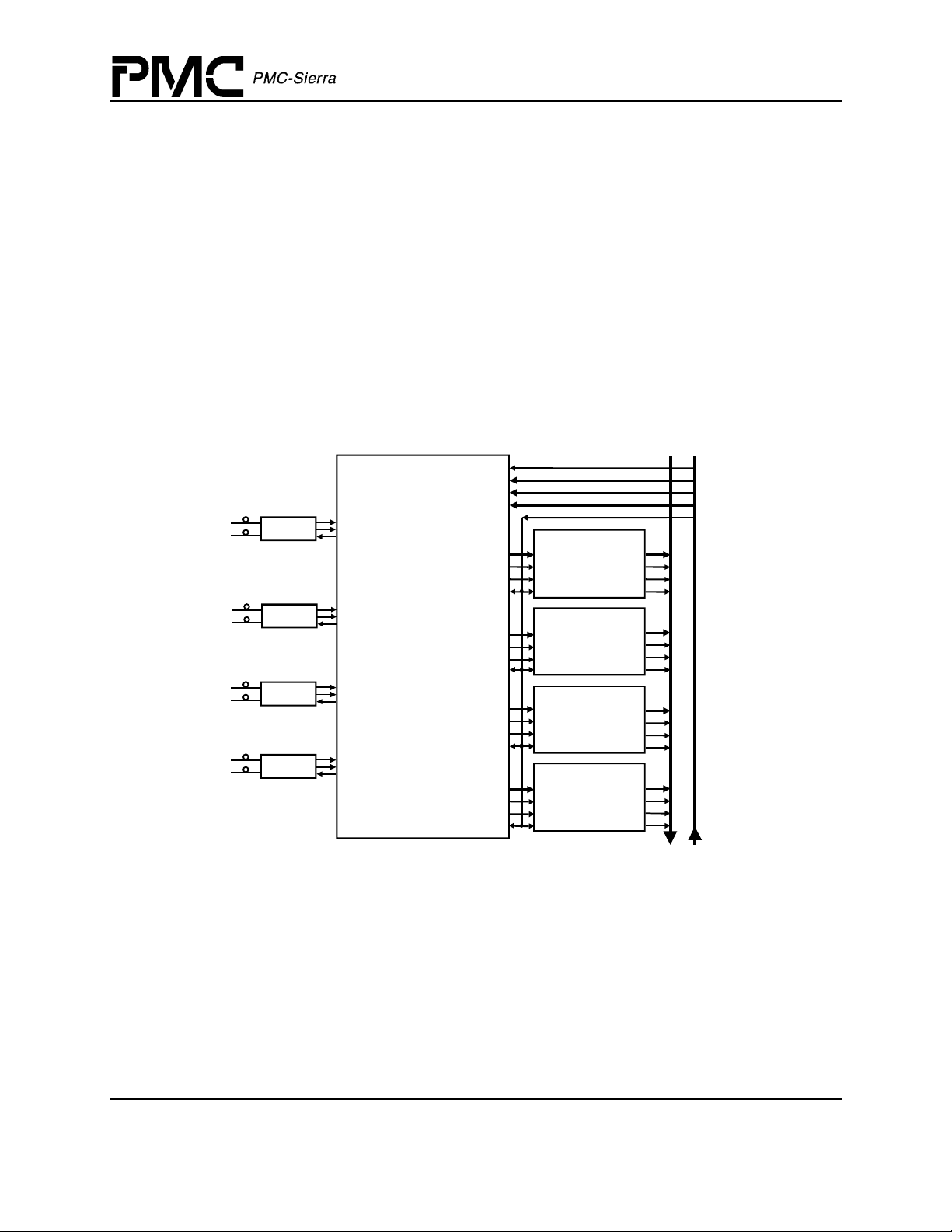

Figure 1 shows how the SPECTRA-4x155 is used to implement four 155 Mbit/s aggregate

interfaces. In this application, the SPECTRA-4x155 performs SONET/SDH section, line, and

path termination and the PM5362 TUPP-PLUS performs tributary pointer processing and

performance monitoring.

Figure 1 STS-3 (STM-0/AU-3) or STS-3c (STM-1/AU-4) Application with 19.44 MHz Byte

TelecomBus Interface

155 Mbits

Optical

Interface

155 Mbits

Optical

Interface

155 Mbits

Optical

Interface

155 Mbits

Optical

Interface

Optica l

Transceiver

Optica l

Transceiver

Optica l

Transceiver

Optica l

Transceiver

RXD1+/SD1

TXD1+/-

RXD2+/SD2

TXD2+/-

RXD3+/SD3

TXD3+/-

RXD4+/SD4

TXD4+/-

PM5316

SPECTRA-4x155

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

ACK

AD[31:0], ADP[4:1]

AC1J1V1[4:1]

APL[4:1]

PM5362

DD[31:24], DDP[4]

DC1J1V1[4]

DPL[4]

DCK

DD[23:16], DDP[3]

DC1J1V1[3]

DPL[3]

DCK

DD[15:8], DDP[2]

DC1J1V1[2]

DPL[2]

DCK

DD[7:0], DDP[1]

DC1J1V1[1]

DPL[1]

DCK

ID[7:0], IDP

IC1J 1

IPL

SCLK

ID[7:0], IDP

IC1J 1

IPL

SCLK

ID[7:0], IDP

IC1J 1

IPL

SCLK

ID[7:0], IDP

IC1J 1

IPL

SCLK

TUPP-PLUS

PM5362

TUPP-PLUS

PM5362

TUPP-PLUS

PM5362

TUPP-PLUS

OD[7:0], ODP

OTV5

OTPL

TPOH

OD[7:0], ODP

OTV5

OTPL

TPOH

OD[7:0], ODP

OTV5

OTPL

TPOH

OD[7:0], ODP

OTV5

OTPL

TPOH

Four

19.44 M Hz

8-bit

IEEE P1396

Telecombus

Interfaces

Drop Add

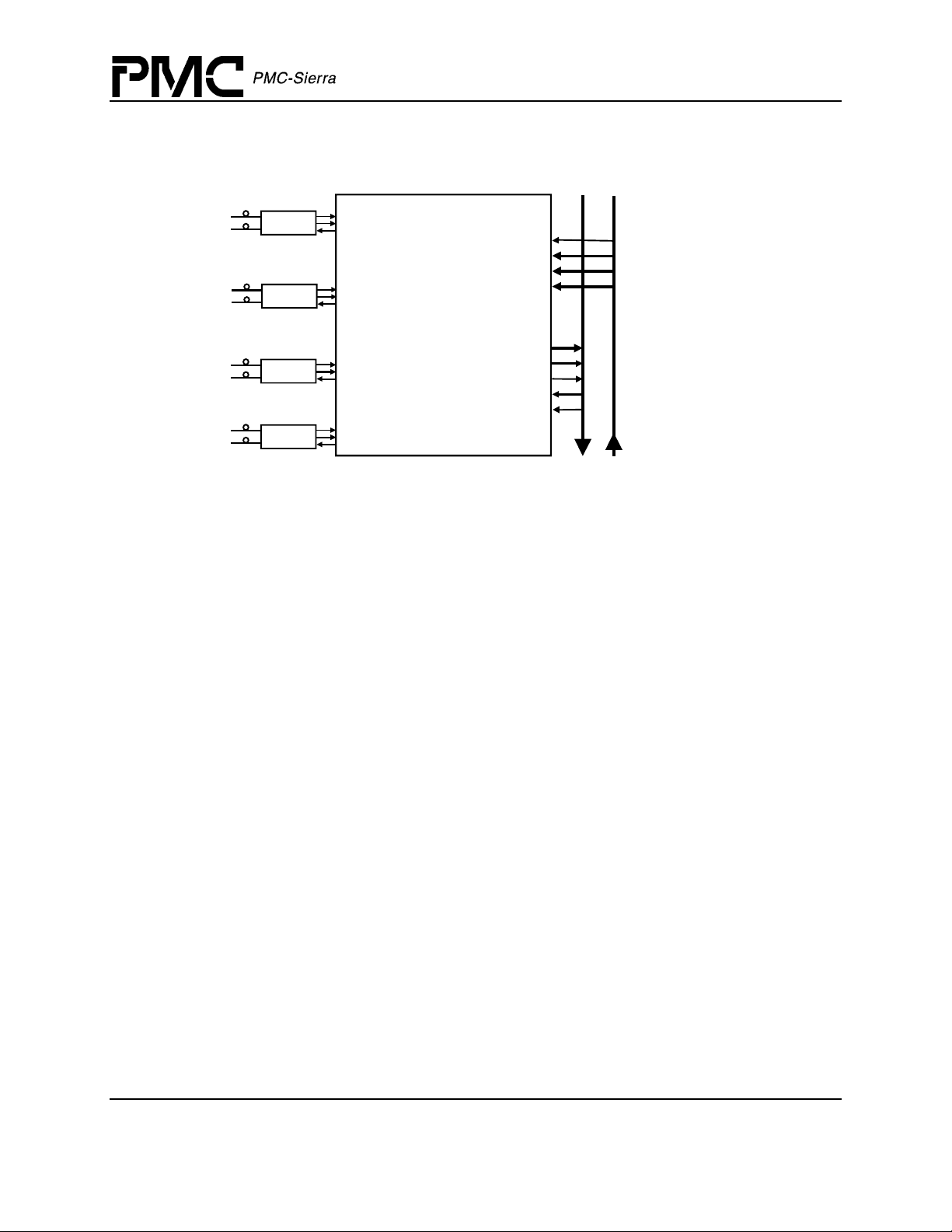

The system side interface of the SPECTRA-4x155 can be configured to have a 77.76 MHz byte

TelecomBus interface. Figure 2 shows how the SPECTRA-4x155 is used to implement a 622

Mbit/s aggregate interface using the high-speed TelecomBus on the system side interface. In this

application, the SPECTRA-4x155 performs SONET/SDH section, line, and path termination.

Proprietary and Confidential to PMC-Sierra, Inc. and for its customers’ internal use 8

Document ID: PMC-1990822, Issue 4

SONET/SDH Payload Extractor/Aligner (SPECTRA-4x155)

Production

Figure 2 STS-3 (STM-1/AU-3) or STS-3c (STM-1/AU-4) Application with 77.76 MHz Byte

TelecomBus Interface

155 Mbits

Optical

Interface