PMC-Sierra,Inc.

SPECTRA-4x155

Quad Channel 155 Mbit/s SONET/SDH Framer and Aligner

PM5316

FEATURES

• Monolithic four channel SONET/SDH

Payload Extractor/Aligner for use in

STS-3 (STM-1/AU-3) or STS-3c (STM1/AU-4) interface applications,

operating at serial interface speeds of

155.52 Mbit/s.

• Provides integrat ed clock re covery and

clock synthesis to allow direct interface

to optical modules.

• Each channel provides termination for

SONET Section and Line, SDH

Regenerator Section and Multiplexer

Section transport overhead, and path

overhead of three STS-1 (STM-0/AU-

3) paths or a single STS-3c (STM1/AU-4) path.

• Each channel maps three STS-1

(STM-0/AU-3) payloads or a single

STS-3c (STM -1/AU-4) payload to

system timing reference,

accommodating plesiosynchronous

timing offsets between the references

through pointer processing.

• The entire SONET/SDH transport and

path overheads are extracted to and

inserted from dedicated pins.

• Frames to the SONET/SDH receive

stream and inserts framing bytes and

STS identification into the transmit

stream and processes or inserts the

transport overhead.

• Interprets or generates the STS (AU)

pointer bytes (H1, H2, H3), extracts or

inserts the synchronous payload

envelope(s) and processes or inserts

the path overhead.

• Supports Automatic Protection

Switching (APS):

• Ring control port communication of

path REI and path RDI alarms;

• Filters the APS channel (K1,K2)

bytes into internal registers; inserts

the APS channel into the transmit

stream.

• Provides Time Slot Interchange (TSI)

function at the ADD and DROP

TelecomBus Interfaces for groomi ng

twelve STS-1 (STM-0/AU-3) paths.

• Supports line loopback from the line

side receive stream to the transmit

stream and diagnostic loo pba ck from

an ADD TelecomBus interface to a

DROP TelecomBus interface.

• Provides a standard five signal

P1149.1 JTAG test port for boundary

scan board test purposes.

• Provides a generic 8-bit

microprocessor bus interface for

configuration, contro l, and sta tus

monitoring.

• Low power 3.3 V CMOS with TTL

compatible digital inputs and

CMOS/TTL digital outputs.

• Industrial temperature range (-40°C to

+85°C).

• 520 pin Super BGA package.

• Supports clock recovery bypass for

use in applications where external

clock recovery is desired.

• Complies with Bellcore GR-253-CORE

jitter tolerance, jitter transfer, and

intrinsic jitter criteria.

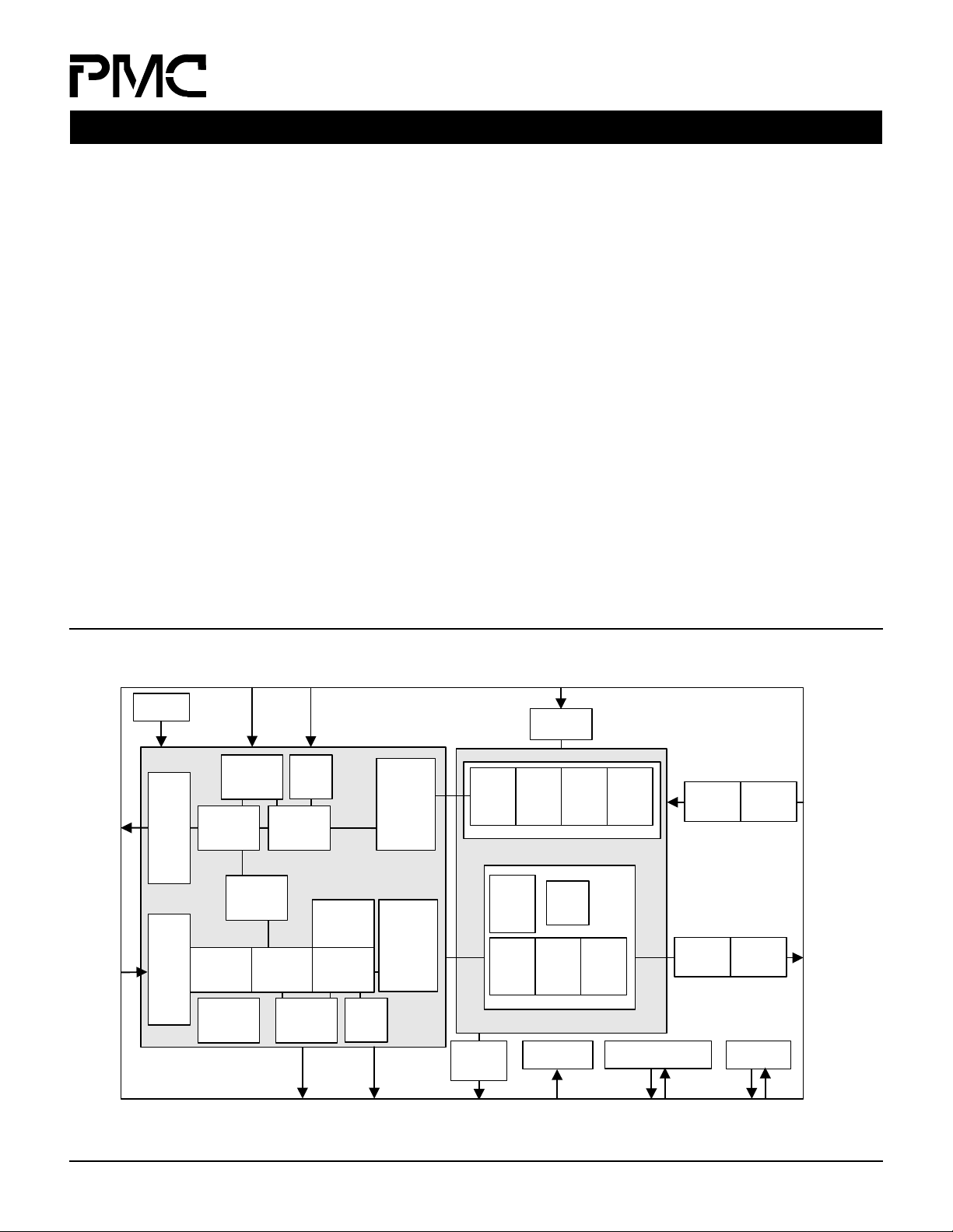

BLOCK DIAGRAM

Clock

Synthesis

Channel Line

Side Top x 4

4 x Serial

155.52 Mbit/s

4 x Serial

155.52 Mbit/s

Tx Line

Interface

Rx Line

Interface

Tx Transport

Tx Section

OH

Processor

Clock and

Data

Recovery

WAN Syn-

chronization

Controller

Transmit

Transport

O/H

Overhead

Controller

Section

Trace Buffer

Rx Section

Processor

Control and

Status

Information

Tx Ring

Control

Port

Tx Line OH

Processor

OH

Rx Transport

Overhead

Controller

Rx APS Synchronization

Extractor and

Bit Error

Monitor

Rx Line OH

Processor

Rx Ring

Control

Port

Tx Re-

Mulitplexer

Rx De-

Mulitplexer

Transmit

Overhead

Tx Path O/H

Controller

Path Processing Slice x 12

Path

Trace

Buffer

Rx Path

O/H

Processor

Tx

Telecom

Aligner

DPAIS and

Telecom

Aligner

TPAIS

Tx Path

O/H

Processor

Transmit Path Processing Slice

Receive Path Processing Slice

Rx Path O/H

Controller

Path

Add Bus

Generator/

PMON

Rx

PRBS

Monitor

Generator/

Drop Bus

PRBS

Monitor

Tx Pointer

Interpreter

(STS/

AU-TU3)

Rx Timeslot

Interchange

Microprocessor Interface

Tx Timeslot

Interchange

Tx

TelecomBus

System

Interface

Rx

TelecomBus

System

Interface

JTAG Test

Access Port

8-bit x 77.76 Mbit/s

TelecomBus

OR

4 x 8-bit x 19.44

Mbit/s TelecomBus

8-bit x 77.76 Mbit/s

TelecomBus

OR

4 x 8-bit x 19.44

Mbit/s TelecomBus

Receive O/H

Clock, Frame

Pulse, Receive

Transport

Overhead

PMC-2000327 (R2) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2001

Control

and Status

Information

Receive

Path

Overhead

Path AIS

Signals

8-bit

Microprocessor

Bus

Test Data

PM5316 SPECTRA-4x155

Quad Channel 155 Mbit/s SONET/SDH Framer and Aligner

APPLICATIONS

• Channelized STS-3/STM-1 Interfaces

for:

• Optical Cross Connects;

• Digital Cross Connects;

• Router and Switch Line Cards;

• ADM Aggregate Cards for TDM and

Multi-service applications;

• Terminal Multiplexers.

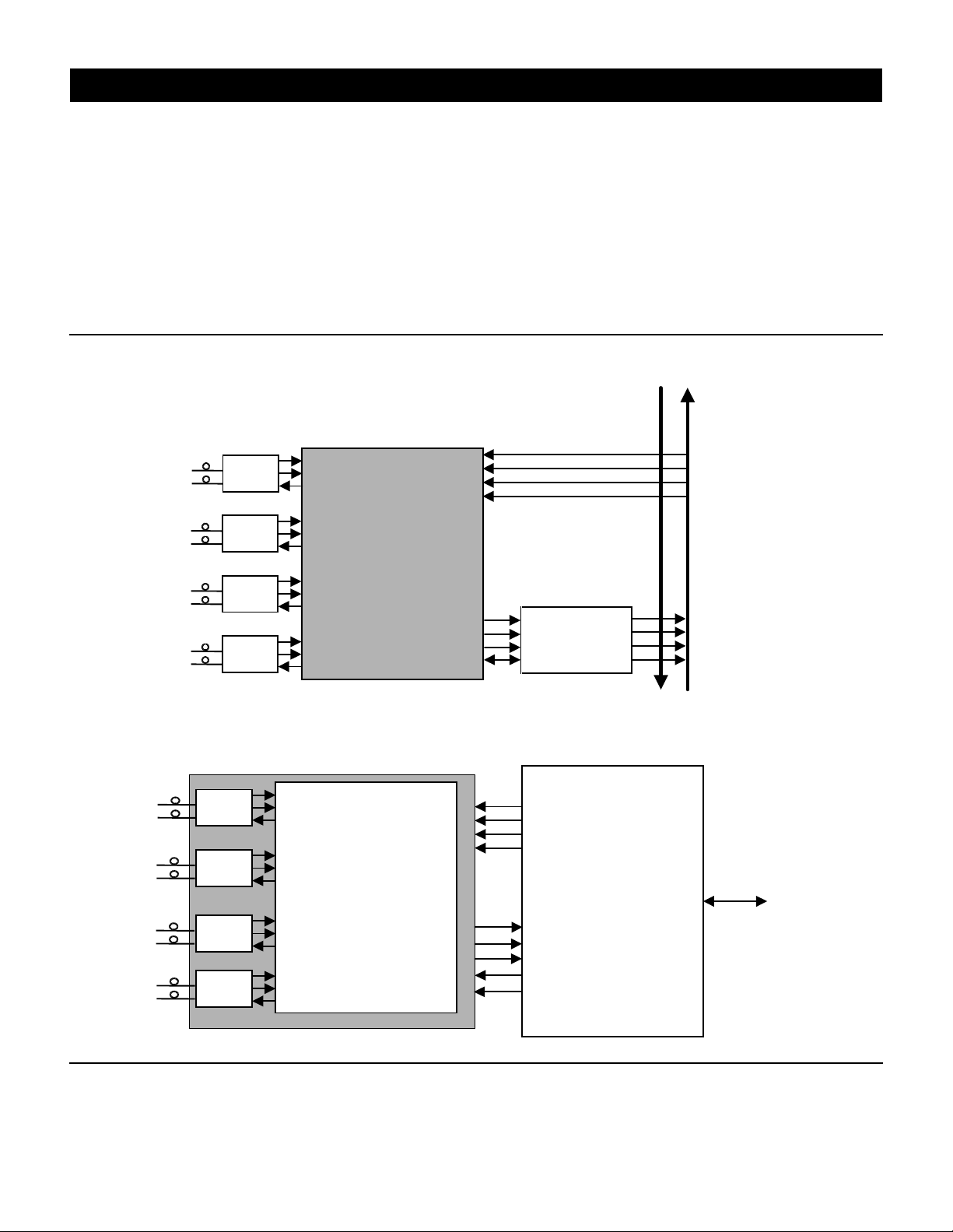

TYPICAL APPLICATIONS

STS-3/STM-0 APPLICATION WITH VT/TU POINTER PROCESSING/ALIGNMENT

8-bit x 77.76

Mbit/s

155.52 Mbit/s

Optical

Interface

155.52 Mbit/s

Optical

Interface

155.52 Mbit/s

Optical

Interface

155.52 Mbit/s

Optical

Interface

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

RXD1+/SD1

TXD1+/-

SPECTRA-4x155

RXD2+/SD2

TXD2+/-

RXD3+/SD3

TXD3+/-

RXD4+/SD4

TXD4+/-

AD[31:0], ADP[4:1]

PM5316

DD[31:0], DDP[4:1]

ACK

AJ0J1[4:1]

APL[4:1]

DJ0J1[4:1]

DPL[4:1]

DCK

ID[7:0], IDP

IC1J1

IPL

SCLK

16 X STS-3/STM-0 APPLICATION WITH POS/ATM PROCESSING

155.52 Mbit/s

Optical

Interface

155.52 Mbit/s

Optical

Interface

155.52 Mbit/s

Optical

Interface

155.52 Mbit/s

Optical

Interface

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

RXD1+/SD1

TXD1+/-

RXD2+/SD2

TXD2+/-

RXD3+/SD3

TXD3+/-

RXD4+/SD4

TXD4+/-

AD[31:0], ADP[4:1]

PM5316

SPECTRA-4x155

DD[31:0], DDP[4:1]

ACK

AJ0J1[4:1]

APL[4:1]

DJ0J1[4:1]

DPL[4:1]

DCK

DFP

x4

OD[7:0], ODP

OTV5

PM5363

TUPP+622

OTPL

TPOH

PM7390

S/UNI-MACH48

Drop

Cross-Connect

or Tributary

Add

To VT/TU

Cards

POS-PHY

Level 3/

UTOPIA

Level 3

To a

Datalink

Layer

Device

Head Office:

PMC-Sierra, Inc.

#105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

PMC-2000327 (R2)

© Copyrigh t PMC-Sierr a,

Inc. 2001. SPECTRA is a

trademark of PMC-Sierra,

Inc. All rights reserved.

Loading...

Loading...