PMC-Sierra,Inc.

PM5313

SPECTRA-622

SONET/SDH Payload Extractor/Aligner for 622 Mbit/s Interfaces

FEATURES

The SPECTRA-622 chip offers the

following features:

• Monolithic SONET/SDH

Payload-Extractor/Aligner for use in

STS-12 (STM-4/AU3 or STM-4/AU4) or

STM-12c (STM-4/AU4-4c) interface

applications that operate at serial

interface speeds up to 622.08 Mbit/s.

• Provides integrated clo ck recovery and

clock synthesis to allow a direct int erface

to optical modules.

• Complies with Bellcore GR-253-CORE

jitter tolerance and intrinsic jitter criteria.

• Provides control circuitry required to

comply with WAN clocking requirements

for wander, holdover, and long term

stability.

• Provides termination fo r SONET Section

and Line, and SDH Regenera tor Sectio n

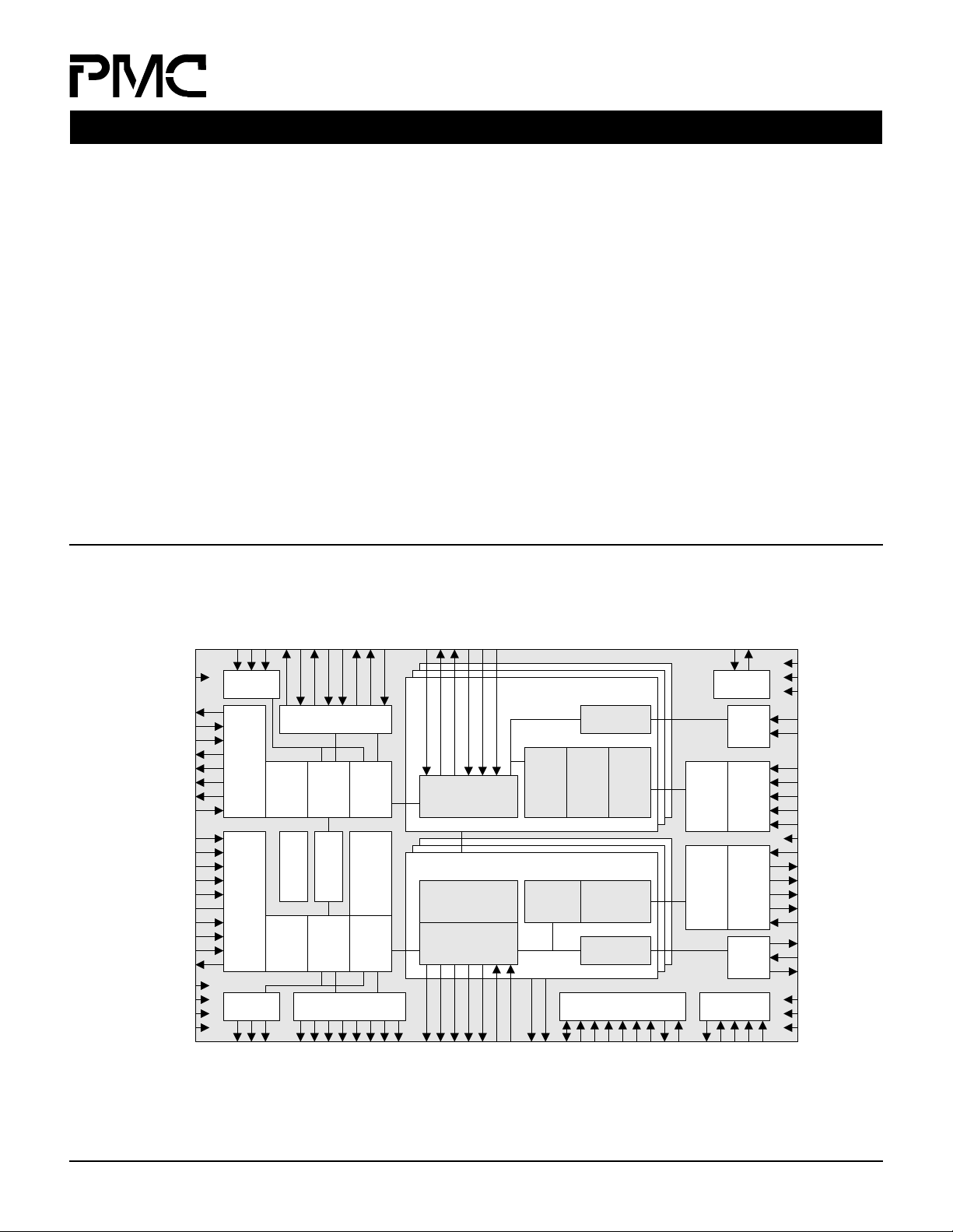

BLOCK

DIAGRAM

TSLD/TSOW/TSUC

TSLDCLK/TOWCLK

TLAIS/TRCPDAT

RLAIS/TRCPCLK

TCLK/PGMTCLK

TDREF/ TDREF1

RCLK/PGMRCLK

/TFP

TC1J1V1/TFPO

TFPI

TDCK

TXD+/-

TPL

TD[7:0]

TDP

PECLV

REFCLK+/-

RXD+/-

RRCLK+/-

SD

C0, C1

PICLK

PIN[7:0]

FPIN

OOF

ATP[1:0]

PREFEN

PECLREF

/RFP

TLRDI/TRCPFP

Tx Ring

Control Port

Tx Line Interface

Rx Line Interface

Rx Ring

Control Port

LOS/RRCPFP

LAIS/RRCPDAT

LRDI/RRCPCLK

Tx Transport O/H

Controller

Clock

Synthesis

Controller

WAN Sync

Clock

& Data

Recovery

Rx Transport O/H

LOF, SALM

TLDCLK/TOWCLK

Tx Section

Rx Section

RSLDCLK, ROWCLK

and Multiplexer Section

transport-overhead. Also provides

termination for Path overhead of twelve

STS-1 (STM-0/AU3) paths, four STS-3/

3c (STM-1/AU3/AU4) paths, or a single

STS-12c (STM-4/AU4-4c) path.

• Maps twelve STS-1 (STM-0/AU3)

payloads, four STS-3/3c (STM-1/AU3/

AU4) payloads , or a single STS-12c

(STM-4/AU4-4c) payload to system

timing references. This accommodates

plesiochronous timing offsets between

the references.

• Maps twelve DS3 bit-streams into an

STS-12 (STM-4/AU3) frame.

• Configurable on an STS-1 basis to

support a mix of traffi c from the DS-3 a nd

Telecom inte rfac es .

• Provides a Time-Slot Interchange (TSI)

function on the Telecom Add and Drop

buses for grooming twelve STS-1

TTOHEN

TTOHCLK

TTOHFP

TTOH/TTOHREI

TLD/TLOW/TOH

O/H

Processor

Tx Line O/H

Buffer

Section Trace

Extractor &

Rx APS Synch

O/H

Processor

Rx Line O/H

Controller

RTOH

RLD, RLOW, ROH

RLDCLK, ROHCLK

RSLD, RSOW, RSUC

Processor

Processor

TPOH

TPOHFP

Tx Path O/H

Processor

RTOHFP

RTOHCLK

Path Trace Buffer

Rx Path O/H

Processor

RPOH

RPOHFP

Bit Error Monitor

TPOHRDY

TAD/TAFP/TACK

TPOHEN

TPOHCLK

Transmit Path Processing Slice x12

Tx Telecom

Receive Path Processing Slice x12

Rx Telecom

Aligner

RTCEN

B3E

RTCOH

RPOHCLK

RALM

RPOHEN

DS3 Mapper

Add Side

Aligner

RAD

Monitor

Generator/

Add Bus PRBS

Drop Bus PRBS

Generator/

Monitor

DS3 Mapper

Drop Side

Microprocessor Interface

ALE

CSB

D[7:0]

A[13:0]

(STM-0/AU3) paths or four STS-3/3c

(STM-1/AU3/AU4) paths.

• Supports line loopbac k and diagnostic

loopback.

• Supports OC-4 8 (STM-16) applications

with byte interfaces for connection to

an OC-48 front-end device.

23

• Supports diagnostic 2

-1

pseudo-random bit-sequence (PRBS)

generation and monitoring.

• Provides a standard JTAG test-port for

boundary scan board-test purposes.

• Provides a generic 8-bit

microprocessor bus-interface.

• Low-power 3.3V CMO S with TTL

compatible inputs and CMOS/TTL

digital outputs. PECL inputs and

outputs are 3.3V and 5V compa tib le.

• Available in a 520-pin SBGA package.

• Supports industria l temp erat ure-ra ng e

(-40°C to 85°C) operation.

SCPI[3:0]

SCPO[1:0]

TPAISCK

I/F

Interface

I/F

TRSTB

TPAISFP

TPAIS

DS3TICLK [12:1]

DS3TDAT [12:1]

AC1J1V1[4:1]/

AFP[4:1]

ACK

APL[4:1]

AD[31:0]

ADP[4:1]

DMODE[1:0]

DCK

DC1J1V1[4:1]

DPL[4:1]

DD[31:0]

DDP[4:1]

DFP

DS3ROCLK [12:1]

DS3RICLK

DS3RDAT [12:1]

DPAISCK

DPAISFP

DPAIS

Tx Pointer

Interpreter

RDB/E

WRB, RWB

Serial

Control Port

System

Tx DS3

Interchange

Tx Telecombus

Interchange

Rx Telecombus

Rx DS3

JTAG Test

Access Port

TDI

TCK

TDO

System

System Interface

System

TMS

Tx Timeslot

Rx Timeslot

INTB

RSTB

MBEB

PMC-1981271 (R4) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC. AND FOR IT’S CUSTOMERS’ INTERNAL USE 2001 PMC-Sierra, Inc.

PM5313 SPECTRA-622

SONET/SDH Payload Extractor/Aligner for 622 Mbit/s Interfaces

BACKPLANE/DEVICE MODES

• 77.76 MHz Telecom Byte

• 19.44 MHz Telecom Byte x 4

• Datacom DS-3 x 12

APPLICATIONS

Use the SPECTRA-622 chip in the

following applications:

• SONET/SDH Add/Drop Multiplexers

• Channelized Routers and Switches

• SONET/SDH Terminal Multiplexers

• SONET/SDH Digital Cross-Connects

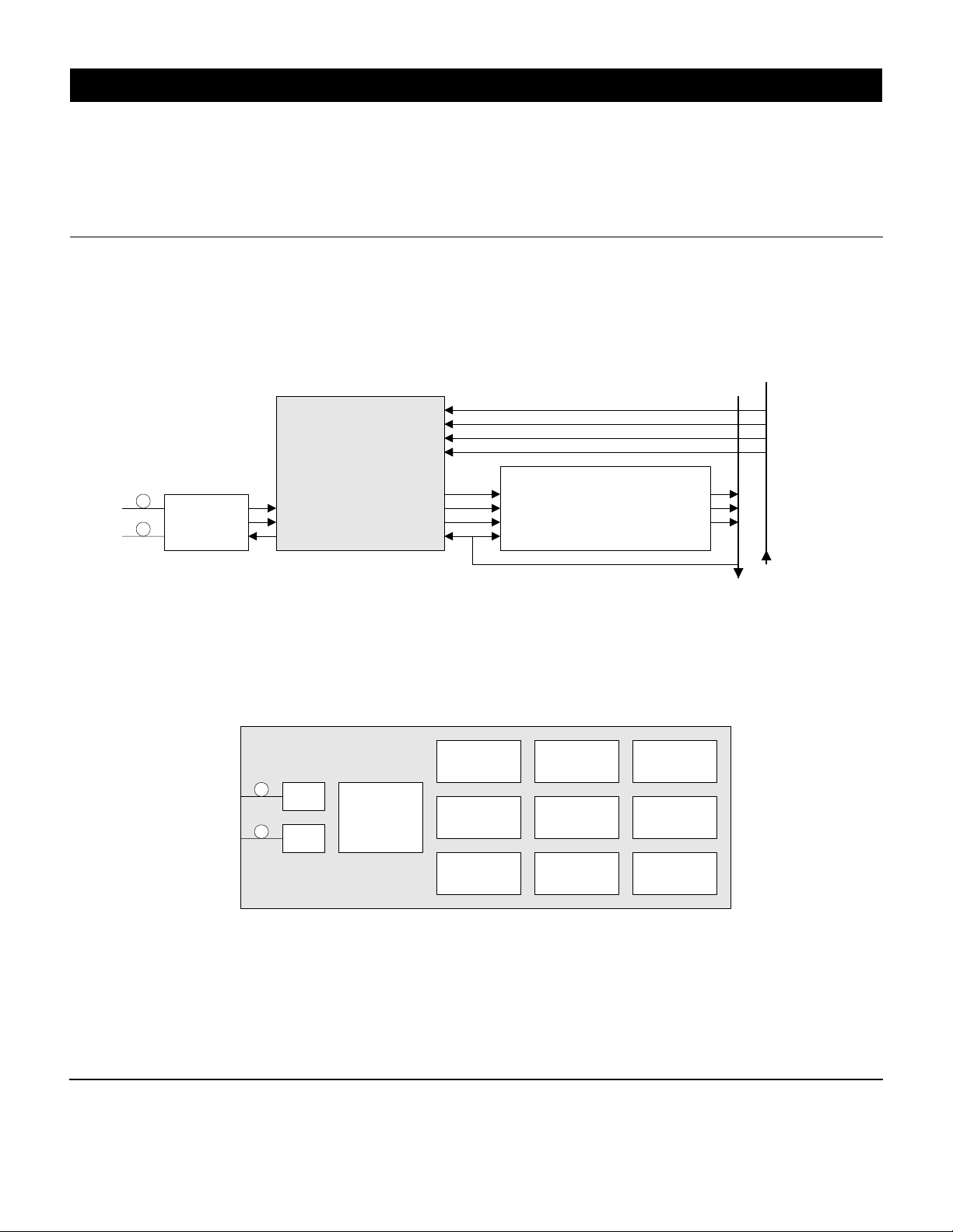

TYPICAL APPLICATIONS

STS-12/STM-4 AGGREGATE INTERFACE WITH TRIBUTARY POINTER PROCESSING AND PERFORMANCE MONITORING

77.76 MHz

8-Bit

High-Speed

Telecombus

Interface

Add

622 Mbit/s

Optical Interface

Optical

Transceiver

AD[7:0], ADP[1]

PM5313

SPECTRA-622

RXD +/SD

TXD +/-

DD[7:0], DDP[1]

AC1J1V1[1]

APL[1]

ACK

DC1J1V1[1]

DPL[1]

DCK

PM5363 TUPP+622

IC1J1[1]

ID[7:0], IDP[1]

IPL[1]

HSCLK

OC1J1V1[1]

OD[7:0], ODP[1]

OPL[1]

Drop

CHANNELIZED OC-12 INTERFACE FOR HIGH SPEED ROUTERS

622 Mbit/s

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

Optical

Interface

Channelized

OC-12 Card

Opt

Opt

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

SPECTRA-

622

S/UNI

QJET

S/UNI

QJET

S/UNI

QJET

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

FREEDM-8

FREEDM-8

FREEDM-8

FREEDM-8

FREEDM-8

FREEDM-8

Bus

Interface

PMC-1981271 (R4)

2001 PMC-Sierra, Inc.

FREEDM-8 is a trademark of

PMC-Sierra, Inc.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC. AND FOR IT’S CUSTOMERS’ INTERNAL USE

Loading...

Loading...