PMC PM4388-NI, PM4388-RI Datasheet

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

PM4388

TOCTL

OCTAL T1 FRAMER

DATASHEET

ISSUE 5: NOVEMBER 1998

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................3

3 REFERENCES.........................................................................................4

4 APPLICATION EXAMPLES......................................................................5

5 BLOCK DIAGRAM....................................................................................6

6 DESCRIPTION.........................................................................................7

7 PIN DIAGRAM..........................................................................................8

8 PIN DESCRIPTION................................................................................10

9 FUNCTIONAL DESCRIPTION...............................................................20

9.1 FRAMER (FRMR)........................................................................20

9.2 FRAMER/SLIP BUFFER RAM (FRAM).......................................20

9.3 INBAND LOOPBACK CODE DETECTOR (IBCD).......................21

9.4 PERFORMANCE MONITOR COUNTERS (PMON)....................21

9.5 BIT ORIENTED CODE DETECTOR (RBOC)..............................21

9.6 RDLC FACILITY DATA LINK RECEIVER.....................................22

9.7 ALARM INTEGRATOR (ALMI).....................................................23

9.8 ELASTIC STORE (ELST)............................................................23

9.9 SIGNALING EXTRACTOR (SIGX)...............................................24

9.10 RECEIVE PER-DS0 SERIAL CONTROLLER (RPSC)................24

9.11 INGRESS INTERFACE (IIF)........................................................25

9.12 PATTERN DETECTOR/GENERATOR (PRGD)............................27

9.13 BASIC TRANSMITTER (XBAS)...................................................28

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

9.14 TRANSMIT PER-DS0 SERIAL CONTROLLER (TPSC)..............29

9.15 SIGNALING ALIGNER (SIGA).....................................................29

9.16 INBAND LOOPBACK CODE GENERATOR (XIBC).....................29

9.17 BIT ORIENTED CODE GENERATOR (XBOC)............................29

9.18 TDPR FACILITY DATA LINK TRANSMITTER..............................30

9.19 RECEIVE AND TRANSMIT DIGITAL JITTER ATTENUATOR (RJAT,

TJAT)............................................................................................31

9.20 TIMING OPTIONS (TOPS)..........................................................35

9.21 EGRESS INTERFACE (EIF)........................................................35

9.22 MICROPROCESSOR INTERFACE (MPIF) .................................37

10 REGISTER DESCRIPTION....................................................................38

11 NORMAL MODE REGISTER DESCRIPTION........................................42

12 TEST FEATURES DESCRIPTION.......................................................191

12.1 TEST MODE 0...........................................................................193

12.2 JTA G TEST PORT......................................................................197

13 FUNCTIONAL TIMING DIA GRAMS .....................................................200

14 OPERATIONS.......................................................................................207

14.1 CONFIGURING THE T OCTL FR OM RESET.............................207

14.2 USING THE INTERNAL FDL TRANSMITTER...........................210

14.3 USING THE INTERNAL FDL RECEIVER..................................214

14.4 USING THE PRGD PATTERN GENERATOR/DETECTOR........218

14.5 USING THE LOOPBACK MODES.............................................223

14.5.1LINE LOOPBACK............................................................223

14.5.2DIAGNOSTIC DIGITAL LOOPBACK...............................224

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

14.5.3PER-DS0 LOOPBACK....................................................225

14.6 USING THE PER-DS0 SERIAL CONTROLLERS......................226

14.6.1INITIALIZATION ..............................................................226

14.6.2DIRECT ACCESS MODE ...............................................226

14.6.3INDIRECT ACCESS MODE............................................227

14.7 USING THE TRANSMIT DIGITAL JITTER ATTENUATOR.........228

14.7.1DEFAULT APPLICATION.................................................228

14.7.2DATA BURST APPLICATION ..........................................228

14.7.3ELASTIC STORE APPLICATION....................................229

14.7.4ALTERNATE TLCLK REFERENCE APPLICATION.........229

14.8 ISOLATING AN INTERRUPT ....................................................229

14.9 USING THE PERFORMANCE MONITOR COUNTER VALUES230

14.10 JTAG SUPPORT........................................................................232

15 ABSOLUTE MAXIMUM RATINGS........................................................243

16 D .C. CHARACTERISTICS..................................................................244

17 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS ......246

18 TOCTL I/O TIMING CHARACTERISTICS............................................251

19 ORDERING AND THERMAL INFORMATION ......................................263

20 MECHANICAL INFORMATION.............................................................264

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

LIST OF REGISTERS

REGISTERS 000H, 080H, 100H, 180H, 200H, 280H, 300H, 380H: RECEIVE

LINE OPTIONS ......................................................................................43

REGISTERS 001H, 081H, 101H, 181H, 201H, 281H, 301H, 381H: INGRESS

INTERFACE OPTIONS...........................................................................46

REGISTERS 002H, 082H, 102H, 182H, 202H, 282H, 302H, 382H: BACKPLANE

PARITY CONFIGURATION AND STATUS..............................................48

REGISTERS 003H, 083H, 103H, 183H, 203H, 283H, 303H, 383H: RECEIVE

INTERFACE CONFIGURATION .............................................................50

REGISTERS 004H, 084H, 104H, 184H, 204H, 284H, 304H. 384H: TRANSMIT

INTERFACE CONFIGURATION .............................................................52

REGISTERS 005H, 085H, 105H, 185H, 205H, 285H, 305H, 385H: EGRESS

OPTIONS ...............................................................................................54

REGISTERS 006H, 086H, 106H, 186H, 206H, 286H, 306H, 386H: TRANSMIT

FRAMING AND BYPASS OPTIONS.......................................................56

REGISTERS 007H, 087H, 107H, 187H, 207H, 287H, 307H, 387H: TRANSMIT

TIMING OPTIONS..................................................................................58

REGISTERS 008H, 088H, 108H, 188H, 208H, 288H, 308H, 388H: INTERRUPT

SOURCE #1...........................................................................................66

REGISTERS 009H, 089H, 109H, 189H, 209H, 289H, 309H, 389H: INTERRUPT

SOURCE #2...........................................................................................67

REGISTERS 00AH, 08AH, 10AH, 18AH, 20AH, 28AH, 30AH, 38AH: MASTER

DIAGNOSTICS.......................................................................................68

REGISTER 00BH: TOCTL MASTER TEST.......................................................70

REGISTER 00CH: TOCTL REVISION/CHIP ID/GLOBAL PMON UPDATE.......72

REGISTERS 00DH, 08DH, 10DH, 18DH, 20DH, 28DH, 30 DH, 38DH: FRAMER

RESET....................................................................................................73

REGISTER 00EH: INTERRUPT ID ...................................................................74

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

REGISTERS 00FH, 08FH, 10FH, 18FH, 20FH, 28FH, 30FH, 38FH: PATTERN

GENERATOR/DETECTOR POSITIONING/CONTROL ..........................75

REGISTERS 010H, 090H, 110H, 190H, 210H, 290H, 310H, 390H: RJAT

INTERRUPT STATUS.............................................................................77

REGISTER 011H, 091H, 111H, 191H, 211H, 291H, 311H, 391H: RJAT

REFERENCE CLOCK DIVISOR (N1) CONTROL..................................78

REGISTERS 012H, 092H, 112H, 192H, 212H, 292H, 312H, 392H: RJAT

OUTPUT CLOCK DIVISOR (N2) CONTROL .........................................79

REGISTERS 013H, 093H, 113H, 193H, 213H, 293H, 313H, 393H: RJAT

CONFIGURATION..................................................................................80

REGISTERS 018H, 098H, 118H, 198H, 218H, 298H, 318H, 398H: TJAT

INTERRUPT STATUS.............................................................................82

REGISTER 019H, 099H, 119H, 199H, 219H, 299H, 319H, 399H: TJAT

REFERENCE CLOCK DIVISOR (N1) CONTROL..................................83

REGISTERS 01AH, 09AH, 11AH, 19AH, 21AH, 29AH, 31AH, 39AH: TJAT

OUTPUT CLOCK DIVISOR (N2) CONTROL .........................................84

REGISTERS 01BH, 09BH, 11BH, 19BH, 21BH, 29BH, 31BH, 39BH: TJAT

CONFIGURATION..................................................................................85

REGISTERS 01CH, 09CH, 11CH, 19CH, 21CH, 29CH, 31 CH, 39CH: ELST

CONFIGURATION..................................................................................87

REGISTERS 01DH, 09DH, 11DH, 19DH, 21DH, 29DH, 31 DH, 39DH: ELST

INTERRUPT ENABLE/STATUS..............................................................88

REGISTERS 01EH, 09EH, 11EH, 19EH, 21EH, 29EH, 31EH, 39EH: ELST

TROUBLE CODE ...................................................................................89

REGISTERS 020H, 0A0H, 120H, 1A0H, 220H, 2A0H, 320H, 3A0H: FRMR

CONFIGURATION..................................................................................90

REGISTERS 021H, 0A1H, 121H, 1A1H, 221H, 2A1H, 321H, 3A1H: FRMR

INTERRUPT ENABLE............................................................................92

REGISTERS 022H, 0A2H, 122H, 1A2H, 222H, 2A2H, 322H, 3A2H: FRMR

INTERRUPT STATUS.............................................................................94

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

REGISTERS 027H, 0A7H, 127H, 1A7H, 227H, 2A7H, 327H, 3A7H: CLOCK

MONITOR...............................................................................................96

REGISTERS 02AH, 0AAH, 12AH, 1AAH, 22AH, 2AAH, 32AH, 3AAH: RBOC

ENABLE .................................................................................................98

REGISTERS 02BH, 0ABH, 12BH, 1ABH, 22BH, 2ABH, 32BH, 3ABH: RBOC

CODE STATUS.......................................................................................99

REGISTERS 02CH, 0ACH, 12CH, 1ACH, 22CH, 2ACH, 32CH, 3ACH: ALMI

CONFIGURATION................................................................................100

REGISTERS 02DH, 0ADH, 12DH, 1ADH, 22DH, 2ADH, 32DH, 3 ADH: ALMI

INTERRUPT ENABLE..........................................................................101

REGISTERS 02EH, 0AEH, 12EH, 1AEH 22EH, 2AEH, 32EH, 3AEH: ALMI

INTERRUPT STATUS...........................................................................102

REGISTERS 02FH, 0AFH, 12FH, 1AFH, 22FH, 2AFH, 32FH, 3AFH: ALMI

ALARM DETECTION STATUS .............................................................103

REGISTERS 030H, 0B0H, 130H, 1B0H, 230H, 2B0H, 330H, 3B0H: TPSC

CONFIGURATION................................................................................105

REGISTERS 031H, 0B1H, 131H, 1B1H, 231H, 2B1H, 331H, 3B1H: TPSC µP

ACCESS STATUS.................................................................................106

REGISTERS 032H, 0B2H, 132H, 1B2H, 232H, 2B2H, 332H, 3B2H: TPSC

CHANNEL INDIRECT ADDRESS/CONTROL......................................107

REGISTERS 033H, 0B3H, 133H, 1B3H, 233H, 2B3H, 333H, 3B3H: TPSC

CHANNEL INDIRECT DATA BUFFER..................................................108

TPSC INTERNAL REGISTERS 01-18H: EGRESS CONTROL BYTE............110

TPSC INTERNAL REGISTERS 19-30H: IDLE CODE BYTE ..........................113

TPSC INTERNAL REGISTERS 31-48H: SIGNALING CONTROL BYTE........114

REGISTER 034H, 0B4H, 134H, 1B4H, 234H, 2B4H ,334H, 3B4H: TDPR

CONFIGURATION................................................................................115

REGISTER 035H, 0B5H, 135H, 1B5H, 235H, 2B5H ,335H, 3B5H: TDPR

UPPER TRANSMIT THRESHOLD .......................................................117

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

REGISTER 036H, 0B6H, 136H, 1B6H, 236H, 2B6H ,336H, 3B6H: TDPR

LOWER INTERRUPT THRESHOLD....................................................118

REGISTER 037H, 0B7H, 137H, 1B7H, 237H, 2B7H ,337H, 3B7H: TDPR

INTERRUPT ENABLE..........................................................................119

REGISTER 038H, 0B8H, 138H, 1B8H, 238H, 2B8H ,338H, 3B8H: TDPR

INTERRUPT STATUS /UDR CLEAR.....................................................121

REGISTER 039H, 0B9H, 139H, 1B9H, 239H, 2B9H ,339H, 3B9H: TDPR

TRANSMIT DATA..................................................................................123

REGISTERS 03CH, 0BCH, 13CH, 1BCH, 23CH, 2BCH, 33CH, 3 BCH: IBCD

CONFIGURATION................................................................................124

REGISTERS 03DH, 0BDH, 13DH, 1BDH, 23DH, 2BDH, 33DH, 3 BDH: IBCD

INTERRUPT ENABLE/STATUS............................................................125

REGISTERS 03EH, 0BEH, 13EH, 1BEH, 23EH, 2BEH, 33EH, 3BEH: IBCD

ACTIVATE CODE..................................................................................127

REGISTERS 03FH, 0BFH, 13FH, 1BFH, 23FH, 2BFH, 33FH, 3BFH: IBCD

DEACTIVATE CODE.............................................................................128

REGISTERS 040H, 0C0H, 140H, 1C0H, 240H, 2C0H, 340H, 3C0H: SIGX

CONFIGURATION (COSS=0) ..............................................................129

REGISTERS 040H, 0C0H, 140H, 1C0H, 240H, 2C0H, 340H, 3C0H: SIGX

CONFIGURATION (COSS=1) ..............................................................131

REGISTERS 041H, 0C1H, 141H, 1C1H, 241H, 2C1H, 341H, 3C1H: SIGX µP

ACCESS STATUS (COSS=0)...............................................................132

REGISTERS 041H, 0C1H, 141H, 1C1H, 241H, 2C1H, 341H, 3C1H: SIGX

SIGNALING STATE CHANGE CHANNELS 17-24 (COSS=1)..............133

REGISTERS 042H, 0C2H, 142H, 1C2H, 242H, 2C2H, 342H, 3C2H: SIGX

CHANNEL INDIRECT ADDRESS/CONTROL (COSS=0)....................134

REGISTERS 042H, 0C2H, 142H, 1C2H, 242H, 2C2H, 342H, 3C2H: SIGX

SIGNALING STATE CHANGE CHANNELS 9-16 (COSS=1)................135

REGISTERS 043H, 0C3H, 143H, 1C3H, 243H, 2C3H, 343H, 3C3H: SIGX

CHANNEL INDIRECT DATA BUFFER (COSS = 0)..............................136

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

REGISTERS 043H, 0C3H, 143H, 1C3H, 243H, 2C3H, 343H, 3C3H: SIGX

SIGNALING STATE CHANGE CHANNELS 1-8 (COSS=1)..................137

SIGX INTERNAL REGISTERS 20-37H: SIGNALING DATA............................139

SIGX INTERNAL REGISTERS 40-57H: PER-DS0 CONFIGURATION DATA .141

REGISTERS 044H, 0C4H, 144H, 1C4H, 244H, 2C4H, 344H, 3C4H: XBAS

CONFIGURATION................................................................................142

REGISTERS 045H, 0C5H, 145H, 1C5H, 245H, 2C5H, 345H, 3C5H: XBAS

ALARM TRANSMIT..............................................................................144

REGISTERS 046H, 0C6H, 146H, 1C6H, 246H, 2C6H, 346H, 3C6H: XIBC

CONTROL............................................................................................145

REGISTERS 047H, 0C7H, 147H, 1C7H, 247H, 2C7H, 347H, 3C7H: XIBC

LOOPBACK CODE...............................................................................147

REGISTERS 049H, 0C9H, 149H, 1C9H, 249H, 2C9H, 349H, 3C9H: PMON

INTERRUPT ENABLE/STATUS............................................................148

REGISTERS 04A-04FH, 0CA-0CFH, 14A-14FH, 1CA-1CFH, 24A-24FH, 2CA-

2CFH, 34A-34FH, 3CA-3CFH: LATCHING PERFORMANCE DATA.....149

REGISTERS 04AH, 0CAH, 14AH 1CAH, 24AH, 2CAH, 34AH, AND 3CAH:

PMON BEE COUNT (LSB)...................................................................150

REGISTERS 04BH, 0CBH, 14BH 1CBH, 24BH, 2CBH, 34BH, AND 3CBH:

PMON BEE COUNT (MSB)..................................................................151

REGISTERS 04CH, 0CCH, 14CH, 1CCH, 24CH, 2CCH, 34CH, 3CCH: PMON

FER COUNT (LSB)...............................................................................152

REGISTERS 04DH, 0CDH, 14DH, 1CDH, 24DH, 2CDH, 34DH, 3CDH: PMON

FER COUNT (MSB)..............................................................................153

REGISTERS 04EH, 0CEH, 14EH, 1CEH, 24EH, 2CEH, 34EH, 3CEH: PMON

OOF COUNT........................................................................................154

REGISTERS 04FH, 0CFH, 14FH, 1CFH, 24FH, 2CFH, 34FH, 3CFH: PMON

COFA COUNT......................................................................................155

REGISTERS 050H, 0D0H, 150H, 1D0H, 250H, 2D0H, 350H, 3D0H: RPSC

CONFIGURATION................................................................................156

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

REGISTERS 051H, 0D1H, 151H, 1D1H, 251H, 2D1H, 351H, 3D1H: RPSC µP

ACCESS STATUS.................................................................................157

REGISTERS 052H, 0D2H, 152H, 1D2H, 252H, 2D2H, 352H, 3D2H: RPSC

CHANNEL INDIRECT ADDRESS/CONTROL......................................158

REGISTERS 053H, 0D3H, 153H, 1D3H, 253H, 2D3H, 353H, 3D3H: RPSC

CHANNEL INDIRECT DATA BUFFER..................................................159

RPSC INTERNAL REGISTERS 01-18H: INGRESS CONTROL BYTE...........161

RPSC INTERNAL REGISTERS 19-30H: DATA TRUNK CONDITIONING CODE

BYTE....................................................................................................163

RPSC INTERNAL REGISTERS 31-48H: SIGNALING TRUNK CONDITIONING

BYTE....................................................................................................164

REGISTERS 054H, 0D4H, 154H, 1D4H, 254H, 2D4H, 354H, 3D4H: RDLC

CONFIGURATION................................................................................165

REGISTER 055H, 0D5H, 155H, 1D5H, 255H, 2D5H, 355H, 3D5H: RDLC

INTERRUPT CONTROL.......................................................................167

REGISTER 056H, 0D6H, 156H, 1D6H, 256H, 2D6H, 356H, 3D6H: RDLC

STATUS ................................................................................................168

REGISTER 057H, 0D7H, 157H, 1D7H, 257H, 2D7H, 357H, 3D7H: RDLC DATA

..............................................................................................................171

REGISTER 058H, 0D8H, 158H, 1D8H, 258H, 2D8H, 358H, 3D8H: RDLC

PRIMARY ADDRESS MATCH..............................................................172

REGISTER 059H, 0D9H, 159H, 1D9H, 259H, 2D9H, 359H, 3D9H: RDLC

SECONDARY ADDRESS MATCH........................................................173

REGISTERS 05DH, 0DDH, 15DH, 1DDH, 25DH, 2DDH, 35DH, 3DDH: XBOC

CODE...................................................................................................174

REGISTER 060H, 0E0H, 160H, 1E0H, 260H, 2E0H, 360H, 3E0H: PRGD

CONTROL............................................................................................175

REGISTER 061H, 0E1H, 161H, 1E1H, 261H, 2E1H, 361H, 3E1H: PRGD

INTERRUPT ENABLE/STATUS............................................................177

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

REGISTER 062H, 0E2H, 162H, 1E2H, 262H, 2E2H, 362H, 3E2H: PRGD

LENGTH...............................................................................................179

REGISTER 063H, 0E3H, 163H, 1E3H, 263H, 2E3H, 363H, 3E3H: PRGD TAP

..............................................................................................................180

REGISTER 064H, 0E4H, 164H, 1E4H, 264H, 2E4H, 364H, 3E4H: PRGD

ERROR INSERTION REGISTER.........................................................181

REGISTER 068H, 0E8H, 168H, 1E8H, 268H, 2E8H, 368H, 3E8H: PRGD

PATTERN INSERTION #1 ....................................................................183

REGISTER 069H, 0E9H, 169H, 1E9H, 269H, 2E9H, 369H, 3E9H: PRGD

PATTERN INSERTION #2 ....................................................................184

REGISTER 06AH, 0EAH, 16AH, 1EAH, 26AH, 2EAH, 36AH, 3EAH: PRGD

PATTERN INSERTION #3 ....................................................................185

REGISTER 06BH, 0EBH, 16BH, 1EBH, 26BH, 2EBH, 36BH, 3EBH: PRGD

PATTERN INSERTION #4 ....................................................................186

REGISTER 06CH, 0ECH, 16CH, 1ECH, 26CH, 2ECH, 36CH, 3 ECH: PRGD

PATTERN DETECTOR #1 ....................................................................187

REGISTER 06DH, 0EDH, 16DH, 1EDH, 26DH, 2EDH, 36DH, 3 EDH: PRGD

PATTERN DETECTOR #2 ....................................................................188

REGISTER 06EH, 0EEH, 16EH, 1EEH, 26EH, 2EEH, 36EH, 3EEH: PRGD

PATTERN DETECTOR #3 ....................................................................189

REGISTER 06FH, 0EFH, 16FH, 1EFH, 26FH, 2EFH, 36FH, 3EFH: PRGD

PATTERN DETECTOR #4 ....................................................................190

REGISTER 00BH: TOCTL MASTER TEST.....................................................192

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

LIST OF FIGURES

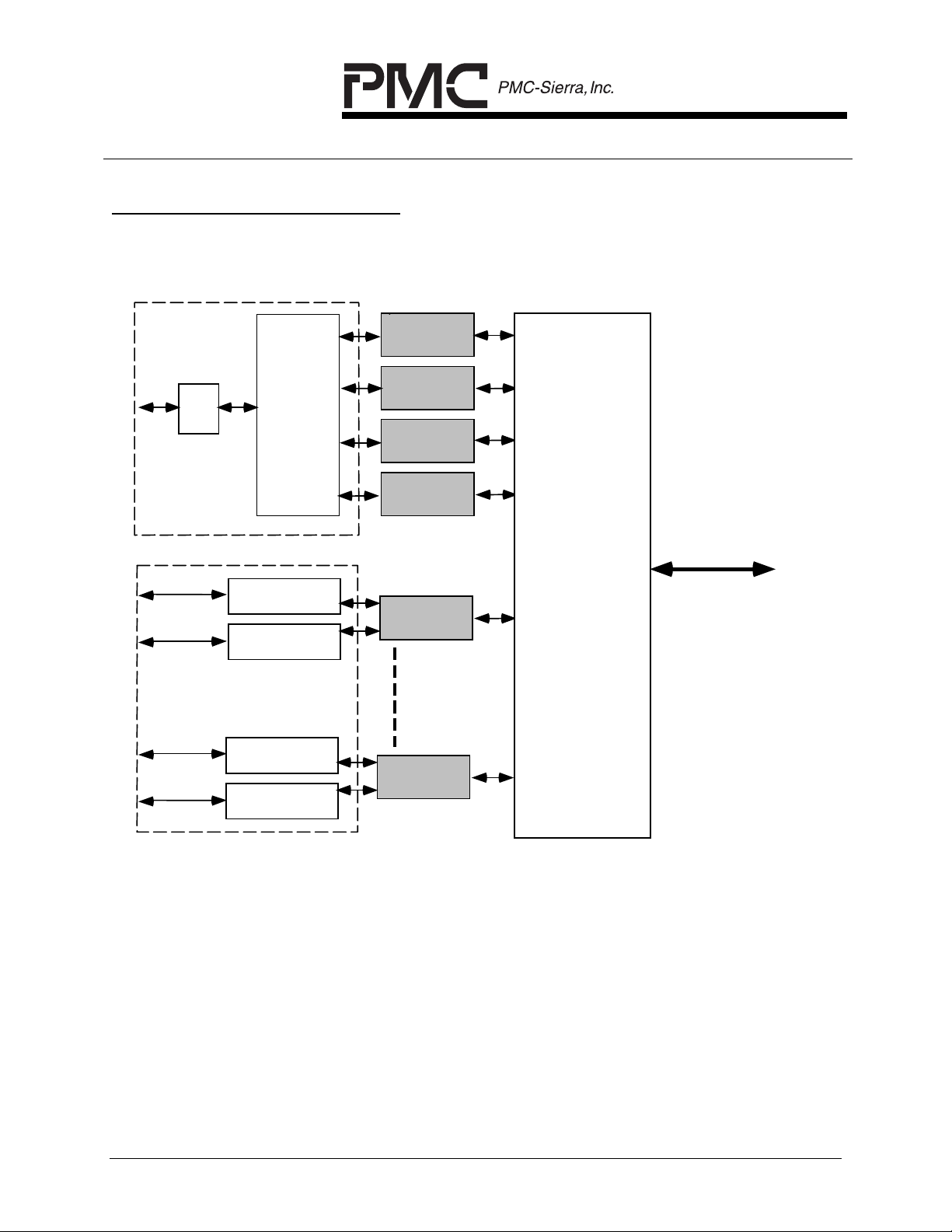

FIGURE 1 - HIGH DENSITY CHANNELIZED PORT CARD..............................5

FIGURE 2 - CLOCK MASTER: FULL DS1 .......................................................25

FIGURE 3 - CLOCK MASTER: NXDS0 ...........................................................26

FIGURE 4 - CLOCK SLAVE: ICLK REFERENCE............................................26

FIGURE 5 - CLOCK SLAVE: EXTERNAL SIGNALING ................................... 27

FIGURE 6 - DJAT JITTER TOLERANCE .........................................................33

FIGURE 7 - DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY...34

FIGURE 8 - DJAT JITTER TRANSFER ............................................................34

FIGURE 9 - CLOCK MASTER: FULL DS1 .......................................................35

FIGURE 10- CLOCK MASTER: NXDS0 ...........................................................36

FIGURE 11- CLOCK SLAVE: EFP ENABLED ..................................................36

FIGURE 12- CLOCK SLAVE: EXTERNAL SIGNALING....................................37

FIGURE 13- TRANSMIT TIMING OPTIONS.....................................................65

FIGURE 14- INGRESS INTERFACE CLOCK MASTER: NXDS0 MODE........200

FIGURE 15- EGRESS INTERFACE CLOCK MASTER: NXDS0 MODE.........200

FIGURE 16- INGRESS INTERFACE CLOCK MASTER : FULL DS1 MODE..201

FIGURE 17- EGRESS INTERFACE : 1.544 MHZ CLOCK MASTER: FULL DS1

MODE...................................................................................................201

FIGURE 18- INGRESS INTERFACE: 1.544MHZ CLOCK SLAVE MODES....202

FIGURE 19- EGRESS INTERFACE : 1.544 MHZ CLOCK SLAVE: EFP

ENABLED MODE.................................................................................202

FIGURE 20- EGRESS INTERFACE : 1.544 MHZ CLOCK SLAVE: EXTERNAL

SIGNALING MODE ..............................................................................203

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

FIGURE 21- INGRESS INTERFACE: 2.048 MHZ CLOCK SLAVE MODE......204

FIGURE 22- EGRESS INTERFACE: 2.048 MHZ CLOCK SLAVE: EFP ENABLED

MODE...................................................................................................205

FIGURE 23- EGRESS INTERFACE: 2.048 MHZ CLOCK SLAVE: EXTERNAL

SIGNALING MODE ..............................................................................206

FIGURE 24- TYPICAL DATA FRAME..............................................................216

FIGURE 25- EXAMPLE MULTI-PACKET OPERATIONAL SEQUENCE.........217

FIGURE 26- PRGD PATTERN GENERATOR .................................................220

FIGURE 27- LINE LOOPBACK.......................................................................224

FIGURE 28- DIAGNOSTIC DIGITAL LOOPBACK..........................................225

FIGURE 29- PER-DS0 LOOPBACK ...............................................................226

FIGURE 30- BEE COUNT EXPECTED VS BIT ERROR RATE FOR ESF......231

FIGURE 31- BOUNDARY SCAN ARCHITECTURE........................................232

FIGURE 32- TAP CONTROLLER FINITE STATE MACHINE ..........................234

FIGURE 33- INPUT OBSERVATION CELL (IN_CELL)...................................240

FIGURE 34- OUTPUT CELL (OUT_CELL).....................................................241

FIGURE 35- BIDIRECTIONAL CELL (IO_CELL)............................................241

FIGURE 36- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS242

FIGURE 37- MICROPROCESSOR READ ACCESS TIMING.........................247

FIGURE 38- MICROPROCESSOR WRITE ACCESS TIMING .......................249

FIGURE 39- XCLK=37.056 MHZ INPUT TIMING...........................................251

FIGURE 40- EGRESS INTERFACE TIMING - CLOCK SLAVE: EFP ENABLED

MODE...................................................................................................252

FIGURE 41- EGRESS INTERFACE TIMING - CLOCK SLAVE: EXTERNAL

SIGNALING MODE ..............................................................................253

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

FIGURE 42- EGRESS INTERFACE TIMING - CLOCK MASTER: FULL DS1

MODE...................................................................................................254

FIGURE 43- EGRESS INTERFACE INPUT TIMING - CLOCK MASTER : NXDS0

MODE...................................................................................................255

FIGURE 44- INGRESS INTERFACE TIMING - CLOCK SLAVE MODES.......256

FIGURE 45- INGRESS INTERFACE TIMING - CLOCK MASTER MODES....257

FIGURE 46- TRANSMIT LINE INTERFACE TIMING ......................................258

FIGURE 47- LINE INTERFACE INPUT TIMING..............................................259

FIGURE 48- JTAG PORT INTERFACE TIMING DIAGRAM............................261

FIGURE 49- 128 PIN COPPER LEADFRAME PLASTIC QUAD FLAT PACK (R

SUFFIX):...............................................................................................264

FIGURE 50- 128 PIN CHIP ARRAY BALL GRID ARRAY (N SUFFIX):...........265

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiii

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

LIST OF TABLES

TABLE 1 - NORMAL MODE REGISTER MEMORY MAP .............................38

TABLE 2 - TYPICAL TRANSMIT TIMING CONFIGURATIONS .....................60

TABLE 3 - TPSC INDIRECT MEMORY MAP...............................................108

TABLE 4 - SIGX INDIRECT MEMORY MAP ...............................................138

TABLE 5 - ACCESSING INPUTS IN TEST MODE 0...................................194

TABLE 6 - CONTROLLING OUTPUTS IN TEST MODE 0 ..........................195

TABLE 7 - BOUNDARY SCAN REGISTER.................................................198

TABLE 8 - DEFAULT SETTINGS.................................................................207

TABLE 9 - ESF FRAME FORMAT...............................................................208

TABLE 10 - SF FRAME FORMAT..................................................................209

TABLE 11 - PMON POLLING SEQUENCE...................................................209

TABLE 12 - PSEUDO RANDOM PATTERN GENERATION (PS BIT = 0)......221

TABLE 13 - REPETITIVE PATTERN GENERATION (PS BIT = 1).................222

TABLE 14 - BOUNDARY SCAN REGISTER.................................................237

TABLE 15 - TOCTL ABSOLUTE MAXIMUM RATINGS .................................243

TABLE 16 - TOCTL D.C. CHARACTERISTICS..............................................244

TABLE 17 - MICROPROCESSOR READ ACCESS (FIGURE 37) ................246

TABLE 18 - MICROPROCESSOR WRITE ACCESS (FIGURE 38)...............248

TABLE 19 - XCLK=37.056 MHZ INPUT (FIGURE 39)...................................251

TABLE 20 - EGRESS INTERFACE TIMING - CLOCK SLAVE: EFP ENABLED

MODE (FIGURE 40).............................................................................252

TABLE 21 - EGRESS INTERFACE TIMING - CLOCK SLAVE: EXTERNAL

SIGNALING (FIGURE 41)....................................................................253

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiv

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

TABLE 22 - EGRESS INTERFACE TIMING - CLOCK MASTER: FULL DS1

FIGURE 42)..........................................................................................254

TABLE 23 - EGRESS INTERFACE INPUT TIMING - CLOCK MASTER : NXDS0

MODE (FIGURE 43).............................................................................255

TABLE 24 - INGRESS INTERFACE TIMING - CLOCK SLAVE MODES

(FIGURE 44).........................................................................................256

TABLE 25 - INGRESS INTERFACE TIMING - CLOCK MASTER MODES

(FIGURE 45).........................................................................................257

TABLE 26 - TRANSMIT LINE INTERFACE TIMING (FIGURE 46)................258

TABLE 27 - RECEIVE LINE INTERFACE TIMING (FIGURE 47)...................259

TABLE 28 - JTAG PORT INTERFACE TIMING (FIGURE 48)........................260

TABLE 29 - TOCTL ORDERING INFORMATION..........................................263

TABLE 30 - TOCTL THERMAL INFORMATION.............................................263

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xv

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

1

FEATURES

Integrates eight T1 framers in a single device for terminating duplex DS-1

•

signals.

Supports SF and ESF format DS-1 signals.

•

Supports transfer of PCM data to/from 1.544 MHz system-side devices. Also

•

supports a fractional T1 system interface with independent ingress/egress

NxDS0 rates. Supports a 2.048 MHz system-side interface without external

clock gapping.

Provides jitter attenuation in the receive and transmit directions.

•

Provides per-DS0 line loopback and per link diagnostic and line loopbacks.

•

Provides an integral patter n generator/detector that may be programmed to

•

generate and detect common pseudo-random or repetitive sequences. The

programmed sequence may be inserted/detected in the entire DS-1 frame, or

on an NxDS0 basis, in both the ingress and egress directions. May be

configured to transmit or detect in only the 7 most significant bits of selected

channels, in order to support fractional T1 loopback codes in an N x 56kbps

fractional T1 setup. Each framer possesses its own independent pattern

generator/detector, and each detector counts pattern errors using a 32-bit

saturating error counter.

Provides robbed bit signaling extraction and insertion on a per-DS0 basis.

•

Provides programmable idle code substitution, data and sign inversion, and

•

digital milliwatt code insertion on a per-DS0 basis.

Software compatible with the PM4341A T1XC Single T1 Transceiver and the

•

PM4344 TQU AD Quad T1 F ramer .

Seamless interface to the PM8313 D3MX single chip M13 multiplex and to

•

the PM4314 QDSX Quad Line Interface.

Provides an 8-bit microprocessor bus interface for configuration, control, and

•

status monitoring.

Low power 3.3V CMOS technology with 5V tolerant inputs.

•

Supports standard 5 signal P1149.1 JTAG boundary scan.

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

Available in a 14 mm by 20 mm 128 pin Plastic Quad Flat Pack (PQFP) or an

•

11mm by 11mm 128 pin Chip Array Ball Grid Array (CABGA) package.

Each one of eight receiver sections:

Accepts gapped data streams to support higher rate demultiplexing.

•

Provides Red, Yellow, and AIS alarms integration.

•

Provides programmable in-band loopback code detection.

•

Indicates signaling state change, and 2 superframes of signaling debounce

•

on a per-DS0 basis.

Provides an HDLC interface with 128 bytes of buffering for terminating the

•

facility data link.

Provides performance monitoring counters sufficiently large as to allow

•

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the performance monitoring counters and interrupts the

microprocessor once per second, timed to the receive line.

Provides an optional elastic store which may be used to time the ingress

•

streams to a common clock and frame alignment, or to facilitate per-DS0

loopbacks.

Each one of eight transmitter sections:

May be timed to its associated receive clock (loop timing) or may derive its

•

timing from a common egress clock or a common transmit clock; the transmit

line clock may be synthesized from an N*8kHz reference.

Provides minimum ones density through Bell (bit 7), GTE or “jammed bit 8”

•

zero code suppression on a per-DS0 basis.Provides a 128 byte buffer to allow

insert ion of the facility dat a link using the host interface.

Supports transmission of the alarm indication signal (AIS) or the Yellow alarm

•

signal in both SF and ESF formats.

Provides a digital phase locked loop for generation of a low jitter transmit

•

clock.

Provides a FIFO buffer for jitter attenuation and rate conversion in the

•

transmitter.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

2

APPLICATIONS

High density Internet T1 interfaces for multiplexers, switches, routers and

•

digital modems.

Frame Relay switches and access devices (FRADS)

•

SONET/SDH Add Drop Multiplexers

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

3

REFERENCES

1. American National Standard for Telecommunications - Digital Hierarchy -

Formats Specification, ANSI T1.107-1995

2. American National Standard for Telecommunications - Digital Hierarchy -

Layer 1 In-Service Digital Transmission Performance Monitoring, ANSI

T1.231-1993

3. American National Standard for Telecommunications - Carrier to Customer

Installation - DS-1 Metallic Interface Specification, ANSI T1.403-1995

4. American National Standard for Telecommunications - Integrated Services

Digital Network (ISDN) Primary Rate- Customer Installation Metallic

Interfaces Layer 1 Specification, ANSI T1.408-1990

5. Bell Communications Research - DS-1 Rate Digital Service Monitoring Unit

Functional Specification, TA-TSY-000147, Issue 1, October, 1987.

6. Bell Communications Research - Alar m Indication Signal Requirements and

Objectives, TR-TSY-000191 Issue 1, May 1986.

7. Bell Communications Research - Integrated Digital Loop Carrier Generic

Requirements, Objectives, and Interface, TR-NWT-000303, Issue 2,

December, 1992.

8. Bell Communications Research - Functional Criteria for the DS-1 Interface

Connector, TR-TSY-000312, Issue 1, March, 1988.

9. Bell Communications Research - Transport Systems Generic Requirements

(TSGR): Common Requirement, TR-TSY-000499, Issue 5, December, 1993.

10. AT&T - Requirements For Interfacing Digital Terminal Equipment To Ser vices

Employing The Extended Superframe Format, TR 54016, September, 1989.

11. AT&T, TR 62411 - Accunet T1.5 - "Service Description and Interface

Specification" December, 1990.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM4388 TOC TL

/

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

4

T1 Channelized

DS-3 Interface

APPLICATION EXAMPLES

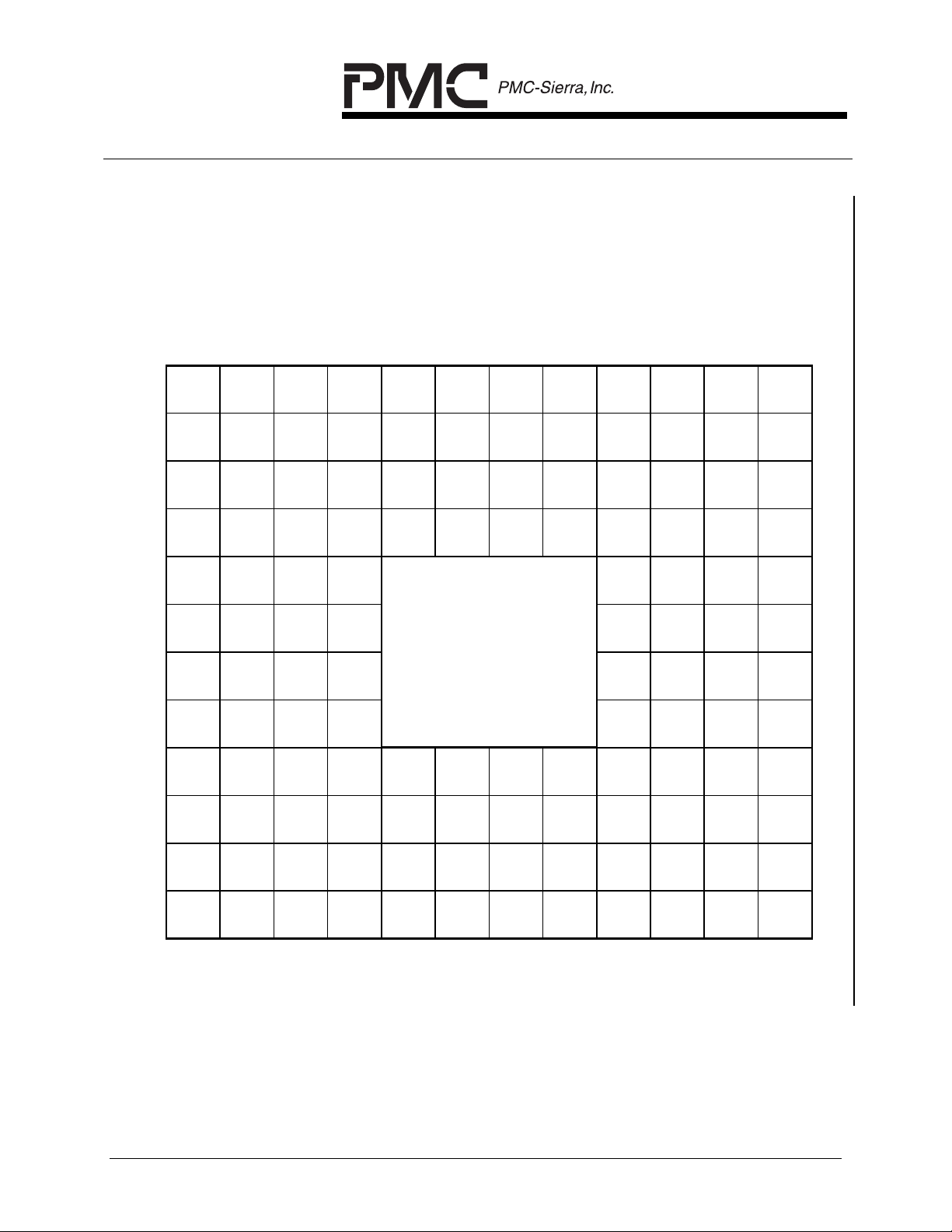

Figure 1 - High Density Channelized Port Card

#1 of 11

PM4388-RI

TOCTL

PM4388-RI

LIU

PM8313-RI

D3MX

AND/OR

PM4314-RI

QDSX

PM4314-RI

QDSX

TOCTL

PM4388-RI

TOCTL

PM4388-RI

TOCTL

Channelized

Unchannelized

HDLC

Processor(s)

PM4388-RI

TOCTL

#5 of 11

Packet Router Core

or

Packet Switch Core

Channelized

And/Or Unchannelized T1

Interfaces

PM4314-RI

QDSX

PM4314-RI

QDSX

PM4388-RI

TOCTL

#11 of 11

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM4388 TOC TL

8

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

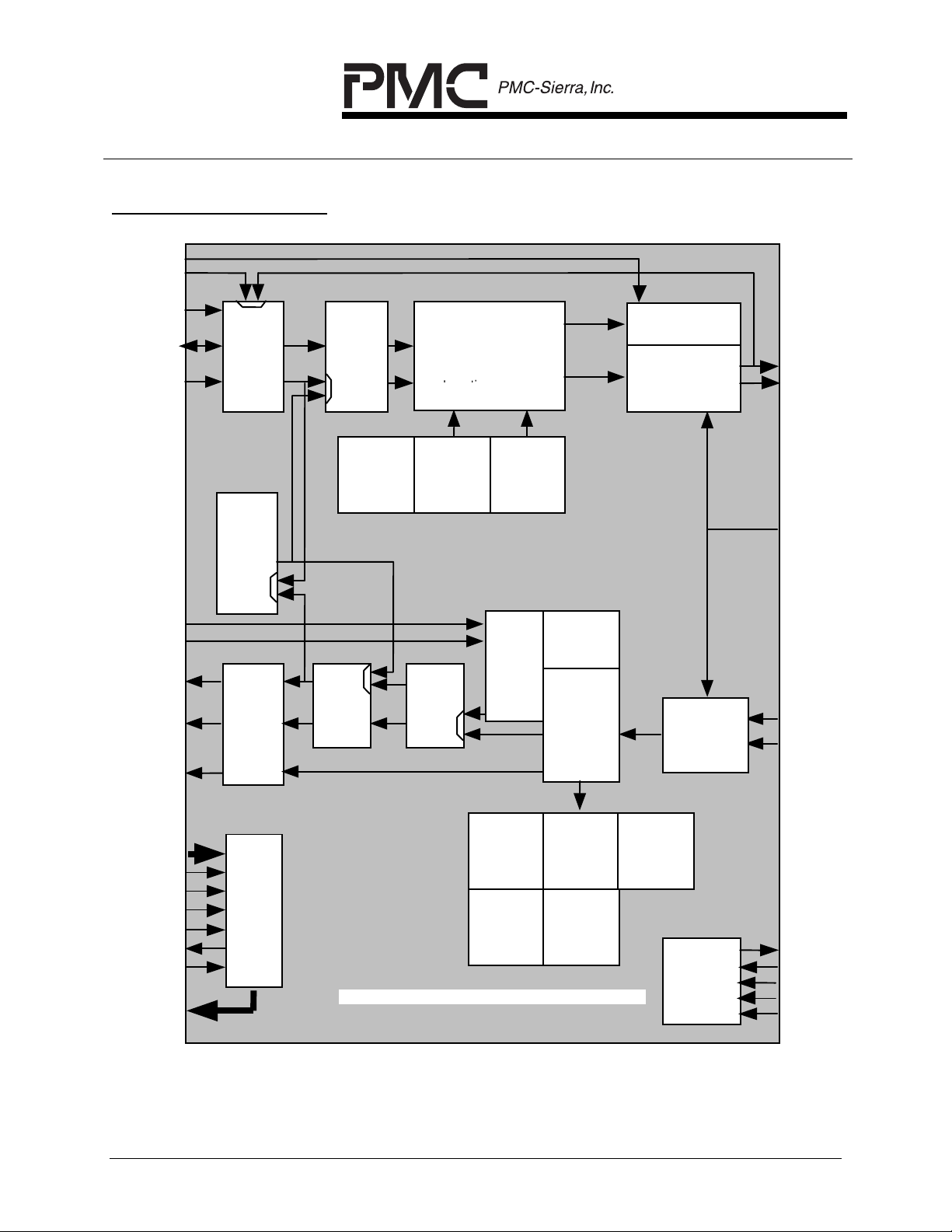

5

CTCLK*

CECLK*

CEFP*

ECLK[1:8]/

EFP[1:8]/

ESIG[1:8]

ED[1:8]

CICLK*

CIFP*

ID[1:8]

ICLK[1:8]/

ISIG[1:8]

BLOCK DIAGRAM

EIF

Egress

Interface

PRGD

Pattern

Generator/

Detector

IIF

Ingress

Interface

TPSC

Per-DS0

Controller

Transmitter

RPSC

Per-DS0

Controller

TDPR

HDLC

TRANSMITTER

XBAS

BasicTransmitter:

Frame Generation,

Alarm Insertion,

Signaling

Trunk Conditioning

XBOC

Bit Oriented

Code

Generator

RECEIVER

SIGX

Signaling

Extractor

ELST

Elastic

XIBC

Inband

Loopback

Code

Generator

ELST

Elastic

Store

Store

FRAM

Framer/

Elastic Store

RAM

FRMR

Framer:

Frame

Alignment,

Alarm

Extraction

TOPS

Timing Options

TJAT

Digital Jitter

Attenuator

RJAT

Digital Jitter

Attenuator

TLCLK[1:8]

TLD[1:8]

XCLK*

RLCLK[1:

RLD[1:8]

IFP[1:8]

RBOC

A[10:0]*

RDB*

WRB*

CSB*

ALE*

INTB*

RSTB*

D[7:0]*

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

MPIF

Micro-

Processor

Interface

* These signals are shared between all eight framers.

Bit Oriented

Code

Detector

RDLC

HDLC

Receiver

ALMI

Alarm

Integrator

PMON

Performance

Monitor

Counters

IBCD

Inband

Loopback

Code

Detector

Test Access

JTAG

Port

TDO

TDI

TCLK

TMS

TRSTB

6

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

6

DESCRIPTION

The PM4388 Octal T1 Framer (TOCTL) is a feature-rich device for use primarily

in systems carrying data (frame relay, Point to Point Protocol, or other protocols)

over DS-1 facilities. Each of the framers and transmitters is independently

software configurable, allowing feature selection without changes to external

wiring.

On the receive side, each of eight independent framers can be configured to

frame to either of the common DS-1 signal formats: (SF, ESF) or to be bypassed

(unframed mode). The TOCTL detects and indicates the presence of Yellow and

AIS patterns and also integrates Yellow, Red, and AIS alarms.

Performance monitoring with accumulation of CRC-6 errors, framing bit errors,

out-of-frame events, and changes of frame alignment is provided. The TOCTL

also detects the presence of in-band loopback codes, ESF bit oriented codes,

and detects and terminates HDLC messages on the ESF data link. The HDLC

messages are terminated in a 128 byte FIFO. An elastic store that optionally

supports slip buffering and adaptation to backplane timing is provided, as is a

signaling extractor that supports signaling debounce, signaling freezing and

interrupt on signaling state change on a per-DS0 basis. The TOCTL also

supports idle code substitution and detection, digital milliwatt code insertion, data

extraction, trunk conditioning, data sign and magnitude inversion, and pattern

generation or detection on a per-DS0 basis.

On the transmit side, the TOCTL generates framing for SF or ESF DS-1 formats,

or framing can be optionally disabled. The TOCTL supports signaling insertion,

idle code substitution, data insertion, line loopback, data inversion, zero-code

suppression, and pattern generation or detection on a per-DS0 basis.

The TOCTL can generate a low jitter transmit clock from a variety of clock

references, and also provides jitter attenuation in the receive path.

The TOCTL provides a parallel microprocessor interface for controlling the

operation of the TOCTL device. Serial PCM interfaces allow 1.544 Mbit/s

ingress/egress system interfaces to be directly supported. Tolerance of gapped

clocks allows other backplane rates to be supported with a minimum of external

logic.

It should be noted that the TOCTL device operates on unipolar data only: B8ZS

substitution and line code violation monitoring, if required, must be processed by

the T1 LIU.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

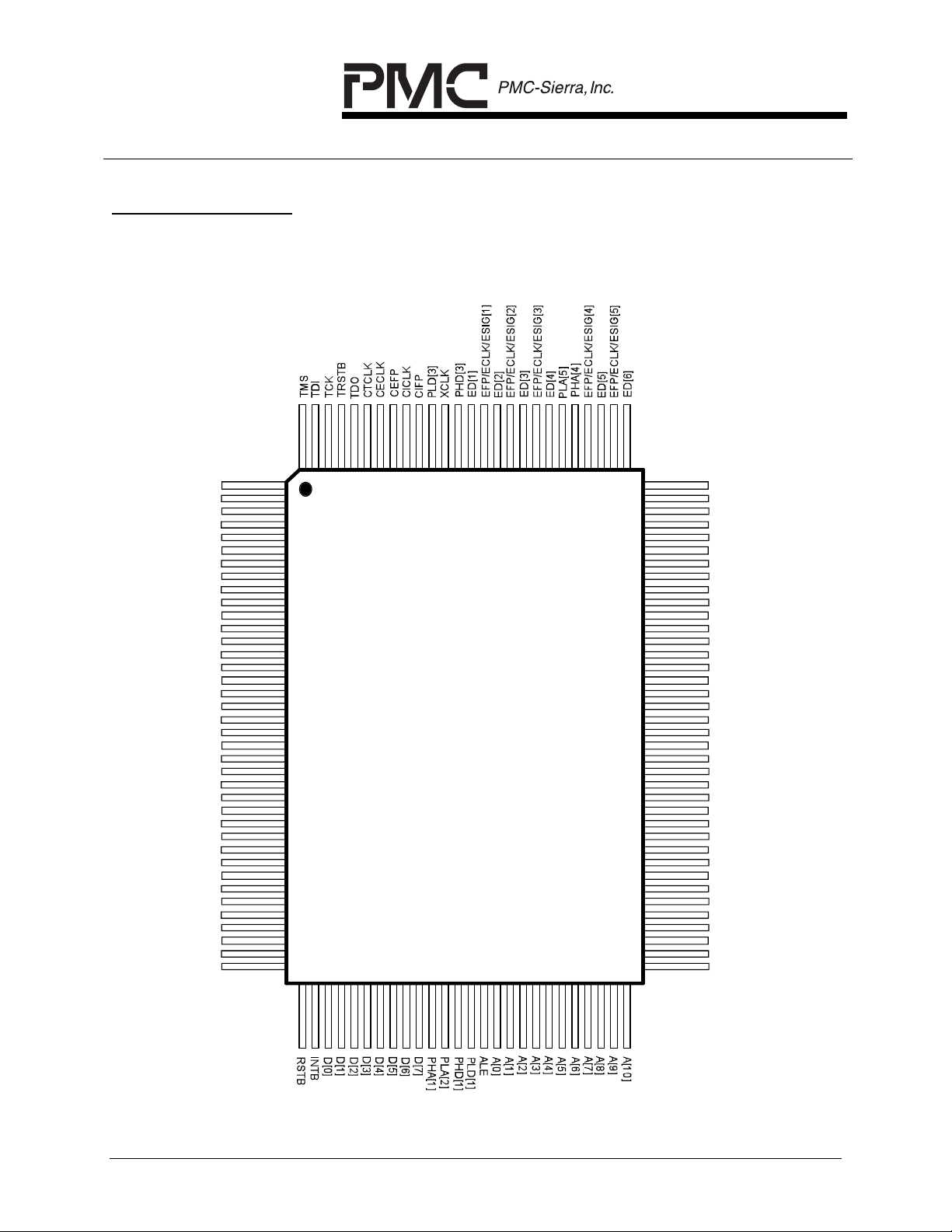

7

PIN DIAGRAM

The TOCTL is packaged in a 128-pin plastic QFP package having a body size of

14mm by 20mm and a pin pitch of 0.5mm.

PIN 128

PIN 1

RLD[1]

RLCLK[1]

RLD[2]

RLCLK[2]

RLD[3]

RLCLK[3]

RLD[4]

RLCLK[4]

TLD[1]

TLCLK[1]

TLD[2]

TLCLK[2]

TLD[3]

TLCLK[3]

TLD[4]

TLCLK[4]

BIAS

PHA[0]

PLA[0]

PHD[0]

PLD[0]

TLD[5]

TLCLK[5]

TLD[6]

TLCLK[6]

TLD[7]

TLCLK[7]

TLD[8]

TLCLK[8]

PLA[1]

RLD[5]

RLCLK[5]

RLD[6]

RLCLK[6]

RLD[7]

RLCLK[7]

RLD[8]

RLCLK[8]

Index Pin

PM 4388

TOC TL

Top

View

PIN 103

PIN 102

EFP/ECLK/ESIG[6]

ED[7]

EFP/ECLK/ESIG[7]

ED[8]

EFP/ECLK/ESIG[8]

ID[1]

ICLK/ISIG[1]

IFP[1]

ID[2]

PLA[4]

PHA[3]

ICLK/ISIG[2]

IFP[2]

ID[3]

ICLK/ISIG[3]

IFP[3]

PLD[2]

PHD[2]

ID[4]

ICLK/ISIG[4]

IFP[4]

ID[5]

ICLK/ISIG[5]

IFP[5]

ID[6]

ICLK/ISIG[6]

IFP[6]

PLA[3]

PHA[2]

ID[7]

ICLK/ISIG[7]

IFP[7]

ID[8]

ICLK/ISIG[8]

IFP[8]

RDB

WRB

CSB

PIN 38

PIN 39 PIN 64

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PIN 65

8

PM4388 TOC TL

[7]ED[6]

[4]

]

[1]

]

[1]ED[8]

[6]ED[5]

[2]ED[1]

[2]

]

[2]

[1]

[8]

[7]

]

[3]

]

[2]

]

[5]ED[4]ED[2]

]

[3]

]

]

[4]

]

]

[4]

]ID[6]

]

]

[5]

[5]

]

[7]

]

[6]ID[7]

]A[9]A[7]

]

]

[2]ID[8]

]A[3]A[0]D[5]D[2]

]

[7]

]A[4]A[1]

]D[0]

]

[8]

]A[5]A[2]

]D[3]D[1]

]

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

The TOCTL is also available in a 128 pin Chip Array Ball Grid Array (CABGA)

package having a body size of 11mm by 11mm and a ball pitch of 0.8mm.

121110987654321

A

ED

B

ID

C

ID

ICLK/

D

ISIG

ICLK/

E

ISIG

F

ID

ICLK/

ISIG

IFP[2]PHA[3]IFP[1

IFP[3]ID[3]PLA[4

PHD[2]PLD[2]ID[5

EFP/

ECLK/

ESIG

EFP/

ECLK/

ESIG

EFP/

ECLK/

ESIG

PLA[5]ED[3

EFP/

ECLK/

ESIG

EFP/

ECLK/

ESIG

PHA[4

EFP/

ECLK/

ESIG

EFP/

ECLK/

ESIG

EFP/

ECLK/

ESIG

PHD[3]CICLK CTCLK TCK RLD[1]RLD[3

XCLK/

VCLK

PLD[3]CEFP TDO RLCLK[1]RLCLK[3]TLCLK[1

CIFP CECLK TMS RLD

TRSTB TDI RLCLK[2]TLD[1]TLCLK[2

RLCLK[4]TLD[2]TLCLK[4]TLD[4

TLD[3]TLCLK[3]PLA[0]PHA[0

RLD[4

A

B

C

D

E

F

BOTTOM VIEW

G

IFP

H

IFP

J

IFP

K

PHA

ICLK/

ISIG[4

ICLK/

ISIG

PLA[3

IFP[8

WRB A[6

ICLK/

ISIG[6

ICLK/

ISIG

PHA[1]D[4

BIAS TLD[5]PLD[0]PHD[0

TLCLK[8]TLCLK[6]TLCLK[5]TLD[6

INTB RLD[5]TLD[8]TLD[7]TLCLK[7

RLCLK[7]RLCLK[6]RLCLK[5]PLA[1

G

H

J

K

L

IFP

ICLK/

M

ISIG

121110987654321

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

RDB A[10

CSB A[8

ALE PHD[1]D[7

PLD[1]PLA[2]D[6

RLCLK[8]RLD[7]RLD[6

RSTB RLD[8

9

L

M

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

8

PIN DESCRIPTION

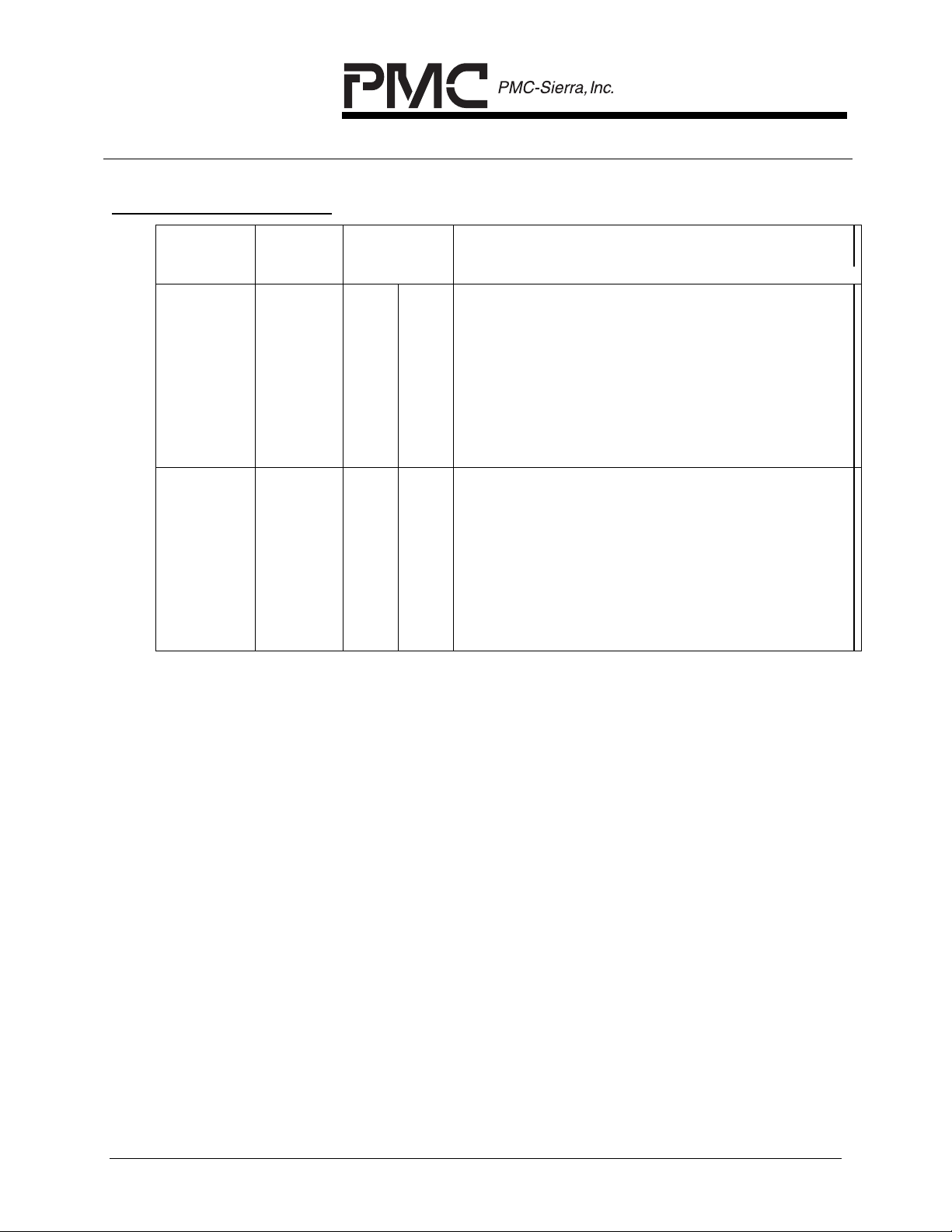

Pin

Name

RLD[1]

RLD[2]

RLD[3]

RLD[4]

RLD[5]

RLD[6]

RLD[7]

RLD[8]

RLCLK[1]

RLCLK[2]

RLCLK[3]

RLCLK[4]

RLCLK[5]

RLCLK[6]

RLCLK[7]

RLCLK[8]

Type Pin No.

-RI -NI

Input 1

3

5

7

31

33

35

37

Input 2

4

6

8

32

34

36

38

A2

B2

A1

B1

J4

L1

L2

M1

C3

D3

C2

E4

K2

K3

K4

L3

Function

Receive Line Data (RLD[1:8]). RLD[1:8]

contain the receive stream from each of the

eight DS-1 line interface units, or from a higher

order demultiplex interface. These inputs are

sampled on the active edge of the

corresponding RLCLK[1:8].

Receive Line Clocks (RLCLK[1:8]). Each input

is an externally recovered 1.544 MHz line clock

that samples the RLD[x] inputs on its active

edge. RLCLK[x] may be a gapped clock

subject to the timing constraints in the AC

Timing section of this datasheet.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

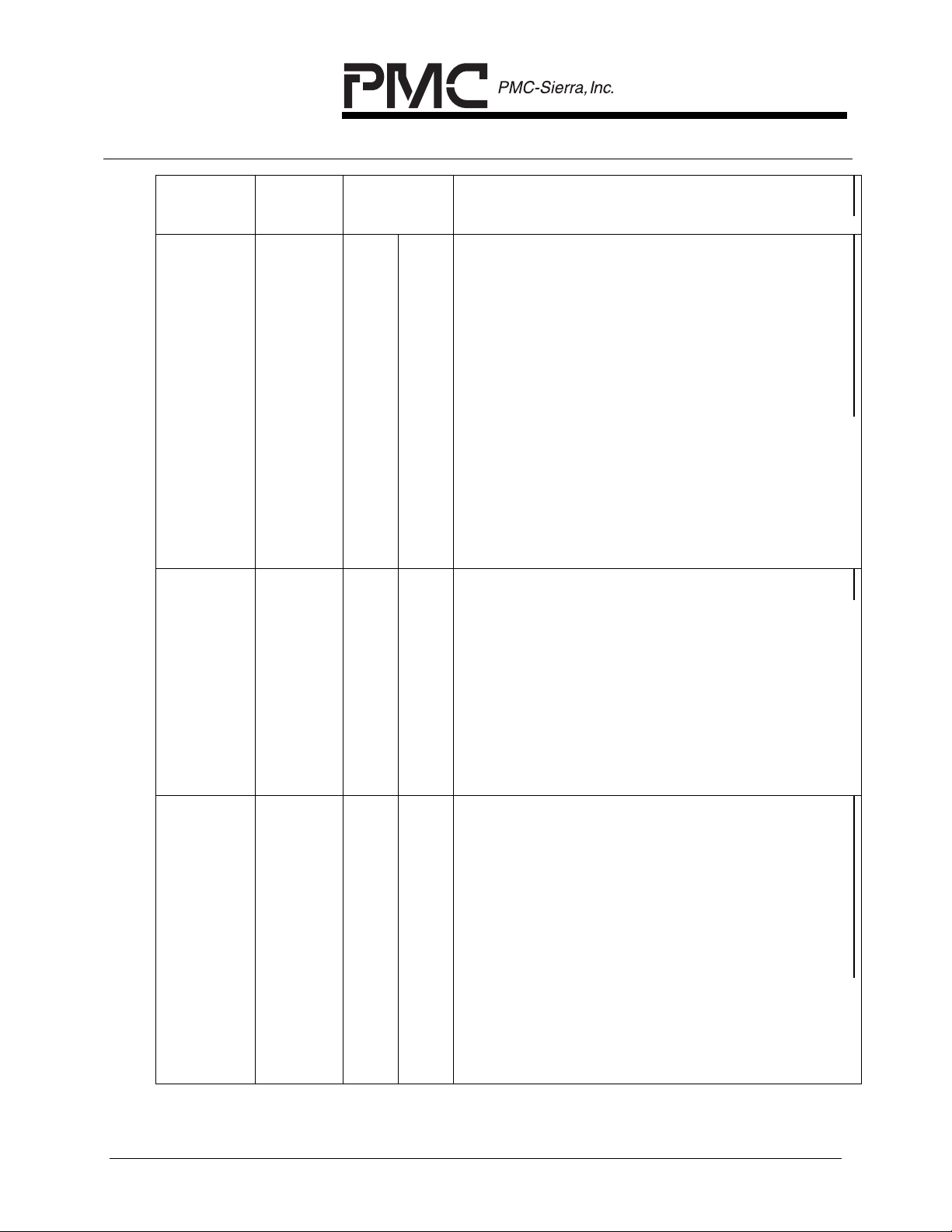

Pin

Name

ICLK[1]

ICLK[2]

ICLK[3]

ICLK[4]

ICLK[5]

ICLK[6]

ICLK[7]

ICLK[8]/

ISIG[1]

ISIG[2]

ISIG[3]

ISIG[4]

ISIG[5]

ISIG[6]

ISIG[7]

ISIG[8]

Type Pin No.

-RI -NI

Output 96

91

88

83

80

77

72

69

C11

D12

E12

G11

H11

G9

H9

M12

Function

Ingress Clocks (ICLK[1:8]). The Ingress Clocks

are active when the external signaling interface

is disabled. Each ingress clock is a smoothed

(jitter attenuated) version of the associated

receive line clock (RLCLK[x]). When the Clock

Master: NxDS0 mode is active, ICLK[x] is a

gapped version of the smoothed RLCLK[x].

When Clock Slave: ICLK Reference mode is

active, ICLK[x] may optionally be the smoothed

RLCLK[x], or the smoothed RLCLK[x] divided

by 193. When Clock Master: Full DS1 mode is

active, IFP[x] and ID[x] are updated on the

active edge of ICLK[x]. When the Clock

Master: NxDS0 mode is active, ID[x] is updated

on the active edge of ICLK[x].

Ingress Signaling (ISIG[1:8]). When the Clock

Slave: External Signaling mode is enabled,

each ISIG[x] contains the extracted signaling

bits for each channel in the frame, repeated for

the entire superframe. Each channel's

signaling bits are valid in bit locations 5,6,7,8

of the channel and are channel-aligned with

the ID[x] data stream. ISIG[x] is updated on

the active edge of the common ingress clock,

CICLK.

IFP[1]

IFP[2]

IFP[3]

IFP[4]

IFP[5]

IFP[6]

IFP[7]

IFP[8]

Output 95

90

87

82

79

76

71

68

D9

D11

E11

G12

H12

J12

L12

J10

Ingress Frame Pulse (IFP[1:8]). The IFP[x]

outputs are intended as timing references.

IFP[x] indicates the frame alignment or the

superframe alignment of the ingress stream,

ID[x].

When Clock Master: Full DS1 mode is active,

IFP[x] is updated on the active edge of the

associated ICLK[x]. When Clock Master:

NxDS0 mode is active, ICLK[x] is gapped

during the pulse on IFP[x]. When the Clock

Slave ingress modes are active, IFP[x] is

updated on the active edge of CICLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

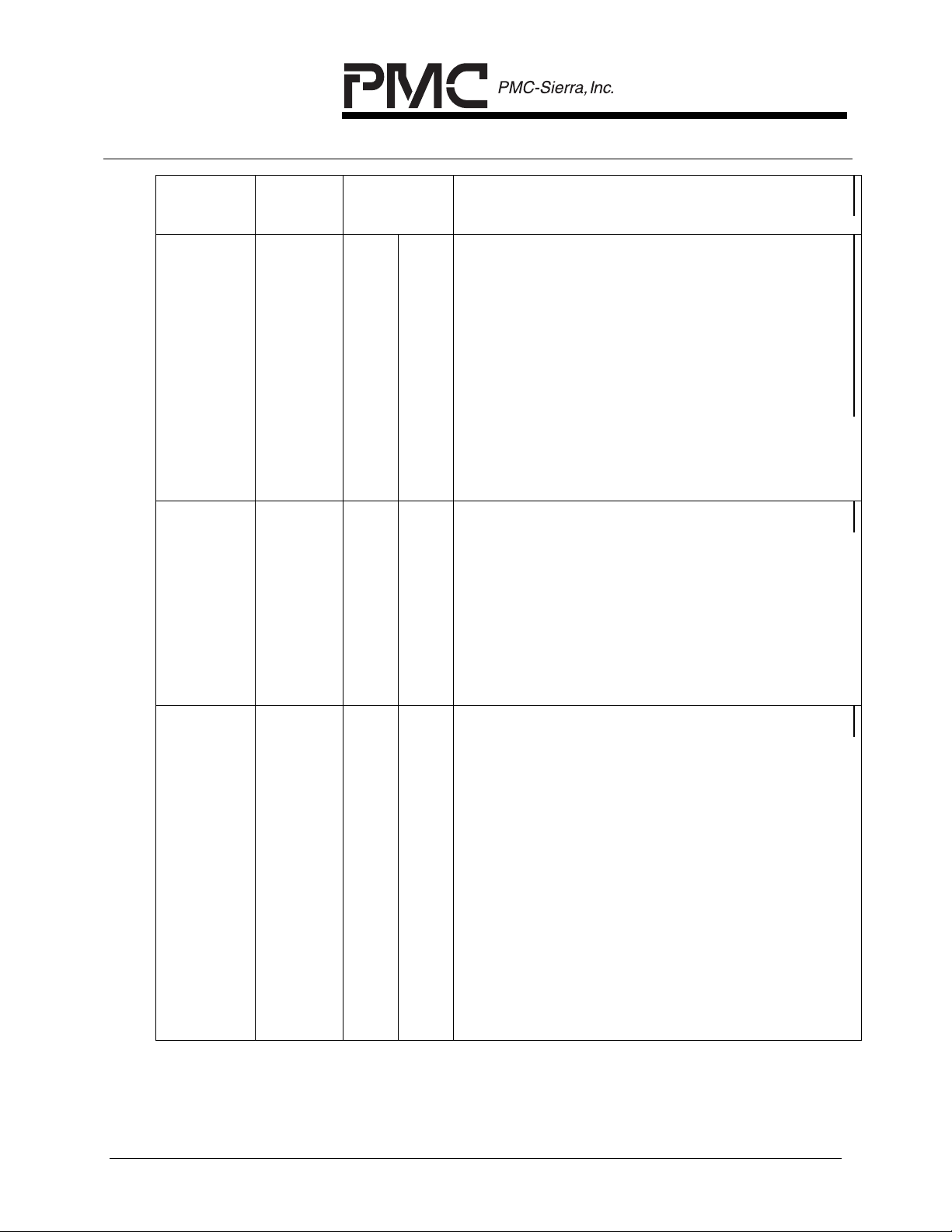

Pin

Name

ID[1]

ID[2]

ID[3]

ID[4]

ID[5]

ID[6]

ID[7]

ID[8]

Type Pin No.

-RI -NI

Output 97

94

89

84

81

78

73

70

B12

C12

E10

F12

F9

G10

J11

K11

Function

Ingress Data (ID[1:8]). Each ID[x] signal

contains the recovered data stream which may

have been passed through the elastic store.

When the Clock Slave ingress modes are

active, the ID[x] stream is aligned to the

common ingress timing and is updated on the

active edge of CICLK.

When the Clock Master ingress modes are

active, ID[x] is aligned to the receive line timing

and is updated on the active edge of the

associated ICLK[x].

CICLK Input 120 A5 Common Ingress Clock (CICLK). CICLK is

either a 1.544MHz or 2.048MHz clock with

optional gapping for adaptation to non-uniform

backplane data streams. CICLK is common to

all eight framers. CIFP is sampled on the

active edge of CICLK. When the Clock Slave

ingress modes are active, ID[x], ISIG[x], and

IFP[x] are updated on the active edge of

CICLK.

CIFP Input 119 B5 Common Ingress Frame Pulse (CIFP). When

the elastic store is enabled (Clock Slave mode

is active on the ingress side), CIFP is used to

frame align the ingress data to the system

frame alignment. CIFP is common to all eight

framers. When frame alignment is required, a

pulse at least 1 CICLK cycle wide must be

provided on CIFP a maximum of once every

frame (nominally 193 bit times or 256 bit times

if the 2.048 MHz rate is selected). If ingress

signaling alignment is required, ingress

signaling alignment must be enabled, and a

pulse at least 1 CICLK cycle wide must be

provided on CIFP every 12 or 24 frame times.

CIFP is sampled on the active edge of CICLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

Pin

Name

ED[1]

ED[2]

ED[3]

ED[4]

ED[5]

ED[6]

ED[7]

ED[8]

EFP[1]

EFP[2]

EFP[3]

EFP[4]

EFP[5]

EFP[6]

EFP[7]

EFP[8]/

Type Pin No.

-RI -NI

Input 115

113

111

109

105

103

101

99

I/O 114

112

110

106

104

102

100

98

B7

D6

A8

D7

B9

A11

A12

B11

A7

B8

C7

A10

D8

B10

C9

C10

Function

Egress Data (ED[1:8]). The egress data

streams to be transmitted are input on these

pins. When the Clock Master: Full DS1 mode

is active, ED[x] is sampled on the rising edge

of TLCLK[x]. When the Clock Master: NxDS0

mode is active, ED[x] is sampled on the active

edge of ECLK[x]. When the Clock Slave

egress modes are active, ED[x] is sampled on

the active edge of CECLK.

Egress Frame Pulse (EFP[1:8]). When the

Clock Master: Full DS1 or Clock Slave: EFP

Enabled modes are active, the EFP[1:8]

outputs indicate the frame alignment or the

superframe alignment of each of the eight

framers. When the Clock Master modes are

active, EFP[x] is updated by the falling edge of

the TLCLK[x]. When the Clock Slave egress

modes are active, EFP[x] is updated on the

active edge of CECLK.

ECLK[1]

ECLK[2]

ECLK[3]

ECLK[4]

ECLK[5]

ECLK[6]

ECLK[7]

ECLK[8]

ESIG[1]

ESIG[2]

ESIG[3]

ESIG[4]

ESIG[5]

ESIG[6]

ESIG[7]

ESIG[8]

Egress Clock (ECLK[1:8]). When the Clock

Master: NxDS0 mode is active, the ECLK[x]

output is used to sample the associated egress

data (ED[x]). ECLK[x] is a version of TLCLK[x]

that is gapped during the framing bit position

and optionally for between 1 and 23 DS0

channels in the associated ED[x] stream.

ED[x] is sampled on the active edge of the

associated ECLK[x].

Egress Signaling (ESIG[1:8]). When the Clock

Slave: External Signaling mode is active, the

ESIG[8:1] inputs contain the signaling bits for

each channel in the transmit data frame,

repeated for the entire superframe. Each

channel's signaling bits are in bit locations

5,6,7,8 of the channel and are frame-aligned

by the common egress frame pulse, CEFP.

ESIG[x] is sampled on the active edge of

CECLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

PM4388 TOC TL

DATA SHEET

PMC-960840 ISSUE 5 OCTAL T1 FRAMER

Pin

Name

Type Pin No.

-RI -NI

Function

CTCLK Input 123 A4 Common Transmit Clock (CTCLK). This input

signal is used to generate the TLCLK[x] clock

signals. Depending on the configuration of the

TOCTL, CTCLK may be a 12.352 MHz clock

(so TLCLK[x] is generated by dividing CTCLK

by 8), or a line rate clock (so TLCLK[x] is

generated directly from CTCLK, or from

CTCLK after jitter attenuation), or a multiple of

8kHz (Nx8khz, where 1•N•256) so long as

CTCLK is jitter-free when divided down to

8kHz (in which case TLCLK is derived by the

DJAT PLL using CTCLK as a reference).

The TOCTL may be configured to ignore the

CTCLK input and utilize CECLK or RLCLK[x]

instead. RLCLK[x] is automatically substituted

for CTCLK if line loopback is enabled.

CECLK Input 122 B4 Common Egress Clock (CECLK). The

common egress clock is used to time the

egress interface when Clock Slave mode is

enabled in the egress side. CECLK may be a

1.544MHz or 2.048MHz clock with optional

gapping for adaptation from non-uniform

system clocks. When the Clock Slave: EFP

Enabled mode is active, CEFP and ED[x] are

sampled on the active edge of CECLK, and

EFP[x] is updated on the active edge of

CECLK. When the Clock Slave: External

Signaling mode is active, CEFP, ESIG[x] and

ED[x] are sampled on the active edge of

CECLK.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

Loading...

Loading...