Combined E1/T1/J1 Transceiver/Framer

PM4351

COMET

FEATURES

• Monolithic 3.3 V device that integrates

an E1/T1/J1 Framer and line driver for

shorthaul and longhaul app lic at ions.

• Software selectable between T1/J1

and E1 operation on a per device

basis.

• Provides fully p rogram mable shorth aul

and longhaul pulse templates and line

build out.

• Meets or exceeds T1, J1, and E1

shorthaul and lo nghaul network ac cess

specifications, which include:

ANSI T1.102, T1.403, T1.408, AT&T

TR 62411, ITU-T G.703 and G.823, as

well as the newer G.775 and

ETSI 300-011 specifications.

• Supports B8ZS, HDB3, and AMI line

codes.

• Provides receive clock recovery and

line performance monitoring.

• Provides on-board binary sequence

generators and detectors that can be

configured with various patterns for

error testing, including those

conforming to ITU-T 0.151.

• Provides transmit and receive jitter

attenuation.

• Provides three full-featured HDLC

controllers, each with 128-byte

transmit and receive FIFOs, enabling

dual compliance to the V5.1 and V5.2

interface standards.

• Supports an IEEE P1149.1 JTAG test

port.

• Automatically generates DS1

performance report messages to ANSI

T1.231 and other specifications.

• Compatible with Mitel ST

, and MVIP PCM backplanes

CHI

supporting rates of 1.544 Mbit/s,

2.048 Mbit/s, 4.096 Mbit/s and

8.192 Mbit/s.

• Provides an 8-bit microprocessor bus

interface for config uration , contro l, a nd

status monitoring.

• Low power +3.3 V CMOS technology.

• Available in an 80-pin PQFP (14 mm

by 14 mm) and an 81-pin CABGA (9

mm by 9 mm) package.

• Provides a -40 °C to +85 °C industrial

temperature operating rang e.

-bus, AT&T

RECEIVE

• Provides single-rail digital PCM and

signaling outputs for 1.544 Mbit/s,

2.048 Mbit/s, 4.096 Mbit/s, or

8.192 Mbit/s backplane buses.

• Guaranteed signal recovery of up to

-36 dB at 1024 kHz (E1) and 772 kHz

(T1/J1) under production test

conditions (VDD = 3.069 V, 25 °C)

using PIC-22 gauge cable emulation.

• Frames to a G.704 E1 signal.

• Frames to a JT-G704 J1 signal.

• Frames to a DSX/DS-1 signal in D4,

SF, ESF, or SLC

96 formats.

• Accommodates up to 0.4 UI peak-to peak, high frequency jitter as required

by AT&T TR 62411.

• Supports line and path performance

monitoring to AT&T and ANSI

specifications and ITU-T

recommendations.

• Detects both programmable in-band

loopback activate and deactivate code

sequences receiv ed in the DS 1/E1

data stream.

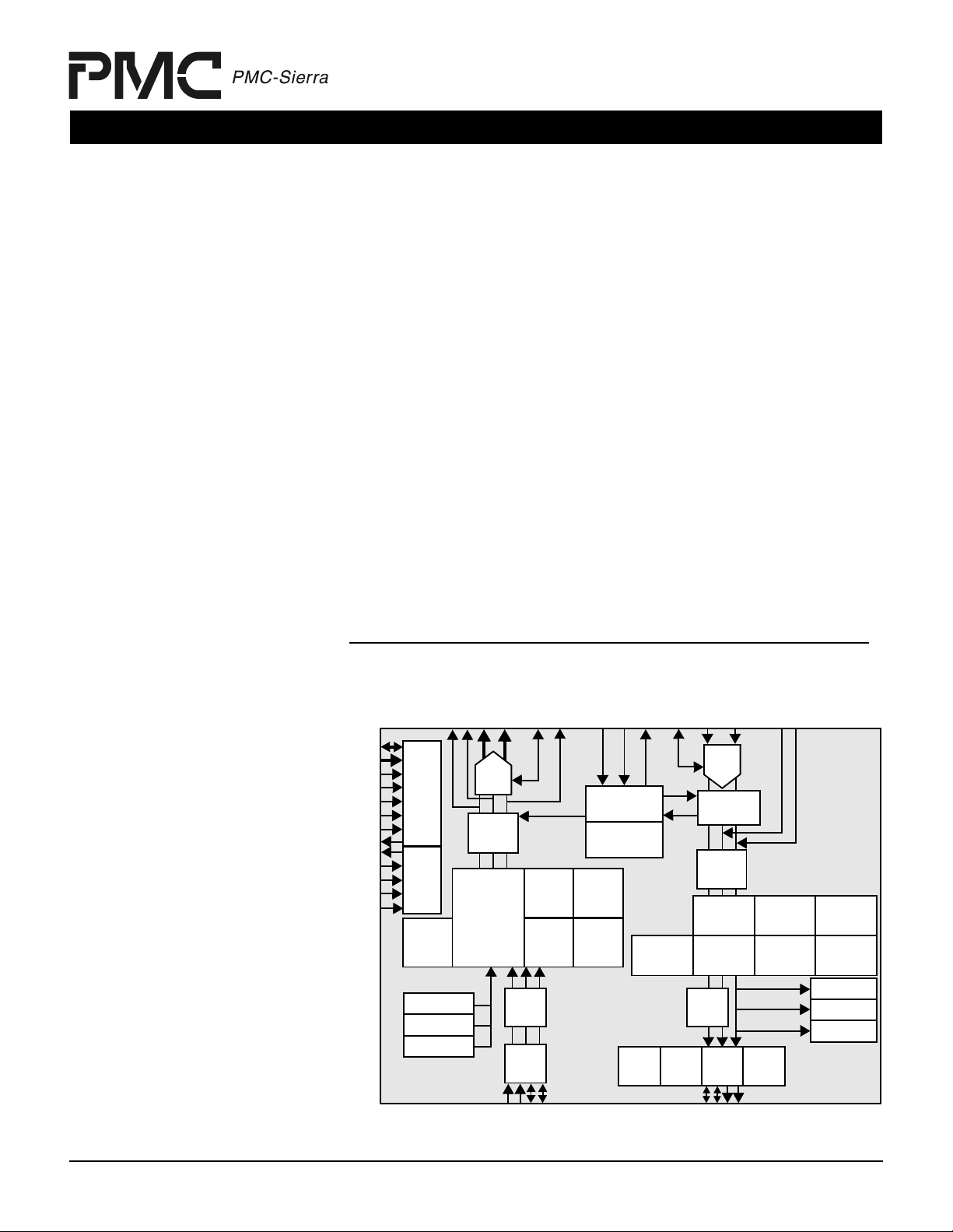

BLOCK DIAGRAM

TDAT

TFP

TXTIP[1:0]

TXRING[1:0]

TVREF

TCLKO

D[7:0]

A[8:0]

RDB

WRB

CSB

ALE

RSTB

INTB

TDO

TCK

TMS

TRSTB

TDI

MPIF

Micro-

processor

Interface

JTAG

Test

Access

Port

XBOC

Bit-Oriented

Code

Generator

TDPR #3

HDLC Transmitter

TDPR #2

HDLC Transmitter

TDPR #1

HDLC Transmitter

XLPG

Transmit

LIU

TJAT

Transmit

Digital Jitter

Attenuator

T1-XBAS/

E1-TRAN

Basic Transmitter:

Frame Generation,

Alarm Insertion,

Signaling Insertion,

Trunk Conditioning

Backplane

TX-ELST

Elastic

Store

BTIF

Transmit

Interface

IBCD

In-band

Loopback

Code

Detector

FRMR

Frame

Alignment,

Alarm

Extraction

Performance

XCLK /VCLK

Clock Synthesis

and Distribution

Timing Options

PMON

Monitor

Counters

ALMI

Alarm

Integrator

TRANSMIT

• Supports transfer of transmitted PCM

and signaling data from 1.544 Mbit/s,

2.048 Mbit/s, 4.096 Mbit/s, or

8.192 Mbit/s backplane buses.

• Supports tristate line outputs.

• Generates DSX-1 T1 shorthaul- and

T1 longhaul-compatible pulses with

programmable pulse shape to AT&T

and ANSI specifications and ITU-T

recommendations.

• Generates G.703 E1 pulses.

• Detects violations of the ANSI T1.403

12.5% pulse density rule over a

moving 192-bit window.

• Allows insertion of in-band loopback

code sequences.

• Supports transmission of the Alarm

Indication Signal (AIS) or the yellow

alarm signal in all formats.

• Provides a FIFO for jitt er attenuatio n in

the transmit path.

• Complies to all jitter attenuation, jitter

transfer and residual jitter

specifications required by AT&T T R

62411 and ETSI TBR12/13.

TCLKI

CSD

TOPS

PRGD

½ Pattern

Generator/

Detector

RSYNC

FRAM

Framing

RAM

RVREF

RPSC

Per-DS0

Serial

Controller

RXTIP

RLPS

Receive

LIU

CDRC

Clock and Data

Recovery

RJAT

Receive

Digital Jitter

Attenuator

IBCD

In-Band

Loopback Code

Detector

FRMR

Frame

Alignment,

Alarm Extraction

RX-ELST

Elastic

Store

BRIF

Backplane

Receive

Interface

RXRING

Signalling

Extractor

Performance

Monitor

Counters

Integrator

E1/T1-

SIGX

RDAT

PMON

ALMI

Alarm

RCLKI

HDLC Receive r

HDLC Receive r

HDLC Receive r

PDVD

Pulse Density

Violation

Detector

BRIF

Bit-Oriented

Code Detector

RDLC #3

RDLC #2

RDLC #1

BTFP

BTSIG

BTCLK

BTPCM

PMC-1961230 (R3) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2001

BRFP

BRSIG

BRCLK

BRPCM

Combined E1/T1/J1 Transceiver/Framer

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

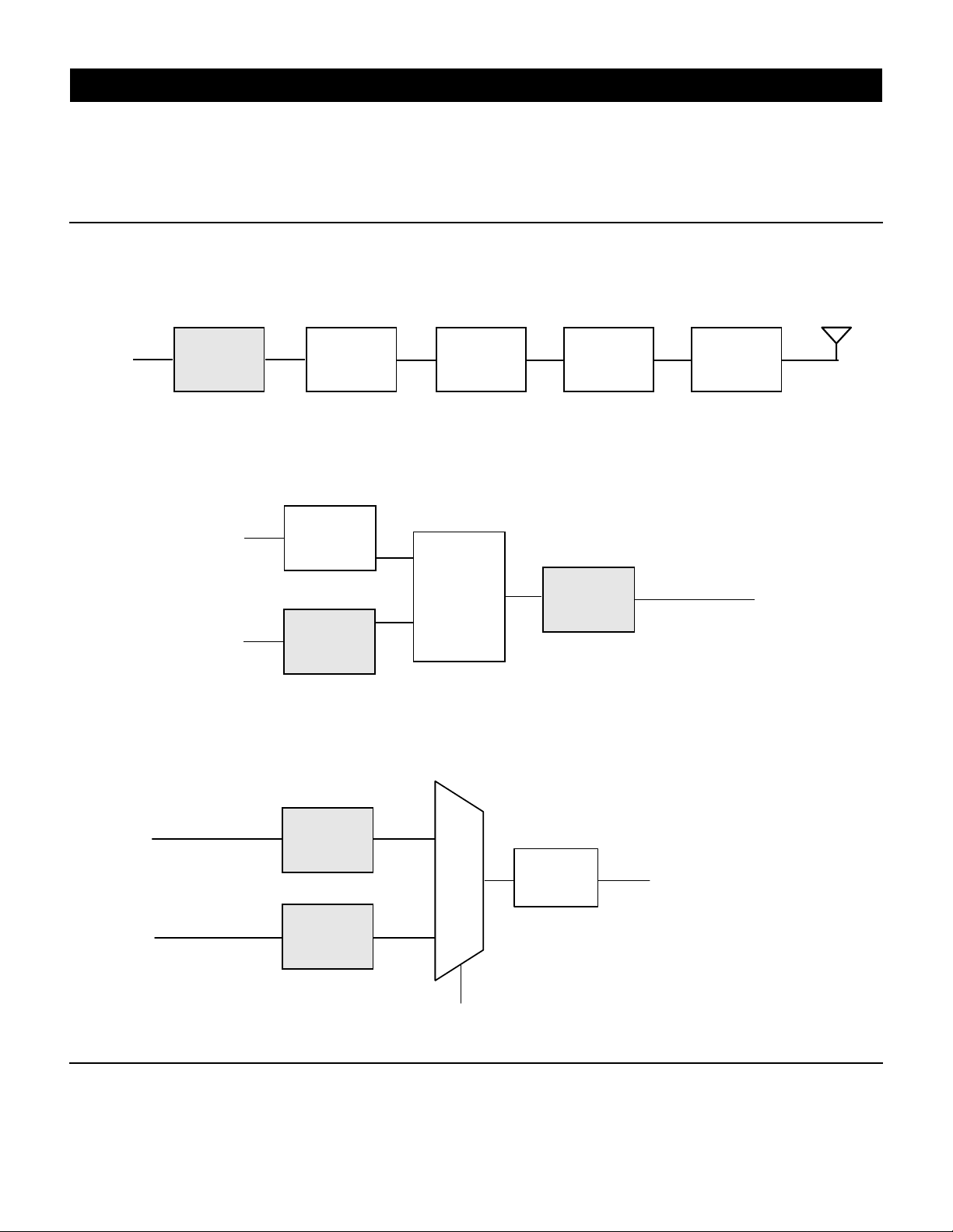

INTEGRATED ACCESS DEVICE (IAD)

APPLICATIONS

• Wireless Base Tr ansceiver S tation and

Digital LoopCarriers (DLCs).

• BITS Timing Systems.

TYPICAL APPLICATIONS

WIRELESS BASE TRANSCEIVER STATION (BTS)

• Integrated Access Device (IAD).

• Channel and Data Service Units

(CSU/DSU).

PM4351 COMET

• Enterpri se Routers.

• V5.1/V5.2 Interfaces.

E1 or T1

PM4351

COMET

Ethernet

(Data)

E1 or T1

(Voice)

BITS TIMING APPLICATION

ATM UNI

& AAL2

Processing

10 Base T

PHY

PM4351

COMET

Modem

CrossConnect and

Interworking

PM7815

PALADIN-15

PM4351

COMET

RF

T1

ATM or

Packet

T1

BITS Timing

PM4351

COMET

Signal A

T1

BITS Ti ming

PM4351

COMET

Signal B

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

Timing Selector

PLL

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corporate informatio n,

send email to:

info@pmc-sierra.com

Recovered

Timing

PMC-1961230 (R3)

© Copyright PMC-Sierra, Inc. 2001.

All rights reserved. July 2001 .

®

SLC

96, ST, and CHI are registered

trademarks of AT&T.

COMET, PALADIN-15, and PMC-Sierra are

trademarks of PMC-Sierra, Inc.

Loading...

Loading...