T1 TRANSCEIVER

PM4341A

T1XC

Summary Information

FEATURES

• Monolithic single chip device which

integrates a full featured T1 framer

with an on-chip analog line interface.

• Supports SF, ESF, T1DM (DDS) and

SLC®96 format DS1 signals.

Supports unframed mode. Supports

B8ZS or AMI line codes.

• Recovers clock and data from the

incoming DSX-1 signal, generates

DSX-1 output signal.

• Supports transfer of PCM and

signalling to/from 1.544 Mbit/s and

2.048 Mbit/s backplane buses.

Supports gapped data streams used

in higher rate multiplexing.

• Provides robbed bit signalling

insertion/extraction, idle code

substitution, digital milliwatt code

substitution, data inversion and 2

superframes of signalling debounce

on a per channel basis.

• Pin compatible with the PM6341

E1XC E1 Transceiver.

• Software compatible with the

PM4344 TQUAD Quad T1 Framer

and PM4388 TOCTL Octal T1

Framer.

• Provides an 8-bit microprocessor bus

interface for configuration, control

and status monitoring.

• Low-power 5V CMOS technology.

• Avalable in a high density 80-pin (14

by14mm) PQFP or in a 68-pin PLCC

package.

APPLICATIONS

• T1 & T3 Multiplexers

• T1 Frame Relay Interfaces

• T1 ATM UNI Interfaces

• Fractional T1

• T1 Channel Service Units (CSUs)

and Data Service Units (DSUs)

• Digital Access and Cross-Connect

Systems (DACS) and Electronic

Digital Cross-Connects (EDSX)

• Digital Loop Carriers (DLCs)

• SONET Add-Drop Multiplexers

(ADM)

• ISDN Primary Rate Interfaces (PRI)

• Digital Private Branch Exchanges

(PBX)

• T1 & T3 Test Equipment

SLC®96 is a registered trademark of AT&T

RECEIVE SECTION

• Provides loss of signal, red alarm,

yellow alarm and AIS alarm

indication. Detects violations of the

ANSI T1.403 12.5% pulse density

rule over a moving 192 bit window.

• Supports line and path performance

monitoring per Bellcore, AT&T and

ANSI recommendations.

• Accumulators are provided for ESF

CRC-6 and framing bit errors, Line

Code Violations and Loss Of Frame

or Change Of Frame Alignment

events.

• Extracts the data link in ESF, T1DM

and SLC®96 formats. Extracts the

D-channel for primary rate interfaces.

• Provides ESF bit-oriented code

detection and an HDLC interface for

terminating the ESF datalink.

• Provides a 2 frame elastic store for

jitter and wander attenuation.

• Detects programmable in-band

loopback codes.

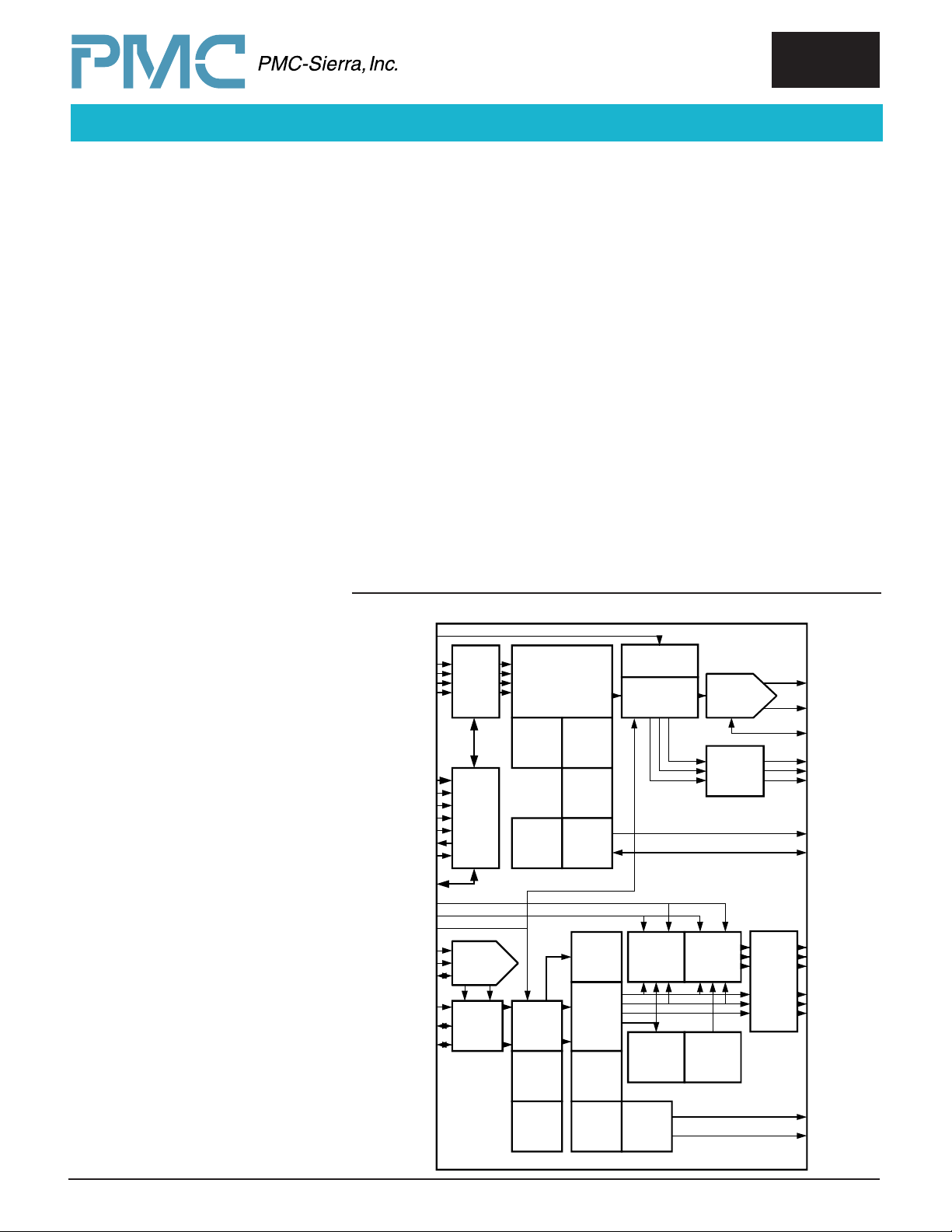

BLOCK DIAGRAM

TCLKI

BTPCM/BTDP

BTSIG/BTDN

BTFP

BTCLK

A(7-0)

RDB

WRB

CSB

ALE

INTB

RSTB

D(7-0)

BRCLK

BRFPI

XCLK/VCLK

RAS

REF

RRC

RCLKI

RDP/RDD /

SDP

RDN/RLC V /

SDN

BTIF

BACKPLANE

TRANSMIT

INTER-

FACE

MPIF

MICRO-

PROCESS-

OR

INTERFACE

RSLC

ANALOG

DSX-1 PULSE

SLICER

DRIF

DIGITAL

DS-1 RX

INTER-

FACE

XBAS

BASICTRANSMITTER:

FRAME GENERATION,

ALARM INSERTION,

TRUNK CO N DITIONING

LINE CODI NG

TPSC

PER-CHAN

CONT :

SIG,IDLE,

XBOC

BIT-

CDRC

DATA

IBCD

IN-BAND

CODE

PDVD

PULSE

DENSITY

GENERATOR

ZERO CONT

ORIENTED

CODE GE N .

CLOCK A N D

RECOVERY

LOOPBACK

DETECT OR

VIOLATION

DETECT O R

IN-BA ND

LOOPBACK

CODE

PULSE

DENSITY

ENFORCER

TRANSMITTER

FORMANCE

COUNTERS

ALIGNMENT,

XIBC

XPDE

XFDL

HDLC

PMON

PER-

MONITOR

FRMR

FRAMER:

FRAME

ALARM

EXTRACT

ALMI

ALARM

INTE-

GRATOR

RBOC

BIT-

ORIENTED

CODE

DETECTO R

TRANSMIT SECTION

• Provides per channel minimum ones

density through Bell (Bit 7), GTE or

DDS zero code suppression.

• Detects violations of the ANSI T1.403

12.5% pulse density rule over a

moving 192 bit window.

• Inserts the data link in ESF, T1DM

and SLC®96 formats. Inserts the Dchannel for primary rate interfaces.

• Generates AIS and yellow alarm in

all formats.

• Inserts the data link in ESF, T1DM

and SLC®96 formats. Inserts the Dchannel for primary rate interfaces.

• Generates ESF bit-oriented codes

and provides an HDLC interface for

generating the ESF datalink.

• Inserts programmable in-band

loopback codes.

• Provides a FIFO buffer for jitter

attenuation and rate conversion.

TOPS

TIMING OPTIONS

DJAT

DIGITAL JITTER

ATTENUATOR

ELST

ELASTIC

STORE

FRAM

FRAMER/

SLIP BUFFER

RAM

RFDL

HDLC

RECEIVE R

TRANSMITTER

XPLS

ANALOG DSX-1

PULSE

GENERATOR

DIGITAL DS-1

TRANSMIT

INTE R FAC E

SIGX

SIGNALLING

EXTRACT-

OR

RPSC

PER-CHANNEL

CONTRO L:

TRUNK

CONDITION

DTIF

RECEIVER

BRIF

BACKPLANE

RECEIVE

INTER-

FACE

TAP

TAN

TC

TCLKO

TDP/TDD

TDN/TFLG

TDLCLK/

TDLUDR

TDLSIG/

TDLINT

BRPCM/BRDP

BRSIG/BRDN

BRFPO

RDPCM /RPCM

RCLKO

RFP

RDLSIG/

RDLINT

RDLCLK/

RDLEOM

PMC

-920108(R7)

© 1998 PMC-Sierra, Inc. March, 1998

T1 TRANSCEIVER

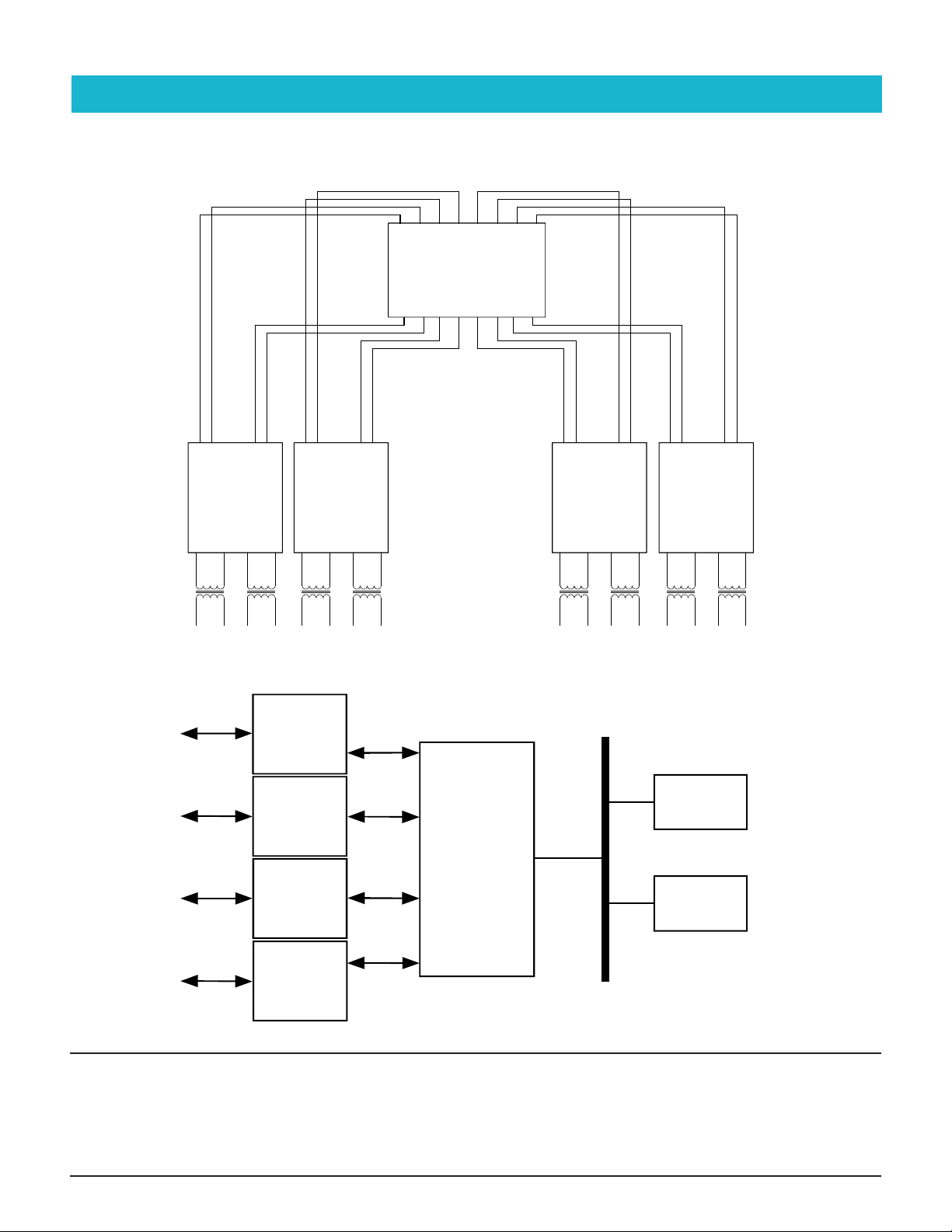

TYPICAL APPLICATIONS:

1/0 CROSS-CONNECT WITH DSX-1 INTERFACE:

PM4341A T1XC

Summary Information

BTSIG

BTPCM

PMC

PM4341A

T1XC

TAP

DSX-1

Transmit

TAN

BRSIG

BRPCM

RAS

DSX-1

Receive

BTSIG

BTPCM

PMC

PM4341A

T1XC

TAP

REF

DSX-1

Transmit

TAN

BRSIG

BRPCM

REF

RAS

DSX-1

Receive

FULLY CHANNELIZED QUAD DS1 HDLC CARD:

STo1

STo2

STo3

Digital Crosspoint

Switch

STi2

STi3

STi1

STo4

STi4

STo5

STi5

STo6

STi6

STo7

STi7

STo8

STi8

BTSIG

BTPCM

PM4341A

TAP

DSX-1

Transmit

PMC

T1XC

TAN

BRSIG

BRPCM

RAS

DSX-1

Receive

BTSIG

BTPCM

PMC

PM4341A

T1XC

TAP

REF

DSX-1

Transmit

TAN

BRSIG

BRPCM

REF

RAS

DSX-1

Receive

DS1

DS1

DS1

DS1

Head Office:

PMC-Sierra, Inc.

Suite 105 - 8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

PMC

PM4341A

T1XC

PMC

PM4341A

T1XC

PMC

PM4341A

T1XC

PMC

PM4341A

T1XC

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn:Document Coordinator

PMC

PM7366

FREEDM-8

HDLC

Controller

All product documentation is

available on our web site at:

http://www.pmc-sierra.com

For corporate information,

send email to:

info@pmc-sierra.com

Processor

Packet

Memory

PCI Bu s

PMC-920108(R7)

© 1998

PMC-Sierra, Inc.

March, 1998

Loading...

Loading...