PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

PM4332

TE-32

HIGH DENSITY 32 CHANNEL T1/E1/J1

FRAMER

DATA SHEET

PROPRIETARY AND CONFIDENTIAL

PRELIMINARY

ISSUE 1: JUNE 2001

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS i

CONTENTS

1 FEATURES .............................................................................................. 1

2 APPLICATIONS ....................................................................................... 7

3 REFERENCES......................................................................................... 8

4 APPLICATION EXAMPLES ....................................................................11

5 BLOCK DIAGRAM ................................................................................. 14

6 DESCRIPTION....................................................................................... 16

7 PIN DIAGRAM ....................................................................................... 19

8 PIN DESCRIPTION................................................................................ 20

9 FUNCTIONAL DESCRIPTION............................................................... 49

9.1 T1 FRAMING............................................................................... 49

9.2 E1 FRAMING .............................................................................. 51

9.3 T1/E1 PERFORMANCE MONITORING...................................... 58

9.4 T1/E1 HDLC RECEIVER............................................................. 59

9.5 T1/E1 ELASTIC STORE (ELST) ................................................. 60

9.6 T1/E1 SIGNALING EXTRACTION .............................................. 60

9.7 T1/E1 RECEIVE PER-CHANNEL CONTROL ............................. 61

9.8 T1 TRANSMITTER...................................................................... 61

9.9 E1 TRANSMITTER...................................................................... 63

9.10 T1/E1 HDLC TRANSMITTERS ................................................... 63

9.11 T1/E1 RECEIVE AND TRANSMIT DIGITAL JITTER

ATTENUATORS .......................................................................... 64

9.12 T1/E1 PSEUDO RANDOM BINARY SEQUENCE GENERATION

AND DETECTION (PRBS).......................................................... 70

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS ii

9.13 EGRESS H-MVIP SYSTEM INTERFACE ................................... 70

9.14 INGRESS SYSTEM H-MVIP INTERFACE.................................. 72

9.15 EXTRACT SCALEABLE BANDWIDTH INTERCONNECT (EXSBI)

.................................................................................................... 74

9.16 INSERT SCALEABLE BANDWIDTH INTERCONNECT (INSBI). 75

9.17 JTAG TEST ACCESS PORT ....................................................... 76

9.18 MICROPROCESSOR INTERFACE ............................................ 77

10 NORMAL MODE REGISTER DESCRIPTION ....................................... 85

10.1 TOP LEVEL MASTER REGISTERS ........................................... 86

10.2 T1/E1 MASTER CONFIGURATION REGISTERS .....................110

10.3 T1/E1 RECEIVE JITTER ATTENUATOR (RJAT) REGISTERS..118

10.4 T1/E1 TRANSMIT JITTER ATTENUATOR (TJAT) REGISTERS122

10.5 T1/E1 RECEIVE H-MVIP PER-CHANNEL CONTROLLER (RPCC)

REGISTERS.............................................................................. 126

10.6 T1/E1 RECEIVE SBI PER-CHANNEL CONTROLLER (RPCC-SBI)

REGISTERS.............................................................................. 142

10.7 T1/E1 RECEIVE H-MVIP ELASTIC STORE (RX-MVIP-ELST)

REGISTERS.............................................................................. 159

10.8 T1/E1 RECEIVE SBI ELASTIC STORE (RX-SBI-ELST)

REGISTERS.............................................................................. 166

10.9 T1/E1 TRANSMIT ELASTIC STORE (TX-ELST) REGISTERS. 177

10.10 T1/E1 TRANSMIT PER-CHANNEL CONTROLLER (TPCC)

REGISTERS.............................................................................. 186

10.11 T1/E1 RECEIVE HDLC CONTROLLER (RHDL) REGISTERS . 203

10.12 T1/E1 TRANSMIT HDLC CONTROLLER (THDL) REGISTERS 214

10.13 T1/E1 SIGNALING EXTRACTOR REGISTERS........................ 226

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS iii

10.14 T1/E1 TRANSMITTER REGISTERS......................................... 237

10.15 T1/E1 FRAMER REGISTERS................................................... 249

10.16 SYSTEM SIDE SBI (SCALEABLE BANDWIDTH INTERCONNECT)

MASTER CONFIGURATION REGISTER ................................. 283

10.17 SYSTEM SIDE EXSBI (EXTRACT SCALEABLE BANDWIDTH

INTERCONNECT) REGISTERS ............................................... 287

10.18 SYSTEM SIDE INSBI (INSERT SCALEABLE BANDWIDTH

INTERCONNECT) REGISTERS ............................................... 299

10.19 FULL FEATURED T1/E1 PATTERN GENERATORS AND

RECEIVERS...............................................................................311

10.20 T1/E1 PATTERN GENERATOR AND DETECTOR REGISTERS311

10.21 LINE SIDE SBI MASTER CONFIGURATION REGISTERS ...... 336

10.22 LINE SIDE INSBI REGISTERS................................................. 342

10.23 LINE SIDE EXSBI REGISTERS................................................ 349

11 TEST FEATURES DESCRIPTION....................................................... 361

11.1 JTAG TEST PORT .................................................................... 363

12 OPERATION ........................................................................................ 370

12.1 SLC96 .................................................................................... 370

12.2 SERVICING INTERRUPTS....................................................... 371

12.3 USING THE PERFORMANCE MONITORING FEATURES ...... 372

12.4 USING THE INTERNAL T1/E1 DATA LINK RECEIVER............ 376

12.5 USING THE INTERNAL T1/E1 DATA LINK TRANSMITTER..... 378

12.6 USING THE TIME-SLICED T1/E1 TRANSCEIVERS ................ 380

12.7 T1 AUTOMATIC PERFORMANCE REPORT FORMAT ............ 381

12.8 T1/E1 FRAMER LOOPBACK MODES...................................... 383

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS iv

12.9 LINE SIDE SBI BUS LOOPBACK MODE ................................. 385

12.10 SBI BUS DATA FORMATS ........................................................ 385

12.11 H-MVIP DATA FORMAT ............................................................ 396

12.12 JTAG SUPPORT ....................................................................... 401

13 FUNCTIONAL TIMING......................................................................... 409

13.1 SBI BUS INTERFACE TIMING.................................................. 409

13.2 EGRESS H-MVIP LINK TIMING................................................ 410

13.3 INGRESS H-MVIP LINK TIMING ...............................................411

14 ABSOLUTE MAXIMUM RATINGS ....................................................... 412

15 D.C. CHARACTERISTICS ................................................................... 413

16 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS ..... 416

17 TE-32 TIMING CHARACTERISTICS ................................................... 420

18 ORDERING AND THERMAL INFORMATION...................................... 434

19 MECHANICAL INFORMATION ............................................................ 435

LIST OF FIGURES

FIGURE 1 - EDGE ROUTER LINE CARD.........................................................11

FIGURE 2 - MULTISERVICE SWITCH............................................................. 12

FIGURE 3 - VOICE GATEWAY APPLICATION................................................. 13

FIGURE 4 - TE-32 BLOCK DIAGRAM ............................................................ 14

FIGURE 5 - PIN DIAGRAM ............................................................................. 19

FIGURE 6 - CRC MULTIFRAME ALIGNMENT ALGORITHM ......................... 55

FIGURE 7 - JITTER TOLERANCE T1 MODES............................................... 66

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS v

FIGURE 8 - JITTER TOLERANCE E1 MODES .............................................. 67

FIGURE 9 - JITTER TRANSFER T1 MODES ................................................. 68

FIGURE 10-JITTER TRANSFER E1 MODES.................................................. 69

FIGURE 11 - EGRESS CLOCK SLAVE: H-MVIP.............................................. 71

FIGURE 12- INGRESS CLOCK SLAVE: H-MVIP............................................. 72

FIGURE 13 - INSERT SBI SYSTEM INTERFACE............................................ 75

FIGURE 14- FER COUNT VS. BER (E1 MODE) ........................................... 373

FIGURE 15- CRCE COUNT VS. BER (E1 MODE) ........................................ 374

FIGURE 16- FER COUNT VS. BER (T1 ESF MODE).................................... 375

FIGURE 17- CRCE COUNT VS. BER (T1 ESF MODE)................................. 376

FIGURE 18- CRCE COUNT VS. BER (T1 SF MODE) ................................... 376

FIGURE 19- T1/E1 LINE LOOPBACK............................................................ 384

FIGURE 20- T1/E1 DIAGNOSTIC DIGITAL LOOPBACK............................... 384

FIGURE 21- BOUNDARY SCAN ARCHITECTURE....................................... 401

FIGURE 22- TAP CONTROLLER FINITE STATE MACHINE......................... 403

FIGURE 23- INPUT OBSERVATION CELL (IN_CELL) .................................. 406

FIGURE 24- OUTPUT CELL (OUT_CELL) .................................................... 407

FIGURE 25- BIDIRECTIONAL CELL (IO_CELL)............................................ 407

FIGURE 26- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS 408

FIGURE 27- SBI BUS T1/E1 FUNCTIONAL TIMING ..................................... 409

FIGURE 28- SYSTEM INTERFACE SBI ADD BUS JUSTIFICATION REQUEST

FUNCTIONAL TIMING................................................................. 410

FIGURE 29- EGRESS 8.192 MBIT/S H-MVIP LINK TIMING ..........................411

FIGURE 30- INGRESS 8.192 MBIT/S H-MVIP LINK TIMING .........................411

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS vi

FIGURE 31- LINE SIDE SBI BUS INPUT TIMING ......................................... 421

FIGURE 32- LINE SIDE SBI BUS OUTPUT TIMING ..................................... 422

FIGURE 33- LINE SIDE SBI BUS TRISTATE OUTPUT TIMING.................... 422

FIGURE 34- SYSTEM SIDE SBI ADD BUS TIMING...................................... 424

FIGURE 35- SYSTEM SIDE SBI DROP BUS TIMING................................... 426

FIGURE 36- SYSTEM SIDE SBI DROP BUS COLLISION AVOIDANCE TIMING

..................................................................................................... 426

FIGURE 37- H-MVIP EGRESS DATA & FRAME PULSE TIMING.................. 428

FIGURE 38- H-MVIP INGRESS DATA TIMING.............................................. 429

FIGURE 39- XCLK INPUT TIMING ................................................................ 430

FIGURE 40- TRANSMIT LINE INTERFACE TIMING ..................................... 431

FIGURE 41- JTAG PORT INTERFACE TIMING............................................. 433

FIGURE 42- 324 PIN PBGA 23X23MM BODY............................................... 435

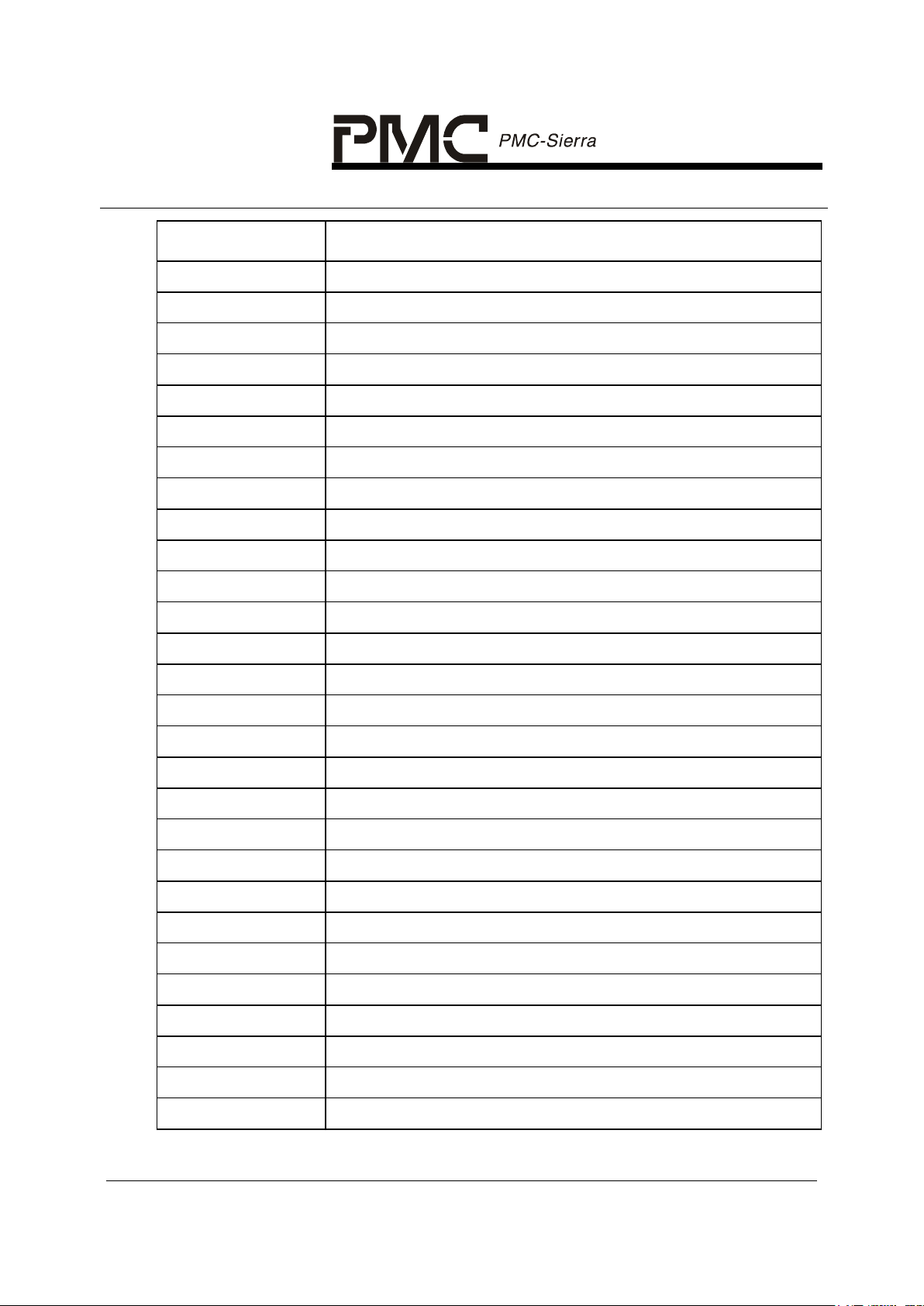

LIST OF TABLES

TABLE 1 - E1 FRAMER FRAMING STATES ................................................ 56

TABLE 2 - REGISTER MEMORY MAP......................................................... 77

TABLE 3 - SYSTEM SIDE EXSBI TRIB_TYP ENCODING......................... 294

TABLE 4 - SYSTEM INTERFACE INSBI TRIB_TYP ENCODING .............. 307

TABLE 5 - GENERATOR CONTROLLER INDIRECT REGISTER MAP ..... 327

TABLE 6 - GENERATOR CONTROLLER INDIRECT REGISTERS 0X20-0X3F:

DDS CONTROL BYTE................................................................. 329

TABLE 7 - GENERATOR CONTROLLER INDIRECT REGISTERS 0X40-0X5F:

BIT ENABLE BYTE...................................................................... 330

TABLE 8 - RECEIVER CONTROLLER INDIRECT REGISTER MAP ......... 334

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS vii

TABLE 9 - RECEIVER CONTROLLER INDIRECT REGISTERS 0X40-0X5F:

BIT ENABLE BYTE...................................................................... 335

TABLE 10 - INSTRUCTION REGISTER ....................................................... 363

TABLE 11 - IDENTIFICATION REGISTER ................................................... 363

TABLE 12 - BOUNDARY SCAN REGISTER ................................................ 364

TABLE 13 - PMON COUNTER SATURATION LIMITS (E1 MODE).............. 372

TABLE 14 - PMON COUNTER SATURATION LIMITS (T1 MODE).............. 372

TABLE 15 - PERFORMANCE REPORT MESSAGE STRUCTURE AND

CONTENTS ................................................................................. 381

TABLE 16 - PERFORMANCE REPORT MESSAGE STRUCTURE NOTES 382

TABLE 17 - PERFORMANCE REPORT MESSAGE CONTENTS................ 383

TABLE 18 - 19.44 MHZ SBI STRUCTURE FOR CARRYING MULTIPLEXED

LINKS........................................................................................... 387

TABLE 19 - 77.76 MHZ SBI (SBI336) STRUCTURE FOR CARRYING

MULTIPLEXED LINKS................................................................. 387

TABLE 20 - T1 TRIBUTARY COLUMN NUMBERING .................................. 387

TABLE 21 - E1 TRIBUTARY COLUMN NUMBERING .................................. 388

TABLE 22 - SBI T1/E1 LINK RATE INFORMATION...................................... 390

TABLE 23 - SBI T1/E1 CLOCK RATE ENCODING....................................... 390

TABLE 24 - T1 FRAMING FORMAT ............................................................. 391

TABLE 25 - T1 CHANNEL ASSOCIATED SIGNALING BITS........................ 393

TABLE 26 - E1 FRAMING FORMAT ............................................................. 394

TABLE 27 - E1 CHANNEL ASSOCIATED SIGNALING BITS ....................... 396

TABLE 28 - DATA AND CAS T1 H-MVIP FORMAT ....................................... 397

TABLE 29 - DATA AND CAS E1 H-MVIP FORMAT....................................... 398

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS viii

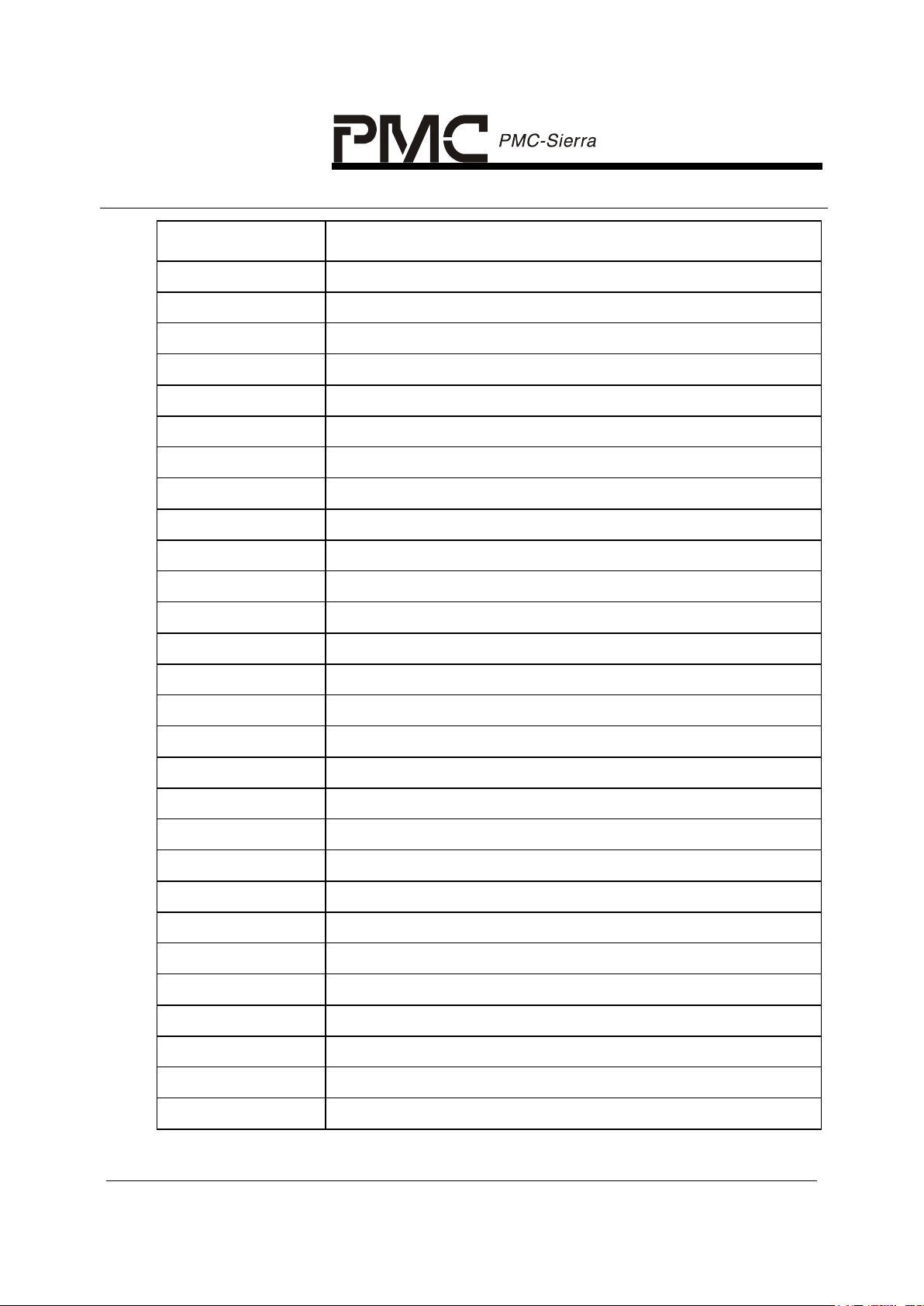

TABLE 30 - CCS H-MVIP FORMAT .............................................................. 399

TABLE 31 - ABSOLUTE MAXIMUM RATINGS ............................................. 412

TABLE 32 - D.C. CHARACTERISTICS......................................................... 413

TABLE 33 - MICROPROCESSOR INTERFACE READ ACCESS................. 416

TABLE 34 - MICROPROCESSOR INTERFACE WRITE ACCESS............... 418

TABLE 35 - RSTB TIMING............................................................................ 420

TABLE 36 - LINE SIDE SBI BUS INPUT TIMING (FIGURE 34) ................... 420

TABLE 37 - LINE SIDE SBI BUS OUTPUT TIMING (FIGURE 32 AND FIGURE

33)................................................................................................ 421

TABLE 38 - SYSTEM SIDE SBI ADD BUS TIMING – 19.44 MHZ (FIGURE 34)

..................................................................................................... 423

TABLE 39 - SYSTEM SIDE SBI ADD BUS TIMING – 77.76 MHZ (FIGURE 34)

..................................................................................................... 423

TABLE 40 - SYSTEM SIDE SBI DROP BUS TIMING – 19.44 MHZ (FIGURE 35

AND FIGURE 36)......................................................................... 424

TABLE 41 - SYSTEM SIDE SBI DROP BUS TIMING – 77.76 MHZ (FIGURE 35

AND FIGURE 36)......................................................................... 425

TABLE 42 - H-MVIP EGRESS TIMING (FIGURE 37) .................................. 427

TABLE 43 - H-MVIP INGRESS TIMING (FIGURE 38).................................. 428

TABLE 44 - XCLK INPUT (FIGURE 39)........................................................ 430

TABLE 45 - TRANSMIT LINE INTERFACE TIMING (FIGURE 40) ............... 431

TABLE 46 - JTAG PORT INTERFACE .......................................................... 432

TABLE 47 - ORDERING INFORMATION...................................................... 434

TABLE 48 - THERMAL INFORMATION – THETA JA VS. AIRFLOW ............ 434

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 1

1 FEATURES

• High Density 32 channel T1/E1/J1 framer.

• Software selectable between T1/J1 or E1 operation on a per device basis.

• Supports 8 Mbit/s H-MVIP on the system interface for all T1 or E1 links, a

separate 8 Mbit/s H-MVIP system interface for all T1 or E1 CAS channels and

a separate 8 Mbit/s H-MVIP system interface for all T1 or E1 CCS and

V5.1/V5.2 channels.

• Supports a byte serial Scaleable Bandwidth Interconnect (SBI) bus interface

for high density system side device interconnection of up to 32 T1 streams, 32

E1 streams.

• Provides jitter attenuation in the T1 or E1 receive and transmit directions.

• Provides three independent de-jittered T1 or E1 recovered clocks for system

timing and redundancy.

• Provides per link diagnostic and line loopbacks.

• Also provides PRBS generators and detectors on each tributary for error

testing at DS1, E1 and NxDS0 rates as recommended in ITU-T O.151 and

O.152.

• Provides a generic 8-bit microprocessor bus interface for configuration,

control and status monitoring. Provides a standard 5 signal P1149.1 JTAG

test port for boundary scan board test purposes.

• Low power 1.8V/3.3V CMOS technology. All pins are 5V tolerant.

• 324-pin fine pitch PBGA package (23mm x 23mm). Supports industrial

temperature range (-40 oC to 85 oC) operation.

• Line side interface is SBI bus.

• System side interface is either H-MVIP or SBI bus.

Each one of 32 T1 receiver sections:

• Frames to DS-1 signals in SF, SLC96 and ESF formats.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 2

• Frames to TTC JT-G.704 multiframe formatted J1 signals. Supports the

alternate CRC-6 calculation for Japanese applications.

• Provides Red, Yellow, and AIS alarm integration.

• Supports RAI-CI and AIS-CI alarm detection and generation.

• Provides ESF bit-oriented code detection and an HDLC/LAPD interface for

terminating the ESF facility data link.

• Provides Inband Loopback Code generation and detection.

• Indicates signaling state change, and two superframes of signaling debounce

on a per-DS0 basis.

• Provides an HDLC interface with 128 bytes of buffering for terminating the

facility data link.

• Provides performance monitoring counters sufficiently large as to allow

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the performance monitoring counters and interrupts the

microprocessor once per second, timed to the receive line.

• Provides an optional elastic store, which may be used to time the ingress

streams to a common clock and frame alignment in support of a H-MVIP

interface.

• Provides DS-1 robbed bit signaling extraction and insertion, with optional data

inversion, programmable idle code substitution, digital milliwatt code

substitution, bit fixing, and two superframes of signaling debounce on a perchannel basis.

• A pseudo-random sequence user selectable from 27 –1, 211 –1, 215 –1 or 220 –

1, may be detected in the T1 stream in either the ingress or egress directions.

The detector counts pattern errors using a 16-bit non-saturating PRBS error

counter. The pseudo-random sequence can be the entire T1 or any

combination of DS0s within a framed T1.

• Frames in the presence of and detects the “Japanese Yellow” alarm.

• Supports the alternate CRC-6 calculation for Japanese applications.

• Provides external access for up to three de-jittered recovered T1 clocks.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 3

Each one of 32 E1 receiver sections:

• Frames to ITU-T G.704 basic and CRC-4 multiframe formatted E1 signals.

The framing procedures are consistent ITU-T G.706 specifications.

• Provides an HDLC interface with 128 bytes of buffering for terminating the

national use bit data link.

• Extracts 4-bit codewords from the E1 national use bits as specified in

ETS 300 233.

• V5.2 link indication signal detection.

• Provides performance monitoring counters sufficiently large as to allow

performance monitor counter polling at a minimum rate of once per second.

Optionally, updates the performance monitoring counters and interrupts the

microprocessor once per second, timed to the receive line.

• Provides a two-frame elastic store buffer for backplane rate adaptation that

performs controlled slips and indicates slip occurrence and direction.

• Frames to the E1 signaling multiframe alignment when enabled and extracts

channel associated signaling. Alternatively, a common channel signaling data

link may be extracted from timeslot 16.

• Can be programmed to generate an interrupt on change of signaling state.

• Provides trunk conditioning which forces programmable trouble code

substitution and signaling conditioning on all channels or on selected

channels.

• A pseudo-random sequence user selectable from 27 –1, 211 –1, 215 –1 or 220 –

1, may be detected in the E1 stream in either the ingress or egress directions.

The detector counts pattern errors using a 16-bit non-saturating PRBS error

counter. The pseudo-random sequence can be the entire E1 or any

combination of timeslots within the framed E1.

• Provides external access for up to three de-jittered recovered E1 clocks.

Each one of 32 T1 transmitter sections:

• May be timed to its associated receive clock (loop timing) or may derive its

timing from a common egress clock or a common transmit clock; the transmit

line clock may be synthesized from an N*8 kHz reference.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 4

• Provides minimum ones density through Bell (bit 7), GTE or “jammed bit 8”

zero code suppression on a per-DS0 basis. Provides a 128 byte buffer to

allow insertion of the facility data link using the host interface.

• Supports transmission of the alarm indication signal (AIS) or the Yellow alarm

signal in SF, SLC96 and ESF formats.

• Provides transparency for the F-bit to support SLC96 data link insertion.

• Autonomously transmits an ESF Performance Report Message each second.

• Provides a digital phase locked loop for generation of a low jitter transmit

clock.

• Provides a FIFO buffer for jitter attenuation and rate conversion in the

transmitter.

• Supports the alternate ESF CRC-6 calculation for Japanese applications.

• A pseudo-random sequence user selectable from 27 –1, 211 –1, 215 –1 or 220 –

1, may be inserted into the T1 stream in either the ingress or egress

directions. The pseudo-random sequence can be inserted into the entire T1 or

any combination of DS0s within the framed T1.

Each one of 32 E1 transmitter sections:

• Provides a FIFO buffer for jitter attenuation and rate conversion in the

transmit path.

• Transmits G.704 basic and CRC-4 multiframe formatted E1.

• Supports unframed mode and framing bit, CRC, or data link by-pass.

• Provides signaling insertion, programmable idle code substitution, digital

milliwatt code substitution, and data inversion on a per channel basis.

• Provides trunk conditioning which forces programmable trouble code

substitution and signaling conditioning on all channels or on selected

channels.

• Provides a digital phase locked loop for generation of a low jitter transmit

clock.

• A pseudo-random sequence user selectable from 27 –1, 211 –1, 215 –1 or 220 –

1, may be inserted into the E1 stream in either the ingress or egress

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 5

directions. The pseudo-random sequence can be inserted into the entire E1

or any combination of timeslots within the framed E1.

• Optionally inserts a datalink in the E1 national use bits.

• Supports 4-bit codeword insertion in the E1 national use bits as specified in

ETS 300 233

• Supports transmission of the alarm indication signal (AIS) and the remote

alarm indication (RAI) signal.

Six full featured T1/E1 Pattern Generators and Detectors:

• Each generator and detector pair may be associated with any one of the 32

T1s or E1s.

• Any sub-set of DS0s within a tributary may be selected.

• Provides programmable pseudo-random test sequence generation (up to 232-

1 bit length sequences conforming to ITU-T O.151 standards) or any

repeating pattern up to 32 bits. Diagnostic abilities include single bit error

insertion or error insertion at bit error rates ranging from 10-1 to 10-7.

Synchronous System Interfaces:

• Provides eight 8 Mbit/s H-MVIP data interfaces for synchronous access to all

the DS0s of all 32 T1 links or all timeslots of all 32 E1s.

• Provides 8 8 Mbit/s H-MVIP interfaces for synchronous access to all channel

associated signaling (CAS) bits for all T1 DS0s or E1 timeslots. The CAS bits

occupy one nibble of every byte on the H-MVIP interfaces and are repeated

over the entire T1 or E1 multi-frame.

• Provides three 8 Mbit/s H-MVIP interfaces for common channel signaling

(CCS) channels as well as V5.1 and V5.2 channels. In T1 mode DS0 24 is

available through this interface. In E1 mode timeslots 15, 16 and 31 are

available through this interface. Optionally, timeslot 0 may be presented

instead of timeslot 15.

• All links accessed via the H-MVIP interface will be synchronously timed to the

common H-MVIP clock and frame alignment signals, CMV8MCLK, CMVFP,

CMVFPC.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 6

• H-MVIP access for Channel Associated Signaling is available with the

Scaleable Bandwidth Interconnect bus as an optional replacement for CAS

access over the SBI bus as well as with the H-MVIP data interface. Common

Channel Signaling H-MVIP access is available with the SBI bus, serial PCM

and H-MVIP data interfaces.

• Alarm status, T1 F-bit and inband signaling control is available using

otherwise unused bit positions.

• Compatible with H-MVIP PCM backplanes supporting 8.192 Mbit/s.

Scaleable Bandwidth Interconnect (SBI) Bus:

• Provides a high density byte serial interconnect for all TE-32 links. Utilizes an

Add/Drop configuration to asynchronously multiplex up to 32 T1s or 32 E1s

with multiple payload or link layer processors.

• External devices can access framed T1s and framed E1s over this interface.

• Framed T1 access can be selected on a per T1 basis. Framed E1 access

can be selected on a per E1 basis.

• At the system interface, synchronous access for T1 DS0 channels or E1

timeslots is supported in a locked format mode. Selectable on a per tributary

basis.

• At the system interface, channel associated signaling bits for channelized T1

and E1 are explicitly identified across the bus.

• Transmit timing is mastered either by the TE-32 or a layer 2 device

connecting to the system interface SBI bus. Timing mastership is selectable

on a per tributary basis, where a tributary is either an individual T1, E1.

• The line side SBI bus provides a time switch capability in support of

redundancy.

• The system side SBI operates at either 19.44 MHz or 77.76 MHz. The line

side SBI operates at 19.44 MHz.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 7

2 APPLICATIONS

• Multiservice Switches

• Voice Gateways

• Wireless Base Station Controllers

• Edge Routers

• Multiservice Add-Drop Multiplexers

• Digital Access Cross-Connect Systems

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 8

3 REFERENCES

• American National Standard for Telecommunications - Digital Hierarchy - Formats

Specification, ANSI T1.107-1995

• American National Standard for Telecommunications - Digital Hierarchy - Layer 1

In-Service Digital Transmission Performance Monitoring, ANSI T1.231-1997

• American National Standard for Telecommunications - Carrier to Customer

Installation - DS-1 Metallic Interface Specification, ANSI T1.403-1995

• American National Standard for Telecommunications - Integrated Services Digital

Network (ISDN) Primary Rate- Customer Installation Metallic Interfaces Layer 1

Specification, ANSI T1.408-1990

• Bell Communications Research, TR–TSY-000009 - Asynchronous Digital

Multiplexes Requirements and Objectives, Issue 1, May 1986

• Bell Communications Research - DS-1 Rate Digital Service Monitoring Unit

Functional Specification, TA-TSY-000147, Issue 1, October, 1987

• Bell Communications Research - Alarm Indication Signal Requirements and

Objectives, TR-TSY-000191 Issue 1, May 1986

• Bell Communications Research - Wideband and Broadband Digital CrossConnect Systems Generic Criteria, TR-NWT-000233, Issue 3, November 1993

• Bell Communications Research – Digital Interface Between The SLC96 Digital

Loop Carrier System And A Local Digital Switch, TR-TSY-000008, Issue 2,

August 1987

• Bell Communications Research - Integrated Digital Loop Carrier Generic

Requirements, Objectives, and Interface, TR-NWT-000303, Issue 2, December,

1992

• Bell Communications Research - Transport Systems Generic Requirements

(TSGR): Common Requirement, TR-TSY-000499, Issue 5, December, 1993

• Bell Communications Research - OTGR: Network Maintenance Transport

Surveillance - Generic Digital Transmission Surveillance, TR-TSY-000820,

Section 5.1, Issue 1, June 1990

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 9

• AT&T - Requirements For Interfacing Digital Terminal Equipment To Services

Employing The Extended Superframe Format, TR 54016, September 1989.

• AT&T - Accunet T1.5 - Service Description and Interface Specification, TR 62411,

December, 1990

• ITU Study Group XVIII – Report R 105, Geneva, 9-19 June 1992

• ETSI - ETS 300 011 - ISDN Primary Rate User-Network Interface Specification

and Test Principles, 1992.

• ETSI - ETS 300 233 - Access Digital Section for ISDN Primary Rates, May 1994

• ETSI - ETS 300 324-1 - Signaling Protocols and Switching (SPS); V interfaces at

the Digital Local Exchange (LE) V5.1 Interface for the Support of Access Network

(AN) Part 1: V5.1 Interface Specification, February, 1994.

• ETSI - ETS 300 347-1 - Signaling Protocols and Switching (SPS); V Interfaces at

the Digital Local Exchange (LE) V5.2 Interface for the Support of Access Network

(AN) Part 1: V5.2 Interface Specification, September 1994.

• ITU-T - Recommendation G.704 - Synchronous Frame Structures Used at

Primary Hierarchical Levels, July 1995.

• ITU-T - Recommendation G.706 - Frame Alignment and CRC Procedures

Relating to G.704 Frame Structures, 1991.

• ITU-T - Recommendation G.732 – Characteristics of Primary PCM Multiplex

Equipment Operating at 2048 kbit/s, 1993.

• ITU-T Recommendation G.775, - Loss of Signal (LOS) and Alarm Indication

Signal (AIS) Defect Detection and Clearance Criteria, 11/94

• ITU-T Recommendation G.823, - The Control of Jitter and Wander within Digital

Networks which are Based on the 2048 kbit/s Hierarchy, 03/94

• ITU-T Recommendation G.964, - V-Interfaces at the Digital Local Ex–hange (LE)

- V5.1 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN),

June 1994.

• ITU-T Recommendation G.965, - V-Interfaces at the Digital Local Ex–hange (LE)

- V5.2 Interface (Based on 2048 kbit/s) for the Support of Access Network (AN),

March –995.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 10

• ITU-T - Recommendation I.431 - Primary Rate User-Network Interface – Layer 1

Specification, 1993.

• ITU-T Recommendation O.151 – Error Performance Measuring Equipment

Operating at the Primary Rate and Above, October 1992

• ITU-T Recommendation O.152 – Error Performance Measuring Equipment for Bit

Rates of 64 kbit/s and N x 64 kbit/s, October 1992

• ITU-T Recommendation O.153 - Basic Parameters for the Measurement of Error

Performance at Bit Rates below the Primary Rate, October 1992.

• ITU-T Recommendation Q.921 - ISDN User-Network Interface Data Link Layer

Specification, March 1993

• International Organization for Standardization, ISO 3309:1984 - High-Level Data

Link Control procedures - Frame Structure

• TTC Standard JT-G704 - Frame Structures on Primary and Secondary

Hierarchical Digital Interfaces, 1995.

• TTC Standard JT-G706 - Frame Synchronization and CRC Procedure

• TTC Standard JT-I431 - ISDN Primary Rate User-Network Interface Layer 1 -

Specification, 1995.

• Nippon Telegraph and Telephone Corporation - Technical Reference for HighSpeed Digital Leased Circuit Services, Third Edition, 1990.

• GO-MVIP, Multi-Vendor Integration Protocol, MVIP-90, Release 1.1, 1994

• GO-MVIP, H-MVIP Standard, Release1.1a, 1997

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 11

4 APPLICATION EXAMPLES

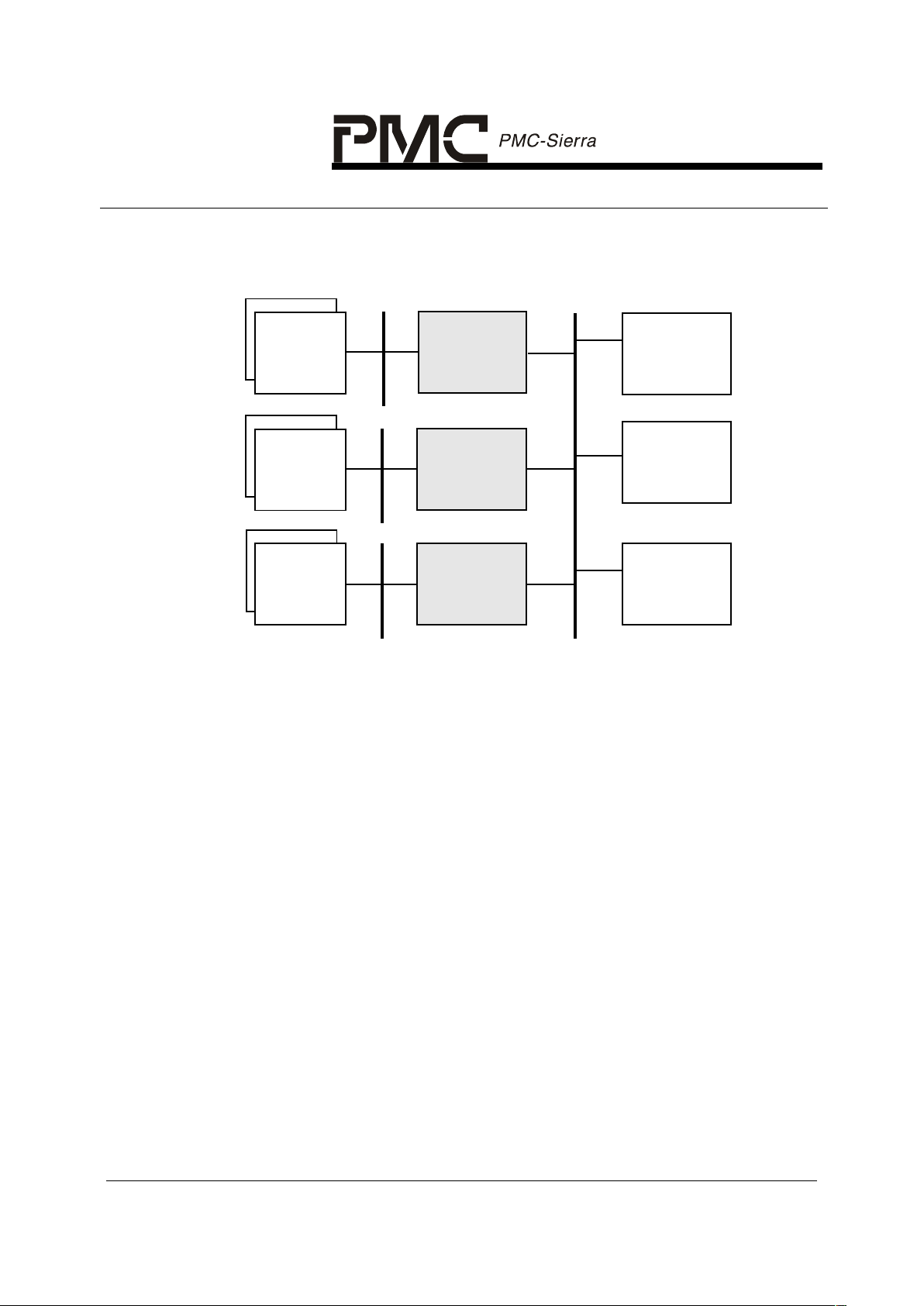

Figure 1 - Edge Router Line Card

PM4318

OCTLIU

PM4318

OCTLIU

PM4318

OCTLIU

PM4318

OCTLIU

PM4332

TE32

SBI

SBI

PM7384

FREEDM-

84P672

PCI

Figure 1illustrates a 32-Channel T1/E1/J1 Edge Router Line Card using the

FREEDM-84P672 (PM7384) and the OCTLIU (PM4318).

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 12

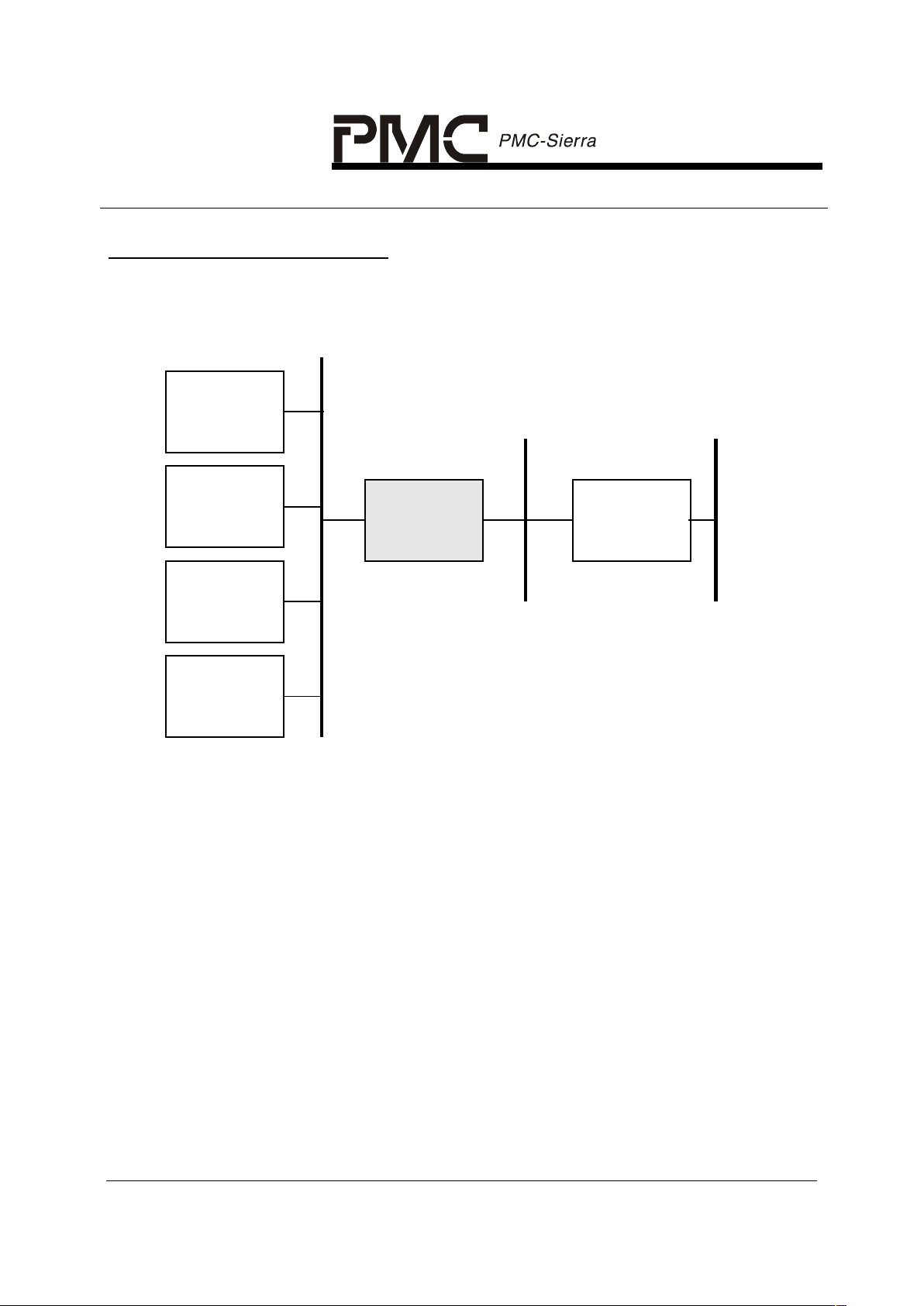

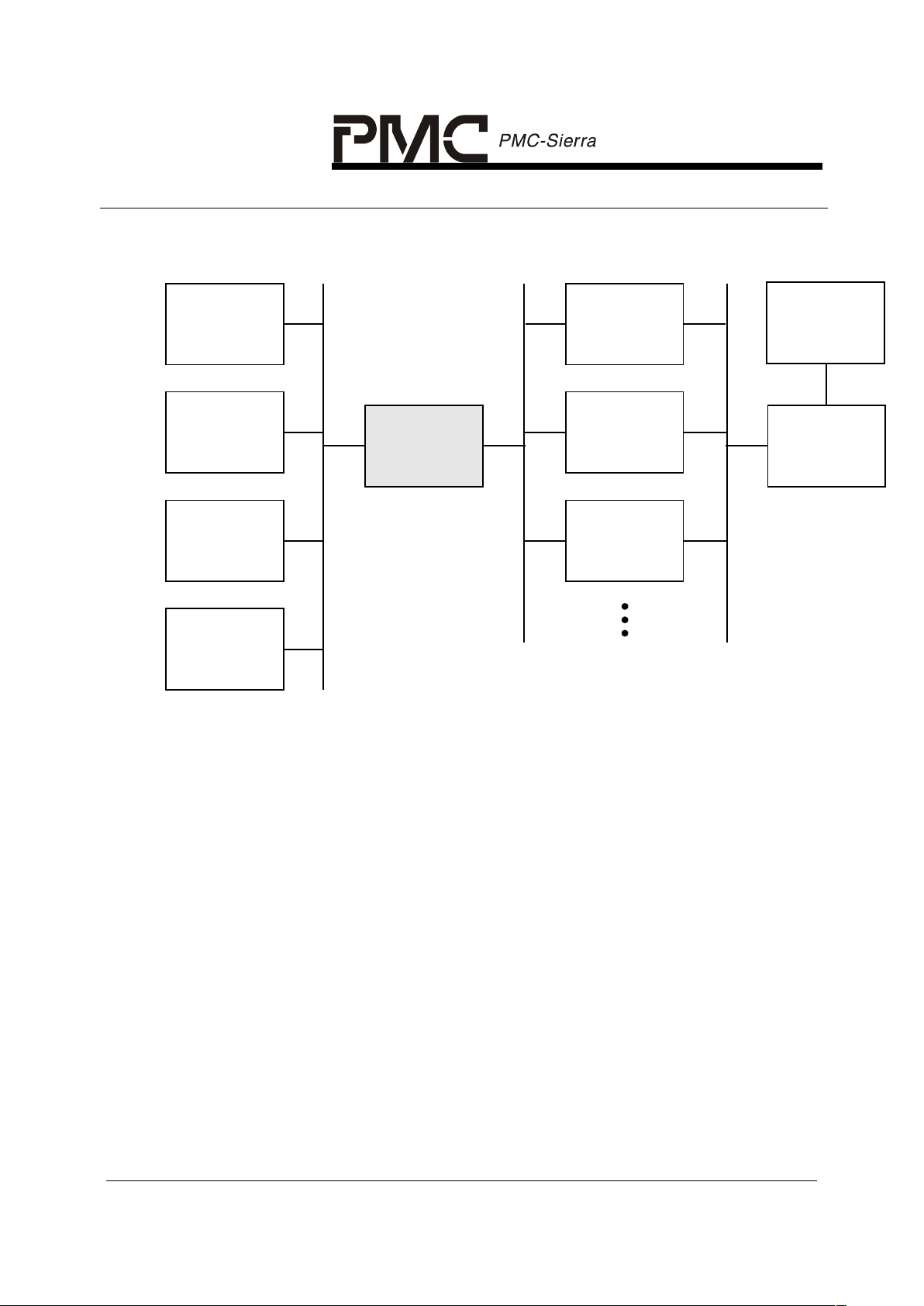

Figure 2 - Multiservice Switch

PM4332

TE32

19.44 MHz

SBI

19.44 MHz

SBI

PM4332

TE32

PM4332

TE32

PM7389

FREEDM-

84A1024

PM7341

S/UNI-

IMA-84

PM73122

AAL1gator-32

PM4318

OCTLIU

PM4318

OCTLIU

4 x OCTLIU

PM4318

OCTLIU

PM4318

OCTLIU

4 x OCTLIU

PM4318

OCTLIU

PM4318

OCTLIU

4 x OCTLIU

Figure 2 illustrates how frame relay (FREEDM-84A1024), circuit emulation

(AAL1gator-32) and ATM inverse multiplexing (S/UNI-IMA-84) may all be

supported on a single platform using a common SBI bus as the enabling

technology. A high density T1/E1/J1 line interface is provided through an SBI bus

connection to the OCTLIU (PM4318).

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 13

Figure 3 - Voice Gateway Application

PM4318

OCTLIU

PM4318

OCTLIU

PM4318

OCTLIU

PM4318

OCTLIU

PM4332

TE32

SBI

PCM Highway

H-MVIP

VoATM

DSP

VoATM

DSP

VoATM

DSP

PM7326

S/UNI-APEX

PM7324

S/UNI-ATLAS

Utopia L2

Figure 3 illustrates a typical voice gateway application using VoATM processing

and ATM traffic management (PM7326, PM7324).

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 14

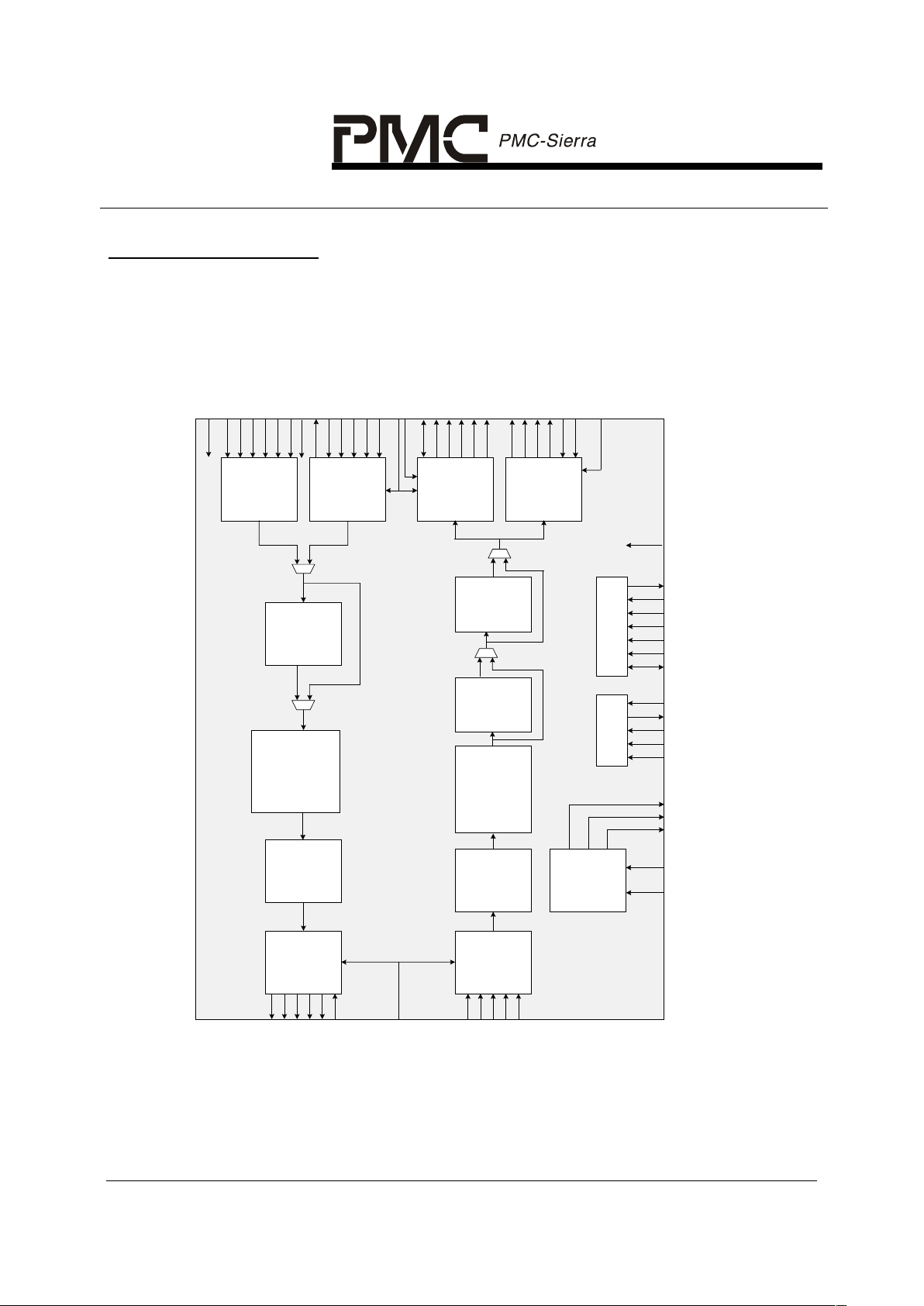

5 BLOCK DIAGRAM

Figure 4 - TE-32 Block Diagram

LADATA[7:0]

LADP

LAV5

LAPL

JTAG uP Interface

System

Side SBI

Extract

INTB

RDB

WRB

CSB

ALE

A[12:0]

D[7:0]

TRSTB

TDO

TDI

TMS

TCK

T1/E1

Transmitter;

HDLC

Transmitter,

PRBS

Generator

Egress

H-MVIP

System

Side SBI

Insert

Ingress

H-MVIP

LAC1FPO

LAC1FPI

Line Side

SBI Insert

Line Side

SBI Extract

LDDATA[7:0]

LDDP

LDV5

LDPL

LDC1FP

RJAT

Digital Jitter

Attenuator

T1/E1 Framer;

HDLC Receiver,

PMON, PRBS

Checker

ELST

Elastic

Store

T1/E1

SIGX

TJAT

Digital Jitter

Attenuator

ELST

Elastic

Store

LREFCLK

Recovered

Clock

RSTB

SREFCLK

SAC1FP

SDC1FP

CMVFPC

MVED[1:8]

SAJUST_REQ

SADATA[7:0]

SADP

SAPL

SAV5

SDDATA[7:0]

SDDP

SDPL

SDV5

SBIACT

SBIDET[1:0]

CASED[1:8]

CCSED[1:3]

CMVFPB

CMV8MCLK

CMVFPC

CMVFPB

CMV8MCLK

MVID[1:8]

CASID[1:8]

CCSID[1:3]

TS0ID

CTCLK

S77

RECVCLK1

RECVCLK3

RECVCLK2

XCLK_T1

XCLK_E1

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 15

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 16

6 DESCRIPTION

The PM4332 High Density 32 Channel T1/E1 Framer is a feature-rich device for

use in any application requiring high density framing of T1/J1 and E1 links.

Each of the T1 and E1 framers and transmitters is independently software

configurable, allowing timing master and feature selection without changes to

external wiring. However, mixed framing modes are not supported. The framers

must be all configured for either T1 or E1 framing.

T1 Operation

In the ingress direction, each of the 32 T1 links is extracted from the Scaleable

Bandwidth Interconnect (SBI) bus. A Scaleable Bandwidth Interconnect (SBI)

high density byte serial line interface provides higher levels of integration and

dense interconnect. Each T1 framer detects the presence of Yellow and AIS

patterns and also integrates Yellow, Red, and AIS alarms.

T1 performance monitoring with accumulation of CRC-6 errors, framing bit errors,

out-of-frame events, and changes of frame alignment is provided. The TE-32

also detects the presence of ESF bit oriented codes, and detects and terminates

HDLC messages on the ESF data link. The HDLC messages are terminated in a

128 byte FIFO. An elastic store that optionally supports slip buffering and

adaptation to backplane timing is provided, as is a signaling extractor that

supports signaling debounce, signaling freezing and interrupt on signaling state

change on a per-DS0 basis. The TE-32 also supports inband loopback code

generation and detection, idle code substitution, digital milliwatt code insertion,

data link extraction, trunk conditioning, data sign and magnitude inversion, and

pattern generation and detection on a per-DS0 basis.

In the egress direction, framing is generated for 32 T1s into an SBI add bus. A

Scaleable Bandwidth Interconnect (SBI) high density byte serial line interface

provides higher levels of integration and dense interconnect. Each T1 transmitter

frames to SF or ESF DS1 formats, or framing can be optionally disabled. The

TE-32 supports signaling insertion, idle code substitution, data insertion, line

loopback, data inversion and zero-code suppression on a per-DS0 basis. PRBS

generation and detection is supported on a framed and unframed T1 basis.

E1 Operation

In the ingress direction, each of the 32 E1 links is extracted from Scaleable

Bandwidth Interconnect (SBI). Each E1 framer detects and indicates the

presence of remote alarm and AIS patterns and also integrates Red and AIS

alarms.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 17

The E1 framers support detection of various alarm conditions such as loss of

frame, loss of signaling multiframe and loss of CRC multiframe. The E1 framers

also support reception of remote alarm signal, remote multiframe alarm signal,

alarm indication signal, and time slot 16 alarm indication signal.

E1 performance monitoring with accumulation of CRC-4 errors, far end block

errors and framing bit errors is provided. The TE-32 provides a receive HDLC

controller for the detection and termination of messages on the national use bits.

Detection of the 4-bit Sa-bit codewords defined in ITU-T G.704 and ETSI 300-233

is supported. V5.2 link ID signal detection is also supported. An interrupt may be

generated on any change of state of the Sa codewords. An elastic store for slip

buffering and rate adaptation to backplane timing is provided, as is a signaling

extractor that supports signaling debounce, signaling freezing, idle code

substitution, digital milliwatt tone substitution, data inversion, and signaling bit

fixing on a per-channel basis. Receive side data and signaling trunk conditioning

is also provided.

In the egress direction, framing is generated for 32 E1s into SBI add bus. Each

E1 transmitter generates framing for a basic G.704 E1 signal. The signaling

multiframe alignment structure and the CRC multiframe structure may be

optionally inserted. Framing can be optionally disabled. Transmission of the 4-bit

Sa codewords defined in ITU-T G.704 and ETSI 300-233 is supported. PRBS

generation or detection is supported on a framed and unframed E1 basis.

General Operation

The TE-32 can generate a low jitter transmit clock from a variety of clock

references, and also provides jitter attenuation in the receive path. Three jitter

attenuated recovered T1/E1 clocks can be routed outside the TE-32 for network

timing applications.

In synchronous backplane systems, 8 Mbit/s H-MVIP interfaces are provided for

access to 768 DS0 channels, channel associated signaling (CAS) for all 768 DS0

channels and common channel signaling (CCS) for all 32 T1s or 32 E1s (or

combination thereof). The CCS signaling H-MVIP interface is independent of the

DS0 channel and CAS H-MVIP access. The use of any of the H-MVIP interfaces

requires that common clocks and frame pulse be used along with T1 slip buffers.

A Scaleable Bandwidth Interconnect (SBI) high density byte serial system

interface provides higher levels of integration and dense interconnect. The SBI

bus interconnects up to 32 T1s or E1s both synchronously or asynchronously.

The SBI allows transmit timing to be mastered by either the TE-32 or link layer

device connected to the system SBI bus. Error event accumulation is also

provided by the TE-32. Framing bit errors, and far end block errors are

accumulated. Error accumulation continues even while the off-line framers are

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 18

indicating OOF. The counters are intended to be polled once per second, and

are sized so as not to saturate at a 10

-3

bit error rate. Transfer of count values to

holding registers is initiated through the microprocessor interface.

The TE-32 is configured, controlled and monitored via a generic 8-bit

microprocessor bus through which all internal registers are accessed. All

sources of interrupts can be masked and acknowledged through the

microprocessor interface.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 19

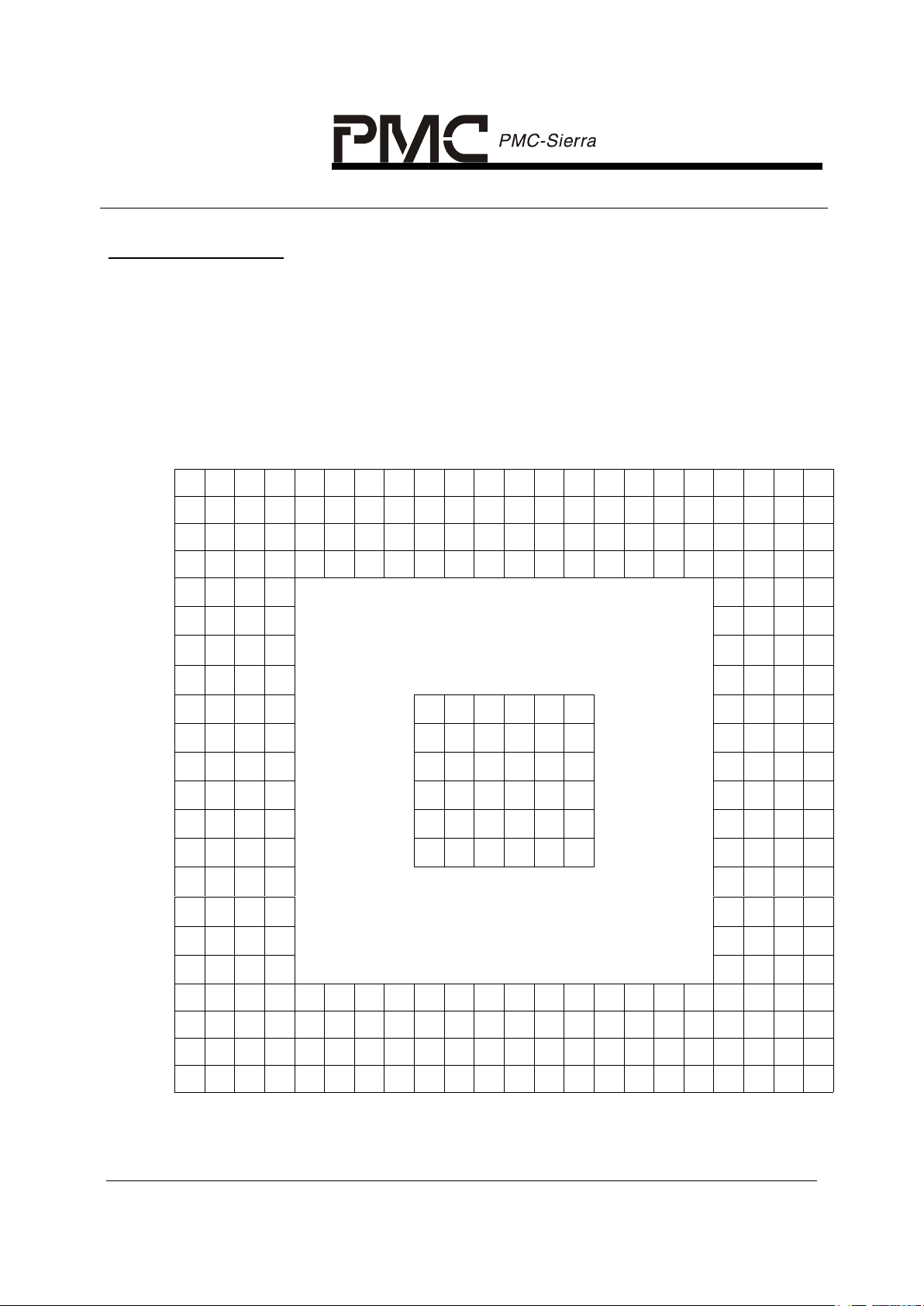

7 PIN DIAGRAM

The TE-32 is packaged in a 324-pin PBGA package having a body size of 23mm

by 23mm and a ball pitch of 1.0 mm. The center 36 balls are not used as signal

I/Os and are thermal balls. Pin names and locations are defined in the Pin

Description Table in section 8. Mechanical information for this package is in

section 19.

Figure 5 - Pin Diagram

22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

A

B

C

D

E

F

G

H

324 PBGA

J

VSS VSS VSS VSS VSS VSS

K

VSS VSS VSS VSS VSS VSS

L

VSS VSS VSS VSS VSS VSS

M

VSS VSS VSS VSS VSS VSS

N

VSS VSS VSS VSS VSS VSS

P

VSS VSS VSS VSS VSS VSS

R

T

Bottom View

U

V

W

Y

AA

AB

22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 20

8 PIN DESCRIPTION

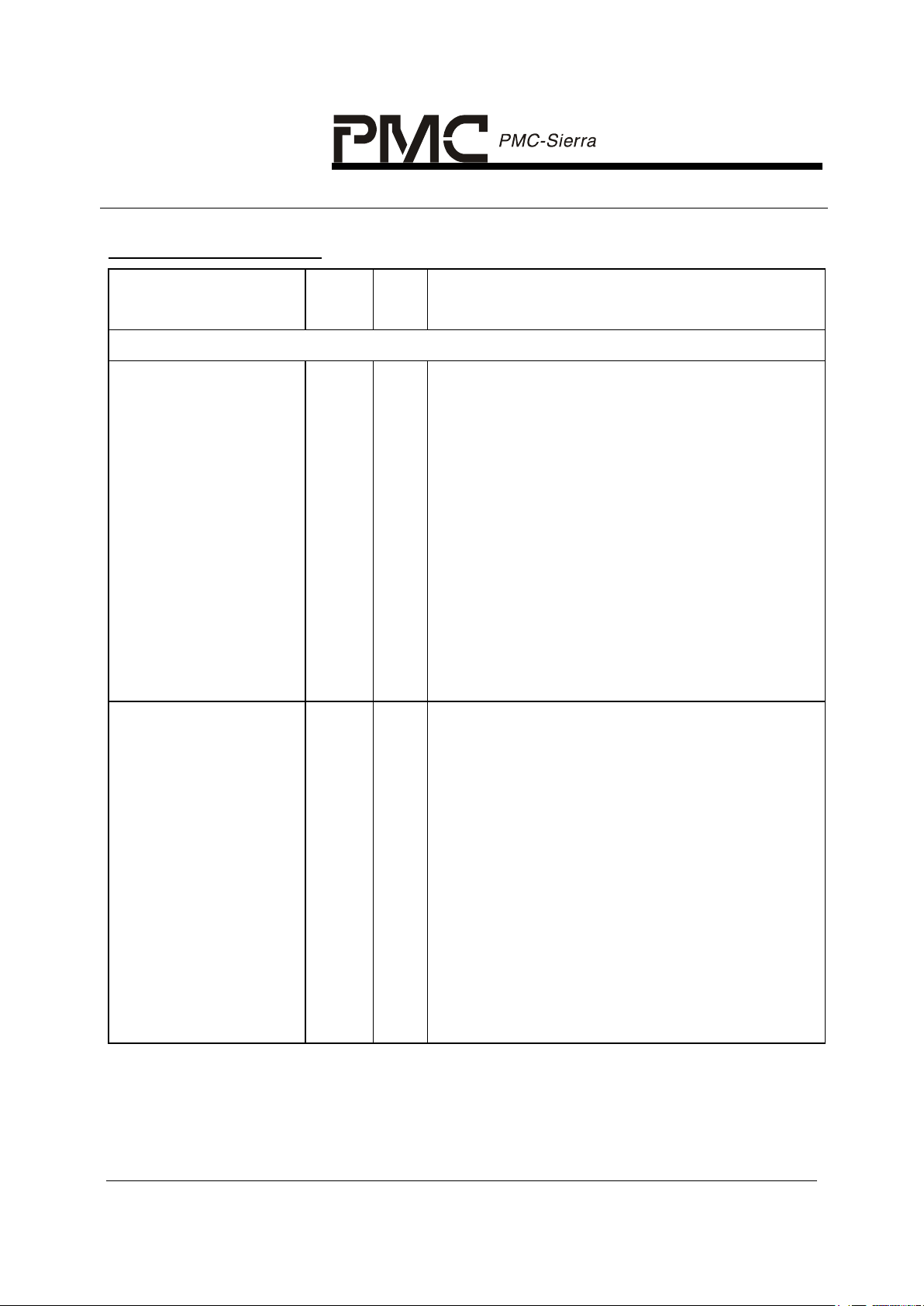

Pin Name Type Pin

No.

Function

H-MVIP System Side Interfaces

CMV8MCLK Input T22 Common 8M H-MVIP Clock (CMV8MCLK). The

common 8.192 Mbit/s H-MVIP data provides the

data clock for receive and transmit links

configured for operation in 8.192 Mbit/s H-MVIP

mode.

CMV8MCLK is used to sample the MVED[1:8],

CASED[1:8] and CCSED[1:3] inputs and update

MVID[1:8], CASID[1:8], CCSID[1:3] and TS0ID

outputs. CMV8MCLK is nominally a 50% duty

cycle clock with a frequency of 16.384 MHz.

The H-MVIP interfaces are enabled via the

SYSOPT[1:0] bits in the Global Configuration

register. If the TE-32 is not configured for HMVIP operation, this clock may be tied high or

low.

CMVFPC Input R20 Common H-MVIP Frame Pulse Clock

(CMVFPC). The common 8.192 Mbit/s H-MVIP

frame pulse clock provides the frame pulse clock

for receive and transmit links configured for

operation in 8.192 Mbit/s H-MVIP mode.

CMVFPC is used to sample CMVFPB. CMVFPC

is nominally a 50% duty cycle clock with a

frequency of 4.096 MHz. The falling edge of

CMVFPC must be aligned with the falling edge of

CMV8MCLK with no more than ±10ns skew.

The H-MVIP interfaces are enabled via the

SYSOPT[1:0] bits in the Global Configuration

register. If the TE-32 is not configured for HMVIP operation, this clock may be tied high or

low.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 21

Pin Name Type Pin

No.

Function

CMVFPB Input R22 Common H-MVIP Frame Pulse (CMVFPB). The

active low common frame pulse for 8.192 Mbit/s

H-MVIP signals references the beginning of each

frame for links operating in 8.192 Mbit/s H-MVIP

mode.

If the CMMFP bit of the Master H-MVIP Interface

Configuration register is a logic 1, the CMVFPB

is becomes a multiframe pulse. Mulitframe

alignment is only relevant when the T1 F-bit or

the E1 TS0 is being carried transparently in the

egress direction and alignment to CAS signaling

is required. To support any combination of SF,

SLC96, ESF and E1, the CMVFPB must pulse

low at a multiple of 48 frames at the beginning of

the frame.

The H-MVIP interfaces are enabled via the

SYSOPT[1:0] bits in the Global Configuration

register. If the TE-32 is not configured for HMVIP operation, this frame pulse may be tied

high or low.

The CMVFPB frame pulse occurs at multiples of

125us and is sampled on the falling edge of

CMVFPC.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 22

Pin Name Type Pin

No.

Function

MVID[1]/SDC1FP

MVID[2]/SBIACT

MVID[3]/SAJUST_REQ

MVID[4]/SDDATA[0]

MVID[5]/SDDATA[4]

MVID[6]/SDDATA[5]

MVID[7]/SDDATA[6]

MVID[8]/SDDATA[7]

Output B3

A3

A2

C5

A5

B6

C7

D6

H-MVIP Ingress Data (MVID[1:8]). MVID[x]

carries the recovered T1 or E1 channels which

have passed through the elastic store. Each

MVID[x] signal carries the channels of four

complete T1s or E1s.

MVID[x] is aligned to the common H-MVIP

16.384 Mbit/s clock, CMV8MCLK, frame pulse

clock, CMVFPC, and frame pulse, CMVFPB.

MVID[x] is updated on every second rising or

falling edge of the common H-MVIP 16.384Mb /s

clock, CMV8MCLK, as fixed by the common HMVIP frame pulse clock, CMVFPC. The

updating edge of CMV8MCLK is selected via the

CMVIDE bit in the Master and H-MVIP Interface

Configuration register.

Each of MVID[1:4] and MVID[5:8] carries 16

independent T1s or E1s.

MVID[1:8] share the same pins as SDC1FP,

SBIACT, SAJUST_REQ, SDDATA[0] and

SDDATA[4:7]. MVID[1:8] are selected when the

SYSOPT[1:0] are set to “01” (H-MVIP), in the

Global Configuration register.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 23

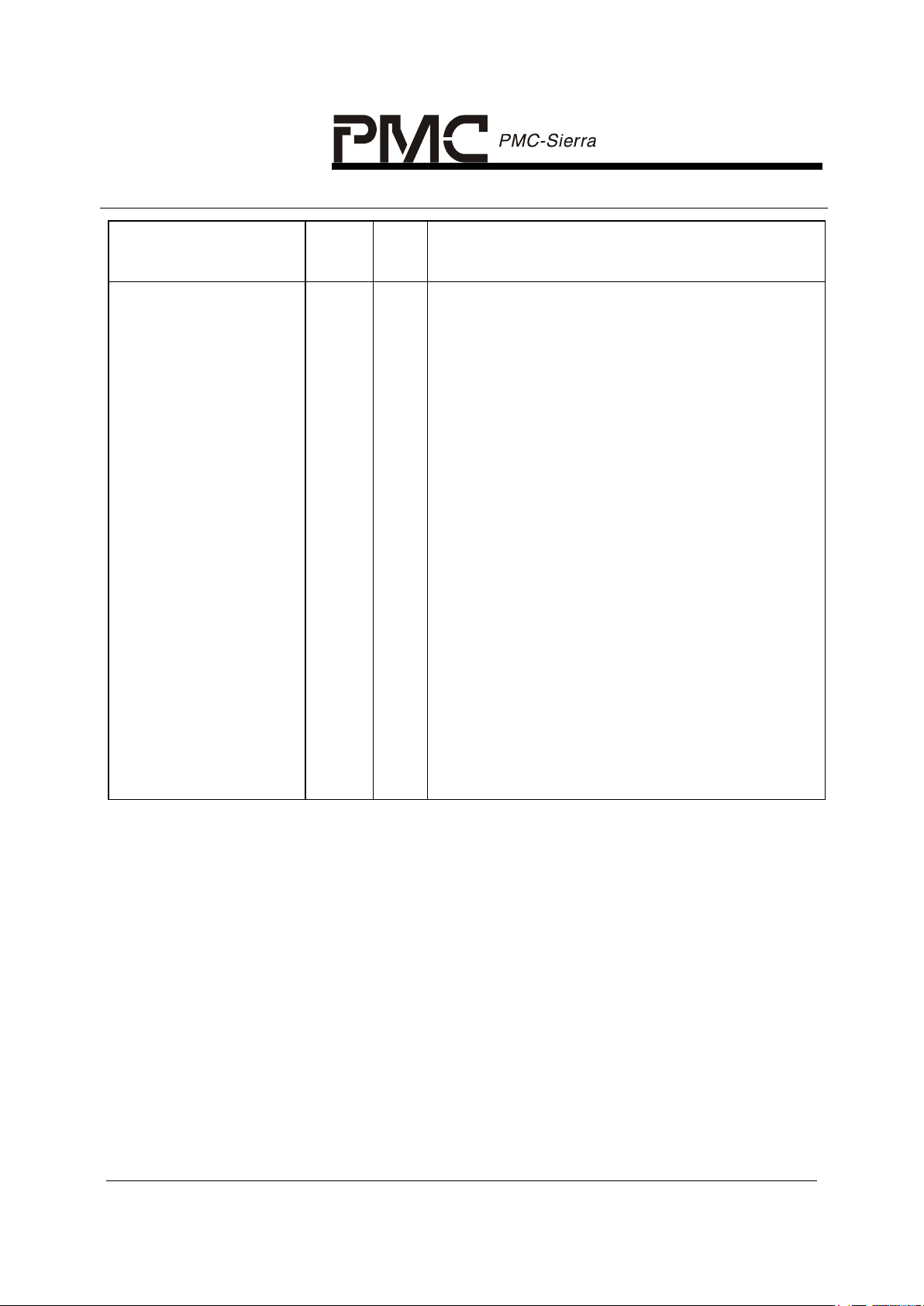

Pin Name Type Pin

No.

Function

CASID[1]

CASID[2]

CASID[3]

CASID[4]

CASID[5]

CASID[6]

CASID[7]

CASID[8]

Output B18

A19

A20

B19

D20

B22

C21

D21

Channel Associated Signaling Ingress Data

(CASID[1:8]). Each CASID[x] signal carries

CAS for four complete T1s or E1s. CASID[x]

carries the corresponding CAS values of the

channel carried in MVID[x]. It also carries the

framer and alarm statuses.

CASID[x] is aligned to the common H-MVIP

16.384 Mbit/s clock, CMV8MCLK, frame pulse

clock, CMVFPC, and frame pulse, CMVFPB.

CASID[x] is updated on every second rising or

falling edge of CMV8MCLK as fixed by the

common H-MVIP frame pulse clock, CMVFPC.

The updating edge of CMV8MCLK is selected via

the CMVIDE bit in the Master H-MVIP Interface

Configuration register.

Each of CASID[1:4] and CASID[5:8] carries 16

independent T1s or E1s.

CCSID[1]

CCSID[2]

CCSID[3]

Output C16

D18

B17

Common Channel Signaling Ingress Data

(CCSID[1:3]). In T1 mode, CCSID[1] carries the

32 common channel signaling channels

extracted from each of the 32 T1s. In E1 mode,

CCSID[1:3] carries up to 3 timeslots (15,16, 31)

from each of the 32 E1s. CCSID is formatted

according to the H-MVIP standard.

CCSID[x] is aligned to the common H-MVIP

16.384 Mbit/s clock, CMV8MCLK, frame pulse

clock, CMVFPC, and frame pulse, CMVFPB.

CCSID is updated on every second rising or

falling edge of CMV8MCLK as fixed by the

common H-MVIP frame pulse clock, CMVFPC.

The updating edge of CMV8MCLK is selected via

the CMVIDE bit in the Master H-MVIP Interface

Configuration register.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 24

Pin Name Type Pin

No.

Function

TS0ID Output D17 E1 Timeslot 0 Ingress Data (TS0ID). In E1

mode, TS0ID carries the first timeslot of each

frame.

TS0ID is aligned to the common H-MVIP

16.384 Mbit/s clock, CMV8MCLK, frame pulse

clock, CMVFPC, and frame pulse, CMVFPB.

TS0ID is updated on every second rising or

falling edge of CMV8MCLK as fixed by the

common H-MVIP frame pulse clock, CMVFPC.

The updating edge of CMV8MCLK is selected via

the CMVIDE bit in the Master H-MVIP Interface

Configuration register.

MVED[1]

MVED[2]

MVED[3]/S77

MVED[4]/SAC1FP

MVED[5]/SADATA[3]

MVED[6]/SADATA[4]

MVED[7]/SADATA[5]

MVED[8]/SADATA[6]

Input B10

A10

D10

B11

C12

D13

B13

C13

H-MVIP Egress Data (MVED[1:8]). The egress

data streams to be transmitted are input on these

pins. Each MVED[x] signal carries the channels

of four complete T1s or E1s formatted according

to the H-MVIP standard.

MVED[x] is aligned to the common H-MVIP

16.384 Mbit/s clock, CMV8MCLK, frame pulse

clock, CMVFPC, and frame pulse, CMVFPB.

MVED[x] is sampled on every second rising or

falling edge of CMV8MCLK as fixed by the

common H-MVIP frame pulse clock, CMVFPC.

The sampling edge of CMV8MCLK is selected

via the CMVEDE bit in the Master Common

Ingress Serial and H-MVIP Interface

Configuration register.

Each of MVED[1:4] and MVED[5:8] carries 16

independent T1s or E1s.

MVED[3:8] share the same pins as S77,

SAC1FP, and SADATA[3:6] respectively.

MVED[3:8] are selected when the SYSOPT[1:0]

are set to “01” (H-MVIP), in the Global

Configuration register.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 25

Pin Name Type Pin

No.

Function

CASED[1]

CASED[2]

CASED[3]

CASED[4]

CASED[5]

CASED[6]

CASED[7]

CASED[8]

Input H19

J20

J21

J22

K19

L20

L22

M22

Channel Associated Signaling Egress Data

(CASED[1:8]). Each CASED[x] signal carries

CAS for four complete T1s or E1s formatted

according to the H-MVIP standard. CASED[x]

carries the corresponding CAS values of the

channel data carried in MVED[x]. CASED[x] may

also present inband information for the control of

signaling insertion.

CASED[x] is aligned to the common H-MVIP

16.384 Mbit/s clock, CMV8MCLK, frame pulse

clock, CMVFPC, and frame pulse, CMVFPB.

CASED[x] is sampled on every second rising or

falling edge of CMV8MCLK as fixed by the

common H-MVIP frame pulse clock, CMVFPC.

The sampling edge of CMV8MCLK is selected

via the CMVEDE bit in the Master H-MVIP

Interface Configuration register.

Each of CASED[1:4] and CASED[5:8] carries 16

independent T1s or E1s.

CCSED[1]

CCSED[2]

CCSED[3]

Input H20

H21

H22

Common Channel Signaling Egress Data

(CCSED[1:3]). In T1 mode CCSED[1] carries

the common channel signaling channels to be

transmitted in each of the T1s. In E1 mode

CCSED carries up to 3 timeslots (15,16, 31) to

be transmitted in each of the E1s. CCSED is

formatted according to the H-MVIP standard.

CCSED is aligned to the common H-MVIP

16.384 Mbit/s clock, CMV8MCLK, frame pulse

clock, CMVFPC, and frame pulse, CMVFPB.

CCSED is sampled on every second rising or

falling edge of CMV8MCLK as fixed by the

common H-MVIP frame pulse clock, CMVFPC.

The sampling edge of CMV8MCLK is selected

via the CMVEDE bit in the Master H-MVIP

Interface Configuration register.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 26

Pin Name Type Pin

No.

Function

Recovered T1 and E1 Clocks

RECVCLK1 Output F2 Recovered Clock 1 (RECVCLK1). This clock

output is a recovered and de-jittered clock from

any one of the 32 T1 framers or E1 framers.

RECVCLK2 Output E4 Recovered Clock 2 (RECVCLK2). This clock

output is a recovered and de-jittered clock from

any one of the 32 T1 framers or E1 framers.

RECVCLK3 Output G3 Recovered Clock 3 (RECVCLK3). This clock

output is a recovered and de-jittered clock from

any one of the 32 T1 framers or E1 framers.

XCLK_T1 Input E2 T1 Crystal Clock Input (XCLK_T1). This input

clocks the digital phase locked loop that performs

jitter attenuation on the T1 recovered clocks

which drive the RECVCLK1/2/3 outputs.

XCLK_T1 is nominally a 37.056 MHz ± 32ppm,

50% duty cycle clock.

This input may be tied to ground in applications

that do not use the RECVCLK1/2/3 outputs as

support T1.

XCLK_E1 Input F3 E1 Crystal Clock Input (XCLK_E1). This input

clocks the digital phase locked loop that performs

jitter attenuation on the E1 recovered clocks

which drive the RECVCLK1/2/3 outputs.

XCLK_E1 is nominally a 49.152 MHz ± 32ppm,

50% duty cycle clock when configured for E1

modes.

This input may be tied to ground in applications

that do not use the RECVCLK1/2/3 outputs as

support E1.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 27

Pin Name Type Pin

No.

Function

SBI Line Side Interface

LREFCLK Input Y4 Line Reference Clock (LREFCLK). This signal

provides reference timing for the line side SBI

bus interface. On the incoming byte interface of

the line side SBI bus, LDC1FP, LDDATA[7:0],

LDDP, LDPL, LDV5 and LAC1FPI are sampled of

the rising edge or LREFCLK. In the outgoing byte

interface, LADATA[7:0], LADP, LAPL, LAV5 and

LAC1FPO are updated on the rising edge of

LREFCLK.

This clock is nominally a 19.44 MHz +/-50ppm

clock with a 50% duty cycle. This clock must be

phase locked to SREFCLK and can be externally

connected to SREFCLK, when the S77 input is

logic ‘0’.

LAC1FPI Input W10 Line Add C1 Frame Pulse Input (LAC1FPI).

The Add bus timing signal identifies the frame

and multiframe boundaries on the Add Data bus

LADATA[7:0].

LAC1FPI is set high to mark the first C1 byte of

the first transport envelope frame of the 4 frame

multiframe on the LADATA[7:0] bus. LAC1FPI

need not be presented on every occurrence of

the multiframe.

LAC1FPI is sampled on the rising edge of

LREFCLK.

LAC1FPO Output AA11 Line Add Bus C1 Frame Pulse Output

(LAC1FPO). The Add bus C1 frame pulse output

identifies the frame boundaries on the Line Add

Data bus LADATA[7:0]. LAC1FPO pulses high to

mark the first C1 byte of the SBI multiframe.

LAC1FPO will align to LAC1FPI if present, but

fly-wheels in its absence.

Multiple TE-32’s cannot be connected to the

same line side SBI bus interface.

LAC1FPO is updated on the rising edge of

LREFCLK.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 28

Pin Name Type Pin

No.

Function

LAPL Output AB11 Line Add Bus Tributary Payload Active

(LAPL). The tributary payload active signal

marks the bytes carrying the tributary payload.

LAPL is high during each tributary payload byte

on the LADATA[7:0] bus. LAPL will be low during

transport overhead, path overhead, V1 bytes and

V2 bytes. To indicate pointer adjustments, LAPL

will be asserted appropriately during the V3 byte

and following byte for the tributary.

Multiple TE-32’s cannot be connected to the

same line side SBI bus interface.

LAPL is updated on the rising edge of LREFCLK.

LADATA[0]

LADATA[1]

LADATA[2]

LADATA[3]

LADATA[4]

LADATA[5]

LADATA[6]

LADATA[7]

Output

Tristate

W14

Y13

A

A13

A

B13

W13

A

A12

W12

W11

Line Add Bus Data (LADATA[7:0]). The add

bus data contains the line side SBI Add bus

payload data in byte serial format. All transport

overhead bytes are set to 00h. LADATA[7] is the

most significant bit (corresponding to bit 1 of

each serial word, the first bit to be transmitted).

By default, LADATA[7:0] is only asserted during

the tributaries assigned to this device as

determined by the ENBL bit in the Line Side

INSBI Tributary Control Indirect Access Data

register. As options, LADATA[7:0] can be driven

all the time or during the first nine columns.

LADATA[7:0] is updated on the rising edge of

LREFCLK.

LADP Output

Tristate

A

B14 Line Add Bus Data Parity (LADP). The Add Bus

data parity signal carries the parity of the

outgoing signals. The parity calculation

encompasses the LADATA[7:0] bus, the LAV5

signal and the LAPL signal. Odd parity is

selected by setting the LAOP register bit to logic

1 and even parity is selected by setting the LAOP

bit to logic 0.

LADP is valid for all non-tristate cycles.

LADP is updated on the rising edge of LREFCLK.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 29

Pin Name Type Pin

No.

Function

LAV5 Output

Tristate

W15 Line Add Bus V5 Byte (LAV5). The outgoing

tributary V5 byte signal marks the various

tributary V5 bytes. LAV5 marks each tributary V5

byte on the LADATA[7:0] bus when high.

By default, LAV5 is only asserted during the

T1/E1 tributaries assigned to this device as

determined by the ENBL bit in Line Side INSBI

Tributary Control Indirect Access Data register.

As options, LAV5 can be driven all the time or

during the first nine columns.

LAV5 is updated on the rising edge of LREFCLK.

LDDATA[0]

LDDATA[1]

LDDATA[2]

LDDATA[3]

LDDATA[4]

LDDATA[5]

LDDATA[6]

LDDATA[7]

Input W5

AA6

AB5

Y3

Y6

AA5

AB4

AB3

Line Drop Bus Data (LDDATA[7:0]). The drop

bus data contains the T1/E1 receive payload data

in byte serial format. LDDATA[7] is the most

significant bit, corresponding to bit 1 of each

serial word, the bit transmitted first.

LDDATA[7:0] is sampled on the rising edge of

LREFCLK.

LDDP Input Y7 Line Drop Bus Data Parity (LDDP). The

incoming data parity signal carries the parity of

the incoming signals. The parity calculation

encompasses the LDDATA[7:0] bus, the LDV5

signal and the LDPL signal. Odd parity is

selected by setting the SBI_PAR_CTL bit in the

Line Side EXSBI Control Register high and even

parity is selected by setting the SBI_PAR_CTL bit

low.

LDDP is sampled on the rising edge of

LREFCLK.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 30

Pin Name Type Pin

No.

Function

LDC1FP Input AB6 Line Drop C1 Frame Pulse (LDC1FP). The

LDC1FP provides frame synchronization for

devices connected via an SBI interface. LDC1FP

is asserted, for one LREFCLK cycle, for the first

C1 byte of the SBI multiframe on the

LDDATA[7:0] bus. This signal occurs every

500µS (i.e. every 9720 LREFCLK cycles).

LDC1FP is sampled on the rising edge of

LREFCLK.

LDV5 Input W6 Line Drop Bus V5 Byte (LDV5). The incoming

tributary V5 byte signal marks the various

tributary V5 bytes. LDV5 marks each tributary V5

byte on the LDDATA[7:0] bus when high.

LDV5 is sampled on the rising edge of

LREFCLK.

LDPL Input Y8 Line Drop Bus Tributary Payload Active

(LDPL). The tributary payload active signal

marks the bytes carrying the tributary payload

which have been identified by an external

payload processor. When this signal is available,

the internal pointer processor can be bypassed.

LDPL is only respected for asynchronously

mapped tributaries.

LDPL is high during each tributary payload byte

on the LDDATA[7:0] bus.

LDPL is sampled on the rising edge of

LREFCLK.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 31

Pin Name Type Pin

No.

Function

SBI System Side Interface

CTCLK Input F19 Common Transmit Clock (CTCLK). This input

signal is used as a reference transmit tributary

clock which can be used in egress Clock Master

modes. CTCLK must be multiple of 8 kHz. The

transmit clock is derived by the jitter attenuator

PLL using CTCLK as a reference.

The TE-32 may be configured to ignore the

CTCLK input and lock to the data or one of the

recovered Ingress clocks instead, RECVCLK1,

RECVCLK2 and RECVCLK3. The receive

tributary clock is automatically substituted for

CTCLK if line loopback or looptiming is enabled.

S77/MVED[3] Input D10 System Side SBI 77.76 MHz Select (S77). This

input determines the frequency of SREFCLK. If

S77 is low, SREFCLK is expected to be

19.44MHz. If S77 is high, SREFCLK is expected

to be 77.76 MHz and data is driven and sampled

every fourth cycle.

This signal is a don’t care when the

SYSOPT[1:0] register bits are binary “01” (HMVIP inteface). In this mode SREFCLK is

required to be 19.44 MHz.

S77 is expected to be held static.

S77 shares the same pin as MVED[3]. S77 is

selected when the SYSOPT[1:0] bits are set to

“10” or “11”, in the Global Configuration register.

SREFCLK Input C10 System Reference Clock (SREFCLK). This

system reference clock is a nominal 19.44 MHz

+/-50ppm pr 77.76 MHz +/-50ppm 50% duty

cycle clock. This clock is common to both the add

and drop sides of the SBI bus.

SREFCLK must be active for all applications.

When the SYSOPT[1:0] register bits are binary

“01” (H-MVIP interface), SREFCLK is required to

be 19.44 MHz.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 32

Pin Name Type Pin

No.

Function

SDC1FP/MVID[1] I/O B3 SBI Drop C1 Frame Pulse (SDC1FP). The

SDC1FP C1 frame pulse synchronizes devices

interfacing to the Insert SBI bus. The frame pulse

indicates SBI bus multiframe alignment which

occurs every 500 µS, therefore this signal is

pulsed every 9720 SREFCLK cycles (38880

cycles if S77 is high). This signal does not need

to occur every SBI multiframe and is also used to

indicate T1 and E1 multiframe alignment in

synchronous SBI mode by pulsing at multiples of

every 12 SBI multiframes (48 T1/E1 frames). In

synchronous locked mode, as selected by the

SYNCSBI context bit programmed through the

RX-SBI-ELST Indirect Channel Data register,

SDC1FP pulses every 116640 SREFCLK cycles

(466560 cycles if S77 is high). If the SYNCSBI

bit is logic 1 for at least one tributary, SDC1FP

must indicate T1 and E1 multiframe alignment.

The TE-32 can be configured to generate this

frame pulse. Only one device on the SBI bus

should generate this signal. By default this

signal is not enabled to generate the frame

pulse.

If a SDC1FP pulse is received at an unexpected

cycle, the Drop bus with become high-impedence

until two consecutive valid SDC1FP pulses occur.

The system frame pulse is a single SREFCLK

cycle long and is updated on the rising edge of

SREFCLK.

This signal must be held low if the SBI bus is not

being used.

SDC1FP shares the same pin as MVID[1].

SDC1FP is selected when the SYSOPT[1:0] bits

are set to “10” or “11”, in the Global Configuration

register.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 33

Pin Name Type Pin

No.

Function

SAC1FP/MVED[4] Input B11 SBI Add C1 Frame Pulse (SAC1FP). The

Extract C1 frame pulse synchronizes devices

interfacing to the Extract SBI bus. The frame

pulse indicates SBI bus multiframe alignment

which occurs every 500 µS, therefore this signal

is pulsed every 9720 SREFCLK cycles (38880

cycles if S77 is high). This signal does not need

to occur every SBI multiframe. SAC1FP is

sampled on the rising edge of SREFCLK.

This signal must be held low if the SBI bus is not

being used.

SAC1FP shares the same pin as MVED[4].

SAC1FP is selected when the SYSOPT[1:0] bits

are set to “10” or “11”, in the Global Configuration

register.

SADATA[0]

SADATA[1]

SADATA[2]

SADATA[3]/MVED[5]

SADATA[4]/MVED[6]

SADATA[5]/MVED[7]

SADATA[6]/MVED[8]

SADATA[7]

Input A11

D12

B12

C12

D13

B13

C13

D14

System Add Bus Data (SADATA[7:0]). The

System add data bus is a time division

multiplexed bus which carries the E1, T1 and

DS3 tributary data is byte serial format over the

SBI bus structure. This device only monitors the

add data bus during the timeslots assigned to

this device.

SADATA[7:0] is sampled on the rising edge of

SREFCLK.

SADATA[3:6] share the same pins as MVED[5:8].

SADATA[3:6] is selected when the SYSOPT[1:0]

bits are set to “10” or “11”, in the Global

Configuration register.

SADP Input A14 System Add Bus Data Parity (SADP). The

system add bus signal carries the even or odd

parity for the add bus signals SADATA[7:0],

SAPL and SAV5. The TE-32 monitors the add

bus parity cycles when S77 is low and during the

entire selected STM-1 when S77 is high.

SADP is sampled on the rising edge of

SREFCLK.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 34

Pin Name Type Pin

No.

Function

SAPL Input B14 System Add Bus Payload Active (SAPL). The

add bus payload active signal indicates valid data

within the SBI bus structure. This signal must be

high during all octets making up a tributary. This

signal goes high during the V3 octet of a tributary

to indicate negative timing adjustments between

the tributary rate and the fixed SBI bus structure.

This signal goes low during the octet after the V3

octet of a tributary to indicate positive timing

adjustments between the tributary rate and the

fixed SBI bus structure.

The TE-32 only monitors the add bus payload

active signal during the tributary timeslots

assigned to this device.

SAPL is sampled on the rising edge of

SREFCLK.

SAV5 Input C14 System Add Bus Payload Indicator (SAV5).

The add bus payload indicator locates the

position of the floating payloads for each tributary

within the SBI bus structure. Timing differences

between the tributary timing and the synchronous

SBI bus are indicated by adjustments of this

payload indicator relative to the fixed SBI bus

structure.

All timing adjustments indicated by this signal

must be accompanied by appropriate

adjustments in the SAPL signal.

The TE-32 only monitors the add bus payload

indicator signal during the tributary timeslots

assigned to this device.

SAV5 is sampled on the rising edge of

SREFCLK.

PRELIMINARY

PM4332 TE-32

DATA SHEET

PMC-2011402 ISSUE 1 HIGH DENSITY 32 CHANNEL T1/E1/J1 FRAMER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR THE INTERNAL USE OF ITS CUSTOMERS 35

Pin Name Type Pin

No.

Function

SAJUST_REQ/

MVID[3]

Output

Tristate

A2 System Add Bus Justification Request

(SAJUST_REQ). The justification request signals

the Link Layer device to speed up, slow down or

maintain the rate which it is sending data to the

TE-32. This is only used when the TE-32 is the

timing master for the tributary transmit direction.

This active high signal indicates negative timing

adjustments when asserted high during the V3