PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

PM4318

OCTLIU

OCTAL E1/T1/J1 LINE INTERFACE

DEVICE

DATASHEET

PROPRIETARY AND CONFIDENTIAL

PRELIMINARY

ISSUE 3: APRIL 2001

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 .415.6000

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

CONTENTS

1 FEATURES........................................................................................................................ 1

1.1 EACH RECEIVER SECTION: .............................................................................. 2

1.2 EACH TRANSMITTER SECTION: ....................................................................... 2

2 APPLICATIONS.................................................................................................................4

3 REFERENCES ..................................................................................................................5

4 APPLICATION EXAMPLES............................................................................................... 7

5 BLOCK DIAGRAM............................................................................................................. 9

6 DESCRIPTION ................................................................................................................ 11

7 PIN DIAGRAM................................................................................................................. 12

8 PIN DESCRIPTION .........................................................................................................13

9 FUNCTIONAL DESCRIPTION ........................................................................................35

9.1 OCTANTS...........................................................................................................35

9.2 RECEIVE INTERFACE ......................................................................................35

1.3 CLOCK AND DATA RECOVERY (CDRC).......................................................... 36

1.4 RECEIVE JITTER ATTENUATOR (RJAT) .........................................................38

1.5 T1 INBAND LOOPBACK CODE DETECTOR (IBCD) ....................................... 38

1.6 T1 PULSE DENSITY VIOLATION DETECTOR (PDVD) ................................... 39

1.7 PERFORMANCE MONITOR COUNTERS (PMON).......................................... 39

1.8 PSEUDO RANDOM BINARY SEQUENCE GENERATION AND DETECTION

(PRBS) ...............................................................................................................39

1.9 T1 INBAND LOOPBACK CODE GENERATOR (XIBC)..................................... 39

1.10 PULSE DENSITY ENFORCER (XPDE)............................................................. 39

1.11 TRANSMIT JITTER ATTENUATOR (TJAT) ....................................................... 40

1.12 LINE TRANSMITTER......................................................................................... 44

1.13 TIMING OPTIONS (TOPS) ................................................................................ 44

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE i

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

1.14 SCALEABLE BANDWIDTH INTERCONNECT (SBI) INTERFACE ................... 44

1.14.1 INTERFACING OCTLIUS TO A HIGH DENSITY FRAMER.................. 45

1.15 SBI EXTRACTER AND PISO............................................................................. 46

1.16 SBI INSERTER AND SIPO ................................................................................ 46

1.17 SBI TO CLK/DATA CONVERTER ...................................................................... 46

1.18 SERIAL PROM INTERFACE.............................................................................. 46

1.19 JTAG TEST ACCESS PORT.............................................................................. 48

1.20 MICROPROCESSOR INTERFACE ................................................................... 48

2 NORMAL MODE REGISTER DESCRIPTION ................................................................ 49

2.1 NORMAL MODE REGISTER MEMORY MAP ................................................... 50

3 TEST FEATURES DESCRIPTION................................................................................ 169

3.1 JTAG TEST PORT............................................................................................ 169

4 OPERATION.................................................................................................................. 172

4.1 CONFIGURING THE OCTLIU FROM RESET................................................. 172

4.2 SERVICING INTERRUPTS.............................................................................. 172

4.3 USING THE PERFORMANCE MONITORING FEATURES ............................173

4.4 USING THE TRANSMIT LINE PULSE GENERATOR ..................................... 173

4.5 USING THE LINE RECEIVER ......................................................................... 194

4.6 USING THE PRBS GENERATOR AND DETECTOR ......................................201

4.7 LOOPBACK MODES ....................................................................................... 201

4.7.1 LINE LOOPBACK................................................................................ 201

4.7.2 DIAGNOSTIC DIGITAL LOOPBACK ..................................................202

4.8 JTAG SUPPORT ..............................................................................................202

4.8.1 TAP CONTROLLER ............................................................................204

5 FUNCTIONAL TIMING ..................................................................................................210

5.1 SBI BUS INTERFACE TIMING ........................................................................210

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE ii

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

5.2 LINE CODE VIOLATION INSERTION ............................................................. 211

5.3 ALARM INTERFACE........................................................................................ 213

6 ABSOLUTE MAXIMUM RATINGS ................................................................................214

7 D.C. CHARACTERISTICS ............................................................................................215

8 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS .............................217

9 OCTLIU TIMING CHARACTERISTICS......................................................................... 221

9.1 RSTB TIMING (FIGURE 33) ............................................................................ 221

9.2 XCLK INPUT TIMING (FIGURE 34)................................................................. 221

9.3 TRANSMIT SERIAL INTERFACE (FIGURE 35) .............................................. 222

9.4 RECEIVE SERIAL INTERFACE (FIGURE 36)................................................. 223

9.5 SBI INTERFACE (FIGURE 37 TO FIGURE 39)............................................... 224

9.6 SERIAL PROM (SPI) INTERFACE (FIGURE 40) ............................................227

9.7 ALARM INTERFACE (FIGURE 41).................................................................. 228

9.8 INGRESS CLK/DATA INTERFACE (FIGURE 42)............................................ 228

9.9 EGRESS CLK/DATA INTERFACE (FIGURE 43) ............................................. 229

9.10 JTAG PORT INTERFACE (FIGURE 44) ..........................................................230

10 ORDERING AND THERMAL INFORMATION .............................................................. 232

11 MECHANICAL INFORMATION .....................................................................................233

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iii

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

LIST OF FIGURES

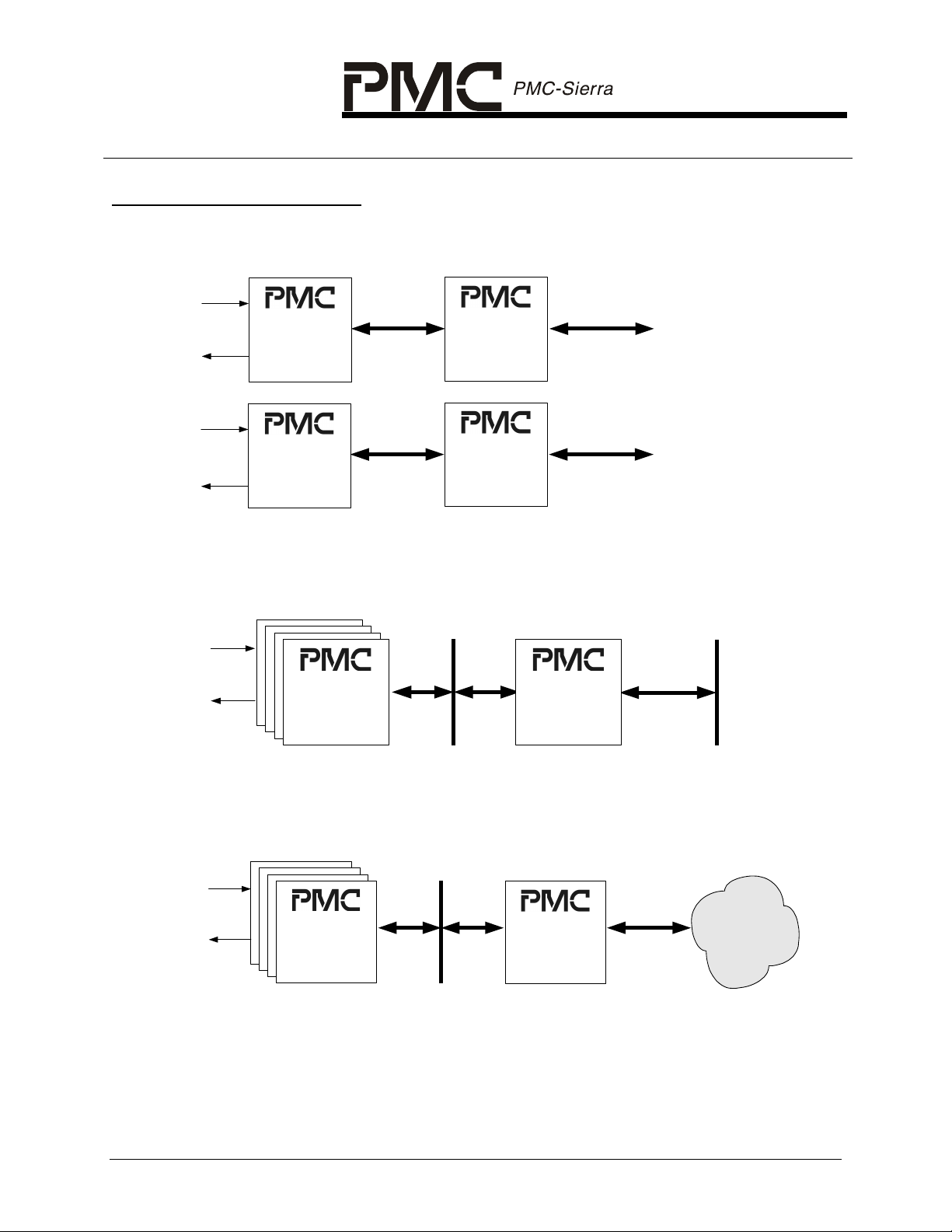

FIGURE 1 – T1/E1 FRAMER/TRANSCEIVER APPLICATION................................................. 7

FIGURE 2 – HIGH DENSITY T1/E1 FRAMER/TRANSCEIVER APPLICATION ...................... 7

FIGURE 3 – HIGH DENSITY LEASED LINE CIRCUIT EMULATION APPLICATION.............. 7

FIGURE 4 – METRO OPTICAL ACCESS EQUIPMENT .......................................................... 8

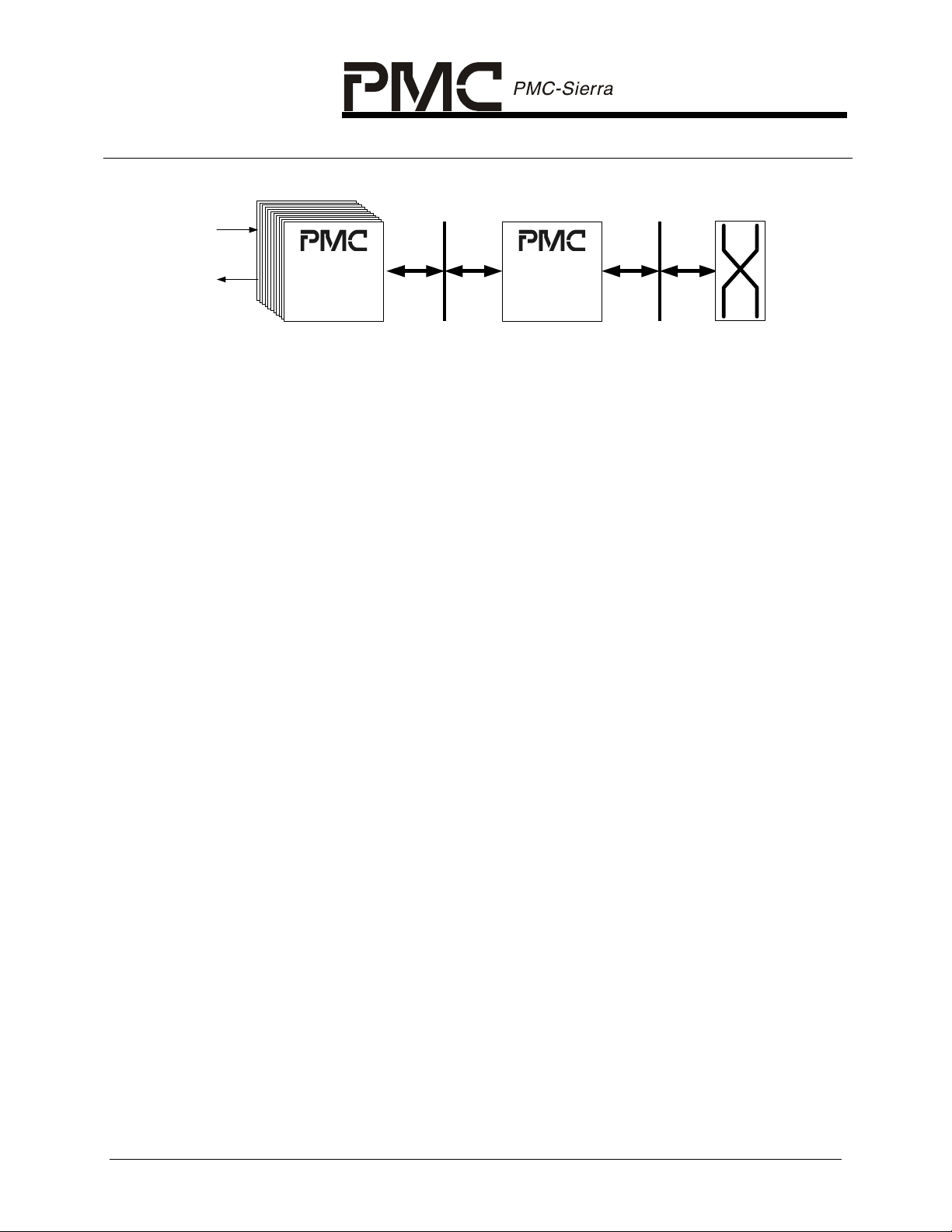

FIGURE 5 – OCTLIU BLOCK DIAGRAM – LIUS ENABLED ................................................... 9

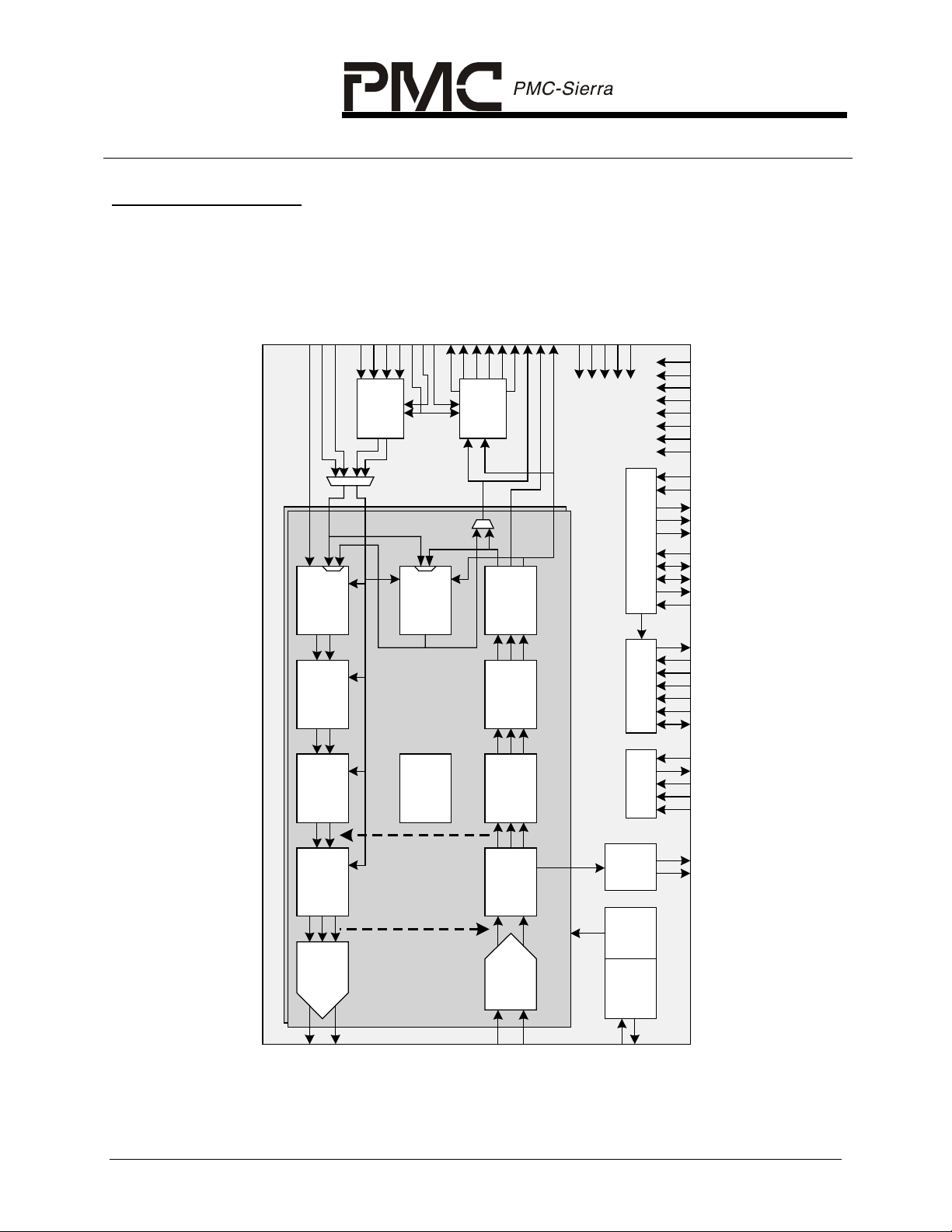

FIGURE 6 – OCTLIU BLOCK DIAGRAM – SBI TO CLK/DATA CONVERTER, LIUS

DISABLED .......................................................................................................... 10

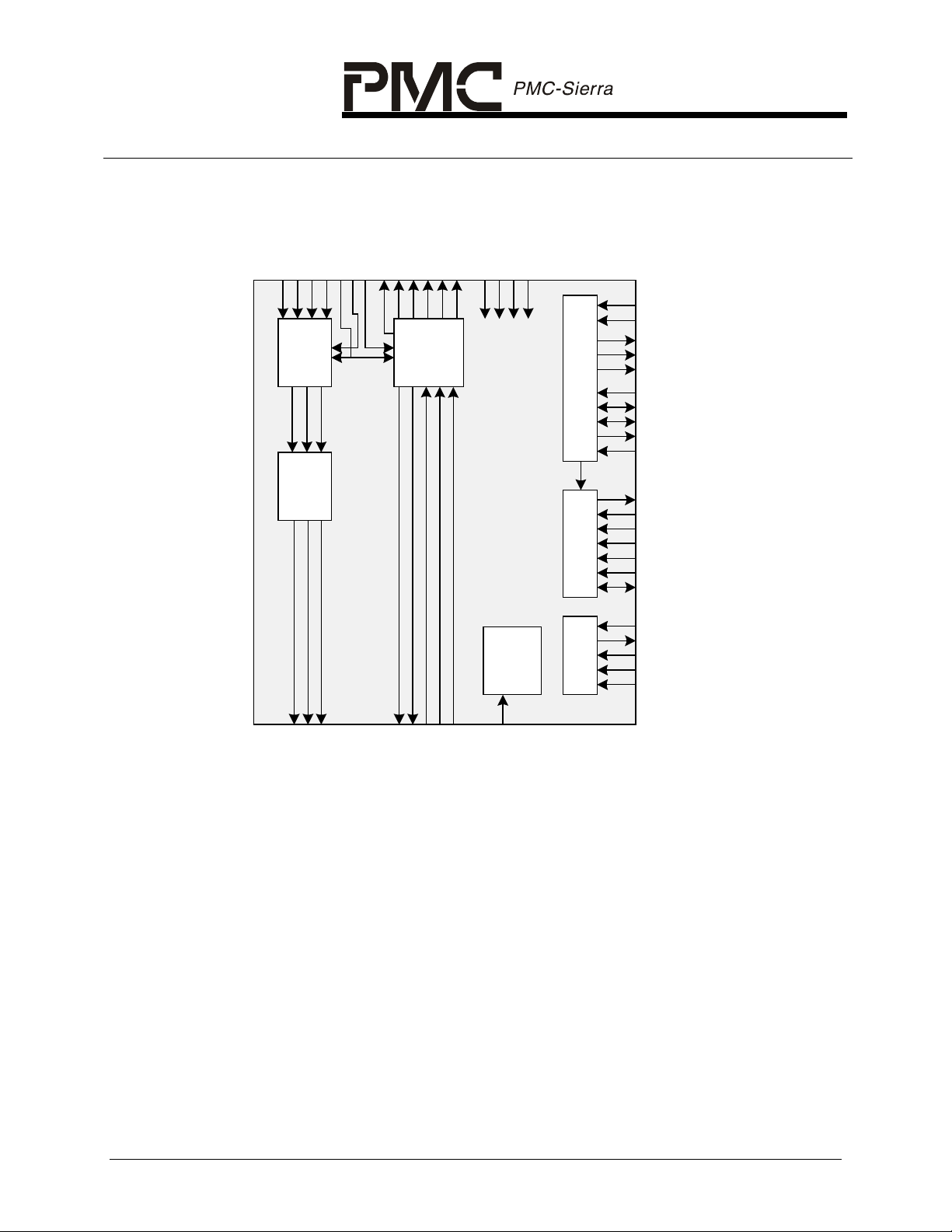

FIGURE 7 – PIN DIAGRAM .................................................................................................... 12

FIGURE 8 – EXTERNAL ANALOGUE INTERFACE CIRCUITS ............................................35

FIGURE 9 – T1 JITTER TOLERANCE ...................................................................................37

FIGURE 10 – COMPLIANCE WITH ITU-T SPECIFICATION G.823 FOR E1 INPUT JITTER .38

FIGURE 11 – TJAT JITTER TOLERANCE ............................................................................... 41

FIGURE 12 – TJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY........................ 42

FIGURE 13 – TJAT JITTER TRANSFER.................................................................................. 43

FIGURE 14 – SBI TO FRAMER LINE SIDE INTERFACE ........................................................ 45

FIGURE 15 – SERIAL PROM CASCADE INTERFACE ...........................................................46

FIGURE 16 – SERIAL PROM COMMAND FORMAT............................................................... 47

FIGURE 17 – TRANSMIT TIMING OPTIONS........................................................................... 75

FIGURE 18 – LINE LOOPBACK ............................................................................................. 202

FIGURE 19 – DIAGNOSTIC DIGITAL LOOPBACK................................................................ 202

FIGURE 20 – BOUNDARY SCAN ARCHITECTURE ............................................................. 203

FIGURE 21 – TAP CONTROLLER FINITE STATE MACHINE ............................................... 205

FIGURE 22 – INPUT OBSERVATION CELL (IN_CELL) ........................................................ 208

FIGURE 23 – OUTPUT CELL (OUT_CELL) OR ENABLE CELL (ENABLE).......................... 208

FIGURE 24 – BIDIRECTIONAL CELL (IO_CELL).................................................................. 209

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE iv

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

FIGURE 25 – LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS .....................209

FIGURE 26 – SBI BUS FUNCTIONAL TIMING...................................................................... 210

FIGURE 27 – B8ZS LINE CODE VIOLATION INSERTION ................................................... 211

FIGURE 28 – HDB3 LINE CODE VIOLATION INSERTION................................................... 212

FIGURE 29 – AMI LINE CODE VIOLATION INSERTION ...................................................... 213

FIGURE 30 – LOS ALARM SERIAL OUTPUT........................................................................ 213

FIGURE 31 – MICROPROCESSOR INTERFACE READ TIMING......................................... 218

FIGURE 32 – MICROPROCESSOR INTERFACE WRITE TIMING ....................................... 220

FIGURE 33 – RSTB TIMING................................................................................................... 221

FIGURE 34 – XCLK INPUT TIMING ....................................................................................... 221

FIGURE 35 – TRANSMIT SERIAL INTERFACE TIMING DIAGRAM..................................... 222

FIGURE 36 – RECEIVE SERIAL INTERFACE TIMING DIAGRAM .......................................223

FIGURE 37 – SBI FRAME PULSE TIMING ............................................................................ 224

FIGURE 38 – SBI ADD BUS TIMING .....................................................................................225

FIGURE 39 – SBI DROP BUS TIMING .................................................................................. 226

FIGURE 40 – SPI INTERFACE TIMING ................................................................................. 227

FIGURE 41 – ALARM INTERFACE TIMING........................................................................... 228

FIGURE 42 – INGRESS CLK/DATA INTERFACE TIMING DIAGRAM................................... 229

FIGURE 43 – EGRESS CLK/DATA INTERFACE TIMING DIAGRAM .................................... 229

FIGURE 44 – JTAG PORT INTERFACE TIMING................................................................... 231

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE v

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

LIST OF TABLES

TABLE 1 – EXTERNAL COMPONENT DESCRIPTIONS ....................................................36

TABLE 2 – SERIAL PROM COMMANDS – CODE BITS .....................................................47

TABLE 3 – SERIAL PROM SPECIAL COMMANDS ............................................................ 47

TABLE 4 – NORMAL MODE REGISTER MEMORY MAP ................................................... 50

TABLE 5 – CLOCK SYNTHESIS MODE.............................................................................. 65

TABLE 6 – TJAT FIFO OUTPUT CLOCK SOURCE ............................................................ 74

TABLE 7 – TJAT PLL SOURCE............................................................................................ 74

TABLE 8 – INSBI TRIBUTARY CHARACTERISTICS ..........................................................89

TABLE 9 – EXSBI TRIBUTARY CHARACTERISTICS....................................................... 105

TABLE 10 – EXSBI CLOCK GENERATION OPTIONS........................................................ 106

TABLE 11 – TRANSMIT IN-BAND CODE LENGTH ............................................................ 114

TABLE 12 – LOOPBACK CODE CONFIGURATIONS......................................................... 126

TABLE 13 – LOSS OF SIGNAL THRESHOLDS ..................................................................131

TABLE 14 – TRANSMIT OUTPUT AMPLITUDE .................................................................. 148

TABLE 15 – ALOS DETECTION/CLEARANCE THRESHOLDS.......................................... 154

TABLE 16 – EQUALIZATION FEEDBACK FREQUENCIES................................................ 161

TABLE 17 – VALID PERIOD................................................................................................. 162

TABLE 18 – BOUNDARY SCAN REGISTER ....................................................................... 170

TABLE 19 – DEFAULT SETTINGS....................................................................................... 172

TABLE 20 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 LONG HAUL (LBO 0 DB)175

TABLE 21 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 LONG HAUL (LBO 7.5 DB)

.......................................................................................................................... 176

TABLE 22 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 LONG HAUL (LBO 15 DB)

.......................................................................................................................... 177

TABLE 23 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 LONG HAUL (LBO 22.5 DB)

.......................................................................................................................... 178

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vi

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

TABLE 24 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (0 – 110 FT.)

.......................................................................................................................... 179

TABLE 25 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (110 –

220 FT.) ............................................................................................................. 180

TABLE 26 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (220 –

330 FT.) ............................................................................................................. 181

TABLE 27 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (330 –

440 FT.)............................................................................................................. 182

TABLE 28 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (440 –

550 FT.) ............................................................................................................. 183

TABLE 29 – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (550 –

660 FT.) ............................................................................................................. 184

TABLE 30 – TR62411 TRANSMIT WAVEFORM VALUES FOR T1 LONG HAUL (LBO 0 DB)

.......................................................................................................................... 185

TABLE 31 – TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (0 – 110 FT.)186

TABLE 32 – TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (110 –

220 FT.) ............................................................................................................. 187

TABLE 33 – TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (220 –

330 FT.) ............................................................................................................. 188

TABLE 34 – TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (330 –

440 FT.) ............................................................................................................. 189

TABLE 35 – TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (440 –

550 FT.) ............................................................................................................. 190

TABLE 36 – TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (550 –

660 FT.) ............................................................................................................. 191

TABLE 37 – TRANSMIT WAVEFORM VALUES FOR E1 120 OHM ....................................192

TABLE 38 – TRANSMIT WAVEFORM VALUES FOR E1 75 OHM ......................................193

TABLE 39 – RLPS REGISTER PROGRAMMING................................................................ 194

TABLE 40 – RLPS EQUALIZER RAM TABLE (T1 MODE) .................................................. 195

TABLE 41 – RLPS EQUALIZER RAM TABLE (E1 MODE) .................................................. 198

TABLE 42 – RLPS EQUALIZER RAM TABLE (MONITOR MODE) .....................................201

TABLE 43 – ABSOLUTE MAXIMUM RATINGS ...................................................................214

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE vii

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

TABLE 44 – D.C. CHARACTERISTICS ............................................................................... 215

TABLE 45 – MICROPROCESSOR INTERFACE READ ACCESS ...................................... 217

TABLE 46 – MICROPROCESSOR INTERFACE WRITE ACCESS..................................... 219

TABLE 47 – RTSB TIMING................................................................................................... 221

TABLE 48 – XCLK INPUT TIMING....................................................................................... 221

TABLE 49 – TRANSMIT SERIAL INTERFACE ....................................................................222

TABLE 50 – RECEIVE SERIAL INTERFACE....................................................................... 223

TABLE 51 – CLOCKS AND SBI FRAME PULSE .................................................................224

TABLE 52 – SBI ADD BUS ................................................................................................... 225

TABLE 53 – SBI DROP BUS ................................................................................................225

TABLE 54 – SPI INTERFACE............................................................................................... 227

TABLE 55 – ALARM INTERFACE ........................................................................................ 228

TABLE 56 – INGRESS CLK/DATA INTERFACE ..................................................................228

TABLE 57 – ENGRESS CLK/DATA INTERFACE................................................................. 229

TABLE 58 – JTAG PORT INTERFACE.................................................................................230

TABLE 59 – ORDERING INFORMATION ............................................................................232

TABLE 60 – OCTLIU THETA JC........................................................................................... 232

TABLE 61 – OCTLIU JUNCTION TEMPERATURE .............................................................232

TABLE 62 – OCTLIU THETA JA VS. AIRFLOW ................................................................... 232

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE viii

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

1 FEATURES

• Monolithic device which integrates eight T1/J1 or E1 short haul and long haul line interface circuits.

• Software switchable between T1/J1 and E1 operation on a per-device basis.

• Meets or exceeds T1/J1 and E1 shorthaul and longhaul network access specifications including ANSI

T1.102, T1.403, T1.408, AT&T TR 62411, ITU-T G.703, G.704 as well as ETSI 300-011, CTR-4, CTR12 and CTR-13.

• Provides encoding and decoding of B8ZS, HDB3 and AMI line codes.

• Provides receive equalization, clock recovery and line performance monitoring.

• Provides transmit and receive jitter attenuation.

• Provides digitally programmable long haul and short haul line build out.

• Provides a selectable, per channel independent de-jittered T1 or E1 recovered clock for system timing

and redundancy.

• Provides PRBS generators and detectors on each tributary for error testing at DS1 and E1 rates as

recommended in ITU-T O.151.

• Provides either serial clock/data or parallel Scaleable Bandwidth Interconnect (SBI) interfaces on the

system side.

• Can be configured to act as a converter between the SBI interfaces and serial clock/data. In this

mode, the LIUs are unused.

• Provides an 8-bit microprocessor bus interface for configuration, control, and status monitoring.

• Provides a hardware-only (no microprocessor) mode in which configuration data is read from an SPI-

compatible serial PROM. The PROM interface can be cascaded such that multiple OCTLIU devices

can be configured simultaneously from a single PROM.

• Uses line rate system clock.

• Provides an IEEE 1149.1 (JTAG) compliant Test Access Port (TAP) and controller for boundary scan

test.

• Implemented in a low power 3.3 V tolerant 1.8/3.3 V CMOS technology.

• Available in a high density 288-pin Tape-SBGA (23 mm by 23 mm) package.

• Provides a –40°C to +85°C Industrial temperature operating range.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 1

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

1.1 Each Receiver Section:

• Supports T1 signal reception for distances with up to 36 dB of cable attenuation at nominal conditions

using PIC 22 gauge cable emulation.

• Supports E1 signal reception for distances with up to 36 dB of cable attenuation at nominal conditions

using PIC 22 gauge cable emulation.

• Supports G.772 compliant non-intrusive protected monitoring points.

• Recovers clock and data using a digital phase locked loop for high jitter tolerance.

• Tolerates more than 0.3 UI peak-to-peak; high frequency jitter as required by AT&T TR 62411 and

Bellcore TR-TSY-000170.

• Outputs either dual rail recovered line pulses, a single rail DS-1/E1 signal or parallel data in SBI bus

format.

• Performs B8ZS or AMI decoding when processing a bipolar DS-1 signal and HDB3 or AMI decoding

when processing a bipolar E1 signal.

• Detects line code violations (LCVs), B8ZS/HDB3 line code signatures, and 4 (E1+HDB3), 8

(T1+B8ZS) or 16 (AMI) successive zeros.

• Accumulates up to 8191 line code violations (LCVs), for performance monitoring purposes, over

accumulation intervals defined by the period between software write accesses to the LCV register.

• Detects loss of signal (LOS), which is defined as 10, 15, 31, 63, or 175 successive zeros.

• Detects programmable inband loopback activate and deactivate code sequences received in the DS-

1 data stream when they are present for 5.1 seconds. Optionally, enters loopback mode

automatically on detection of an inband loopback code.

• Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving 192-bit window.

11

• A pseudo-random sequence user selectable from 2

–1, 215 –1 or 220 –1, may be detected in the

T1/E1 stream in either the receive or transmit directions. The detector counts pattern errors using a

24-bit saturating PRBS error counter.

1.2 Each Transmitter Section:

• Supports transfer of transmitted single rail PCM and signaling data from 1.544 Mbit/s and 2.048

Mbit/s backplane buses.

• Generates DSX-1 shorthaul and DS-1 longhaul pulses with programmable pulse shape compatible

with AT&T, ANSI and ITU requirements.

• Generates E1 pulses compliant to G.703 recommendations.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 2

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

• Provides a digitally programmable pulse shape extending up to 5 transmitted bit periods for custom

long haul pulse shaping applications.

• Provides line outputs that are current limited and may be tristated for protection or in redundant

applications.

• Provides a digital phase locked loop for generation of a low jitter transmit clock complying with all jitter

attenuation, jitter transfer and residual jitter specifications of AT&T TR 62411 and ETSI TBR 12 and

TBR 13.

• Provides a FIFO buffer for jitter attenuation and rate conversion in the transmit path.

• Allows bipolar violation (BPV) transparent operation for error restoring regenerator applications.

• Allows bipolar violation (BPV) insertion for diagnostic testing purposes.

• Supports all ones transmission for alarm indication signal (AIS) generation.

• Accepts either dual rail or single rail DS-1/E1 signals or parallel data from the SBI interface.

• Performs B8ZS or AMI encoding when processing a single rail or SBI-sourced DS-1 signal and HDB3

or AMI encoding when processing a single rail or SBI-sourced E1 signal.

11

• A pseudo-random sequence user selectable from 2

–1, 215 –1 or 220 –1, may be inserted into or

detected from the T1 or E1 stream in either the receive or transmit directions.

• Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving 192-bit window and

optionally stuffs ones to maintain minimum ones density.

• Supports transmission of a programmable unframed inband loopback code sequence.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 3

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

2 APPLICATIONS

• Metro Optical Access Equipment

• Edge Router Linecards

• Multiservice ATM Switch Linecards

• 3G Base Station Controllers (BSC)

• 3G Base Transceiver Stations (BTS)

• Digital Private Branch Exchanges (PBX)

• Digital Access Cross-Connect Systems (DACS) and Electronic DSX Cross-Connect Systems

(EDSX)

• T1/E1 Repeaters

• Test Equipment

• SBI to clk/data converter in multi-service access equipment.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 4

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

3 REFERENCES

1. ANSI – T1.102-1993 – American National Standard for Telecommunications – Digital

Hierarchy – Electrical Interfaces.

2. ANSI – T1.107-1995 – American National Standard for Telecommunications – Digital

Hierarchy – Formats Specification.

3. ANSI – T1.403-1999 – American National Standard for Telecommunications – Carrier to

Customer Installation – DS-1 Metallic Interface Specification.

4. ANSI – T1.408-1990 – American National Standard for Telecommunications – Integrated

Services Digital Network (ISDN) Primary Rate – Customer Installation Metallic Interfaces

Layer 1 Specification.

5. AT&T – TR 62411 – Accunet T1.5 – Service Description and Interface Specification,

December 1990.

6. AT&T – TR 62411 – Accunet T1.5 – Service Description and Interface Specification,

Addendum 1, March 1991.

7. AT&T – TR 62411 – Accunet T1.5 – Service Description and Interface Specification,

Addendum 2, October 1992.

8. TR-TSY-000170 – Bellcore – Digital Cross-Connect System Requirements and Objectives,

Issue 1, November 1985.

9. TR-N1WT-000233 – Bell Communications Research – Wideband and Broadband Digital

Cross-Connect Systems Generic Criteria, Issue 3, November 1993.

10. TR-NWT-000303 – Bell Communications Research – Integrated Digital Loop Carrier Generic

Requirements, Objectives, and Interface, Issue 2, December, 1992.

11. TR-TSY-000499 – Bell Communications Research – Transport Systems Generic

Requirements (TSGR): Common Requirement, Issue 5, December, 1993.

12. ETSI – ETS 300 011 – ISDN Primary Rate User-Network Interface Specification and Test

Principles, 1992.

13. ETSI – ETS 300 233 – Access Digital Section for ISDN Primary Rates.

14. ETSI – CTR 4 – Integrated Services Digital Network (ISDN); Attachment requirements for

terminal equipment to connect to an ISDN using ISDN primary rate access, November 1995.

15. ETSI – CTR 12 – Business Telecommunications (BT); Open Network Provision (ONP)

technical requirements; 2 048 kbit/s digital unstructured leased lines (D2048U) Attachment

requirements for terminal equipment interface, December 1993.

16. ETSI – CTR 13 – Business Telecommunications (BTC); 2 048 kbit/s digital structured leased

lines (D2048S); Attachment requirements for terminal equipment interface, January 1996.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 5

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

17. FCC Rules – Part 68.308 – Signal Power Limitations.

18. ITU-T – Recommendation G.703 – Physical/Electrical Characteristics of Hierarchical Digital

Interface, Geneva, 1998.

19. ITU-T – Recommendation G.704 – Synchronous Frame Structures Used at Primary

Hierarchical Levels, July 1998.

20. ITU-T Recommendation G.772 – Protected Monitoring Points Provided on Digital

Transmission Systems, 1992.

21. ITU-T – Recommendation G.775 – Loss of Signal (LOS), November 1998.

22. ITU-T Recommendation G.823, - The Control of Jitter and Wander Within Digital Networks

Which are Based on the 2048 kbit/s Hierarchy, 1993.

23. ITU-T – Recommendation I.431 – Primary Rate User-Network Interface – Layer 1

Specification, 1993.

24. ITU-T Recommendation O.151, - Error Performance Measuring Equipment For Digital

Systems at the Primary Bit Rate and Above, 1992.

25. TTC Standard JT-G703 – Physical/Electrical Characteristics of Hierarchical Digital Interfaces,

1995.

26. TTC Standard JT-G704 – Frame Structures on Primary and Secondary Hierarchical Digital

Interfaces, 1995.

27. TTC Standard JT-I431 – ISDN Primary Rate User-Network Interface Layer 1 – Specification,

1995.

28. Nippon Telegraph and Telephone Corporation – Technical Reference for High-Speed Digital

Leased Circuit Services, Third Edition, 1990.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 6

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

4 APPLICATION EXAMPLES

Figure 1 – T1/E1 Framer/Transceiver Application

8 x T1 lines

8 x E1 lines

OCTLIU

PM4318

OCTLIU

PM4318

Clock and Data

TOCTL

PM4388

Octal T1 Framer

Clock and Data

EOCTL

PM6388

Octal E1 Framer

Backplane

Backplane

Figure 2 – High Density T1/E1 Framer/Transceiver Application

SBI

32 T1/J1

or E1 lines

OCTLIU

OCTLIU

OCTLIU

OCTLIU

PM4318

PM4318

PM4318

PM4318

4xOCTLIU

TE32

PM4332

T1/J1/E1 Framer

H-MVIP or SBI

Figure 3 – High Density Leased Line Circuit Emulation Application

SBI

32 T1/J1

or E1 lines

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 7

OCTLIU

OCTLIU

OCTLIU

OCTLIU

PM4318

PM4318

PM4318

PM4318

4xOCTLIU

AAL1gator 32

PM73122

AAL1 SAR

Utopia L2

ATM

Backbone

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

Figure 4 – Metro Optical Access Equipment

84 T1/J1

or 63 E1 lines

OCTLIU

OCTLIU

OCTLIU

OCTLIU

OCTLIU

OCTLIU

OCTLIU

OCTLIU

OCTLIU

OCTLIU

OCTLIU

PM4318

PM4318

PM4318

PM4318

PM4318

PM4318

PM4318

PM4318

PM4318

PM4318

PM4318

11xOCTLIU or

8xOCTLIU

SBI

TEMAP-84

PM5366

T1/E1 VT/TU Mapper

Telecom Bus

Cross Connect

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 8

PRELIMINARY

PM4318 OCTLIU

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

5 BLOCK DIAGRAM

Figure 5 – OCTLIU Block Diagram – LIUs Enabled

REFCLK

AC1FP

TDN[8:1]

TDP[8:1]

TCLK[8:1]

ADATA[7:0]

ADP

EXSBI-8

XIBC

Generator

back Code

Inband Loop-

XPDE

Enforcer

Pulse Density

APL

SBI Extract

AV5

DC1FP

DDATA[7:0]

DDP

DPL

C1FPOUT

PRBS

Pattern

Detector

Generator /

DV5

RDP[8:1]

RDN/RLCV[8:1]

RCLK[8:1]

DACTIVE

INSBI-8

SBI Insert

RJAT

Attenuator

Digital Jitter

-

IBCD

Detector

back Code

Inband Loop

VCLK

FBLOW

RSTB

SBI_EN

SBI2CLK

LEN1[2:0]

LEN2[2:0]

LEN3[2:0]

LEN4[2:0]

LEN5[2:0]

LEN6[2:0]

LEN7[2:0]

LEN8[2:0]

HW_ONLY

SRCODE

SRCEN

SRCCLK

SRCDO

H/W only

LIU Octant x 8

Auto-config

SRCASC

SREN

SRCLK

SRDI

SRDO

INTB

RDB

WRB

CSB

ALE

A[10:0]

D[7:0]

TRSTB

TDO

PMON

LCODE

Encoder

HDB3 Line

AMI / B8ZS /

TJAT

Attenuator

Digital Jitter

(Diagnostic

Digit al

XLPG

Transmit LIU

TXTIP1[8:1]

TXTIP2[8:1]

TXRING1[8:1]

TXRING2[8:1]

Monitor

Performance

Loopback)

PDVD

Viol. Detector

Pulse Density

(Line

Loopback)

CDRC

Clk/Data

Recovery

RLPS

Receive LIU

RXTIP[8:1]

RXRING[8:1]

JTAG uP Interface

LOS

Serial

Output

TOPS

Timi ng

Options

CSD

Clock

Synthesis /

Distribution

XCLK

RSYNC

TDI

TMS

TCK

LOS

LOS_L1

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 9

PRELIMINARY

PM4318 OCTLIU

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

Figure 6 – OCTLIU Block Diagram – SBI to Clk/Data Converter, LIUs Disabled

REFCLK

AC1FP

Store x8EDATA[8:1]

AV5

DC1FP

DDATA[7:0]

DDP

DPL

C1FPOUT

DV5

DACTIVE

INSBI-8

SBI Insert

SBI2CLK

VCLK

RSTB

SBI_EN

HW _ONLY

SRCODE

SRCEN

SRCCLK

SRCDO

H/W only

Auto-config

SRCASC

SREN

SRCLK

SRDI

SRDO

INTB

RDB

WRB

CSB

ALE

A[10:0]

D[7:0]

ADATA[7:0]

ADP

APL

EXSBI-8

SBI Extract

ELST

Elastic

TRSTB

TDO

CSD

Clock

Synthesis /

Distribution

EFP

ECLK

IFP_IN

ICLK_IN

IFP_OUT

ICLK_OUT

IDATA[8:1]

XCLK

JTAG uP Interface

TDI

TMS

TCK

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 10

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

6 DESCRIPTION

The PM4318 Octal E1/T1/J1 Line Interface Device (OCTLIU) is a monolithic integrated circuit

suitable for use in long haul and short haul T1, J1 and E1 systems with a minimum of external

circuitry. The OCTLIU is configurable via microprocessor control or SPI-compatible serial PROM

interface, allowing feature selection without changes to external wiring.

Analogue circuitry is provided to allow direct reception of long haul E1 and T1 compatible signals

with up to 36 dB cable loss (at 1.024 MHz) in E1 mode or up to 36 dB cable loss (at 772 kHz) in

T1 mode using a minimum of external components. Typically, only line protection, a transformer

and a line termination resistor are required.

The OCTLIU recovers clock and data from the line. Decoding of AMI, HDB3 and B8ZS line codes

is supported. In T1 mode, the OCTLIU also detects the presence of in-band loop back codes.

The OCTLIU supports detection of loss of signal, pulse density violation and line code violation

alarm conditions. Line code violations are accumulated for performance monitoring purposes.

Internal analogue circuitry allows direct transmission of long haul and short haul T1 and E1

compatible signals using a minimum of external components. Typically, only line protection, a

transformer and an optional line termination resistor are required. Digitally programmable pulse

shaping allows transmission of DSX-1 compatible signals up to 655 feet from the cross-connect,

E1 short haul pulses into 120 ohm twisted pair or 75 ohm coaxial cable, E1 long haul pulses into

120 ohm twisted pair as well as long haul DS-1 pulses into 100 ohm twisted pair with integrated

support for LBO filtering as required by the FCC rules. In addition, the programmable pulse

shape extending over 5-bit periods allows customization of short haul and long haul line interface

circuits to application requirements.

Each channel of the OCTLIU can generate a low jitter transmit clock from the input clock source

and also provide jitter attenuation in the receive path. A low jitter recovered T1 clock can be

routed outside the OCTLIU for network timing applications.

Serial PCM interfaces to each T1/E1 LIU allow 1.544 Mbit/s or 2.048 Mbit/s backplane

receive/backplane transmit system interfaces to be directly supported. Data may be transferred

either as dual rail line pulses or single rail DS-1/E1 data. Alternatively, the OCTLIU supports an

8-bit parallel SBI interface for interfacing to high-density framers.

The OCTLIU may be configured to operate in a mode in which the LIUs are disabled and the

device acts as a converter between the SBI interface and serial clock and data. Up to 8 serial

data streams (sharing a common clock and frame pulse) may be mapped on to the SBI bus in

this mode.

The OCTLIU may be configured, controlled and monitored via a generic 8-bit microprocessor bus

through which all internal registers are accessed. Alternatively, the device may be operated in a

‘hardware only’ mode in which no microprocessor is required. In this case, the OCTLIU reads

configuration information from an SPI-compatible serial PROM interface on power up. Multiple

OCTLIUs can be configured from a single serial PROM via a cascade interface on the OCTLIU.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 11

PRELIMINARY

PM4318 OCTLIU

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

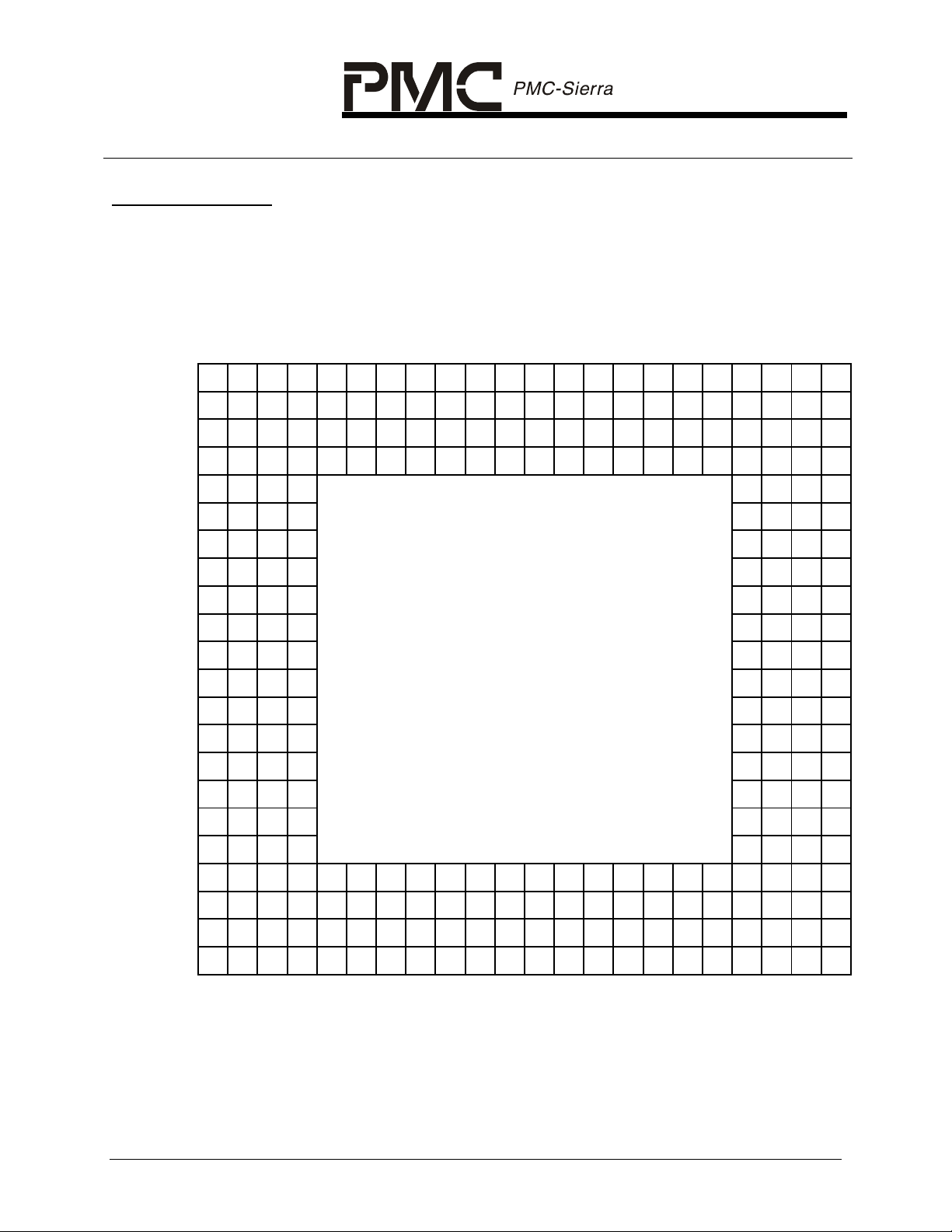

7 PIN DIAGRAM

The OCTLIU is packaged in a 288-pin Tape-SBGA package having a body size of 23mm by

23mm.

Figure 7 – Pin Diagram

22212019181716151413121110987654321

ALE/

A

LEN4[2]

B VDD3V3 VDD3V3

A[8]/

C

LEN3[2]

A[4]/

D

LEN2[1]

A[0]/

E

LEN1[0]

F RAVS1[1] RAVD2[1] QAVD[1]

G RAVD1[1] RXTIP[1] RAVS2[1] VDD3V3 RAVS2[8] RXTIP[8] RAVS1[7] TXRING1 [7] G

VSS

A[9]/

LEN4[0]

A[5]/

LEN2[2]

A[1]/

LEN1[1]

D[1]/

LEN6[2]

CSB/

LEN5[2]

A[10]/

LEN4[1]

A[6]/

LEN3[0]

A[2]/

LEN1[2]

D[2]/

LEN7[0]

LEN7[2]

D[0]/

LEN6[1]

LEN7[1]

RDB/

VDD3V3 VDD3V3 VSS

LEN5[1]

WRB/

VSS

LEN5[0]

A[7]/

LEN3[1]

A[3]/

LEN2[0]

D[4]/

VSS VDD1V8 TAVS2[1] TXRING2 [1] TXRING1 [1] TXTIP1[1] TXTIP2[1] TXTIP2 [8] TXTIP1 [8] TXRING1 [8] TXRING2 [8] RS TB LOS SRCCLK SRCLK VDD3V3 TDI A

D[3]/

D[6]/

SBI_EN QAVS[4] RES[5] TAVD3[1] TAVS3[8] TAVD2[8] QAVD[4] VDD1V8 VDD3V3 RES[1] RES[6] SRCDO SRDO SRCASC TDO HW_ONLY B

LEN8[1]

D[7]/

CAVD TAVD2[1] TAVS3[1] TAVD3[8] TAVS2[8] VSS VSS LOS_L1 SRCODE SRCEN SREN VSS TCK SBI2CLK C

LEN8[2]

INTB/

LEN6[0]

D[5]/

VSS

CAVS TAVS1[1] TAVD1[1] TAVD1[8] TAVS1[8] XCLK

LEN8[0]

RSYNC/

VDD3V3 SRDI VSS NC TMS VDD3V3 RAVS1[ 8] D

ICLK_OUT

TRSTB VSS RAVD2[8] RAVD2[7 ] E

QAVS[3] RES[4] RAVS2[7] TXRING2 [7] F

H TXRING2 [2] RAVD2[2] RAVS2[2] RXRING[1] RXRING [8] RAVD1[8] RAVD1[7] TXTIP1 [7] H

J TXRING1 [2] RXTIP[2] RAVS1[2] RXRING [2] RXRING [7] RXTIP[7] TAVS2[7] TXTIP2 [7] J

K TXTIP1[2] RAVD1[2] TAVS2[2] TAVS1[2] TAVS1[7] TAVD2[7] TAVD3[7] TXTIP2 [6] K

L TXT IP2 [2] TAVD2[2] TAVD3[2] TAV D1[2]

M TXTIP2 [3] TAVS3[2] TAVS3[3] TAVD1[3] TAVD1[6] TAVD3[6] TAVD2[6] TXRING1 [6] M

N TXTIP1 [3] TAVD3[3] TAVD2[3] TAVS1[3] TAVS1[6] TAVS2[6] RAVD1[6] TXRING2 [6] N

P TXRING1 [3] TAVS2[3] RAVD1[3] RXRING [3] RXRING [6] RAVS1[6] RAVD2[6] RXTIP[6] P

R TXRING2 [3] RXTIP[3] RAVD2[3] RXTIP[4] RXTIP[5] RXRING [5] RAVD1[5] RAVS2[6] R

T RAVS1[3] RAVS2[3] RAVD1[4] RAVS2[4] QAVD[3] RAVS2[5] RAVD2[5] RAVS1[5] T

U RXRING [4] RAVS1[4] RAVD2[4]

V RES[1] QAVS[1] VSS

TDP[1]/

W

Y

AA

AB VSS VSS VSS

TDN[1]/

ADATA[0]

REFCLK

TDN[2]/

TDP[3]/

AC1FP

ADATA[2]

TCLK[3]/

TDN[3]/

IDATA[3]

DC1FP

22212019181716151413121110987654321

TCLK[1]/

IDATA[1]

TDP[2]/

ADATA[1]

TCLK[2]/

VDD3V3 TDN[4]/ ADP VDD3V3 VDD3V3

IDATA[2]

TDP[4]/

VDD3V3

TCLK[4]/

IDATA[4]

ADATA[3]

RCLK[1]/

EDATA[1]

RDP[1]/

DDATA[0]

VSS

RCLK[2]/

EDATA[2]

RDN[1]/

RLCV[1]/

IFP_OUT

RDP[2]/

DDATA[1]

VSS VSS

RDN[2]/

RLCV[2]/

EFP

RCLK[3 ]/

EDATA[3]

RDP[3]/

DDATA[2]

RDN[3]/

RLCV[3]/

C1FPOUT

VDD3V3

RCLK[4]/

EDATA[4]

RDP[4]/

DDATA[3]

Bottom View

RDP[5]/

VSS TAVS1[4] TAVD1[4] TAVD1[5] TAVS1[5] VDD1V8

RDN[4]/

RLCV[4]/

TAVS2[4] TAVD3[4] TAVS3[5] TAVD2[5] RES[3]

DDP

VDD1V8 QAVD[2] TAVD2[4] TAVS3[4] TAVD3[5] TAVS2[5] QAVS[2] VSS VSS

TXRING2 [4] TXRING1 [4] TXTIP1[4] TXTIP2 [4] TXTIP2 [5] TXTIP1[5] TXRING1 [5] TXRING2 [5]

DDATA[4]

RDN[5]/

RLCV[5 ]/

DPL

RCLK[6 ]/

EDATA[6]

VDD3V3 VSS

RCLK[7 ]/

EDATA[7]

RCLK[5 ]/

EDATA[5]

TAVD1[7] TAVS3[7] TAVS3[6] TXTIP1[6] L

TCLK[7]/

TDN[8]/

IDATA[7]

IFP_IN

TCLK[6]/

TDN[6]/ AV5

IDATA[6]

RDP[8]/

NC VDD3V3

DDATA[7]

RDN[8]/

RDP[7]/

RLCV[8]/

DDATA[6]

RDP[6]/

DDATA[5]

RDN[6]/

RLCV[6 ]/

DV5

VSS

DACTIVE

RDN[7]/

RLCV[7]/

VDD3V3 VSS TDN[5]/ APL AA

ECLK

VDD3V3 VSS

TDP[8]/

ADATA[7]

TDN[7]/

ICLK_IN

TCLK[5]/

IDATA[5]

TDP[5]/

ADATA[4]

RCLK[8]/

EDATA[8]

VSS U

TCLK[8]/

IDATA[8]

TDP[7]/

ADATA[6]

TDP[6]/

ADATA[5]

VDD3V3 AB

V

W

Y

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 12

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

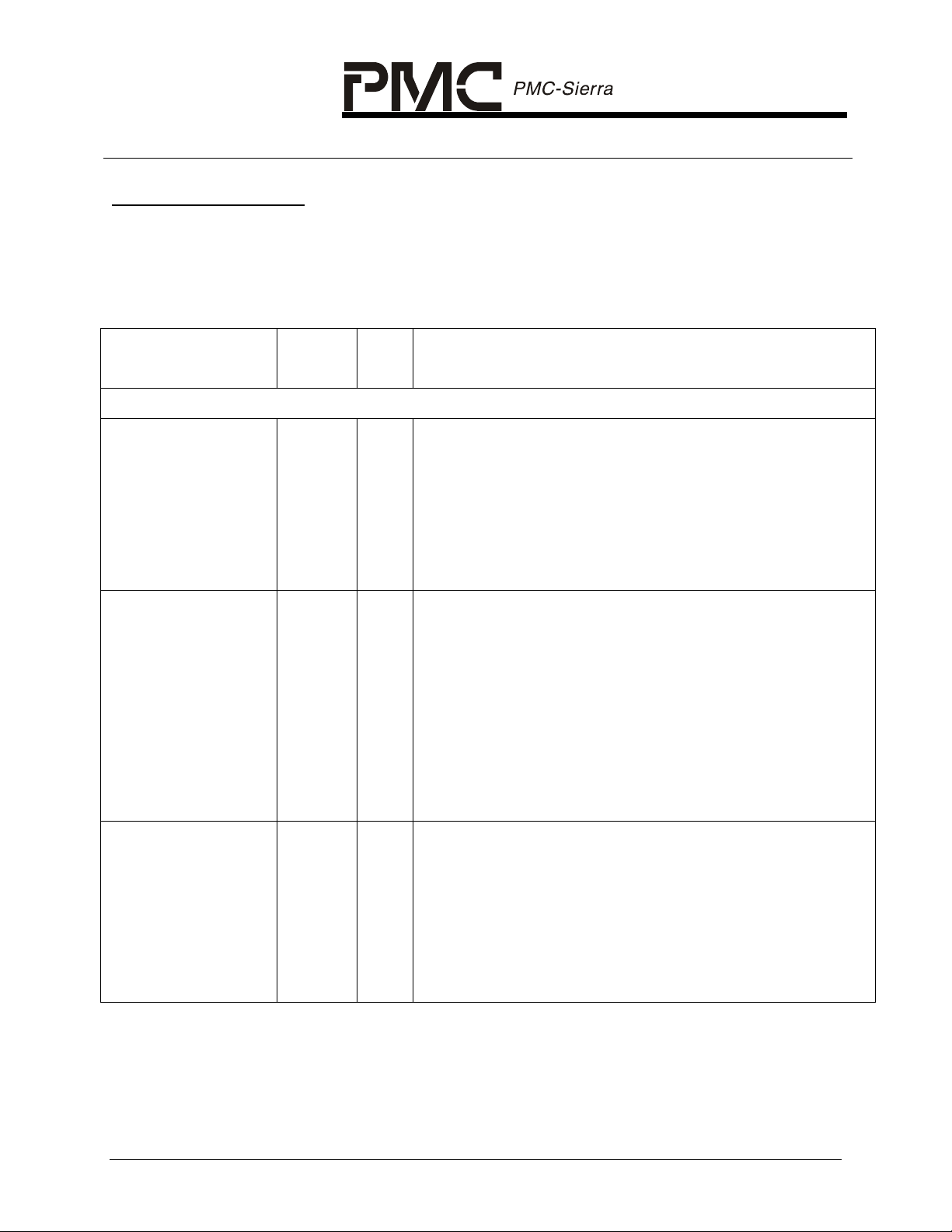

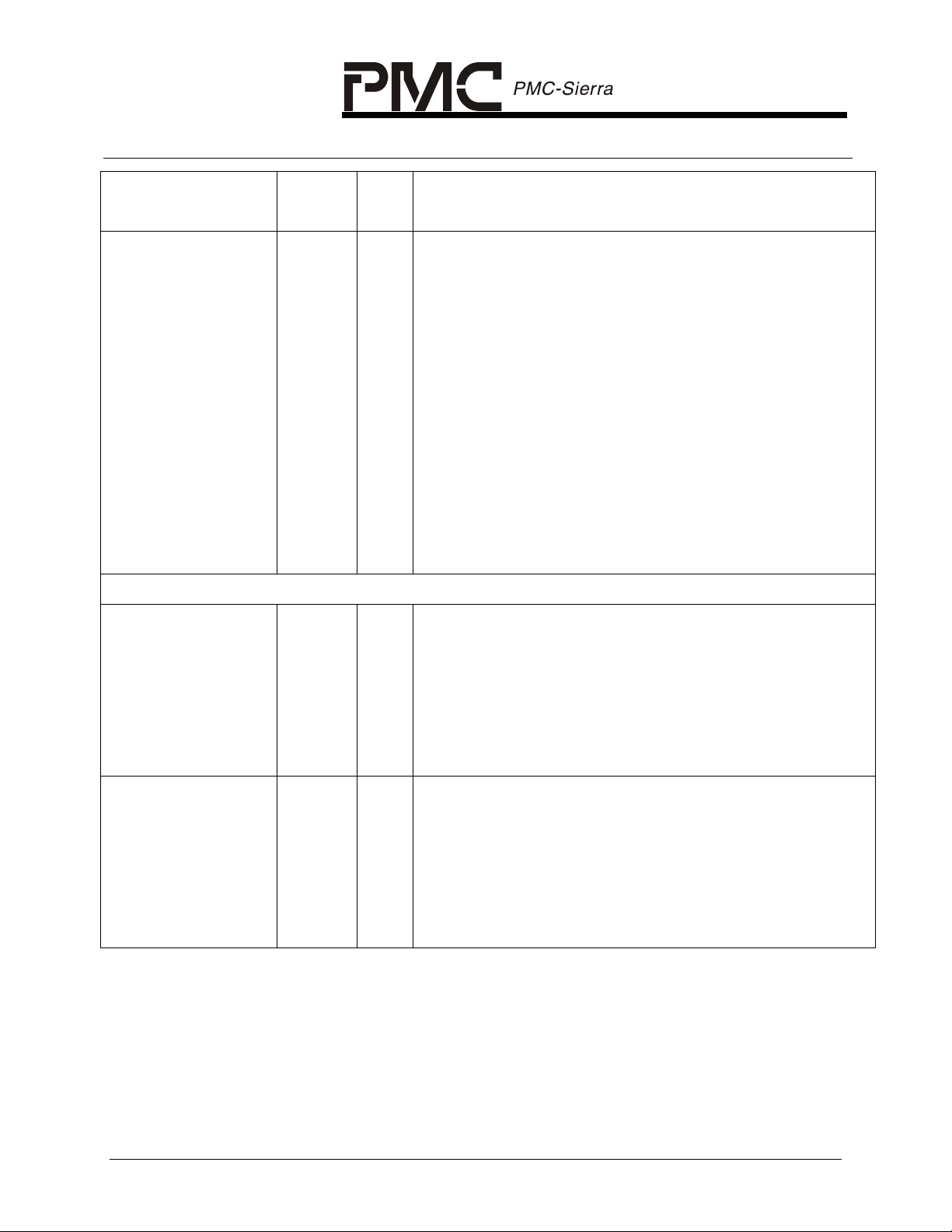

8 PIN DESCRIPTION

By convention, where a bus of eight pins indexed [8:1] is present, the index indicates to which

octant the pin applies. With TCLK[8:1], for example, TCLK[1] applies to octant #1, TCLK[2]

applies to octant #2, etc.

Pin Name Type Pin

Function

No.

T1 and E1 System Side Serial Clock and Data Interface

TCLK[1]/IDATA[1]

TCLK[2]/IDATA[2]

TCLK[3]/IDATA[3]

TCLK[4]/IDATA[4]

TCLK[5]/IDATA[5]

TCLK[6]/IDATA[6]

TCLK[7]/IDATA[7]

TCLK[8]/IDATA[8]

TDP[1]/ADATA[0]

TDP[2]/ADATA[1]

TDP[3]/ADATA[2]

TDP[4]/ADATA[3]

TDP[5]/ADATA[4]

TDP[6]/ADATA[5]

TDP[7]/ADATA[6]

TDP[8]/ADATA[7]

Input U19

W20

AA22

AA20

W2

V3

U4

V1

Input W22

V19

Y21

Y19

Y2

Y1

W1

U2

The Transmit Clock inputs (TCLK[8:1]) should be 1.544 MHz for

DS1 or 2.048 MHz for E1 data streams and are used to sample

the corresponding TDP[8:1] and TDN[8:1] signals.

TCLK[8:1] share the same pins as the IDATA[8:1] inputs.

TCLK[8:1] are selected when SBI2CLK is tied low.

Transmit Positive Data (TDP[8:1]). When in single-rail mode,

these inputs are the NRZ data signals to be transmitted. These

inputs can be configured to be active high or active low. When in

dual-rail mode, these inputs are the NRZ positive data signals to

be transmitted.

TDP[8:1] can be sampled on either the rising or falling edges of

the corresponding TCLK[8:1].

TDP[8:1] share the same pins as the ADATA[7:0] inputs.

TDP[8:1] are selected when SBI_EN and SBI2CLK are both tied

low.

TDN[1]/REFCLK

TDN[2]/AC1FP

TDN[3]/DC1FP

TDN[4]/ADP

TDN[5]/APL

TDN[6]/AV5

TDN[7]/ICLK_IN

TDN[8]/IFP_IN

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 13

Input W21

Y22

AA21

W18

AA1

V4

V2

U3

Transmit Negative Data (TDN[8:1]). When in dual-rail mode,

these inputs are the NRZ negative data signals to be transmitted.

These inputs can be sampled on either the rising or falling edges

of the corresponding TCLK[8:1]. These input pins are ignored if

the device is configured for single-rail (unipolar) transmit mode.

TDN[8:1] share the same pins as the REFCLK, AC1FP, DC1FP,

ADP, APL, AV5, ICLK_IN and IFP_IN inputs. TDN[8:1] are

selected when SBI_EN and SBI2CLK are both tied low.

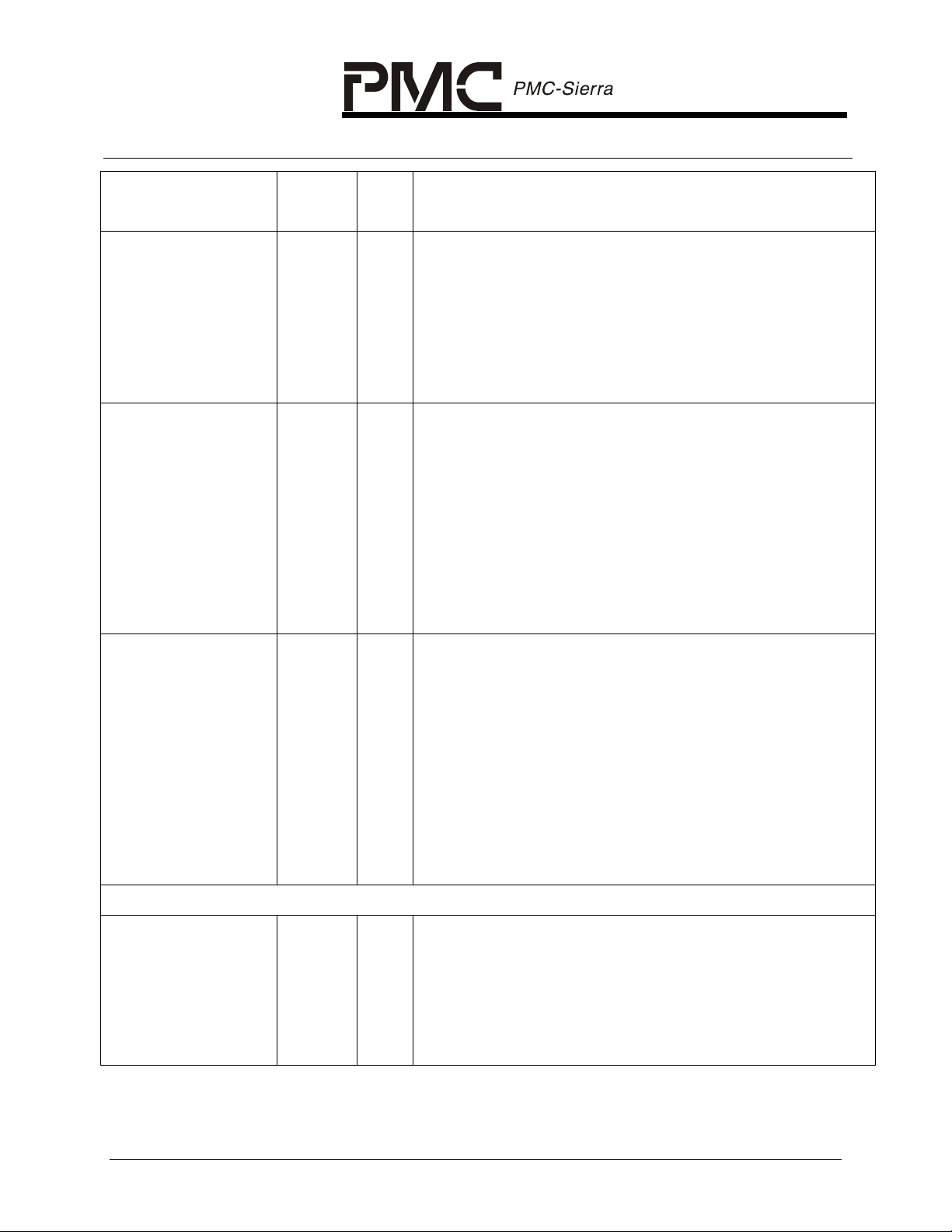

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

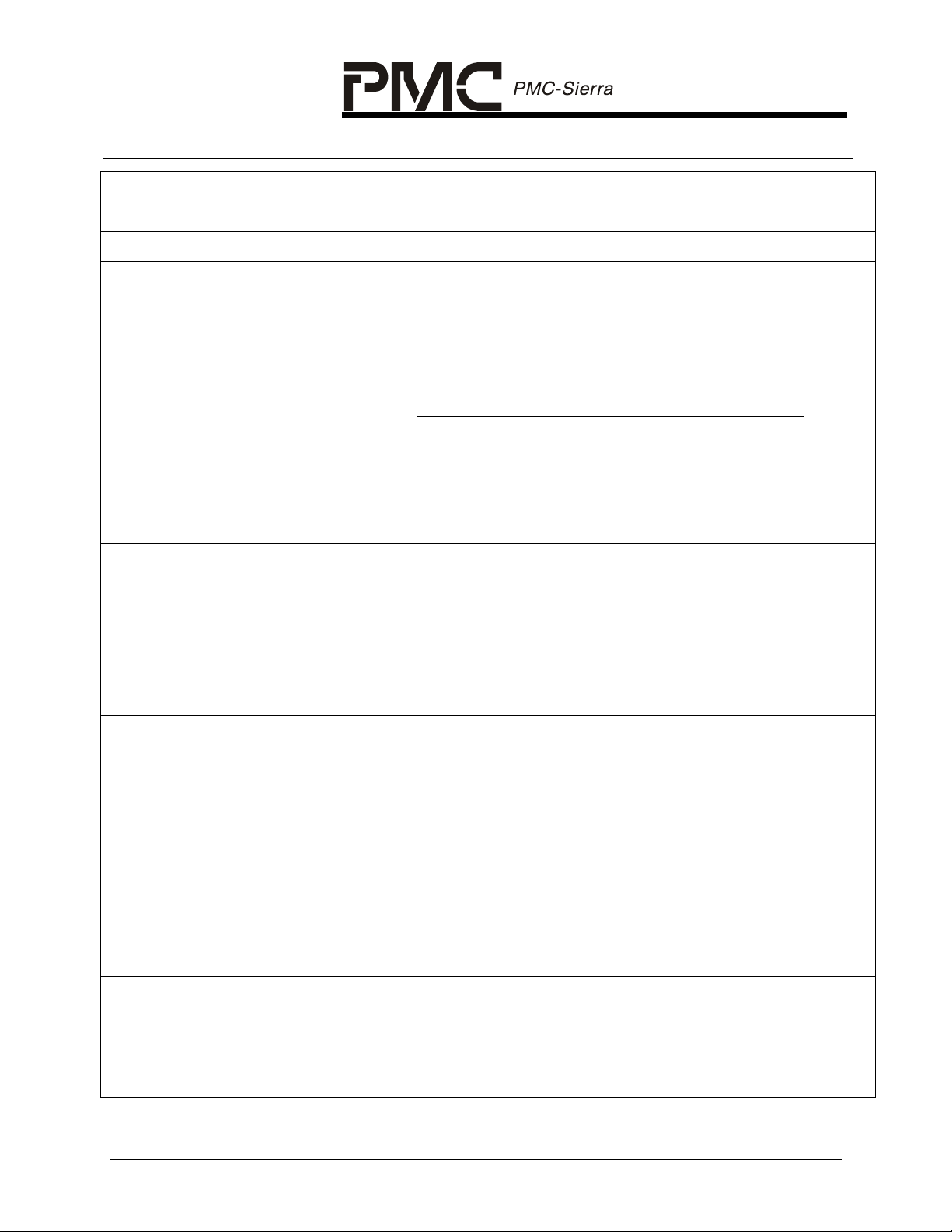

Pin Name Type Pin

No.

RCLK[1]/EDATA[1]

RCLK[2]/EDATA[2]

RCLK[3]/EDATA[3]

RCLK[4]/EDATA[4]

RCLK[5]/EDATA[5]

RCLK[6]/EDATA[6]

RCLK[7]/EDATA[7]

RCLK[8]/EDATA[8]

RDP[1]/DDATA[0]

RDP[2]/DDATA[1]

RDP[3]/DDATA[2]

RDP[4]/DDATA[3]

RDP[5]/DDATA[4]

RDP[6]/DDATA[5]

RDP[7]/DDATA[6]

RDP[8]/DDATA[7]

Output AA19

AA18

Y16

AA15

AB6

W7

W6

AB2

Output AB19

Y17

AB16

AB15

W8

AA5

Y5

W5

Function

Recovered Clock Output (RCLK[8:1]). RCLK[8:1] is the clock

recovered from the RXTIP[8:1] and RXRING[8:1] input signals.

RCLK[8:1] share the same pins as the EDATA[8:1] outputs.

RCLK[8:1] are selected when SBI2CLK is tied low.

Receive Digital Positive Data (RDP[8:1]). When in single rail

mode, RDP[8:1] output NRZ sampled DS-1 or E1 data which has

been decoded by AMI, B8ZS, or HDB3 line code rules. When in

dual rail mode, RDP[8:1] output NRZ sampled bipolar positive

pulses.

RDP[8:1] can be updated on either the falling or rising RCLK[8:1]

edge.

RDP[8:1] share the same pins as the DDATA[7:0] outputs.

RDP[8:1] are selected when SBI_EN and SBI2CLK are both tied

low.

RDN/RLCV[1]/IFP_OUT

RDN/RLCV[2]/EFP

RDN/RLCV[3]/C1FPOUT

RDN/RLCV[4]/DDP

RDN/RLCV[5]/DPL

RDN/RLCV[6]/DV5

RDN/RLCV[7]/ECLK

RDN/RLCV[8]/DACTIVE

Output AB18

AB17

W15

Y14

Y8

AB5

AA4

Y4

Receive Digital Negative Data/Line Code Violation Indication

(RDN/RLCV[8:1]). When in dual rail mode, RDN/RLCV[8:1]

output NRZ sampled bipolar negative pulses. When in single rail

mode, RDN/RLCV[8:1] output a NRZ pulse whenever a line code

violation or excess zeros condition is detected.

RDN/RLCV[8:1] can be updated on either the falling or rising

RCLK[8:1] edge.

RDN/RLCV[8:1] share the same pins as the IFP_OUT, EFP,

C1FPOUT, DDP, DPL, DV5, ECLK and DACTIVE outputs.

RDN/RLCV[8:1] are selected when SBI_EN and SBI2CLK are

both tied low.

SBI System Side Interface

REFCLK/TDN[1] Input W21 The SBI reference clock signal (REFCLK) provides reference

timing for the SBI ADD and DROP busses.

REFCLK is nominally a 50% duty cycle clock of frequency 19.44

MHz ±50ppm.

REFCLK shares the same pin as the TDN[1] input. REFCLK is

selected when SBI_EN or SBI2CLK is tied high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 14

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

Pin Name Type Pin

Function

No.

AC1FP/TDN[2] Input Y22 The SBI ADD bus C1 octet frame pulse signal (AC1FP) provides

frame synchronisation for devices connected via an SBI interface.

AC1FP must be asserted for 1 REFCLK cycle every 500 µs or

multiples thereof (i.e. every 9720 n REFCLK cycles, where n is a

positive integer). All devices connected to the SBI ADD bus must

be synchronised to a AC1FP signal from a single source.

AC1FP is sampled on the rising edge of REFCLK.

AC1FP shares the same pin as the TDN[2] input. AC1FP is

selected when SBI_EN or SBI2CLK is tied high.

DC1FP/TDN[3] Input AA21 The SBI DROP bus C1 octet frame pulse signal (DC1FP)

provides frame synchronisation for devices connected via an SBI

interface. DC1FP must be asserted for 1 REFCLK cycle every

500 µs or multiples thereof (i.e. every 9720 n REFCLK cycles,

where n is a positive integer). All devices connected to the SBI

DROP bus must be synchronised to a DC1FP signal from a single

source.

DC1FP is sampled on the rising edge of REFCLK.

DC1FP shares the same pin as the TDN[3] input. DC1FP is

selected when SBI_EN or SBI2CLK is tied high.

C1FPOUT/RDN/RLCV[3]

ADATA[0]/TDP[1]

ADATA[1]/TDP[2]

ADATA[2]/TDP[3]

ADATA[3]/TDP[4]

ADATA[4]/TDP[5]

ADATA[5]/TDP[6]

ADATA[6]/TDP[7]

ADATA[7]/TDP[8]

Output W15 The C1 octet frame pulse output signal (C1FPOUT) may be used

to provide frame synchronisation for devices interconnected via

an SBI interface. C1FPOUT is asserted for 1 REFCLK cycle

every 500 µs (i.e. every 9720 REFCLK cycles). If C1FPOUT is

used for synchronisation, it must be connected to the A/DC1FP

inputs of all the devices connected to the SBI ADD or DROP bus.

C1FPOUT is updated on the rising edge of REFCLK.

C1FPOUT shares the same pin as the RDN/RLCV[3] output.

C1FPOUT is selected when SBI_EN or SBI2CLK is tied high.

Input W22

V19

Y21

Y19

Y2

Y1

W1

U2

The SBI ADD bus data signals (ADATA[7:0]) contain time division

multiplexed transmit data from up to 84 independently timed links.

Link data is transported as T1 or E1 tributaries within the SBI

TDM bus structure. The OCTLIU may be configured to extract

data from up to 8 tributaries within the structure.

ADATA[7:0] are sampled on the rising edge of REFCLK.

ADATA[7:0] share the same pins as the TDP[8:1] inputs.

ADATA[7:0] are selected when SBI_EN or SBI2CLK is tied high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 15

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

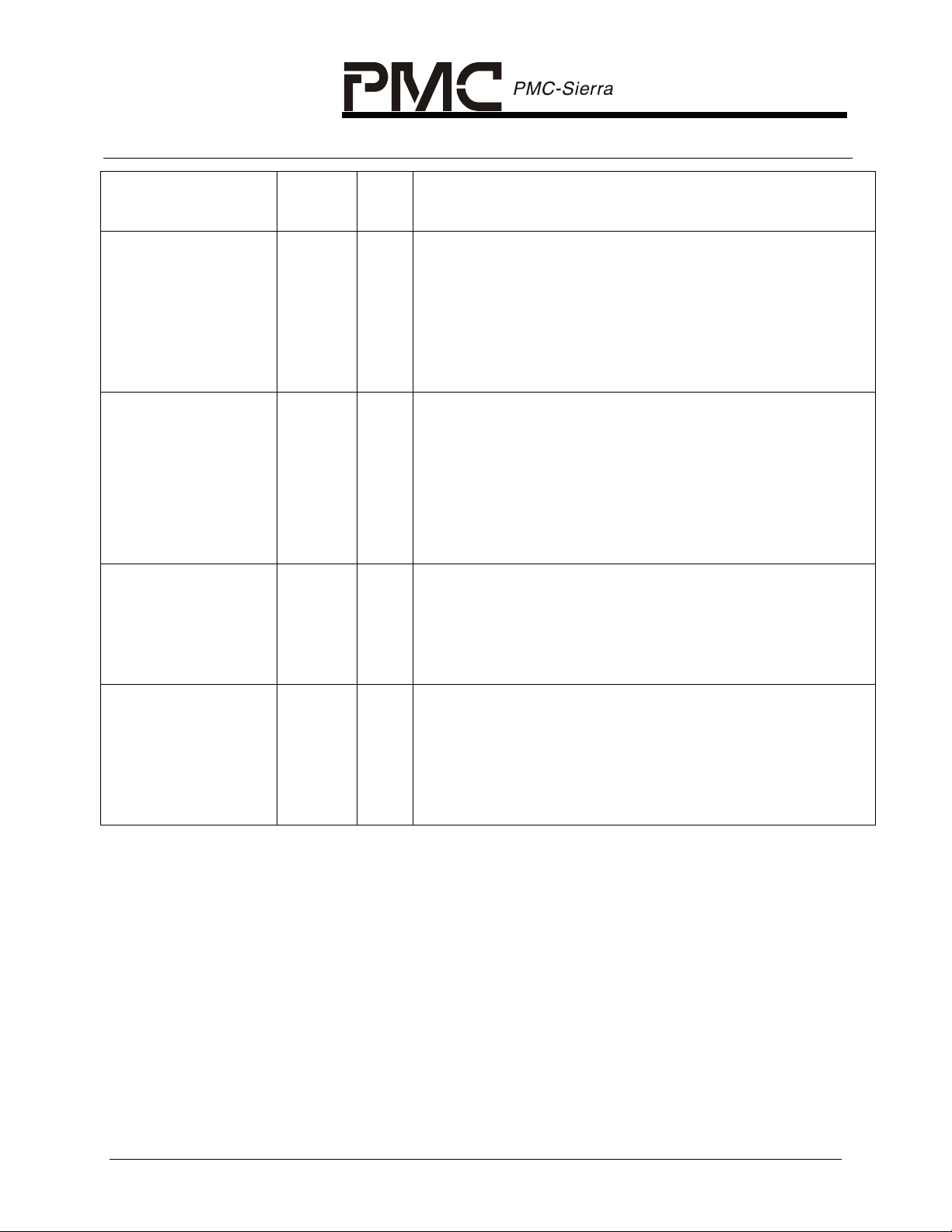

Pin Name Type Pin

Function

No.

ADP/TDN[4] Input W18 The SBI ADD bus parity signal (ADP) carries the even or odd

parity for the ADD bus signals. The parity calculation

encompasses the ADATA[7:0], APL and AV5 signals.

Multiple devices can drive the SBI ADD bus at uniquely assigned

tributary column positions. This parity signal is intended to detect

accidental driver clashes in the column assignment.

ADP is sampled on the rising edge of REFCLK.

ADP shares the same pin as the TDN[4] input. ADP is selected

when SBI_EN or SBI2CLK is tied high.

APL/TDN[5] Input AA1 The SBI ADD bus payload signal (APL) indicates valid data within

the SBI TDM bus structure. This signal is asserted during all

octets making up a tributary. This signal may be asserted during

the V3 octet within a tributary to accommodate negative timing

adjustments between the tributary rate and the fixed TDM bus

structure. This signal may be deasserted during the octet

following the V3 octet within a tributary to accommodate positive

timing adjustments between the tributary rate and the fixed TDM

bus structure.

APL is sampled on the rising edge of REFCLK.

APL shares the same pin as the TDN[5] input. APL is selected

when SBI_EN or SBI2CLK is tied high.

AV5/TDN[6] Input V4 The SBI ADD bus payload indicator signal (AV5) locates the

position of the floating payloads for each tributary within the SBI

TDM bus structure. Timing differences between the port timing

and the TDM bus timing are indicated by adjustments of this

payload indicator relative to the fixed TDM bus structure. All

movements indicated by this signal must be accompanied by

appropriate adjustments in the APL signal.

AV5 is sampled on the rising edge of REFCLK.

AV5 shares the same pin as the TDN[6] input. AV5 is selected

when SBI_EN or SBI2CLK is tied high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 16

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

Pin Name Type Pin

No.

DDATA[0]/RDP[1]

DDATA[1]/RDP[2]

DDATA[2]/RDP[3]

DDATA[3]/RDP[4]

DDATA[4]/RDP[5]

DDATA[5]/RDP[6]

DDATA[6]/RDP[7]

DDATA[7]/RDP[8]

DDP/RDN/RLCV[4] Tristate

Tristate

Output

AB19

Y17

AB16

AB15

W8

AA5

Y5

W5

Y14 The SBI DROP bus parity signal (DDP) carries the even or odd

Output

Function

The SBI DROP bus data signals (DDATA[7:0]) contain time

division multiplexed receive data from up to 84 independently

timed links. Link data is transported as T1 or E1 tributaries within

the SBI TDM bus structure. The OCTLIU may be configured to

insert data into up to 8 tributaries within the structure. Multiple

LIU devices can drive the SBI DROP bus at uniquely assigned

tributary column positions. DDATA[7:0] are tristated when the

OCTLIU is not outputting data on a particular tributary column.

DDATA[7:0] are updated on the rising edge of REFCLK.

DDATA[7:0] share the same pins as the RDP[8:1] outputs.

DDATA[7:0] are selected when SBI_EN or SBI2CLK is tied high.

parity for the DROP bus signals. The parity calculation

encompasses the DDATA[7:0], DPL and DV5 signals.

Multiple LIU devices can drive this signal at uniquely assigned

tributary column positions. DDP is tristated when the OCTLIU is

not outputting data on a particular tributary column. This parity

signal is intended to detect accidental source clashes in the

column assignment.

DPL/RDN/RLCV[5] Tristate

Output

DDP is updated on the rising edge of REFCLK.

DDP shares the same pin as the RDN/RLCV[4] output. DDP is

selected when SBI_EN or SBI2CLK is tied high.

Y8 The SBI DROP bus payload signal (DPL) indicates valid data

within the SBI TDM bus structure. This signal is asserted during

all octets making up a tributary. This signal may be asserted

during the V3 octet within a tributary to accommodate negative

timing adjustments between the tributary rate and the fixed TDM

bus structure. This signal may be deasserted during the octet

following the V3 octet within a tributary to accommodate positive

timing adjustments between the tributary rate and the fixed TDM

bus structure.

Multiple LIU devices can drive this signal at uniquely assigned

tributary column positions. DPL is tristated when the OCTLIU is

not outputting data on a particular tributary column.

DPL is updated on the rising edge of REFCLK.

DPL shares the same pin as the RDN/RLCV[5] output. DPL is

selected when SBI_EN or SBI2CLK is tied high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 17

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

Pin Name Type Pin

No.

DV5/RDN/RLCV[6] Tristate

AB5 The SBI DROP bus payload indicator signal (DV5) locates the

output

DACTIVE/RDN/RLCV[8]

Output Y4 The SBI DROP bus active indicator signal (DACTIVE) is asserted

Function

position of the floating payloads for each tributary within the SBI

TDM bus structure. Timing differences between the port timing

and the TDM bus timing are indicated by adjustments of this

payload indicator relative to the fixed TDM bus structure.

Multiple LIU devices can drive this signal at uniquely assigned

tributary column positions. DV5 is tristated when the OCTLIU is

not outputting data on a particular tributary column.

DV5 is updated on the rising edge of REFCLK.

DV5 shares the same pin as the RDN/RLCV[6] output. DV5 is

selected when SBI_EN or SBI2CLK is tied high.

whenever the OCTLIU is driving the SBI DROP bus signals,

DDATA[7:0], DDP, DPL and DV5.

DACTIVE is updated on the rising edge of REFCLK.

DACTIVE shares the same pin as the RDN/RLCV[8] output.

DACTIVE is selected when SBI_EN or SBI2CLK is tied high.

Transmit Line Interface

TXTIP1[1]

TXTIP1[2]

TXTIP1[3]

TXTIP1[4]

TXTIP1[5]

TXTIP1[6]

TXTIP1[7]

TXTIP1[8]

TXTIP2[1]

TXTIP2[2]

TXTIP2[3]

TXTIP2[4]

TXTIP2[5]

TXTIP2[6]

TXTIP2[7]

TXTIP2[8]

Analogue

Output

A12

K22

N22

AB12

AB9

L1

H1

A9

A11

L22

M22

AB11

AB10

K1

J1

A10

Transmit Analogue Positive Pulse (TXTIP1[8:1] and TXTIP2[8:1]).

When the transmit analogue line interface is enabled, the

TXTIP1[x] and TXTIP2[x] analogue outputs drive the transmit line

pulse signal through an external matching transformer. Both

TXTIP1[x] and TXTIP2[x] are normally connected to the positive

lead of the transformer primary. Two outputs are provided for

better signal integrity and must be shorted together on the board.

After a reset, TXTIP1[x] and TXTIP2[x] are high impedance. The

HIGHZ bit of the octant’s XLPG Line Driver Configuration register

must be programmed to logic 0 to remove the high impedance

state.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 18

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

Pin Name Type Pin

No.

TXRING1[1]

TXRING1[2]

TXRING1[3]

TXRING1[4]

TXRING1[5]

TXRING1[6]

TXRING1[7]

TXRING1[8]

TXRING2[1]

TXRING2[2]

TXRING2[3]

TXRING2[4]

TXRING2[5]

TXRING2[6]

TXRING2[7]

TXRING2[8]

Analogue

Output

A13

J22

P22

AB13

AB8

M1

G1

A8

A14

H22

R22

AB14

AB7

N1

F1

A7

Receive Line Interface

RXTIP[1]

RXTIP[2]

RXTIP[3]

RXTIP[4]

RXTIP[5]

RXTIP[6]

RXTIP[7]

RXTIP[8]

Analogue

Input

G21

J21

R21

R19

R4

P1

J3

G3

Function

Transmit Analogue Negative Pulse (TXRING1[8:1] and

TXRING2[8:1]). When the transmit analogue line interface is

enabled, the TXRING1[x] and TXRING2[x] analogue outputs drive

the transmit line pulse signal through an external matching

transformer. Both TXRING1[x] and TXRING2[x] are normally

connected to the negative lead of the transformer primary. Two

outputs are provided for better signal integrity and must be

shorted together on the board.

After a reset, TXRING1[x] and TXRING2[x] are high impedance.

The HIGHZ bit of the octant’s XLPG Line Driver Configuration

register must be programmed to logic 0 to remove the high

impedance state.

Receive Analogue Positive Pulse (RXTIP[8:1]). When the

analogue receive line interface is enabled, RXTIP[x] samples the

received line pulse signal from an external isolation transformer.

RXTIP[x] is normally connected directly to the positive lead of the

receive transformer secondary.

RXRING[1]

RXRING[2]

RXRING[3]

RXRING[4]

RXRING[5]

RXRING[6]

RXRING[7]

RXRING[8]

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 19

Analogue

Input

H19

J19

P19

U22

R3

P4

J4

H4

Receive Analogue Negative Pulse (RXRING[8:1]). When the

analogue receive line interface is enabled, RXRING[x] samples

the received line pulse signal from an external isolation

transformer. RXRING[x] is normally connected directly to the

negative lead of the receive transformer secondary.

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

Pin Name Type Pin

No.

SBI to Clk/Data Converter Interface

SBI_EN

Input B16C1The SBI interface enable signals (SBI_EN, SBI2CLK) select

SBI2CLK

IDATA[1]/TCLK[1]

IDATA[2]/TCLK[2]

IDATA[3]/TCLK[3]

IDATA[4]/TCLK[4]

IDATA[5]/TCLK[5]

IDATA[6]/TCLK[6]

IDATA[7]/TCLK[7]

IDATA[8]/TCLK[8]

Input U19

W20

AA22

AA20

W2

V3

U4

V1

Function

between the SBI and serial clock/data system side interfaces and

allow selection of an operating mode in which the LIUs are

disabled and the OCTLIU functions as a converter between the

SBI interface and serial clk/data. The signals select the device

operating mode as follows:

SBI_EN SBI2CLK Mode

0 0 LIUs enabled, clk/data selected on system

side.

1 0 LIUs enabled, SBI interface selected on

system side.

0 1 LIUs disabled, converter mode.

1 1 Unused

The Ingress Data inputs (IDATA[8:1]) carry eight serial 1.544

Mbps or 2.048 Mbps data streams to be mapped on to the SBI

interface when the device is operating as a SBI to clk/data

converter. The eight serial data streams are sampled on the

rising edge of ICLK_IN.

IDATA[8:1] share the same pins as the TCLK[8:1] inputs.

IDATA[8:1] are selected when SBI2CLK is tied high.

ICLK_IN/TDN[7] Input V2 The Ingress Input Clock (ICLK_IN) should be 1.544 MHz for DS1

or 2.048 MHz for E1 data streams and is used to sample the

IDATA[8:1] and IFP_IN signals.

ICLK_IN shares the same pin as the TDN[7] input. ICLK_IN is

selected when SBI_EN or SBI2CLK is tied high.

IFP_IN/TDN[8] Input U3 The Ingress Frame Pulse input (IFP_IN) should be set high

during the framing bits of DS1 streams or during the first bit of the

framing octet of E1 data streams. IFP_IN is sampled on the

rising edge of ICLK_IN.

IFP_IN shares the same pin as the TDN[8] input. IFP_IN is

selected when SBI_EN or SBI2CLK is tied high.

ICLK_OUT/RSYNC Output D8 The Ingress Output Clock (ICLK_OUT) is a nominal 1.544 MHz

(for DS1) or 2.048 MHz (for E1) clock and may be used as a

source for the ICLK_IN clock if desired.

ICLK_OUT shares the same pin as the RSYNC output.

ICLK_OUT is selected when SBI2CLK is tied high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 20

PRELIMINARY

DATASHEET

PMC- 2001578 ISSUE 3 OCTAL E1/T1/J1 LINE INTERFACE DEVICE

PM4318 OCTLIU

Pin Name Type Pin

Function

No.

IFP_OUT/RDN/RLCV[1]

Output AB18 The Ingress Frame Pulse output (IFP_OUT) is pulsed high every

193 ICLK_OUT cycles for DS1 and every 256 ICLK_OUT cycles

for E1. It may be used as a framing reference and as a source

for IFP_IN if desired. IFP_OUT is updated on the falling edge of

ICLK_OUT.

IFP_OUT shares the same pin as the RDN/RLCV[1] output.

IFP_OUT is selected when SBI_EN or SBI2CLK is tied high.

EDATA[1]/RCLK[1]

EDATA[2]/RCLK[2]

EDATA[3]/RCLK[3]

EDATA[4]/RCLK[4]

EDATA[5]/RCLK[5]

EDATA[6]/RCLK[6]

EDATA[7]/RCLK[7]

EDATA[8]/RCLK[8]

Output AA19

AA18

Y16

AA15

AB6

W7

W6

AB2

The Egress Data outputs (EDATA[8:1]) carry eight serial 1.544

Mbps or 2.048 Mbps data streams de-mapped from the SBI

interface when the device is operating as a SBI to clk/data

converter. The eight serial data streams are updated on the

falling edge of ECLK.

EDATA[8:1] share the same pins as the RCLK[8:1] outputs.

EDATA[8:1] are selected when SBI2CLK is tied high.

ECLK/RDN/RLCV[7] Output AA4 The Egress Clock output (ECLK) is a 1.544 MHz (for DS1) or

2.048 MHz (for E1) clock, recovered from one of the SBI

tributaries. The SBI tributary used to recover timing is selectable.

ECLK shares the same pin as the RDN/RLCV[7] output. ECLK is

selected when SBI_EN or SBI2CLK is tied high.

EFP/RDN/RLCV[2] Output AB17 The Egress Frame Pulse output (EFP) is set high during the

framing bits of DS1 streams or during the first bit of the framing

octet of E1 data streams. EFP is updated on the falling edge of

ECLK.

EFP shares the same pin as the RDN/RLCV[2] output. EFP is

selected when SBI_EN or SBI2CLK is tied high.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE 21

Loading...

Loading...