PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

PM4314

QDSX

QUAD T1/E1 LINE INTERFACE DEVICE

DATA SHEET

ISSUE 5: JUNE 1998

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

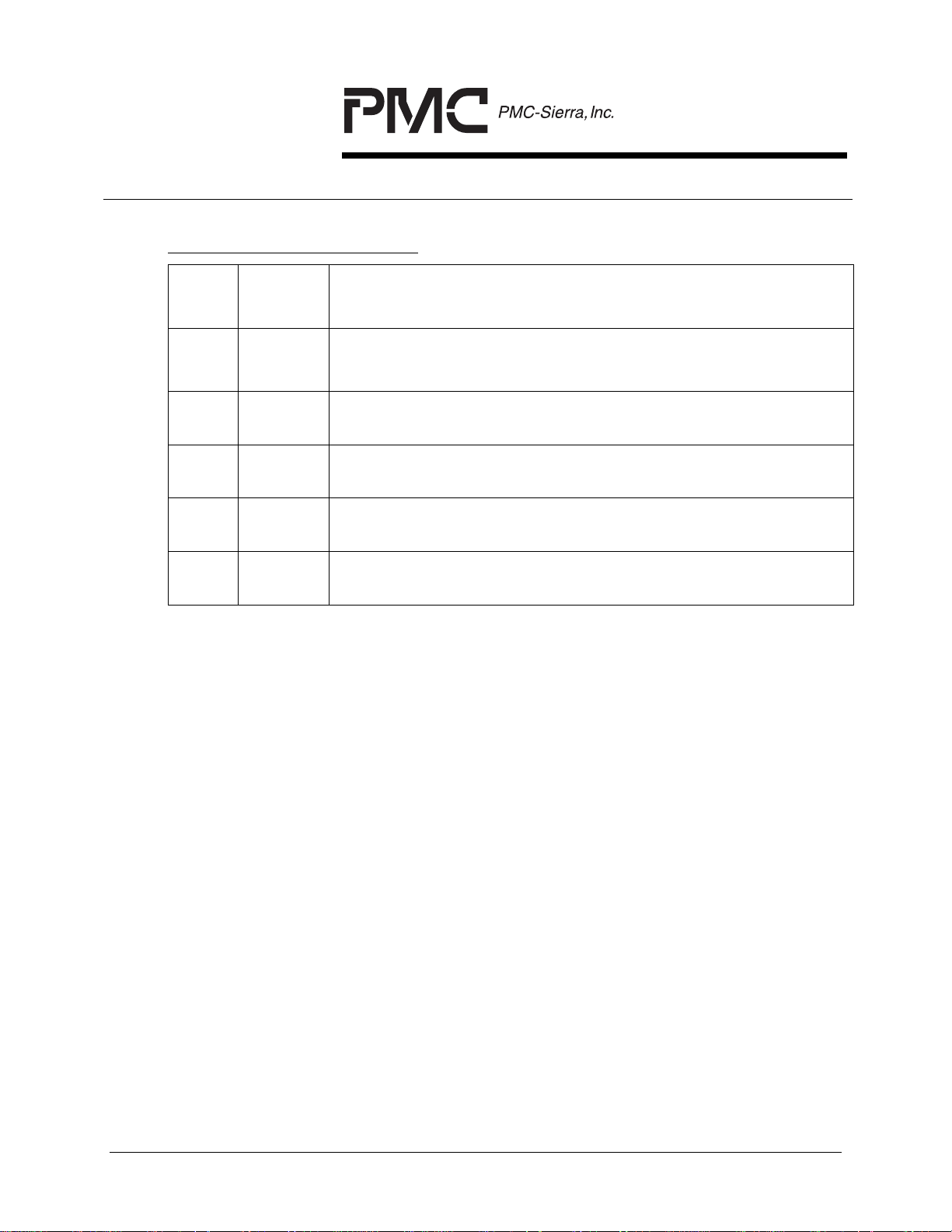

PUBLIC REVISION HISTORY

Issue

No.

Issue

Date

5 June,

1998

4 January,

1997

3 March,

1996

2 January,

1996

1 August,

1995

Details of Change

Data Sheet Reformatted — No Change in Technical Content

Generated R5 data sheet from PMC-950739, R4

Eng Doc Issue R3 released

Public release of document: removal of confidential notices

Upgrade to Eng Doc Issue P2

Creation of Document

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................5

3 REFERENCES.........................................................................................6

4 APPLICATION EXAMPLES......................................................................8

5 BLOCK DIAGRAM..................................................................................13

6 DESCRIPTION.......................................................................................15

7 PIN DIAGRAM........................................................................................18

8 PIN DESCRIPTION................................................................................19

9 FUNCTIONAL DESCRIPTION...............................................................32

9.1 ANALOG PULSE SLICER (RSLC) ..............................................32

9.2 CLOCK AND DATA RECOVERY (CDRC)....................................35

9.3 LINE CODE VIOLATION PERFORMANCE MONITOR

(LCV_PMON)...............................................................................39

9.4 INBAND LOOPBACK CODE DETECTOR (IBCD).......................40

9.5 PSEUDO-RANDOM BIT SEQUENCE MONITOR (PRSM)..........40

9.6 TIMING OPTIONS (TOPS)..........................................................42

9.7 PSEUDO-RANDOM BIT SEQUENCE GENERATOR (PRSG).....42

9.8 INBAND LOOPBACK CODE GENERATOR (XIBC).....................43

9.9 B8ZS/HDB3/AMI LINE ENCODER (LCODE) ..............................43

9.10 DIGITAL JITTER ATTENUATOR (DJAT).......................................43

9.11 ANALOG PULSE GENERATOR (XPLS)......................................49

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

9.12 IEEE P1149.1 JTAG TEST ACCESS PORT................................52

9.13 MICROPROCESSOR INTERFACE.............................................52

9.14 REGISTER MEMORY MAP.........................................................53

10 NORMAL MODE REGISTER DESCRIPTION........................................56

11 TEST FEATURES DESCRIPTION .......................................................113

11.1 TEST MODE 0 DETAILS...........................................................114

11.2 JTAG TEST PORT......................................................................116

12 OPERATIONS.......................................................................................119

12.1 PROGRAMMING THE XPLS WA VEFORM TEMPLATE ............122

12.2 USING THE DIGITAL JITTER ATTENUATOR............................127

12.3 USING XPLS WITHOUT DJAT ..................................................128

12.3.1FIFO NOT IN TX PATH, XSEL[1] = 0...............................129

12.3.2FIFO NOT IN TX PATH, XSEL[1] = 1, XSEL[0] = 0..........129

12.3.3FIFO IS IN TX PATH, XSEL[1] = 1, XSEL[0] = 0.............129

12.3.4FIFO NOT IN TX PATH, XSEL[1] = 1, XSEL[0] = 1..........129

12.3.5FIFO IS IN TX PATH, XSEL[1] = 1, XSEL[0] = 1..............130

12.4 JTAG SUPPORT........................................................................130

13 FUNCTIONAL TIMING .........................................................................141

13.1 LINE CODE VIOLATION INSERTION.......................................141

14 ABSOLUTE MAXIMUM RATINGS........................................................144

15 CAPACITANCE.....................................................................................145

16 D.C. CHARACTERISTICS ....................................................................146

17 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS......149

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

18 A.C. TIMING CHARACTERISTICS.......................................................153

19 ORDERING AND THERMAL INFORMATION ......................................163

20 MECHANICAL INFORMATION.............................................................164

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

LIST OF REGISTERS

REGISTER 000H, 040H, 080H, AND 0C0H: RECEIVE CONFIGURATION......57

REGISTER 001H, 041H, 081H, AND 0C1H: TRANSMIT CONFIGURATION...60

REGISTER 002H, 042H, 082H, AND 0C2H: TX/RX BLOCK PLACEMENT...... 62

REGISTER 003H, 043H, 083H, AND 0C3H: INTERRUPT SOURCE...............64

REGISTER 005H, 045H, 085H, AND 0C5H: DIAGNOSTICS...........................65

REGISTER 006H OR 106H: MASTER TEST....................................................67

REGISTER 007H: REVISION/CHIP ID/GLOBAL MONITORING UPDATE .......70

REGISTER 008H: INTERRUPT QUADRANT ID...............................................71

REGISTER 009H: TOPS MASTER CLOCK CONFIGURATION/CLOCK

ACTIVITY MONITOR..............................................................................72

REGISTER 00AH, 04AH, 08AH, AND 0CAH: TOPS CLOCK TIMING OPTIONS

................................................................................................................74

REGISTER 00BH, 04BH, 08BH, AND 0CBH: LCODE TRANSMIT LINE CODE

CONFIGURATION..................................................................................76

REGISTER 010H, 050H, 090H, AND 0D0H: CDRC CONFIGURATION...........77

REGISTERS 011H, 051H, 091H AND 0D1H: CDRC INTERRUPT ENABLE....79

REGISTERS 012H, 052H, 092H AND 0D2H: CDRC INTERRUPT STATUS.....80

REGISTER 014H, 054H, 094H, AND 0D4H: LCV_PMON INTERRUPT

ENABLE/STATUS...................................................................................81

REGISTERS 01AH-01BH, 05AH-05BH, 09AH-09BH, 0DAH-0DBH: LATCHING

LCV PERFORMANCE DATA ..................................................................82

REGISTERS 01AH, 05AH, 09AH AND 0DAH: LCV_PMON LINE CODE

VIOLATION COUNT LSB .......................................................................83

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

REGISTERS 01BH, 05BH, 09BH AND 0DBH: LCV_PMON LINE CODE

VIOLATION COUNT MSB ......................................................................84

REGISTERS 01CH, 05CH, 09CH AND 0DCH: DJAT INTERRUPT STATUS....85

REGISTER 01DH, 05DH, 09DH AND 0DDH: DJAT REFERENCE CL OCK

DIVISOR (N1) CONTROL ......................................................................86

REGISTERS 01EH, 05EH, 09EH AND 0DEH: DJAT OUTPUT CLOCK DIVISOR

(N2) CONTROL......................................................................................87

REGISTERS 01FH, 05FH, 09FH AND 0DFH: DJAT CONFIGURATION ...........88

REGISTERS 020H, 060H, 0A0H AND 0E0H: IBCD CONFIGURATION...........90

REGISTERS 021H, 061H, 0A1H AND 0E1H: IBCD INTERRUPT

ENABLE/STATUS...................................................................................91

REGISTERS 022H, 062H, 0A2H AND 0E2H: IBCD ACTIVATE CODE.............93

REGISTERS 023H, 063H, 0A3H AND 0E3H: IBCD DEACTIVATE CODE........94

REGISTERS 024H, 064H, 0A4H AND 0E4H: XIBC CONTROL .......................95

REGISTERS 025H, 065H, 0A5H AND 0E5H: XIBC LOOPBACK CODE..........97

REGISTER 027H, 067H, 0A7H, 0E7H: PRSG CONFIGURATION ...................98

REGISTER 029H, 069H, 0A9H, 0E9H: PRSM CONTROL/STATUS.................99

REGISTER 02AH, 06AH, 0AAH, 0EAH: PRSM BIT ERROR EVENT COUNT

LSB.......................................................................................................102

REGISTER 02BH, 06BH, 0ABH, 0EBH: PRSM BIT ERROR EVENT COUNT

MSB......................................................................................................103

REGISTER 02CH, 06CH, 0ACH, 0ECH: XPLS LINE LENGTH CONFIGURATION

..............................................................................................................104

REGISTER 02DH, 06DH, 0ADH, 0EDH: XPLS CONTROL/STATUS..............106

REGISTER 02EH, 06EH, 0AEH, 0EEH: XPLS CODE INDIRECT ADDRESS10 8

REGISTER 02FH, 06FH, 0AFH, 0EFH: XPLS CODE INDIRECT DATA..........110

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

REGISTER 030H, 070H, 0B0H, 0F0H: RSLC CONFIGURATION..................111

REGISTER 031H, 071H, 0B1H, 0F1H: RSLC INTERRUPT ENABLE/STATUS112

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

LIST OF FIGURES

FIGURE 1 - EXAMPLE 1. T1 OR E1 ATM INTERFACES..................................8

FIGURE 2 - EXAMPLE 2. DSX-1 DIGITAL ACCESS CROSS CONNECTS

(DACS)....................................................................................................10

FIGURE 3 - EXAMPLE 3. MULTIPLEXERS (M13).......................................... 12

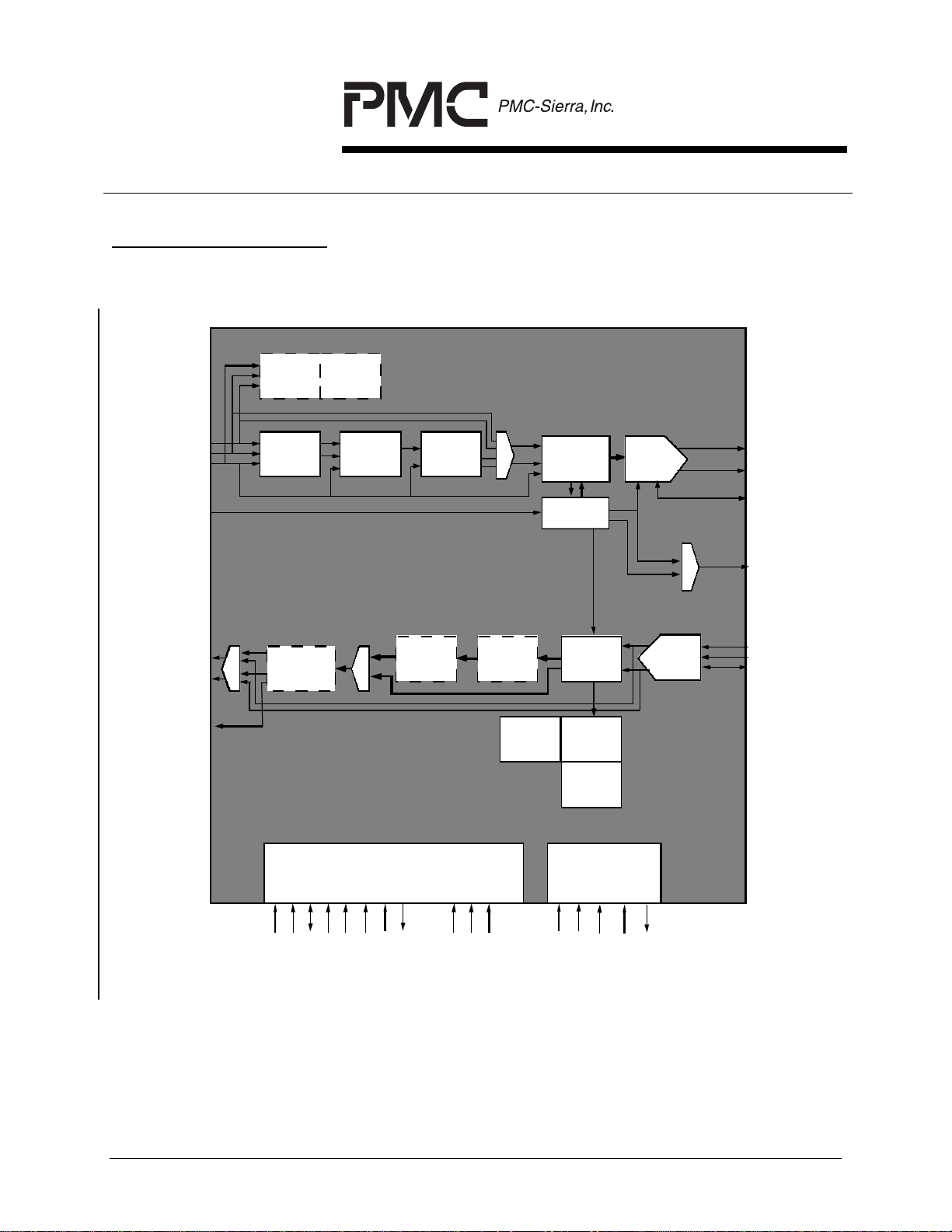

FIGURE 4 - NORMAL OPERATING MODE.....................................................13

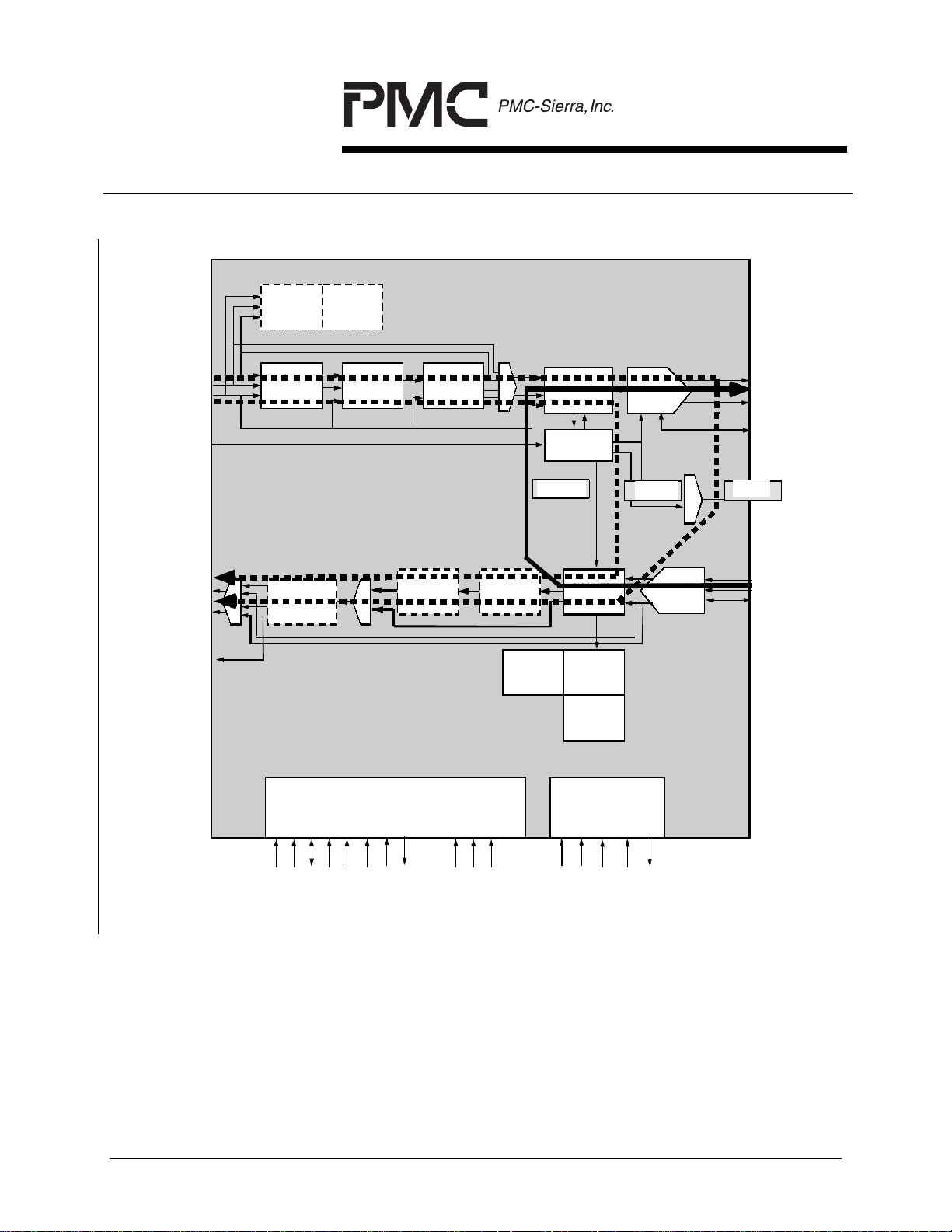

FIGURE 5 - LOOPBACK MODES....................................................................14

FIGURE 6 - EXTERNAL ANALOG RECEIVE INTERFACE CIRCUIT .............34

FIGURE 7 - DSX-1 JITTER TOLERANCE.......................................................37

FIGURE 8 - E1 JITTER TOLERANCE WITH ALGSEL = 1 ..............................38

FIGURE 9 - E1 JITTER TOLERANCE WITH ALGSEL = 0 ..............................39

FIGURE 10- DSX-1 JITTER TOLERANCE .......................................................45

FIGURE 11- E1 JITTER TOLERANCE .............................................................46

FIGURE 12- DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY

(DSX-1 CASE)........................................................................................47

FIGURE 13- DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY (E1

CASE).....................................................................................................47

FIGURE 14- DSX-1 JITTER TRANSFER..........................................................48

FIGURE 15- E1 JITTER TRANSFER................................................................49

FIGURE 16- EXTERNAL ANALOG TRANSMIT INTERFACE CIRCUIT...........51

FIGURE 17- TIMING OPTIONS........................................................................75

FIGURE 18- CODE REGISTER SEQUENCE DURING PULSE GENERATION

.....................................................................................................125

FIGURE 19- CODE REGISTER SEQUENCE FOR 0-110 FEET BUILD-OUT126

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

FIGURE 20- BOUNDARY SCAN ARCHITECTURE........................................131

FIGURE 21- TAP CONTROLLER FINITE STATE MACHINE ..........................133

FIGURE 22- INPUT OBSERVATION CELL (IN_CELL)...................................138

FIGURE 23- OUTPUT CELL (OUT_CELL).....................................................139

FIGURE 24- BIDIRECTIONAL CELL (IO_CELL)............................................140

FIGURE 25- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS140

FIGURE 26- B8ZS LINE CODE VIOLATION INSERTION ..............................141

FIGURE 27- HDB3 LINE CODE VIOLATION INSERTION..............................142

FIGURE 28- AMI LINE CODE VIOLATION INSERTION.................................143

FIGURE 29- MICROPROCESSOR INTERFACE READ TIMING....................150

FIGURE 30- MICROPROCESSOR INTERFACE WRITE TIMING ..................152

FIGURE 31- XCLK INPUT TIMING FOR JITTER ATTENUATION ..................153

FIGURE 32- TCLKI INPUT TIMING ................................................................154

FIGURE 33- CLKO8X INPUT TIMING DIAGRAM (FIFO NOT IN TX PATH) ...156

FIGURE 34- XCLK INPUT TIMING DIAGRAM (FIFO NOT IN TX PATH)........157

FIGURE 35- RCLKO OUTPUT TIMING DIAGRAM.........................................158

FIGURE 36- JTAG PORT INTERFACE TIMING..............................................160

FIGURE 37- ANALOG RECEIVE DATA INPUT TIMING DIAGRAM................161

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

LIST OF TABLES

TABLE 1 - ......................................................................................................33

TABLE 2 - ......................................................................................................35

TABLE 3 - ......................................................................................................51

TABLE 4 - ......................................................................................................90

TABLE 5 - TEST MODE REGISTER MEMORY MAP ..................................113

TABLE 6 - ....................................................................................................115

TABLE 7 - ....................................................................................................115

TABLE 8 - INSTRUCTION REGISTER........................................................116

TABLE 9 - BOUNDARY SCAN REGISTER.................................................117

TABLE 10 - ....................................................................................................122

TABLE 11 - ....................................................................................................123

TABLE 12 - ....................................................................................................124

TABLE 13 - ....................................................................................................136

TABLE 14 -.QDSX ABSOLUTE MAXIMUM RATINGS ..................................144

TABLE 15 - QDSX CAPACITANCE................................................................145

TABLE 16 - QDSX D.C. CHARACTERISTICS...............................................146

TABLE 17 - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 29)

.....................................................................................................149

TABLE 18 - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 30)

.....................................................................................................151

TABLE 19 - XCLK INPUT FOR JITTER ATTENUATION (FIGURE 31)..........153

TABLE 20 - TCLKI INPUT TIMING (FIGURE 32)...........................................154

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

TABLE 21 - CLKO8X INPUT TIMING (FIFO NOT IN TX PATH) (FIGURE 33)156

TABLE 22 - XCLK INPUT TIMING (FIFO NOT IN TX PATH) (FIGURE 34)....157

TABLE 23 - RCLKO OUTPUT TIMING (FIGURE 35) ....................................158

TABLE 24 - JTAG PORT INTERFACE TIMING (FIGURE 36)........................159

TABLE 25 - ANALOG RECEIVE DATA INPUT TIMING (FIGURE 37) ...........161

TABLE 26 - QDSX ORDERING INFORMATION ...........................................163

TABLE 27 - QDSX THERMAL INFORMATION..............................................163

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

1

FEATURES

Integrates four duplex DSX-1 or CEPT E1 compatible line interface circuits in

•

a single monolithic device. Line format is selected on a per-device basis.

Provides clock recovery and line performance monitoring in the receivers.

•

Provides jitter attenuation and programmable line build out in the transmitters.

•

Utilizes digital phase-locked loops for receive and transmit clock derivation

•

without the use of tuned circuits.

Provides an integrated 8X clock multiplier for generation of required high-

•

speed clocks in applications not requiring jitter attenuation.

Optionally inserts Alarm Indication Signal (AIS) when loopback modes are

•

enabled. AIS insertion may also be directly controlled via the microprocessor

interface.

Provides a generic microprocessor interface for initial configuration, ongoing

•

control, and status monitoring.

Generates an interrupt upon detection of any of various alarms, events, or

•

changes in status. Identification of interrupt sources, masking of interrupt

sources, and acknowledgment of interrupts is provided via internal registers.

Provides optional hardware programmed mode which provides external

•

configuration pins when microprocessor access is not available to the device.

Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board

•

test purposes.

Provides seamless interface to PM4344 TQUAD, PM6344 EQUAD, PM8313

•

D3MX, and PM7344 S/UNI-MPH.

Low power CMOS technology, 1500 mW power dissipation processing all

•

ones signals on all four quadrants.

128-pin (14mm x 20mm) PQFP package.

•

Each receiver section

Slices incoming G.703 DSX-1 and CEPT E1 bipolar line signals into digital

•

return-to-zero (RZ) pulses.

Selectable slicer levels (DSX-1/CEPT E1) to provide improved SNR.

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

Squelches RZ signals with pulse amplitudes below 140mV and 105mV for

•

CEPT and T1, respectively.

Typical minimum sensitivity of 50 mV at transformer primary with a 1:2 turns

•

ratio transformer allows for terminating or bridged performance monitoring

applications.

Recovers a 1.544 MHz clock and DS-1 data or a 2.048 MHz clock and E1

•

data using a digital phase-locked loop to achieve high jitter accommodation.

Accommodates up to 0.4 UI peak-to-peak, high frequency jitter to satisfy

•

AT&T TR 62411 and ITU-T G.823.

Optionally outputs either dual rail recovered line pulses or a single rail DS-

•

1/E1 signal.

Performs B8ZS or AMI decoding when processing a bipolar DS-1 signal and

•

HDB3 or AMI decoding when processing a bipolar E1 signal.

Detects line code violations (LCVs), B8ZS/HDB3 line code signatures, and

•

16, 8, or 4 successive zeros.

Accumulates up to 4095 line code violations (LCVs), for performance

•

monitoring purposes, over accumulation intervals defined by the period

between software write accesses to the LCV register.

Detects loss of signal (LOS), which is defined as 10, 15, 31, 63, or 175

•

successive zeros.

Detects both programmable inband loopback activate and deactivate code

•

sequences received in the DS-1 data stream when they are present for 5

seconds. Optionally, enters loopback mode automatically on detection of an

inband loopback code.

Detects any pair of arbitrary inband codes from three to eight bits in length.

•

The inband code detection algorithm operates in the presence of a 10-2 bit

•

error rate.

Programmable to detect CSU (Channel Service Unit), network, and far-end

•

loopback codes.

Optionally allows jitter attenuation of recovered clock and data, using a 2 X 48

•

bit FIFO.

Optionally inserts unframed inband code sequences in place of recovered

•

data.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

Detects unframed 215-1 test sequences as defined in ITU-T O.151 and

•

accumulates bit errors detected using this pseudo-random pattern.

Optionally inserts unframed 215-1 test sequences in place of recovered data.

•

Each transmitter section

Generates DSX-1 and CEPT E1 compatible pulses with programmable pulse

•

shape using an external 1:1.36 turns ratio transformer.

Accommodates standard cable types such as ABAM, PIC, and Coaxial.

•

Provides an integrated analog pulse driver performance monitor which can

•

provide an interrupt upon detection of failure.

Allows bipolar violation (BPV) transparent operation for error restoring

•

regenerator applications.

Allows bipolar violation (BPV) insertion for diagnostic testing purposes.

•

Supports all ones transmission for alarm indication signal (AIS) generation.

•

Provides a digital phase-locked loop for generation of jitter reduced transmit

•

output timing. The DPLL utilizes a 37.056 MHz master clock for DSX-1 or a

49.152 MHz master clock fo r CEPT E1 applications.

Digital phase-locked loop locks 1.544 MHz or 2.048 MHz output timing to the

•

average frequency of the 1.544 MHz or 2.048 MHz jittered transmit input

clock.

Provides a 2 x 48 bit FIFO for jitter attenuation in the transmit path.

•

Provides up to 55 dB of jitter attenuation to satisfy AT&T TR 62411, ITU-T

•

G.737, G.738, G.739, and G.742.

Provides FIFO overrun and underrun indicators.

•

Inhibits FIFO overrun and underrun for excessive jitter amplitudes.

•

Supports transmission of a programmable unframed inband loopback code

•

sequence.

Programmable to transmit repetitions of any arbitrary code from three to eight

•

bits in length.

Accepts either dual rail or single rail DS-1/E1 signals.

•

Performs B8ZS or AMI encoding when processing a single rail DS-1 signal

•

and HDB3 or AMI encoding when processing a single rail E1 signal.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

Optionally detects inband code sequences in DS-1 transmit streams.

•

Optionally inserts unframed 215-1 test sequences in place of input transmit

•

data.

Optionally detects unframed 215-1 test sequences in the input transmit data.

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

2

APPLICATIONS

T1 or E1 ATM interfaces

•

Electronic DSX-1/CEPT E1 Cross-connects

•

Digital Access and Cross-connect Systems (DACS)

•

Multiplexers

•

Channel Service Units (CSUs)

•

DSX-1/CEPT E1 Repeaters

•

Test Equipment

•

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

3

REFERENCES

1. American National Standard for Telecommunications, ANSI T1.102-1992 -

"Digital Hierarchy - Electrical Interfaces".

2. American National Standard for Telecommunications, ANSI T1.107-1991 -

“Digital Hierarchy - Formats Specifications”.

3. American National Standard for Telecommunications, ANSI T1.403-1989 -

"Carrier to Customer Installation - DS1 Metallic Interface Specification".

4. American National Standard for Telecommunications, ANSI T1.408-1990 -

"Integrated Services Digital Network (ISDN) Primary Rate - Customer

Installation Metallic Interfaces Layer 1 Specification".

5. Bell Communications Research, TR-TSY-000009 - "Asynchronous Digital

Multiplexes Requirements and Objectives", Issue 1, May, 1986.

6. Bell Communications Research, TA-TSY-000147 - "DS1 Rate Digital Service

Monitoring Unit Functional Specification", Issue 1, October, 1987.

7. Bell Communications Research, TR-TSY-000170 - "Digital Cross-Connect

System (DCS) - Requirements and Objectives", Issue 1, November, 1985.

8. Bell Communications Research, TR-TSY-000191 - "Alarm Indication Signal

Requirements and Objectives" Issue 1, May 1986.

9. Bell Communications Research, TR-TSY-000303 - "Integrated Digital Loop

Carrier System Generic Requirements, Objectives, and Interface", Issue 1,

Rev. 1, December, 1987.

10. Bell Communications Research, TR-TSY-000312 - "Functional Criteria for the

DS1 Interface Connector", Issue 1, March, 1988.

11. Bell Communications Research, TR-TSY-000499 - "Transport Systems

Generic Requirements (TSGR): Common Requirement", Issue 3, December,

1989.

12. AT&T, TR 43801 - "Digital Channel Bank - Requirements and Objectives",

November, 1982.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

13. AT&T, TR 43802 - "Digital Multiplexers - Requirements and Objectives", July,

1982.

14. AT&T, TR 62411 - Accunet T1.5 - "Service Description and Interface

Specification", December, 1990.

15. CCITT Red Book, Recommendation Q.516, - "Operations and maintenance

functions", V ol. VI, F asc. VI.5, 1984.

16. ITU-T Recommendation O.150, - "Digital Test Patterns for Performance

Measurements on Digital Transmission Equipment", Oct. 1992.

17. ITU-T Recommendation O.151, - "Error Performance Measuring Equipment

Operating at the Primary Rate and Above", Rev.1, 1992.

18. ITU-T Recommendation G.703, - "Physical/Electrical Characteristics of

Hierarchical Digital Interfaces", Rev.1, 1991.

19. ITU-T Recommendation G.704, - "Synchronous Frame Structures Used at

Primary and Secondary Hierarchical Levels", Rev.1, 1991.

20. ITU-T Recommendation G.821, - "Error Performance of an International

Digital Connection Forming Part of an Integrated Services Digital Network",

Blue Book Fasc. III.5, 1988.

21. ITU-T Recommendation G.823, - "The Control of Jitter and Wander Within

Digital Networks Which are Based on the 2048 kbit/s Hierarchy", 1993.

22. ITU-T Recommendation O.151, - "Error Performance Measuring Equipment

Operating at the Primary Rate and Above", Rev. 1, Oct. 1992.

23. ITU-T Recommendation O.162, - "Equipment to Perform in Service

Monitoring on 2048, 8448, 34368, and 139264 kbit/s Signals", Rev.1, Oct.

1992.

24. ITU-T, Recommendation I.432 - “B-ISDN User-Network Interface - Physical

Layer Specification”, August 1992.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

4

APPLICATION EXAMPLES

Figure 1 - Example 1. T1 or E1 ATM Interfaces

SCI-PHY

Multi-PHY

ATM Cell Bus

Generic

Microprocessor

Bus

1X Transmit Reference Clock

DSX-1

PM7344

S/UNI-MPH

Q u a d T1 /E 1

TM

Multi-P HY

Us er Ne tw o r k I n te r fa c e

PM4314

QDSX

Quad T1/E1

Line In terfa c e Dev ic e

Crystal Oscillator 24X Clock

(37.056 MHz for T1 or 49.152 MHz

for E1) if using jitter attenuator or

XPL S W IDEN fun ction . 8 X c loc k

otherwise.

or

E1

Analog

Interfaces

Example 1 shows the PM4314 QDSX used with the PM7344 S/UNI-MPH to

implement a quad T1/E1 UNI where the DS1 or E1 signals are presented on

DSX-1 or E1 electrical interfaces.

In this example, the DSX-1 or E1 line interface functions are provided by the

QDSX and the DS-1 or E1 framing functions are provided by the S/UNI-MPH.

The S/UNI-MPH also provides the ATM cell processing functions associated with

the PHY layer, including the implementation of a SCI-PHY multi-PHY interface to

the ATM layer device(s). The combination of the QDSX device with the S/UNIMPH allows both ANSI/ITU compliant DSX-1/E1 analog signals and ATM Forum

UNI 3.1 and ITU G.804 compliant DS1/E1 digital signals to be processed.

Jitter attenuation by both the QDSX and the S/UNI-MPH can be performed by

supplying a 24X reference clock to the devices. If jitter attenuation is to be

executed by the S/UNI-MPH only, then an 8X reference clock is required by the

QDSX and a 24X reference clock is required by the S/UNI-MPH. If jitter

attenuation is to be executed by the QDSX, then a 24X reference clock must be

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

supplied to it and an 8X reference clock may be supplied to the S/UNI-MPH. If

jitter attenuation is not required by either device, then an 8X reference clock may

be supplied to both devices.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

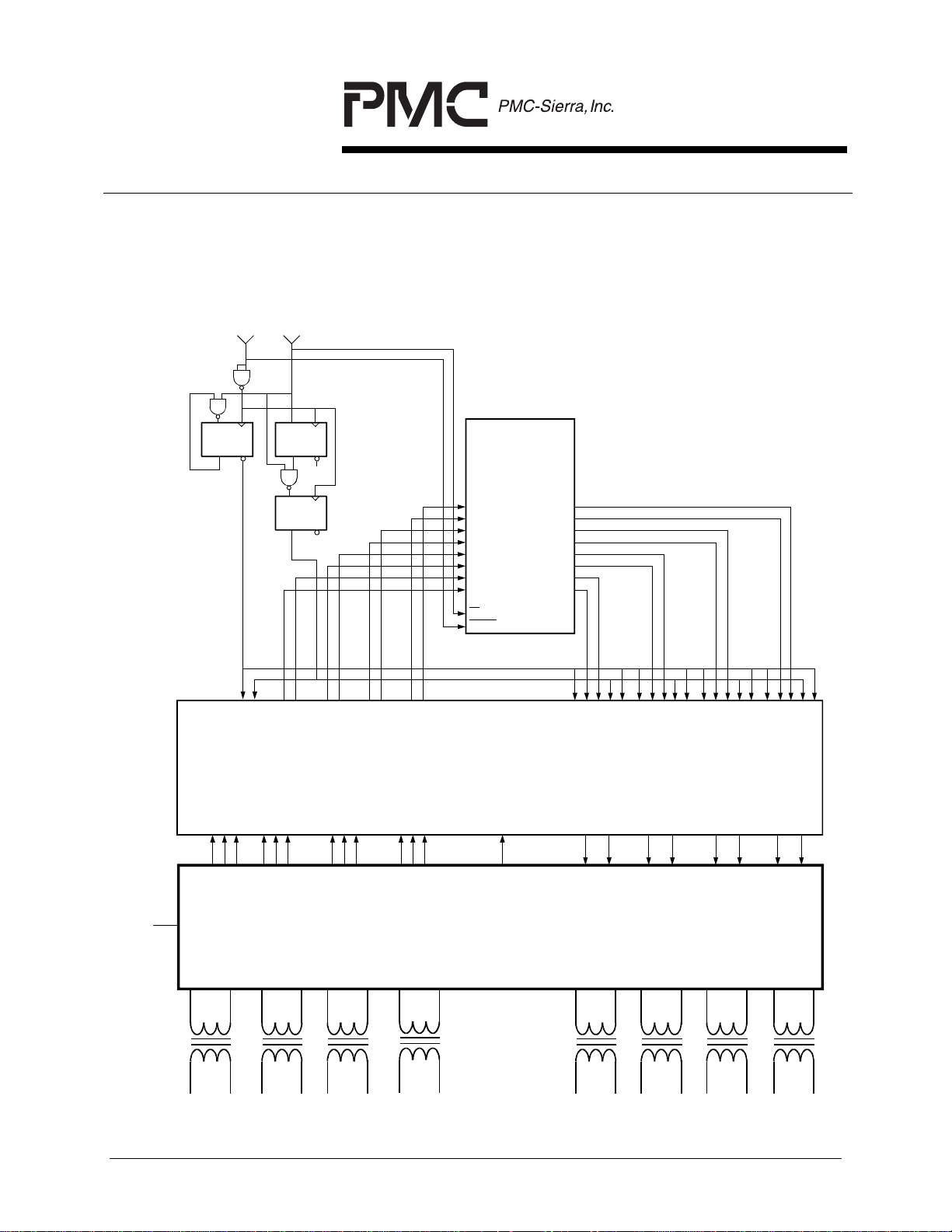

Figure 2 - Example 2. DSX-1 Digital Access Cross Connects (DACs)

ulse

ame P

m Fr

4.096MHz

Syste

Glue logic can be implemented

using one 74 H C T0 0 an d on e

74HCT175 pack.

D

Q

QB

D

Q

QB

tch

37.056 MHz

Clock

XCLK

D

2.048MHz

BRFPI

BRCLK

Q

QB

BRSIG[1]

BRFPO[1]

BRPCM[1]

BRPCM[2]

BRSIG[3]

BRSIG[2]

BRFPO[3]

BRFPO[2]

BRPCM[4]

BRPCM[3]

IN[0]

IN[1]

IN[2]

IN[3]

IN[4]

IN[5]

IN[6]

IN[7]

FP

CLK2X

BRSIG[4]

BRFPO[4]

Swi

ace

/Sp

Time

OUT[0]

OUT[1]

OUT[2]

OUT[3]

OUT[4]

OUT[5]

OUT[6]

OUT[7]

]

]

[1]

TCLK I[1

BTSIG

BTPCM[1

]

]

]

[1]

[2]

BTFP[1

TCLK I[2

BTCLK

BTSIG

BTPCM[2

]

]

]

[2]

[3]

BTFP[2

TCLK I[3

BTSIG

BTCLK

BTPCM[1

]

]

[3]

BTFP[3

BTCLK

]

]

TCLK I[4

[4]

[4]

BTFP[4

BTSIG

BTCLK

BTPCM[4

PM4344 TQUAD

RDN/RLCV[1]

RCL KI[1]

RDP/RDD[1]

P[1]

RCLKO[1]

RDD/RDP/SD

RLCV/RDN/SDN[1]

1]

RXTIP[

RXRING[1]

RCL K I[2 ]

RDN/RLCV[2]

RDP/RDD[2]

P[2]

RCLKO[2]

RDD/RDP/SD

RLCV/RDN/SDN[2]

2]

RXTIP[

RXRING[2]

RCL K I[3 ]

RDN/RLCV[3]

RDP/RDD[3]

P[3]

RCLKO[3]

RDD/RDP/SD

RLCV/RDN/SDN[3]

3]

RXTIP[

RXRING[3]

RCL K I[4 ]

RDN/RLCV[4]

RDP/RDD[4]

P[4]

RCLKO[4]

RDD/RDP/SD

RLCV/RDN/SDN[4]

4]

RXTIP[

RXRING[4]

XCLK

CLKO8X

PM4314

QDSX

]

DP[1

TDD/T

TDN[1]

]

DP[1

TDD/T

]

P[1

TXTI

]

]

DP[2

TDD/T

TCLKO [1

]

TCLKI[1

TDN[2]

]

DP[2

TDD/T

]

P[2

TXTI

TXRING [1]

]

]

DP[3

TCLKO [2

]

TCLK I[2

TXRING [2]

TDN[3]

TDD/T

]

DP[3

TDD/T

]

P[3

TXTI

]

]

TCLKO [3

]

TCLK I[3

TXRING [3]

]

DP[4

TDN[4]

TDD/T

TCLKO [4

]

]

DP[4

TCLK I[4

TDD/T

]

P[4

TXTI

TXRING [4]

*note:

RC a ttenuation

networks not s h o w n

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

Example 2 shows a DSX 1/0 Cross-Connect using a PM4314 QDSX, a PM4344

TQUAD, and a Digital Time/Space Switch to implement a simple 1/0 crossconnect. An alternate architecture could use two Digital Time/Space Switches,

one as a voice switch and the other as a signaling switch, and 2 TQUADs to

cross-connect eight T1s. (Note: a true implementation would require redundancy

in the switch core.)

In this example, the TQUAD is programmed to receive and generate the same

framing format, using the 2.048 MHz backplane data rate. The "system frame

pulse" signal is stretched through the two D-FF into a pulse of 488ns duration,

which is used to frame align the data out of each framer through the elastic store

and to provide frame alignment indication to the transmitters. The raw system

frame pulse signal is used to indicate frame alignment synchronization to the

Digital Time/Space Switch. Another D-FF is configured as a toggle to generate a

2.048MHz clock from the system 4.096MHz clock source, synchronized to the

system frame pulse. The TQUAD is configured to accept and source unipolar

signal from and to the QDSX. As shown, the jitter attenuation is performed in the

QDSX and is disabled in the TQUAD.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

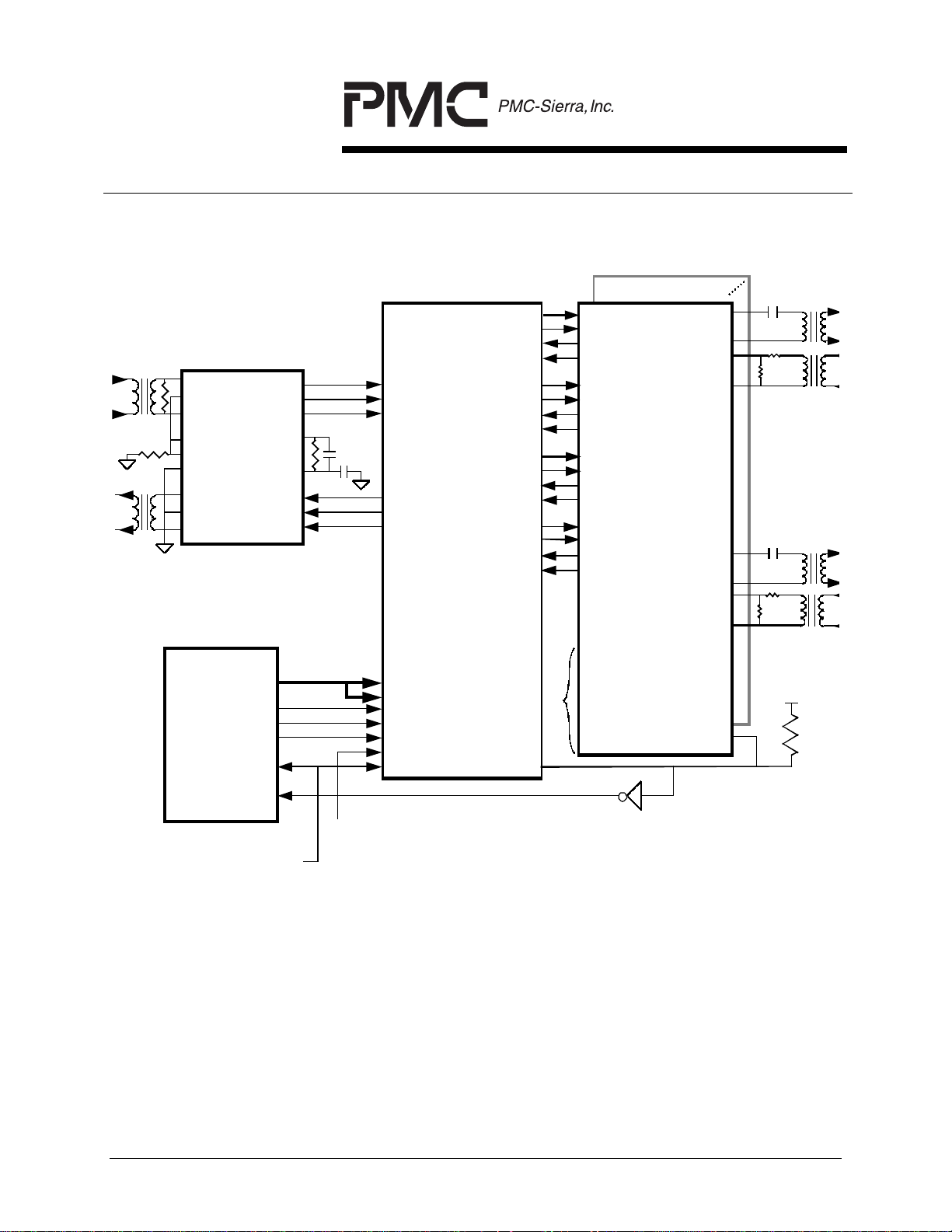

Figure 3 - Example 3. Multiplexers (M13)

(7 Quad DSX-1/E1 line interfaces)

LIN+

NC-R

LIN-

RGND

RFO

TGN D

LOUT+

NC-T

LOUT-

P

µ

0

0

2

7

8P

I 7

SS

DS-3 Line Interfa ce

AD[15:0]

ALE

RDB

WR B

RESB

RPOS

RNEG

RCL K

LF1

LF2

TPOS

TNE G

TCL K

RPOS

RNEG

RCLK

TPOS

TNEG

TCLK

TICLK

TOH

TOHEN

TIMFP

TOHCLK

TOHFP

A[8:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

PM83 13

MX

D3

r

e

lex

tip

ul

M

3

M1

RD1DAT1

RD1CLK1

TD1DAT1

TD1CLK1

RD1DAT2

RD1CLK2

TD1DAT2

TD1CLK2

RD1DAT3

RD1CLK3

TD1DAT3

TD1CLK3

RD1DAT4

RD1CLK4

TD1DAT4

TD1CLK4

RD1DAT28

RD1CLK28

TD1DAT28

TD1CLK28

INTB

•

•

•

•

•

•

•

•

•

1:1.36

1:2

1:1.36

1:2

+5V

PM43 14

SX

QD

TXTIP[1]

TXRING[1]

RXTIP[1]

RXR ING[1]

TXTIP[2]

TXRING[2]

RXTIP[2]

RXR ING[2]

TXTIP[3]

TXRING[3]

RXTIP[3]

RXR ING[3]

TXTIP[4]

TXRING[4]

RXTIP[4]

RXR ING[4]

INTB

TDD[1]

TCLKI[1]

RDD[1]

RCLKO[1]

TDD[2]

TCLKI[2]

RDD[2]

RCLKO[2]

TDD[3]

TCLKI[3]

RDD[3]

RCLKO[3]

TDD[4]

TCLKI[4]

RDD[4]

RCLKO[4]

•

•

•

•

•

o µP

from /t

A[8:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

INT

From chip select

decode circuitry

From Master

reset circuitry

Example 3 shows the use of the PM4314 QDSX with the PM8313 D3MX in an

M13 Multiplexer/Demultiplexer application. Use of the SSI LIU as illustrated

requires that TICLK of the D3MX has a duty cycle of 45% min., 55% max. or

better (e.g.. using a Connor Winfield S65T3 reference oscillator).

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

5

BLOCK DIAGRAM

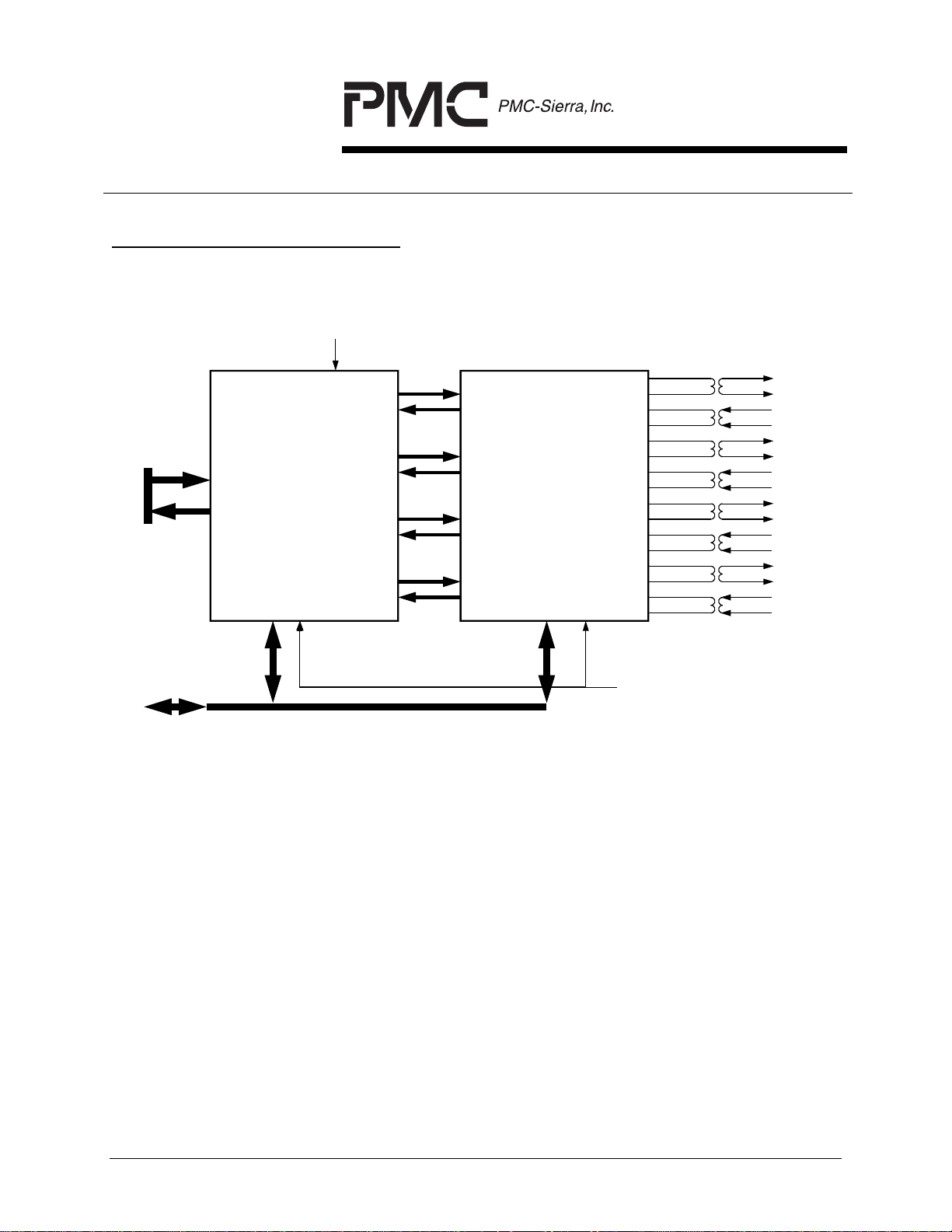

Figure 4 - Normal Operating Mode

TDD/TDP[4:1]

TDN[4:1]

TCLKI[4:1]

XCLK/VCL K

RDD/RDP/SDP[4:1]

RLCV/RDN/SDN[4:1]

PRSM

PRBS

DETECTOR AND

ERROR COUNTER

PRS G

PRBS

GENERA TOR

DJAT

DIGITAL JITTER

ATTENUAT OR

IBC D

IN-BAND LOOP-

BACK C ODE

DETECTOR

XIBC

IN-BAND LOOP-

BACK C ODE

GENERA TOR

AM I/B8Z S/HD B3

ENC ODER

XIBC

IN-BAND LOOP-

BACK C ODE

GENERATOR

LCODE

LINE

PRS G

PRBS

GENERATOR

DJAT

DIGITAL JITTER

ATTENUAT OR

TOPS

TIMING OPTIONS

CDRC

CLO C K AN D

DATA

RECOVERY

TRANSMITTER

XPLS

ANA LOG

PULSE

GENERAT OR

RECEIVER

RSLC

ANALOG

PUL SE

SLICER

TXTIP[4:1]

TXR ING[4 :1]

TC[4:1 ]

CLKO8X/CLKO1X

RXTIP[4:1]

RXRING[4:1]

RC[4:1]

RCLKO[4:1]

IBC D

IN-BAND LOOP-

BACK C ODE

DETECTOR

CONTROL SIGNALS

Microprocess or Interface or

Hardware Control Signals

]

:0

[8

WRB

A

D[7:0]

RSTB

DB

R

B

CS

E

TB

L

A

IN

L

AL

TDU

RDUA

R

C

D

LCV_PMON

LINE CODE

VIOLATION

COUNTER

PRSM

PRBS

DETECTOR AND

ERROR COUNTER

BOUND ARY SCAN

IEEE P1149.1

JTAG Test

Access Port

I

B

ST

TR

S

M

T

TD

O

TCK

TD

Note:

Dashed boxes show optional placement of blocks. Default placement of the

block is shown in solid boxe s.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

PM4314 QDSX

g

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

Figure 5 - Loopback Modes

TDD /TDP[4:1]

TDN[4:1]

TCLKI[4:1]

XCL K/VCLK

RDD/RDP/SDP[4:1]

RLCV/RDN/SDN[4:1]

RCLKO[4:1]

PRSM

PRBS

DETECTOR AND

ERROR COUNTER

PRSG

PRBS

GENERATOR

DJAT

DIGITAL JITTER

ATTENU ATOR

IBCD

IN-BAND LOOP-

BACK CODE

DETECTOR

XIBC

IN-BAND LOOP-

BACK CODE

GENERATOR

LCODE

AMI/B8ZS/H DB3

ENCODER

XIBC

IN-BAND LOOP-

BACK CODE

GENERATOR

LIN E

PRSG

PRBS

GENERATOR

IN-BAND LOOP-

BACK CODE

DETECTOR

LINELB

IBCD

DJAT

DIGITAL JITTER

ATTENUATOR

TOPS

TIMING OPTIONS

CDRC

CLOCK AN D

DATA

RECOVERY

LCV_PMON

LINE CODE

VIOLATION

COUNTER

PRSM

PRBS

DETECTOR AND

ERROR COUNTER

TRANSMITTER

XPL S

ANALOG

PULSE

GENERAT OR

DIALB

RECEIVER

RSLC

ANA LOG

PULSE

SLICER

TXTIP[4:1]

TXRING[4:1 ]

TC[4:1]

DMLB

CLKO8X/CLKO1X

RXTIP[4:1]

RXRING[4:1]

RC[4:1]

CONTROL SIGNALS

Microprocessor Interface or

Hardw are Control Si

]

B

:0

8

A[

RST

B

0]

D[7:

SB

D

R

C

WRB

nals

E

AL

INTB

L

UA

RD

R

C

D

TDU AL

BOUNDAR Y SCAN

IEEE P1149.1

JTAG Test

Access Port

S

K

M

TDI

TC

T

TRSTB

TDO

Note:

Dashed boxes show optional placement of blocks. Default placement of the

block is shown in solid boxe s.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

6

DESCRIPTION

The PM4314 QDSX Quad T1/E1 Line Interface Device is a monolithic integrated

circuit that supports DSX-1 and CEPT E1 compatible transmit and receive

interfaces for four 1.544 Mbit/s or 2.048 Mbit/s data streams.

In the incoming direction, the DSX-1/E1 signals for each quadrant of the QDSX

are first processed by a receive data slicer. The receive data slicer converts the

line signal received via a coupling transformer to dual rail RZ digital pulses.

Adaptation for attenuation is achieved using an integral peak detector that sets

the slicing levels. Through use of passive external attenuation circuitry, either

terminated or bridge monitored DSX-1/E1 signal levels can be accommodated.

The low signal level condition or signal squelch may be enabled to generate

interrupts. Clock and data are recovered from the dual rail RZ digital pulses

using a digital phase-locked loop that provides excellent high frequency jitter

accommodation. The recovered data is decoded using B8ZS, HDB3, or AMI line

code rules and is presented either as a DS-1/E1 stream or presented in an

undecoded dual rail NRZ format. Loss of signal and line code violations are

detected as well as 8 successive zeros/4 successive zeros, and the B8ZS/HDB3

signature. The presence of programmable inband loopback codes is also

detected. These various events or changes in status may be enabled to

generate interrupts. Additionally, line code violations are indicated on outputs.

In the outgoing direction, each quadrant of the QDSX may accept either a DS1/E1 stream to be encoded using B8ZS, HDB3, or AMI line code rules, or it may

accept pre-encoded data in dual rail NRZ format. Jitter attenuation is provided

by passing outgoing data through a FIFO. A low jitter clock is generated by an

integral digital phase-locked loop and is used to read data from the FIFO. FIFO

overrun or underrun may be enabled to generate interrupts. Alarm indication

signal (all ones) may be substituted for the FIFO data. The digital data is

converted to high drive, dual rail RZ pulses that drive the DSX-1/E1 interface

through a coupling transformer. The shape of the pulses is user programmable

to ensure that the DSX-1/E1 pulse template is met after the signal is passed

through different cable lengths or types. Driver performance monitoring is

provided and may be enabled to generate interrupts upon driver failure.

The jitter attenuation function can optionally be moved to the receive side. The

recovered clock and data is passed through the jitter attenuator before being

presented at the digital receive outputs.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

15

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

Internal high speed timing for all quadrants of the QDSX is provided by a

common 37.056 MHz or 49.152 MHz master clock. This master clock rate is

required for applications where QDSX provides jitter attenuation. For

applications where QDSX is not required to attenuate jitter, a 12.352 MHz or

16.384 MHz clock may be used as the master clock and used directly as the

internal 8X high speed clock.

Diagnostic loopback is provided and the loopback may be invoked past the

analog transmit outputs using the driver performance monitors or invoked prior to

the conversion to analog. Line loopback with jitter attenuation is provided and

may be enabled for automatic operation based on detected inband loopback

codes.

The QDSX detects framed or unframed inband loopback code sequences from

the received input pulses. Any arbitrary code from three to eight bits in length

can be declared to be the activate and deactivate codes by writing to

configuration registers. The inband loopback code detector can optionally be

moved to the transmit side where it detects inband loopback codes in the

unipolar input transmit data stream. For framed inband loopback code

sequences, it is expected that the framing bit overwrites the inband loopback

code bit.

The QDSX may insert unframed inband loopback code sequences into the

transmitted PCM data stream. These codes consist of continuous repetitions of

specific bit sequences. Any arbitrary code from three to eight bits in length is

programmable by writing to configuration registers. This unframed inband

loopback code insertion may optionally be switched to the receive side where it

overwrites the data from the slicer.

The QDSX may insert an unframed 215-1 O.151 compatible pseudo-random bit

sequence into the transmitted PCM data stream. Optionally, the PRBS insertion

may be switched to the receive side where it overwr ites the data from the slicer.

The QDSX detects an unframed 215-1 O.151 compatible pseudo-random bit

sequence input to the receive slicer. This PRBS detector can operate in the

presence of a 10-2 bit error rate. Bit errors are detected and recorded. The

PRBS detector can optionally be switched to the transmit side where it can

detect unframed PRBS data from the unipolar input transmit data stream.

The QDSX operates in conjunction with external line coupling transformers,

resistors, and capacitors. An external crystal may be used for high speed timing

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

16

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

generation. The QDSX is configured, controlled, and monitored using registers

that are accessed via a generic microprocessor interface.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

17

PM4314 QDSX

DATA SHEET

PMC-950857 ISSUE 5 QUAD T1/E1 LINE INTERFACE DEVICE

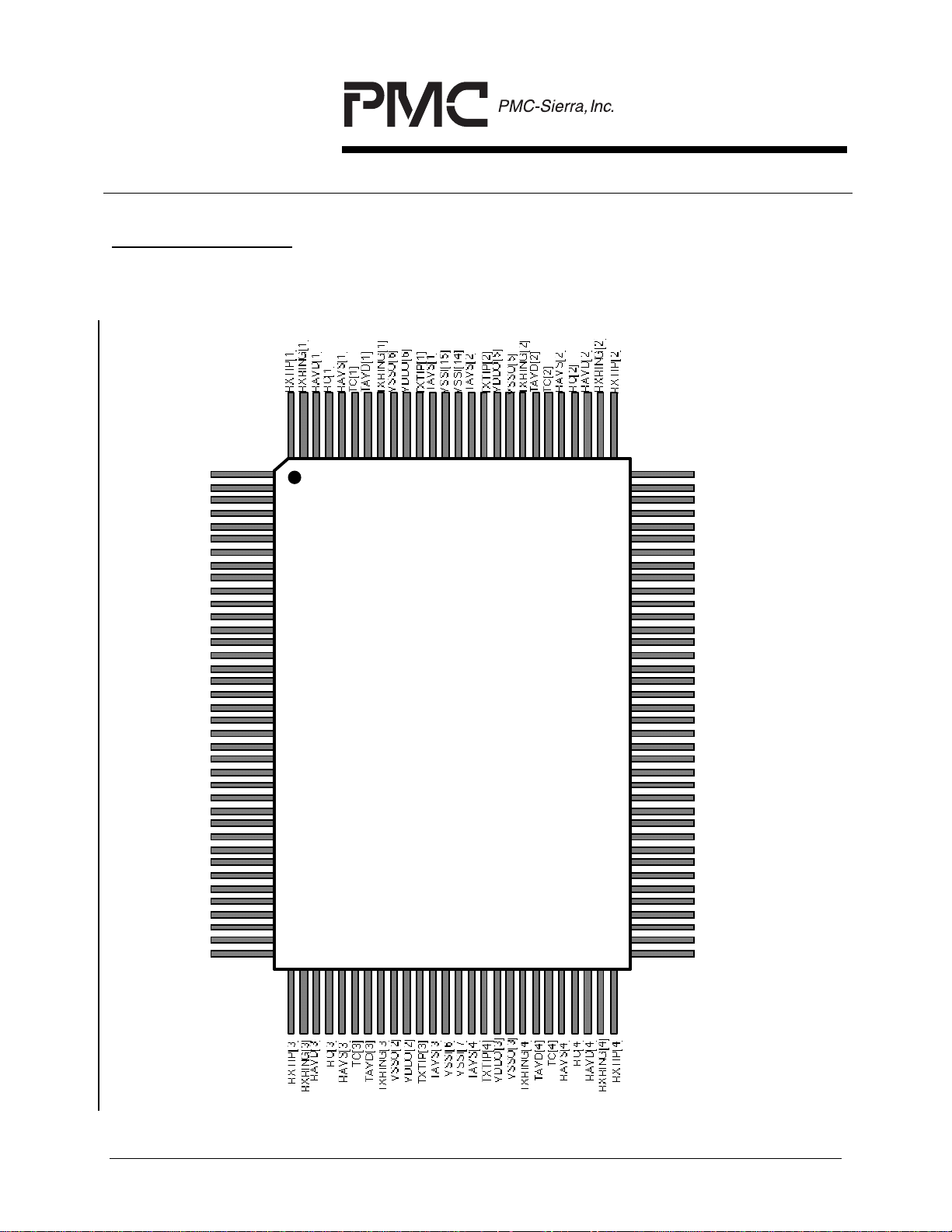

7

PIN DIAGRAM

The QDSX is packaged in a 128-pin plastic QFP package having a body size of

1mm by 20mm and a pin pitch of 0.5 mm.

PIN 128 PIN 103

PIN 1

VSSI[1]

TRSTB

RSTB

VDD0[1]

VSSO[1]

VDDI[1]

VSSI[2]

VSSI[3]

VSSI[4]

VDDI[3]

VSSI[5]

TDI

TCK

TMS

TDO

ALE

CSB

WRB

RDB

INTB

D[0]

D[1]

D[2]

D[3]

D[4]

D[5]

D[6]

D[7]

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

DCR

Index Pin

PM4314

QD SX

Top

View

PIN 102

VSSI[13]

RDUAL

RDD[1]/RDP[1]/SDP[1]

RLCV[1]/RDN[1]/SDN[1]

RCLKO[1]

RDD[2]/RDP[2]/SDP[2]

RLCV[2]/RDN[2]/SDN[2]

RCLKO[2]

VDDO[4]

VSSO[4]

RDD[3]/RDP[3]/SDP[3]

RLCV[3]/RDN[3]/SDN[3]

RCLKO[3]

RDD[4]/RDP[4]/SDP[4]

RLCV[4]/RDN[4]/SDN[4]

RCLKO[4]

CLKO8X/CLK01X

Reserved

VDDI[2]

VSSI[12]

VSSI[11]

VSSI[10]

VSSI[9]

XCLK/VCLK

TCLKI[1]

TDD[1]/TDP[1]

TDN[1]

TCLKI[2]

TDD[2]/TDP[2]

TDN[2]

TCLKI[3]

TDD[3]/TDP[3]

TDN[3]

TCLKI[4]

TDD[4]/TDP[4]

TDN[4]

TDUAL

VSSI[8]

PIN 38

PIN 65

PIN 39

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PIN 64

18

Loading...

Loading...