PMC PM341-QI, PM341-RI Datasheet

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PM6341

E1XC

E1 FRAMER/TRANSCEIVER

DATA SHEET

ISSUE 8: JUNE 1998

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

PUBLIC REVISION HISTORY

Issue

No.

Issue

Date

Details of Change

8 June

1998

Data Sheet Reformatted — No

Change in Technical Content.

Generated R8 data sheet from

PMC-901204, R10

7 February

1996

Update to rev 9 of Eng Doc

6 June

1995

Update to rev 6 of Eng Doc

5

4

3

2

1 Creation of Document

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

i

CONTENTS

1 FEATURES...............................................................................................1

2 APPLICATIONS........................................................................................4

3 REFERENCES.........................................................................................5

4 APPLICATION EXAMPLES......................................................................7

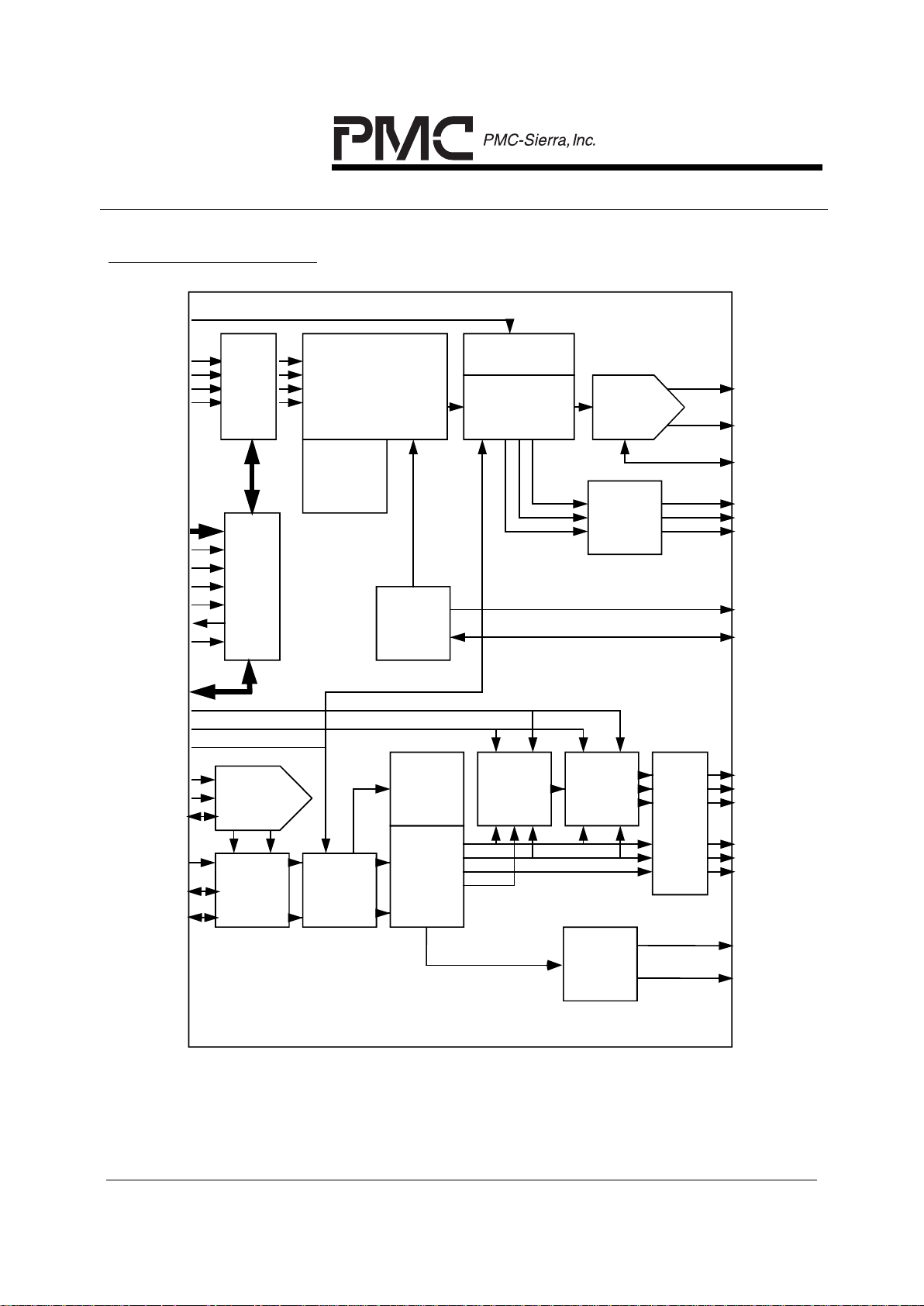

5 BLOCK DIAGRAM..................................................................................10

6 DESCRIPTION.......................................................................................11

7 PIN DIAGRAM........................................................................................13

8 PIN DESCRIPTION................................................................................15

9 FUNCTIONAL DESCRIPTION...............................................................40

9.1 DIGITAL RECEIVE INTERFACE (DRIF)......................................40

9.2 ANALOG PULSE SLICER (RSLC) ..............................................40

1.3 CLOCK AND DATA RECOVERY (CDRC)....................................42

1.4 FRAMER (FRMR)........................................................................44

1.4.1 FRAME FIND....................................................................45

1.4.2 CRC FRAME FIND............................................................48

1.4.3 CRC CHECK AND AIS DETECTION................................49

1.1.4 SIGNALLING FRAME FIND..............................................49

1.1.5 ALARM INTEGRATION.....................................................50

1.5 PERFORMANCE MONITOR COUNTERS (PMON)....................51

1.6 HDLC RECEIVER (RFDL)...........................................................51

1.7 ELASTIC STORE (ELST)............................................................52

1.8 SIGNALLING EXTRACTOR (SIGX).............................................52

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ii

1.9 BACKPLANE RECEIVE INTERFACE (BRIF) ..............................53

1.10 TRANSMITTER (TRAN) ..............................................................53

1.11 TRANSMIT PER-CHANNEL SERIAL CONTROLLER (TPSC)....54

1.12 HDLC TRANSMITTER (XFDL) ....................................................54

1.13 DIGITAL JITTER ATTENUATOR (DJAT).......................................55

1.14 TIMING OPTIONS (TOPS)..........................................................59

1.15 DIGITAL DS-1 TRANSMIT INTERFACE (DTIF)...........................60

1.16 ANALOG PULSE GENERATOR (XPLS)......................................60

1.17 BACKPLANE TRANSMIT INTERFACE (BTIF)............................62

1.18 MICROPROCESSOR INTERFACE (MPIF) .................................6 2

10 REGISTER DESCRIPTION....................................................................63

11 NORMAL MODE REGISTER DESCRIPTION........................................66

11.1 INTERNAL REGISTERS .............................................................67

1.1.1 REGISTERS 49-4FH: LATCHING PERFORMANCE DATA

........................................................................................177

12 TEST FEATURES DESCRIPTION .......................................................187

12.1 INTERNAL REGISTERS ...........................................................190

12.2 TEST MODE 0...........................................................................191

13 TIMING DIAGRAMS.............................................................................193

14 OPERATIONS.......................................................................................198

14.1 CONFIGURING THE E1XC FROM RESET...............................198

14.2 USING THE INTERNAL FDL TRANSMITTER...........................199

14.3 USING THE INTERNAL FDL RECEIVER..................................201

14.3.1KEY USED ON SUBSEQUENT DIAGRAMS:.................205

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iii

14.4 USING THE LOOPBACK MODES.............................................208

14.4.1PAYLOAD LOOPBACK ...................................................209

14.4.2LINE LOOPBACK............................................................209

14.4.3DIAGNOSTIC DIGITAL LOOPBACK...............................210

14.4.4DIAGNOSTIC METALLIC LOOPBACK...........................211

14.5 USING THE PER-CHANNEL SERIAL CONTROLLERS ...........212

14.5.1INITIALIZATION ..............................................................212

14.5.2DIRECT ACCESS MODE ...............................................212

14.5.3INDIRECT ACCESS MODE............................................213

14.6 INTERFACING TO THE ANALOG PULSE SLICER...................213

1.7 ALTERNATIVE LONGITUDINALLY BALANCED RECEIVE

INTERFACE...............................................................................218

1.8 PROGRAMMING THE XPLS WA VEFORM TEMPLATE ............221

1.9 CODE REGISTER PROGRAMMING SEQUENCE FOR CUSTOM

WAVEFORMS............................................................................224

1.10 USING THE DIGITAL JITTER ATTENUATOR............................224

1.10.1DEFAULT APPLICATION.................................................224

1.10.2DATA BURST APPLICATION ..........................................225

1.10.3ELASTIC STORE APPLICATION....................................225

1.10.4ALTERNATE TCLKO REFERENCE APPLICATION........226

1.10.5CHANGING THE JITTER TRANSFER FUNCTION ........226

1.11 USING THE PERFORMANCE MONITOR COUNTER VALUES226

2 ABSOLUTE MAXIMUM RATINGS ........................................................230

3 CAPACITANCE.....................................................................................231

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

iv

4 D.C. CHARACTERISTICS ...................................................................232

5 MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS......234

6 E1XC I/O TIMING CHARACTERISTICS ..............................................239

7 ANALOG CHARACTERISTICS............................................................252

8 ORDERING AND THERMAL INFORMATION ......................................254

9 MECHANICAL INFORMATION............................................................255

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

v

LIST OF REGISTERS

REGISTER 00H: E1XC RECEIVE OPTIONS ...................................................67

REGISTER 01H: E1XC RECEIVE BACKPLANE OPTIONS.............................70

REGISTER 02H: E1XC DATALINK OPTIONS...................................................73

REGISTER 03H: E1XC RECEIVE INTERFACE CONFIGURATION .................76

REGISTER 04H: E1XC TRANSMIT INTERFACE CONFIGURATION...............78

REGISTER 05H: E1XC TRANSMIT BACKPLANE OPTIONS...........................81

REGISTER 06H: E1XC TRANSMIT FRAMING OPTIONS................................83

REGISTER 07H: E1XC TRANSMIT TIMING OPTIONS....................................85

REGISTER 08H: E1XC MASTER INTERRUPT SOURCE................................91

REGISTER 09H: RECEIVE TS0 DATA LINK ENABLES....................................92

REGISTER 0AH: E1XC MASTER DIAGNOSTICS ...........................................94

REGISTER 0BH: E1XC MASTER TEST...........................................................96

REGISTER 0CH: E1XC REVISION/CHIP ID ....................................................98

REGISTER 0DH: E1XC MASTER RESET........................................................99

REGISTER 0EH: E1XC PHASE STATUS WORD (LSB) .................................100

REGISTER 0FH: E1XC PHASE STATUS WORD (MSB).................................102

REGISTER 10H: CDRC BLOCK CONFIGURATION.......................................103

REGISTER 11H: CDRC BLOCK INTERRUPT ENABLE.................................105

REGISTER 12H: CDRC INTERRUPT STATUS...............................................106

REGISTER 13H: ALTERNATE LOSS OF SIGNAL STATUS............................108

REGISTER 14H: XPLS BLOCK LINE LENGTH CONFIGURATION ...............109

REGISTER 15H: XPLS BLOCK CONTROL/STATUS......................................111

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vi

REGISTER REGISTER 16H: XPLS BLOCK CODE INDIRECT ADDRESS....112

REGISTER 17H: XPLS BLOCK CODE INDIRECT DATA................................114

REGISTER 18H: DJAT BLOCK INTERRUPT STATUS....................................115

REGISTER 19H: DJAT BLOCK REFERENCE CLOCK DIVISOR (N1) CONTROL

..............................................................................................................116

REGISTER 1AH: DJAT BLOCK OUTPUT CLOCK DIVISOR (N2) CONTROL

..............................................................................................................117

REGISTER 1BH: DJAT BLOCK CONFIGURATION........................................118

REGISTER 1CH: ELST CONFIGURATION.....................................................120

REGISTER 1DH: ELST INTERRUPT STATUS................................................121

REGISTER 1EH: ELST IDLE CODE...............................................................122

REGISTER REGISTER 20H: FRMR FRAME ALIGNMENT OPTIONS...........123

REGISTER 21H: FRMR MAINTENANCE MODE OPTIONS ..........................125

REGISTER 22H: FRMR FRAMING STATUS INTERRUPT ENABLE..............127

REGISTER 23H: FRMR MAINTENANCE/ALARM STATUS INTERRUPT

ENABLE ...............................................................................................128

REGISTER 24H: FRMR FRAMING STATUS INTERRUPT INDICATION........129

REGISTER 25H: FRMR MAINTENANCE/ALARM STATUS INTERRUPT

INDICATION .........................................................................................130

REGISTER 26H: FRMR FRAMING STATUS...................................................131

REGISTER 27H: FRMR MAINTENANCE/ALARM STATUS............................132

REGISTER 28H: FRMR INTERNATIONAL/NATIONAL BITS..........................134

REGISTER 29H: FRMR EXTRA BITS ............................................................135

REGISTER 2AH: FRMR CRC ERROR COUNTER – LSB..............................136

REGISTER 2BH: FRMR CRC ERROR COUNTER – MSB.............................137

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

vii

REGISTER 2CH: TS16 AIS ALARM STATUS .................................................138

REGISTER 30H: TPSC BLOCK CONFIGURATION........................................139

REGISTER 31H: TPSC BLOCK µP ACCESS STATUS...................................140

REGISTER 32: TPSC BLOCK TIMESLOT INDIRECT ADDRESS/CONTROL141

REGISTER 33H: TPSC BLOCK TIMESLOT INDIRECT DATA BUFFER.........142

TPSC INTERNAL REGISTERS 20-3FH: DATA CONTROL BYTE...................144

TPSC INTERNAL REGISTERS 40-5FH: IDLE CODE BYTE..........................147

REGISTER 34H: XFDL BLOCK CONFIGURATION........................................148

REGISTER 35H: XFDL BLOCK INTERRUPT STATUS...................................150

REGISTER 36H: XFDL BLOCK TRANSMIT DATA..........................................151

REGISTER 38H: RFDL BLOCK CONFIGURATION........................................152

REGISTER 39H: RFDL BLOCK INTERRUPT CONTROL/STATUS ................153

REGISTER 3AH: RFDL BLOCK STATUS........................................................155

REGISTER 3BH: RFDL BLOCK RECEIVE DATA............................................157

REGISTER 40H: SIGX BLOCK CONFIGURATION ........................................158

REGISTER 41H: SIGX BLOCK µP ACCESS STATUS....................................160

REGISTER 42H: SIGX BLOCK TIME SLOT INDIRECT ADDRESS/CONTROL

..............................................................................................................161

REGISTER 43H: SIGX BLOCK TIME SLOT INDIRECT DATA BUFFER.........162

SIGX INDIRECT REGISTERS 33 (21H)- 47 (2FH) - SEGMENT 1: TYPICAL

TIMESLOT SIGNALLING DATA REGISTER (TSS 1-15)......................164

SIGX INDIRECT REGISTERS 49 (31H)- 63 (3FH) - SEGMENT 2: TYPICAL

TIMESLOT SIGNALLING DATA REGISTER (TSS 17-31)....................165

SIGX INDIRECT REGISTERS 64 (40H) - 95 (5FH) - SEGMENT 3: TYPICAL

PER-TIMESLOT PCM TRUNK CONDITIONING DATA REGISTER .....166

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

viii

SIGX INDIRECT REGISTERS 96 (60H) - 127 (7FH) - SEGMENT 4:TYPICAL

PER-TIMESLOT CONFIGURATION AND SIGNALLING TRUNK

CONDITIONING DATA REGISTER ......................................................167

REGISTER 44: TRAN BLOCK CONFIGURATION..........................................169

REGISTER 45: TRAN BLOCK TRANSMIT ALARM/DIAGNOSTIC CONTROL172

REGISTER 46: TRAN BLOCK INTERNATIONAL/NATIONAL CONTROL.......174

REGISTER 47: TRAN BLOCK EXTRA BITS CONTROL................................175

REGISTER 48H: PMON BLOCK CONTROL/STATUS....................................176

REGISTER 49: FRAMING BIT ERROR COUNT.............................................178

REGISTER 4A: FAR END BLOCK ERROR COUNT LSB...............................179

REGISTER 4B: FAR END BLOCK ERROR COUNT MSB..............................180

REGISTER 4C: CRC ERROR COUNT LSB....................................................181

REGISTER 4D: CRC ERROR COUNT MSB...................................................182

REGISTER 4E: LINE CODE VIOLATION COUNT LSB...................................183

REGISTER 4F: LINE CODE VIOLATION COUNT MSB..................................184

REGISTER 5CH: RSLC BLOCK CONFIGURATION.......................................185

REGISTER 5DH: RSLC BLOCK INTERRUPT ENABLE/STATUS...................186

REGISTER 0BH: E1XC MASTER TEST.........................................................190

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

ix

LIST OF FIGURES

FIGURE 1 - ATM E1 AND DS1 USER NETWORK INTERFACE .......................7

FIGURE 2 - DS0 CROSS-CONNECT................................................................8

FIGURE 3 - 68 PIN PLCC (Q-SUFFIX):...........................................................13

FIGURE 4 - 80 PIN PQFP (R-SUFFIX):...........................................................14

FIGURE 5 - EXTERNAL ANALOG RECEIVE INTERFACE CIRCUIT .............42

FIGURE 6 - CDRC JITTER TOLERANCE.......................................................44

FIGURE 7 - BASIC FRAMING ALGORITHM FLOWCHART ...........................47

FIGURE 8 - DJAT JITTER TOLERANCE.........................................................57

FIGURE 9 - DJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY...58

FIGURE 10- DJAT JITTER TRANSFER............................................................59

FIGURE 11- EXTERNAL ANALOG TRANSMIT INTERFACE CIRCUIT...........62

FIGURE 12- TRANSMIT TIMING OPTIONS.....................................................90

FIGURE 13- TS16 TRANSMIT DATALINK INTERFACE..................................193

FIGURE 14- TS0 TRANSMIT DATALINK INTERFACE....................................193

FIGURE 15- TS16 RECEIVE DATALINK INTERFACE....................................194

FIGURE 16- TS0 RECEIVE DATALINK INTERFACE......................................194

FIGURE 17- RECEIVE BACKPLANE INTERFACE ........................................195

FIGURE 18- RECEIVE COMPOSITE MULTIFRAME OUTPUT (BRXSMFP=1

AND BRXCMFP=1):.............................................................................196

FIGURE 19- RECEIVE OVERHEAD OUTPUT (ROHM=1):............................196

FIGURE 20- RECEIVE LINE DATA INTERFACE ............................................196

FIGURE 21- TRANSMIT BACKPLANE INTERFACE......................................197

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

x

FIGURE 22- TYPICAL DATA FRAME..............................................................204

FIGURE 23- RFDL NORMAL DATA AND ABORT SEQUENCE......................205

FIGURE 24- RFDL FIFO OVERRUN ..............................................................206

FIGURE 25- XFDL NORMAL DATA SEQUENCE ...........................................207

FIGURE 26- XFDL UNDERRUN SEQUENCE................................................208

FIGURE 27- PAYLOAD LOOPBACK...............................................................209

FIGURE 28- LINE LOOPBACK.......................................................................210

FIGURE 29- DIAGNOSTIC DIGITAL LOOPBACK..........................................211

FIGURE 30- DIAGNOSTIC METALLIC LOOPBACK.......................................212

FIGURE 31- LONGITUDINALLY BALANCED RECEIVE LINE INTERFACE..219

FIGURE 32- CODE REGISTER SEQUENCE DURING G.803 (120Ω) PULSE

GENERATION ......................................................................................223

FIGURE 33- LCV COUNT VS. BER................................................................227

FIGURE 34- FER COUNT VS. BER................................................................228

FIGURE 35- CRCE COUNT VS. BER.............................................................229

FIGURE 36- MICROPROCESSOR READ ACCESS TIMING.........................235

FIGURE 37- MICROPROCESSOR WRITE ACCESS TIMING .......................237

FIGURE 38- BACKPLANE TRANSMIT INPUT TIMING DIAGRAM................239

FIGURE 39- XCLK=49.152MHZ INPUT TIMING............................................240

FIGURE 40- TCLKI INPUT TIMING ................................................................242

FIGURE 41- DIGITAL RECEIVE INTERFACE INPUT TIMING DIAGRAM......243

FIGURE 42- TRANSMIT DATA LINK INPUT TIMING DIAGRAM....................244

FIGURE 43- BACKPLANE RECEIVE INPUT TIMING DIAGRAM...................245

FIGURE 44- RECEIVE DATA LINK OUTPUT TIMING DIAGRAM...................246

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xi

FIGURE 45- BACKPLANE RECEIVE OUTPUT TIMING DIAGRAM...............246

FIGURE 46- RECOVERED DATA OUTPUT TIMING DIAGRAM.....................247

FIGURE 47- TRANSMIT INTERFACE OUTPUT TIMING DIAGRAM..............248

FIGURE 48- TRANSMIT DATA LINK DMA INTERFACE OUTPUT TIMING

DIAGRAM.............................................................................................249

FIGURE 49- RECEIVE DATA LINK DMA INTERFACE OUTPUT TIMING

DIAGRAM.............................................................................................250

FIGURE 50- ANALOG RECEIVE DATA INPUT TIMING DIAGRAM................252

FIGURE 51- 68 PIN PLASTIC LEADED CHIP CARRIER (Q SUFFIX)...........255

FIGURE 52- 80 PIN COPPER LEADFRAME PLASTIC QUAD FLAT PACK (R

SUFFIX):...............................................................................................256

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xii

LIST OF TABLES

TABLE 1 - RECOMMENDED RX NETWORK VALUES.................................41

TABLE 2 - NORMAL MODE REGISTER MEMORY MAP .............................63

TABLE 3 - TRANSMIT TIMING OPTIONS.....................................................87

TABLE 4 - XPLS CODE REGISTER MEMORY MAP..................................112

TABLE 5 - TPSC INDIRECT MEMORY MAP...............................................142

TABLE 6 - A-LAW DIGITAL MILLIWATT PATTERN......................................145

TABLE 7 - µ-LAW DIGITAL MILLIWATT PATTERN......................................145

TABLE 8 - SIGX INDIRECT MEMORY MAP...............................................162

TABLE 9 - TEST MODE REGISTER MEMORY MAP..................................187

TABLE 10 - E1XC DEFAULT SETTINGS.......................................................198

TABLE 11 - RSLC PERFORMANCE LIMITS ................................................216

TABLE 12 - RECOMMENDED RX NETWORK VALUES...............................218

TABLE 13 - ALTERNATIVE NETWORK RSLC PERFORMANCE LIMITS.....220

TABLE 14 - RECOMMENDED ALTERNATIVE NETWORK VALUES ............221

TABLE 15 - XPLS TYPICAL OUTPUT PULSE AMPLITUDES......................221

TABLE 16 - BER REQUIRED FOR PMON COUNTER SATURATION..........227

TABLE 17 - E1XC D.C. CHARACTERISTICS................................................232

TABLE 18 - MICROPROCESSOR READ ACCESS (FIGURE 36)................234

TABLE 19 - MICROPROCESSOR WRITE ACCESS (FIGURE 37)...............237

TABLE 20 - BACKPLANE TRANSMIT INPUT TIMING (FIGURE 38)............239

TABLE 21 - XCLK=49.152MHZ INPUT (FIGURE 39)....................................240

TABLE 22 - TCLKI INPUT (FIGURE 40)........................................................241

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiii

TABLE 23 - DIGITAL RECEIVE INTERFACE INPUT TIMING (FIGURE 41) .242

TABLE 24 - TRANSMIT DATA LINK INPUT TIMING (FIGURE 42)................244

TABLE 25 - BACKPLANE RECEIVE INPUT TIMING (FIGURE 43)..............245

TABLE 26 - RECEIVE DATA LINK OUTPUT TIMING (FIGURE 44)..............246

TABLE 27 - BACKPLANE RECEIVE OUTPUT TIMING (FIGURE 45)..........246

TABLE 28 - RECOVERED DATA OUTPUT TIMING (FIGURE 46).................247

TABLE 29 - TRANSMIT INTERFACE OUTPUT TIMING (FIGURE 47)..........248

TABLE 30 - TRANSMIT DATA LINK DMA INTERFACE OUTPUT TIMING

(FIGURE 48).........................................................................................249

TABLE 31 - RECEIVE DATA LINK DMA INTERFACE OUTPUT TIMING

(FIGURE 49).........................................................................................250

TABLE 32 - RECEIVE ANALOG INPUT THRESHOLD.................................252

TABLE 33 - ANALOG RECEIVE DATA INPUT TIMING (FIGURE 50) ...........252

TABLE 34 - TRANSMIT PULSE SYMMETRY ...............................................253

TABLE 35 - E1XC ORDERING INFORMATION............................................254

TABLE 36 - E1XC THERMAL INFORMATION...............................................254

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

xiv

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

1

1

FEATURES

•

Integrates a full-featured E1 transceiver in a single device with analog

circuitry for receiving and transmitting G.703 2048 kbit/s compatible signals

and digital circuitry for terminating the duplex digital signal.

•

Pin compatible with the PMC PM4341A T1 Framer/Transceiver device.

•

Provides an 8-bit microprocessor bus interface for configuration, control, and

status monitoring.

•

Low power CMOS technology.

•

Available in either a 68 pin PLCC or an 80 pin PQFP package.

The receiver section:

•

Provides analog circuitry for receiving a G.703 2048 kbit/s signal with up to 6

dB of cable attenuation. Direct digital inputs are also provided to allow for bypassing the analog front-end.

•

Recovers clock and data using a digital phase locked loop for high jitter

tolerance. A direct clock input is provided to allow clock recovery to be bypassed.

•

Accepts dual rail or single rail digital PCM inputs.

•

Supports HDB3 or AMI line code.

•

Accepts gapped data streams to support higher rate demultiplexing.

•

Frames to a G.704 2048 kbit/s signal within 1 ms.

•

Frames to the signalling multiframe alignment when enabled.

•

Frames to the CRC multiframe alignment when enabled.

•

Provides loss of signal detection, and indicates loss of frame alignment

(OOF), loss of signalling multiframe alignment and loss of CRC multiframe

alignment.

•

Supports line and path performance monitoring according to ITU-T

recommendations. Accumulators are provided for counting:

•

CRC-4 errors to 1000 per second;

•

Far end block errors to 1000 per second;

•

Frame sync errors to 127 per second; and

•

Line code violations to 8191 per second.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

2

•

Indicates the reception of remote alarm and remote multiframe alarm.

•

Indicates the reception of alarm indication signal (AIS) and time slot 16 AIS.

•

Declares RED and AIS alarms using Q.516 recommended integration

periods.

•

Provides an HDLC/LAPD interface for terminating a data link. Supports

polled, interrupt-driven, or DMA servicing of the HDLC interface.

•

Optionally extracts the data link from timeslot 16 (64 kbit/s), which may be

used to receive common channel signalling, or from any combination of the

national bits in timeslot 0 of non-frame alignment signal frames (4 kbit/s - 20

kbit/s).

•

Provides a two-frame elastic store buffer for jitter and wander attenuation that

performs controlled slips and indicates slip occurrence and direction.

•

Provides channel associated signalling extraction, with optional data

inversion, programmable idle code substitution, and up to 3 multiframes of

signalling debounce on a per-timeslot basis.

•

Provides trunk conditioning which forces programmable trouble code

substitution and signalling conditioning on all timeslots or on selected

timeslots.

•

Optionally provides dual rail digital PCM output signals to allow BPV

transparency. Also supports unframed mode.

•

Supports transfer of received PCM and signalling data to 2048 kbit/s

backplane buses.

The transmitter section:

•

Supports transfer of transmitted PCM and signalling data from 2048 kbit/s

backplane buses.

•

Formats data to create a G.704 2048 kbit/s signal. Optionally inserts

signalling multiframe alignment signal. Optionally inserts CRC multiframe

structure including optional transmission of far end block errors.

•

Optionally accepts dual rail digital PCM inputs to allow BPV transparency.

Also supports unframed mode.

•

Provides channel associated signalling insertion, programmable idle code

substitution, digital milliwatt code substitution, and data inversion on a per

timeslot basis.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

3

•

Provides trunk conditioning which forces programmable trouble code

substitution and signalling conditioning on all timeslots or on selected

timeslots.

•

Supports transmission of the alarm indication signal (AIS), timeslot 16 AIS,

remote alarm signal or remote multiframe alarm signal.

•

Provides an HDLC/LAPD interface for generating a data link. Supports

polled, interrupt-driven, or DMA servicing of the HDLC interface.

•

Optionally inserts the data link into timeslot 16 (64 kbit/s), which may be used

to transmit common channel signalling, or into any combination of the

national bits in timeslot 0 of non-frame alignment signal frames (4 kbit/s - 20

kbit/s).

•

Provides a digital phase locked loop for generation of a low jitter transmit

clock.

•

Provides a FIFO buffer for jitter attenuation and rate conversion in the

transmitter. FIFO full or empty indication allows for bit-stuffing in higher rate

multiplexing applications.

•

Supports HDB3 or AMI line code.

•

Provides analog circuitry for transmitting a G.703 compatible 2048 kbit/s

signal on a 75 Ω coaxial line or a 120 Ω symmetrical line. Digitally

programmable line build out is provided.

•

Provides dual rail or single rail digital PCM output signals.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

4

2

APPLICATIONS

•

E1 ATM Interfaces

•

E1 Frame Relay Interfaces

•

E1 & E3 Multiplexers (MUX)

•

Digital Private Branch Exchanges (DPBX)

•

Digital Access and Cross-Connect Systems (DACS)

•

Electronic Cross-Connect Systems (EDSX)

•

E1 & E3 Test Equipment (TEST)

•

ISDN Primary Rate Interfaces (PRI)

•

E1 Channel Service Units (CSU) and Data Service Units (DSU)

•

SONET/SDH Add/Drop Multiplexers (ADM)

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

5

3

REFERENCES

1. ITU-T Recommendation G.703, - "Physical/Electrical Characteristics of

Hierarchical Digital Networks", Sept. 1991.

2. ITU-T Recommendation G.704, - "Synchronous Frame Structures Used at

Primary and Secondary Hierarchical Levels", Oct. 1991.

3. ITU-T Recommendation G.706, - "Frame Alignment and Cyclic Redundancy

Check (CRC) Procedures Relating to Basic Frame Structures Defined in

Recommendation G.704", Aug. 1991

4. ITU-T Recommendation G.711, - "Pulse Code Modulation (PCM) of Voice

Frequencies", June 1990.

5. ITU-T Recommendation G.732, - "Characteristics of Primary PCM Multiplex

Equipment Operating at 2048 kbit/s", June 1990.

6. ITU-T Recommendation G.735, - "Characteristics of Primary PCM Multiplex

Equipment Operating at 2048 kbit/s and Offering Synchronous Digital Access

at 384 kbit/s and/or 64 kbit/s", July 1990.

7. ITU-T Recommendation G.821, - "Error Performance of an International

Digital Connection Forming Part of an Integrated Services Digital Network",

July 1990.

8. ITU-T Recommendation G.823, - "The Control of Jitter and Wander Within

Digital Networks Which are Based on the 2048 kbit/s Hierarchy", Jan. 1994.

9. ITU-T Recommendation O.151, - "Error Performance Measuring Equipment

For Digital Systems at the Primary Bit Rate and Above", July 1993.

10. ITU-T Blue Book, Recommendation O.162, - "Equipment to Perform in

Service Monitoring on 2048 kbit/s Signals", Vol. IV, Fascicle IV.4, 1988.

11. ITU-T Recommendation Q.506, - "Operations and maintenance functions",

Vol. VI, Fascicle VI.5, 1984.

12. ITU-T Recommendation Q.516, - "Operations and maintenance functions",

Vol. VI, Fascicle VI.5, 1984.

13. Transmission and Multiplexing (TM); Generic Functional Requirements for

SDH Transmission Equipment, Pa rt 1: Generic Processes and Performance",

ETSI DE/TM-1015, November, 1993, Version 1.0.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

6

14. American National Standard for Telecommunications, ANSI T1.102-1992 -

"Digital Hierarchy - Electrical Interfaces".

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

7

4

APPLICATION EXAMPLES

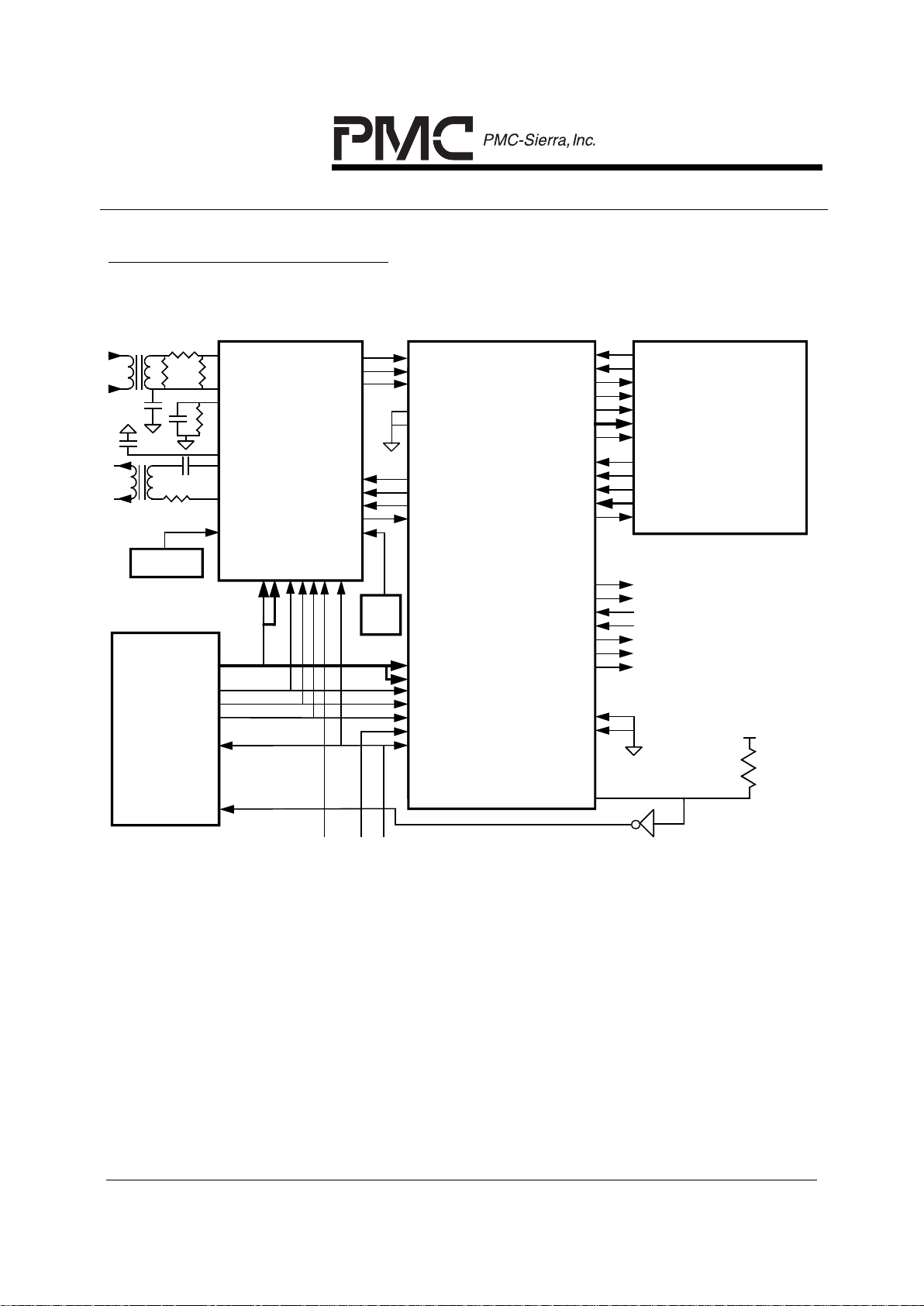

Figure 1 - ATM E1 and DS1 User Network Interface

+5V

AD[7:0]

ALE

RDB

WRB

RESB

INT

Intel/

Motorola

Single Chip

µP

RAS

REF

RRC

TC

TAP

TAN

BRPCM

BRFPO

RCLKO

BTPCM

BTFP

BTCLK

TCLKO

TCLKI

PM 6341

E1XC E1

Transceiver

PM7345

S/UNI-PDH

SATURN

User-Network

Interface for

PDH

RPOS/RDAT

RNEG/ROHM

RCLK

TIOHM

C13/CADD

TPOS/TDAT

TNEG/TOHM

TCLK

TICLK

From Master

reset circuitry

From chip select

decode circuitry

49.152 MHz

RX

CELL

INTERFACE

TX

CELL

INTERFACE

ATM/SMDS

Ad aptation

Layer

Processor

(SA R o r

policing

functions)

RRDENB

FRDB/RFCLK

RSOC

REOH

REOC

FRDATA[7:0 ]

RFIFOE/RCA

TWRENB

FWR B/TFCLK

TSO C

FW DATA[7 :0]

TFIFOFB /TCA

TPO H CLK

TPO H FP

TPO HINS

TPO H

RPOHCLK

RPOHFP

RPOH

TOHINS

TOH

INTB

A[7:0]

D[7:0]

ALE

RDB

WRB

CSB

RSTB

XCLK

2.048

MHz

A[8:0

]

D[7:0]

ALE

RDB

WRB

CSB

RS

TB

Figure 1 shows the PM6341 E1XC used with the PM7345 Saturn User Network

Interface for PDH (S/UNI-PDH™) to implement an ATM wide area User Network

Interface (UNI) or Network Node Interface (NNI).

In this example, the E1 LIU and framing functions are provided by the PM6341

E1XC. The combination of the E1XC with the S/UNI-PDH allows both PLCP

formatted E1 signals and ITU-T G.804 compliant E1 signals to be processed.

The G.804 specification defines ATM cell mappings for a variety of transmission

formats, including the 2.048 Mbit/s E1 format.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

8

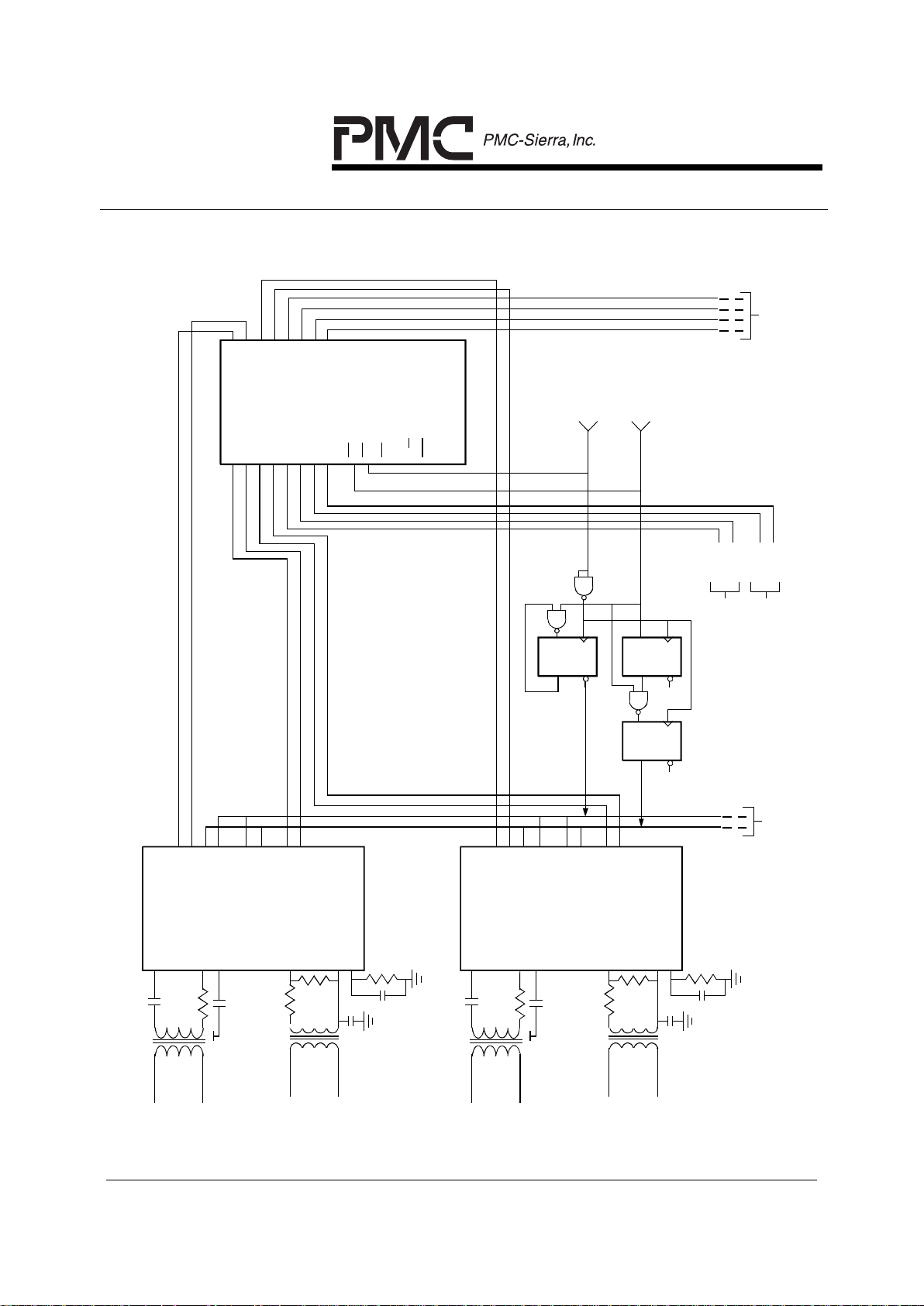

Figure 2 - DS0 Cross-connect

E-

1

Tr

a

n

s

mi

t

A

V

D

+

S

T

i0

S

T

i1

S

T

i2

S

T

i3

S

T

i4

S

T

i5

S

T

i6

S

T

i7

F

0

i

C

4

i

S

T

o

0

S

T

o

1

S

T

o

2

S

T

o

3

S

T

o

4

S

T

o

5

S

T

o

6

S

T

o

7

C

S

T

o

OD

E

C

S

D

S

R/

W

D

T

A

A[

5

:0

]

D[7

:0

]

MT8980 D X

PM6341 E1XC

B

T

P

C

M

B

T

S

IG

B

T

F

P

B

T

C

L

K

BR

C

LK

BR

F

P

I

BR

P

C

M

BR

S

IG

BR

F

PO

T

A

P

T

A

N

T

C

R

A

S

RE

F

RR

C

E-

1

Re

c

e

iv

e

A

V

S

A

V

S

4.0

96

MH

z

D

Q

Q

B

to

t

ra

ns

c

ei

ve

rs

#3

&

4

to

t

ra

ns

c

ei

ve

rs

#3

&

4

#

1

BR

P

C

M

BR

S

IG

BR

P

C

M

BR

S

IG

fr

om

t

ra

ns

ce

iv

e

r

#3

fr

om

t

ra

ns

ce

iv

e

r

#4

PM6341 E1XC

B

T

P

C

M

B

T

S

IG

B

T

F

P

B

T

C

L

K

BR

C

LK

BR

F

P

I

BR

P

C

M

BR

S

IG

BR

F

PO

T

A

P

T

A

N

T

C

R

A

S

RE

F

RR

C

#

2

E-

1

Re

c

e

iv

e

A

V

S

A

V

S

Sy

st

e

m

Fr

am

e

Pu

lse

D

Q

Q

B

D

Q

Q

B

Gl

u

e

log

ic

c

a

n

b

e

im

pl

e

me

n

ted

us

in

g

o

ne

74

HC

T

00

an

d

o

ne

74

H

CT

17

5

p

a

ck

.

2.

0

4

8M

H

z

E-

1

Tr

a

n

s

mi

t

A

V

D

+

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

9

Figure 2 is an application utilizing 4 PM6341 E1XC chips and a Mitel MT8980

Digital Time/Space Switch to implement a simple DS0 cross-connect. An

alternate architecture could use two MT8980, one as a voice switch and the

other as a signalling switch, and 8 E1XCs to cross-connect 8 E1's. ( Note: a true

implementation would require redundancy in the switch core.)

The "system frame pulse" signal is stretched through the two D-FF into a pulse

of 488ns duration, which is used to frame align the data out of each E1XC

through the elastic store and to provide frame alignment indication to the

transmitters. The raw system frame pulse signal is used to indicate frame

alignment synchronization to the MT8980. Another D-FF is configured as a

toggle to generate a 2.048MHz clock from the system 4.096MHz clock source,

synchronized to the system frame pulse.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

10

5

BLOCK DIAGRAM

XCLK/VCL K

BRFPI

BRCLK

RCLKI

RDP/RDD/

SDP

RDN/RLCV/

SDN

RAS

REF

RRC

TCL KI

BTPCM/BTDP

BTCLK

BTSIG/BTDN

INTB

D[7:0]

A[7:0]

RDB

WRB

CSB

ALE

RSTB

BTFP

BRPCM/BRDP

BRSIG/BRDN

BRFPO

RCLKO

RFP

RDPCM/RPCM

RDLC LK/

RDLEOM

RDLSIG/

RDLINT

RFDL

HDLC

Receiver

TDP /TD D

TCL KO

TDN /TFL G

TAN

TAP

TDL S IG/

TDL INT

TDLC L K /

TDLU D R

TC

MPIF

Micro-

Processor

Inter face

Internal

Bus

RECEIVER

TRANSMITTER

BTIF

Backplane

Transmit

Inter face

TRAN

Tra nsmitte r:

Frame Generation,

Alarm Insertion,

Trunk Conditioning

Line Coding

TOPS

Timing Options

DJAT

Digital Jitter

Attenuator

XPLS

Analog Pulse

Generator

DTIF

Digital

Transmit

Interface

PCSC

Per-channel

Controller:

Sign alling, Idle

Control

XFDL

HDLC

Transm itter

RSLC

Analog

Pulse Slicer

DRIF

Digital

Receive

Interface

CDRC

Clock and

Data

Recovery

FRMR

Framer:

Frame

Alignment,

Alarm

Detection

PMON

Performance

Monitor

Counters

ELST

Elastic

Store

SIGX

Signalling

Extractor,

Trunk

Conditioner

BRIF

Backplane

Receive

Interface

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

11

6

DESCRIPTION

The PM6341 E1 Framer/Transceiver (E1XC) is a feature-rich device suitable for

use in many E1 systems (such as CSU, DSU, CH BANK, MUX, DPBX, DACS,

and ESDX) with a minimum of external circuitry. The E1XC is software

configurable, allowing feature selection without changes to external wiring.

On the receive side, the E1XC recovers clock and data and can be configured to

frame to a basic G.704 2048 kbit/s signal or also frame to the signalling

multiframe alignment signal and the CRC multiframe alignment signal.

Analog circuitry is provided to allow direct reception of a G.703 2048 kbit/s signal

with up to 6 dB of loss by using only an external transformer and passive

components.

The E1XC also supports detection of various alarm conditions such as loss of

signal, loss of frame, loss of signalling multiframe, loss of CRC multiframe, and

reception of remote alarm signal, remote multiframe alarm signal, alarm

indication signal, and timeslot 16 alarm indication signal. The E1XC detects and

indicates the presence of remote alarm and AIS patterns and also integrates red

and AIS alarms as per industry specifications.

Performance monitoring with accumulation of CRC-4 errors, far end block errors,

framing bit errors, and line code violation is provided. The E1XC also detects

and terminates HDLC messages on a data link. The data link may be extracted

from timeslot 16 and used for common channel signalling or may be extracted

from the national bits.

An elastic store for slip buffering and adaptation to backplane timing is provided,

as is a channel associated signalling extractor that supports signalling debounce,

signalling freezing, idle code substitution, and data inversion on a per-timeslot

basis. Receive side data and signalling trunk conditioning is also provided.

On the transmit side, the E1XC generates framing for a basic G.704 2048 kbit/s

signal, or framing can be optionally disabled. The signalling multiframe alignment

signal may be optionally inserted and the CRC multiframe structure may be

optionally inserted.

Internal analog circuitry allows direct transmission of a G.703 2048 kbit/s signal

into either a 75 Ω or 120 Ω line using only an external transformer.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

12

Channel associated signalling insertion, idle code substitution, digital milliwatt

tone substitution, and data inversion on a per-timeslot basis is also supported.

Transmit side data and signalling trunk conditioning is provided.

HDLC messages on a data link can be transmitted. The data link may be

inserted into timeslot 16 and used for common channel signalling or may be

inserted into the national bits. The E1XC can generate a low jitter transmit clock

and provides a FIFO for transmit jitter attenuation. When not used for jitter

attenuation, the full or empty status of this FIFO is made available to facilitate

higher order multiplexing applications by controlling bit-stuffing logic.

Interfaces include both a parallel microprocessor port for controlling the

operation of the device and a serial PCM interface that allows 2048 kbit/s

backplanes to be directly supported. Tolerance of gapped clocks allows other

backplane rates to be supported with a minimum of external logic.

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

13

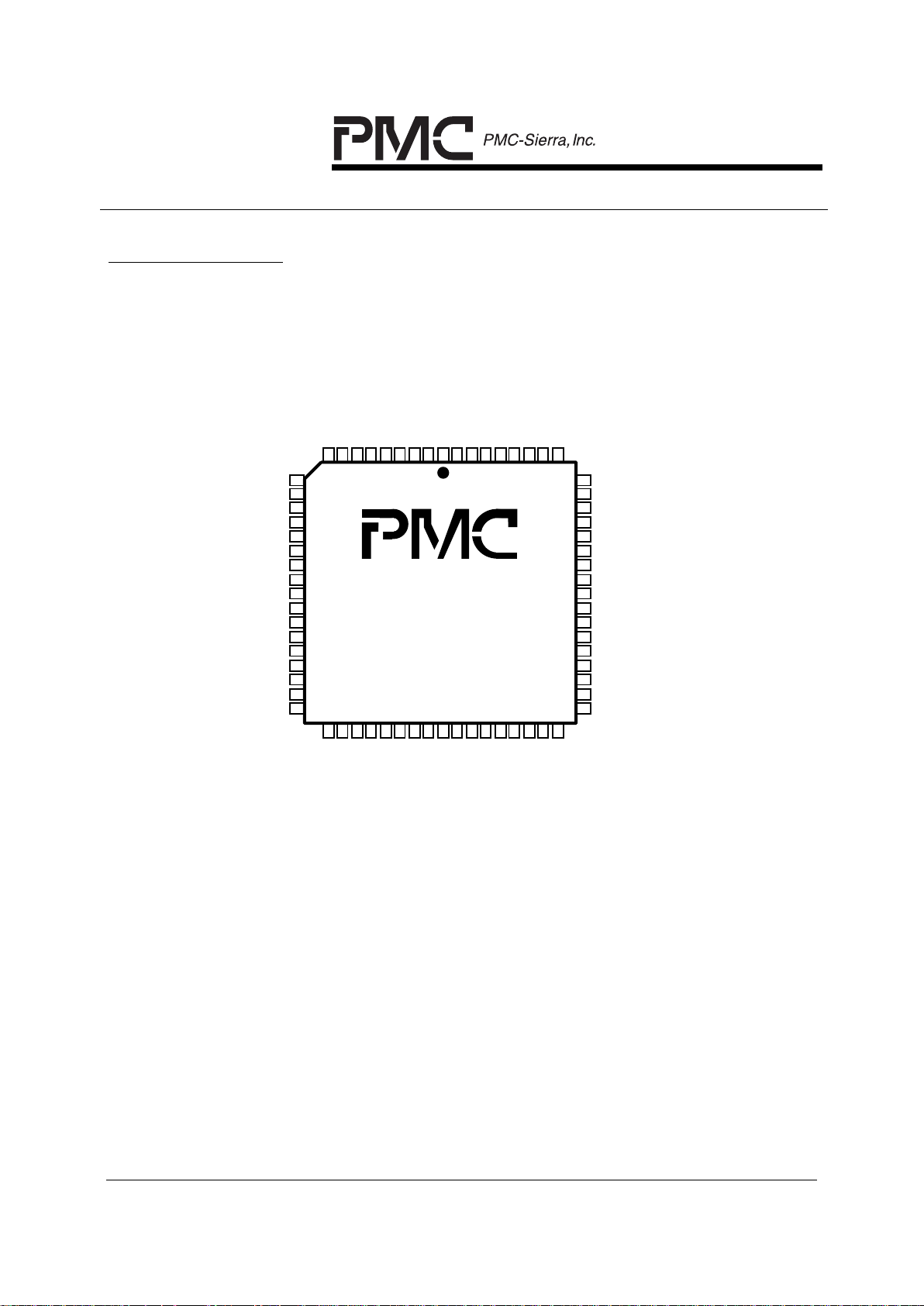

7

PIN DIAGRAM

Figure 3 - 68 Pin PLCC (Q-Suffix):

PM6341

9 8 7 6 5 4 3 2 1 6867666564636261

XCLK/VCLK

BTPCM/BTDP

BTSIG/BTDN

BTFP

BTCLK

TCLKI

TCLKO

TDP/TDD

VSSO[0]

VDDO[0]

TDN/TFLG

TDLCLK/TDLUDR

TDLSIG/TDLINT

TAVS

TAVD

TAN

VDDO[3]

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

ALE

BRFPI

BRCLK

RFP

RDLCLK/RDLEOM

RDLSIG/RDLINT

RCLKO

RDPCM/RPCM

VSSO[2]

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

CSB

RSTB

INTB

D[0]

D[1]

D[2]

D[3]

VSSO[1]

VSSI[0]

VDDI[0]

VDDO[1]

D[4]

D[5]

D[6]

D[7]

RDB

WRB

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

VSSO[3]

TC

TAP

RAVD

RAVS

RAS

RRC

REF

VSSI[1]

VDDI[1]

RCLKI

BRFPO

BRPCM/BRDP

BRSIG/BRDN

RDP/RDD/SDP

RDN/RLCV/SDN

VDDO[2]

(TOP VIEW)

PM6341 E1XC

DATA SHEET

PMC-910419 ISSUE 8 E1 FRAMER/TRANSCEIVER

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

14

Figure 4 - 80 Pin PQFP (R-suffix):

(TOP VIEW)

PM6341

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

NC

CSB

RSTB

INTB

D[0]

D[1]

D[2]

D[3]

VSSO[1]

VSSI[0]

VDDI[0]

VDDO[1]

D[4]

D[5]

D[6]

D[7]

RDB

WRB

NC

NC

NC

NC

VSSO[3]

TC

TAP

RAVD

RAVS

RAS

RRC

REF

VSSI[1]

VDDI[1]

RCLKI

BRFPO

BRPCM/BRDP

BRSIG/BRDN

RDP/RDD/SDP

RDN/RLCV/SDN

VDDO[2]

NC

22232425262728293031323334353637383940

21

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

ALE

BRFPI

BRCLK

RFP

RDLCLK/RDLEOM

RDLSIG/RDLINT

RCLKO

RDPCM/RPCM

VSSO[2]

NC

NC

NC

79787776757473727170696867666564636261

80

NC

XCLK/VCLK

BTPCM/BTDP

BTSIG/BTDN

BTFP

BTCLK

TCLKI

TCLKO

TDP/TDD

VSSO[0]

VDDO[0]

TDN/TFLG

TDLCLK/TDLUD

R

TDLSIG/TDLINT

TAVS

TAVD

TANNCVDDO[3]

NC

Loading...

Loading...