PMC PM3386 Datasheet

Dual Gigabit Ethernet Controller

•

FEATURES

• Two port full-duplex Gigabit Ethernet

Controller with an industry standard

POS-PHY Level 3™ system interfac e.

• Provides direct connection to optics.

• Connection to copp er Gig ab it Eth ern et

physical layer devices via two GMII

interfaces.

• Incorporates dual SERDES,

compatible to IEEE 802.3 1998 PMA

physical layer specification.

• Supports dual IEEE 802.3 -1998

GMII/TBI interfaces for connection to

copper Gigabit Ethernet physical layer

devices.

• Provides dual standard IEEE 802.3

Gigabit Ethernet MACs for frame

verification.

• Provides on-chip data recovery and

clock synthe sis.

• Provides eight unicast exact-match

address filters to filter fram es based o n

DA, SA, or VID.

• Each address filter can indicate

whether to accept or discard based on

a match.

• Provides 64-group multicast address

filter.

• Internal 16 kbyte TX and 64 kbyte RX

FIFOs to accommodate system

latencies.

• SATURN® compatible interface for

Packet-Over-SONET Physical Layer

and Link Laye r devices Level 3 (POSPHY Level 3 system interface).

• Line side loopback for system level

diagnostic capability.

• 16 bit generic micr oprocessor in terface

for device initi alization, control, r egister

and per port statistics access.

GIGABIT ETHERNET MAC

• Verifies frame integrity (FCS and

length checks).

• Errored frames can be filtered or

passed to a higher layer device.

• Automatic Base Page Autonegot iation,

extended Autonegotiation (Next Page)

supported via host.

• Egress Ethernet frame encapsulation

(pad to minimum size, add preamble,

IFG and CRC generation).

•

Supports Ethernet 2.0, IEEE 802.3 LLC

and IEEE 802.3 SNAP/LLC encoding

formats, and VLAN tagged frames.

Minimum frame size 64 b ytes. Supports

jumbo frames up to 9.6 kbytes.

• Supports big endian data formats.

• Programmable inter-packet gap (IPG).

• Loopback for diagnostic capability

through GMAC.

FLOW CONTROL

• Option to support IEEE 802.3-1998

flow control at each Ethernet port.

• Programmable watermarks for

full/empty FIFO conditions.

• Automatic generation of pause frames

based on FIFO fill levels.

• Upper layer device can flow control

Ethernet ports using side-band or host

signaling to cause generation of a

Pause frame.

• Provides per-port side-band Pause

state indication for upstream devices.

• Loss-less flow control on all valid

frames up to 9.6 kbytes.

STATISTICS

• 40 bit counters are used to ensure

rollover compliance with

IEEE 802.3-1998.

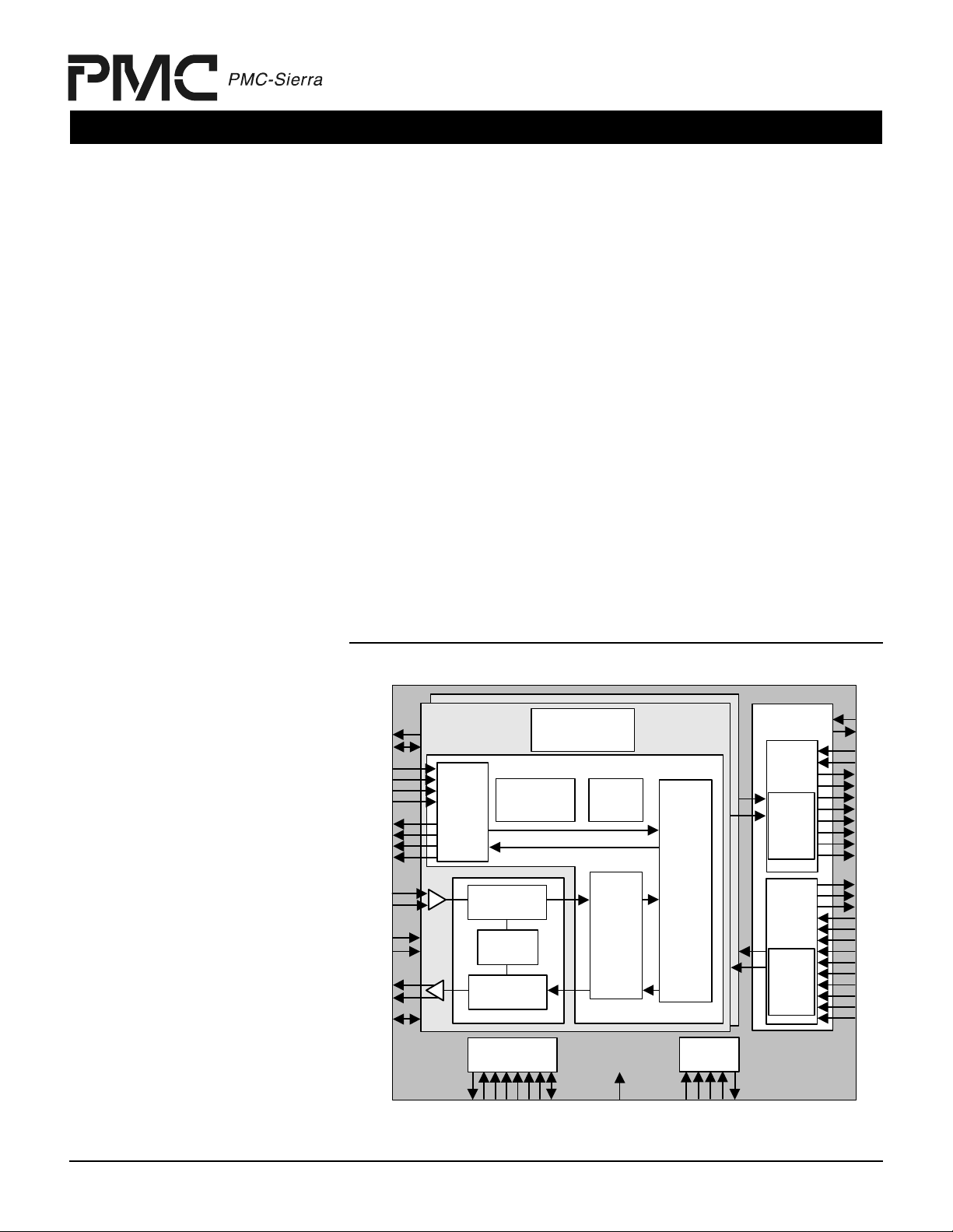

BLOCK DIAGRAM

MDC

MDIO

RX_CLK

RX_DV

RX_ER

RXD [7:0]

GTX_CLK

TX_EN

TX_ER

TXD [7:0]

RXD +/-

SD

CLK125

TXD +/-

ATP[3:0]

Ethernet Statistics

Enhanced Gigabit MAC

Flow Ctrl /

GMII

Interface

Auto-Negotiation

Data Recovery/

Serial to Parallel

PLL Clock

Multiply

Parallel to Serial

SERDES PCS MAC

Microprocessor

Interface

ALE

CSB

RDB

INTB

WDB

RSTB

A [11:0]

Address

Filtering

8B/10B

Encoder/

Decoder

D [15:0]

PM3386

S/UNI®-2xGE

• Minimum 58 minutes before rollover.

• Provides statistic counters to support

SNMP and RMON implementations.

POS-PHY LEVEL 3 SYSTEM INTERFACE

• Standard OC-48 bandwidth

Packet/Cell interface.

Compatible with PMC-Sierra devices

•

supporting POS-PHY L ev el 3, in clud ing:

• PM5381 S/UNI®-2488 ATM and

POS physical layer device.

• PM5358 S/UNI®-4x622 singl e

channel OC-48c device with

integrated analog.

• PM7390 S/UNI-MACH-48 multi-

service access device for

channelized interfaces .

• PM5382 S/UNI-16x155 sixteen

channel OC-3c framer with

integrated analog and POS-PHY

Level 3 and UTOPIA Level 3

interface.

• POS-PHY Level 3 pr ovides co nnection

to upper layer device at data rates up

to 2,400 Mbit/s.

POS-PHY

Level 3

Ingress

Interface

POS

PHY

Ingress

FIFO

Gigabit

Media

Access

Controller

JTAG

TDI

TCK

TMS

TRSTB

PMD_SEL [1:0]

Egress

Interface

POS

PHY

Egress

FIFO

TDO

PAUSE [1:0]

PAUSED [1:0]

RFCLK

RENB

RDAT[31:0]

RMOD[1:0]

RPRTY

RVAL

RSOP

REOP

RERR

RSX

DTPA[1:0]

STPA

PTPA

TADR

TFCLK

TENB

TDAT[31:0]

TMOD[1:0]

TPRTY

TSOP

TEOP

TERR

TSX

PMC-1991223 (R4) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2001

Dual Gigabit Ethernet Controller

Preliminary PM3386 S/UNI®-2xGE

• Supports point-to-point POS-PHY

Level 3 applications.

• 32 bit data at 104 MHz.

• In-band addressing for dual port PHY

support.

PACKAGING

• Packaged in a 352-pin UBGA.

•

Implemented in low power 1.8 V CMOS

technology with 3.3 V compatible I/O.

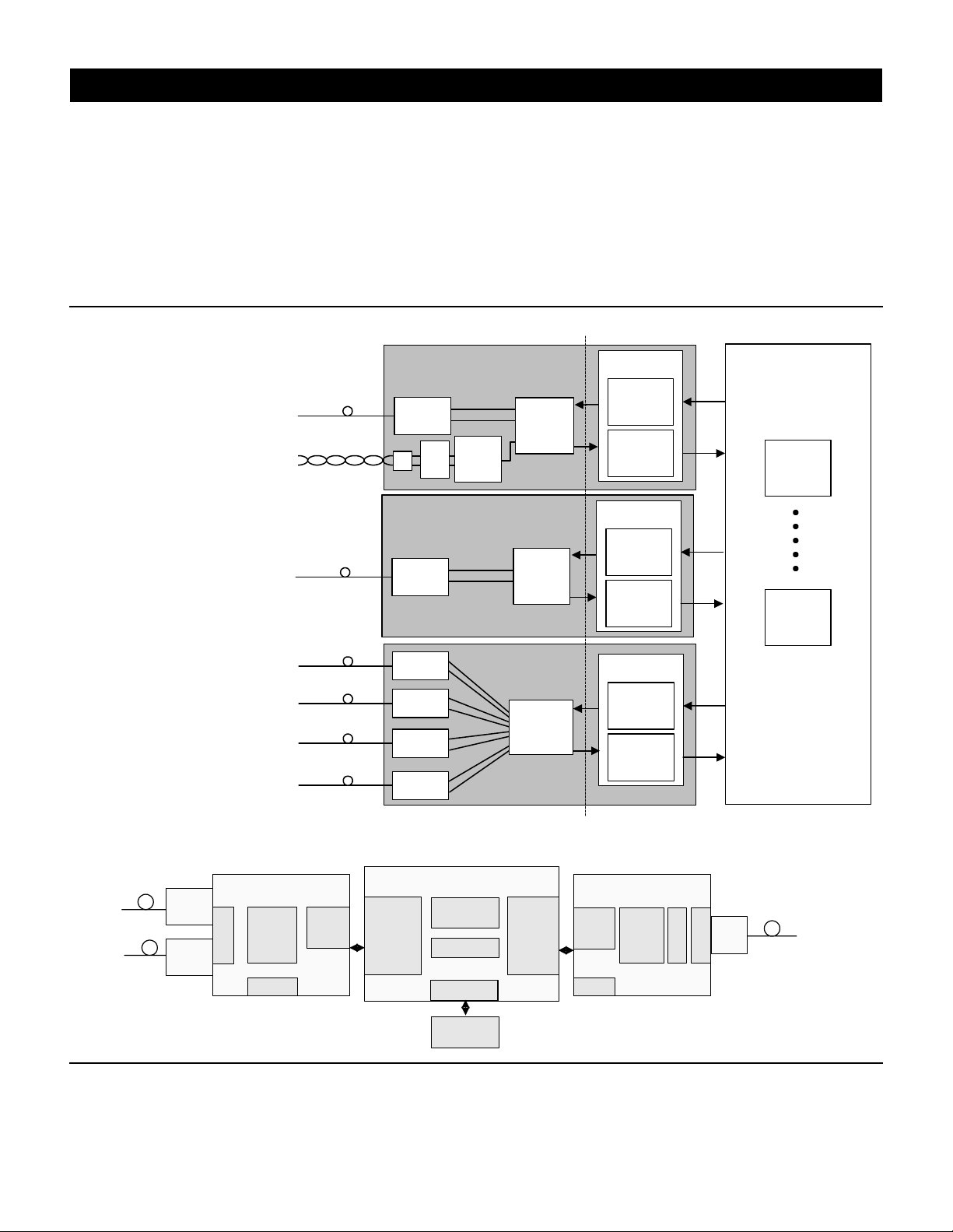

TYPICAL APPLICATIONS

SAMPLE LINE CARDS LINKED

WITH POS-PHY LEVEL 3

INTERFACE

Gigabit Ethernet

Gigabit Ethernet

• Industrial temperatu re r ange (- 40 °C to

+85 °C).

• Provides a standard 5 signal P1149.1

JTAG test por t for boundary scan

board test purposes.

APPLICATIONS

•

POS-PHY Level 3 provides consistent

system interface for mu ltiple P H Y typ es .

Line Card # 1

Twisted Pair

OC-48

Optical

Transceiver

Optical

Transceiver

Mag

TXD +/-

RXD +/-

Copper

GE PHY

TXD + /-

RXD +/-

S/UNI-2xGE

GMII

Line Card # 2

PM5381

S/UNI-2488

PM3386

• Edge and Core Routers.

• Multi-Service Switches.

• SONET/SDH Transport Equipment.

• Ethernet over SONET uplinks.

• Gigabit Ethernet ports for Optical

Cross Connects.

• Gigabit Ethernet Access IADs.

• Gigabit Ethe rnet Test Equipment.

POS-PHY

Level 3 Bus

Upper Layer

Device(s)

Scheduler

Classification

Forwarding

Upper Layer

Device(s)

Scheduler

Classification

Forwarding

Switch Fabric

Switch Fabric

Device

Switch Fabric

Device

ETHERNET OVER SONET

SFF

Optics

Serdes

SFF

Optics

Head Office:

PMC-Sierra, Inc.

8555 Baxter Place

Burnaby, B.C. V5A 4V7

Canada

Tel: 604.415.6000

Fax: 604.415.6200

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE

S/UNI 2xGE

Layer 2

GMAC

Line/

(x2)

Section

Statistics

Optical

UL3/

UL3/PL3

PL3

32-Bit

32-

Master

MASTER

Transceiver

Optical

Transceiver

Optical

Transceiver

Optical

Transceiver

OC-12

OC-12

OC-12

OC-12

OPTIONAL

RAM

PL3

UL3/PP

Slave

L3

SLAVE

APS

To order documentation,

send email to:

document@pmc-sierra.com

or contact the head office,

Attn: Document Coordinator

I/F FPGA

I/F FPGA

EOS Function

EOS

FIFO

RAM I/F

Optional Ram

Line Card # n

PM5380

S/UNI-4x622

Upper Layer

Device(s)

Scheduler

Classification

Forwarding

S/UNI 2488

PL3

UL3/PL3

PL3

32-Bit

32-Bit

Master

Slave

APS

Line/

Section

SONET

Line/

Section

All product documentation is available

on our web site at:

http://www.pmc-sierra.com

For corpo rate information,

send email to:

info@pmc-sierra.com

RAM

UL3/PP

L3

Path O/H

SLAVE

SFF

Optics

Serdes

PMC-1991223 (R4)

© Copyrigh t PMC-Sierra,

Inc. 2001. All rights reserved.

SATURN and S/UNI are

registered trademarks and

POS-PHY Level 3 is a

trademark of PMC-Sierra,

Inc.

Loading...

Loading...