Page 1

PMC

FEATURES

Pm25LV512 / Pm25LV010

512 Kbit / 1 Mbit 3.0 Volt-only , Serial Flash Memory

With 25 MHz SPI Bus Interface

Single Power Supply Operation

- Low voltage range: 2.7 V - 3.6 V

• Memory Organization

- Pm25L V512: 64K x 8 (512 Kbit)

- Pm25L V010: 128K x 8 (1 Mbit)

Cost Effective Sector/Block Architecture

- Uniform 4 Kbyte sectors

- Uniform 32 Kbyte blocks (8 sectors per block)

- Two blocks with 32 Kbytes each (512 Kbit)

- Four blocks with 32 Kbytes each (1 Mbit)

- 128 pages per block

Serial Peripheral Interface (SPI) Compatible

- Supports SPI Modes 0 (0,0) and 3 (1,1)

High Performance Read

- 25 MHz clock rate (maximum)

Page Mode for Program Operations

- 256 bytes per page

Block Write Protection

- The Block Protect (BP1, BP0) bits allow part or entire

of the memory to be configured as read-only.

Hardware Data Protection

- Write Protect (WP#) pin will inhibit write operations

to the status register

• Page Program (up to 256 Bytes)

- Typical 2 ms per page program time

• Sector, Block and Chip Erase

- Typical 40 ms sector/block/chip erase time

Single Cycle Reprogramming for Status Register

- Build-in erase before programming

High Product Endurance

- Guarantee 100,000 program/erase cycles per single

sector (preliminary)

- Minimum 20 years data retention

Industrial Standard Pin-out and Package

- 8-pin JEDEC SOIC

- 8-contact WSON

- Optional lead-free (Pb-free) packages

GENERAL DESCRIPTION

The Pm25L V512/010 are 512 Kbit/1 Mbits 3.0 V olt-only serial Flash memories. These devices are designed to use

a single low voltage, range from 2.7 Volt to 3.6 Volt, power supply to perform read, erase and program operations.

The devices can be programmed in standard EPROM programmers as well.

The device is optimized for use in many commercial applications where low-power and low-voltage operation are

essential. The Pm25L V512/010 is enabled through the Chip Enable pin (CE#) and accessed via a 3-wire interface

consisting of Serial Data Input (Sl), Serial Data Output (SO), and Serial Clock (SCK). All write cycles are completely self-timed.

Block Write protection for top 1/4, top 1/2 or the entire memory array (1M) or entire memory array (512K) is enabled

by programming the status register. Separate write enable and write disable instructions are provided for additional

data protection. Hardware data protection is provided via the WP pin to protect against inadvertent write attempts

to the status register. The HOLD pin may be used to suspend any serial communication without resetting the serial

sequence.

The Pm25L V512/010 are manufactured on PMC’s advanced nonvolatile CMOS technology, P-FLASH™. The devices are offered in 8-pin JEDEC SOIC and 8-contact WSON packages with operation frequency up to 25 MHz.

Programmable Microelectronics Corp.

1

Issue Date: February, 2004, Rev: 1.4

Page 2

PMC Pm25LV512/010

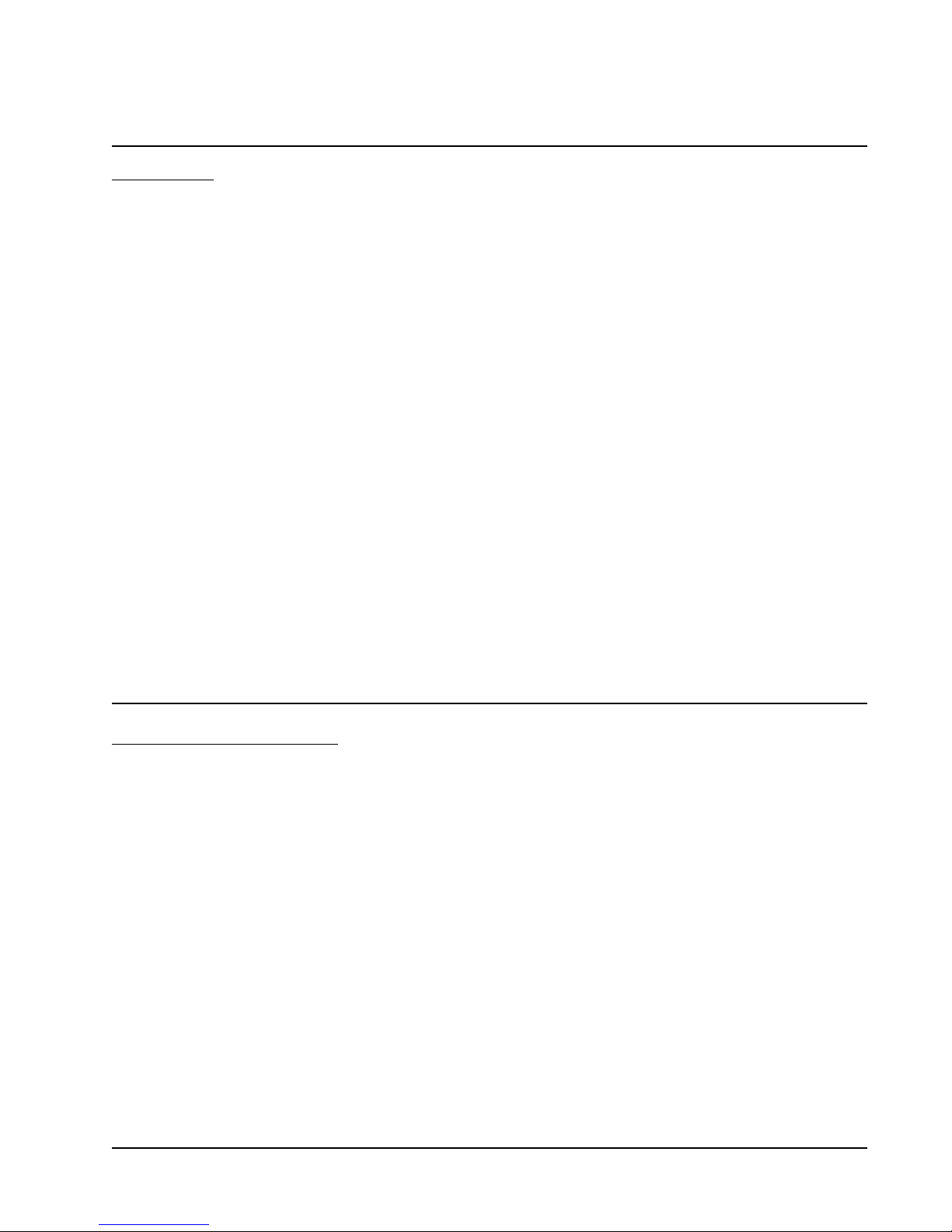

CONNECTION DIAGRAMS

CE#

SO

WP#

GND

2

3

4

8-Pin SOIC

PIN DESCRIPTIONS

LOBMYSEPYTNOITPIRCSED

#ECTUPNI

KCSTUPNIkcolCataDlaireS

ISTUPNItupnIataDlaireS

81

Vcc

7

HOLD#

6

SCK

5

SI

CE#

SO

WP#

GND

1

2

Top View

3

4

8

7

6

5

Vcc

HOLD#

SCK

SI

8-Contact WSON

rofseirtiucriclanretnis'ecivedehtsetavitcawolseog#EC:elbanEpihC

otnisehctiwsdnaecivedehtstcelesedhgihseog#EC.noitarepoecived

tonsiecivedehtnehW.noitpmusnocrewopehtecuderotedomybdnats

ehtdna,)lS(niptupnilairesehtaivdetpeccaebtonlliwatad,detceles

.etatsecnadepmihgihaniniamerlliw)OS(niptuptuolaires

OSTUPTUOtuptuOataDlaireS

DNGdnuorG

ccVylppuSrewoPeciveD

#PWTUPNI

#DLOHTUPNI

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

.ecneuqeslairesehtgnitteser

2

.detibihnieraretsigersutatsehtotsnoitarepoetirw

tuohtiwecivedretsamehthtiwnoitacinummoclairesesuaP:dloH

lla,"1"sitibNEPWdnawolotthguorbnip#PWehtnehW:tcetorPetirW

Page 3

PMC Pm25LV512/010

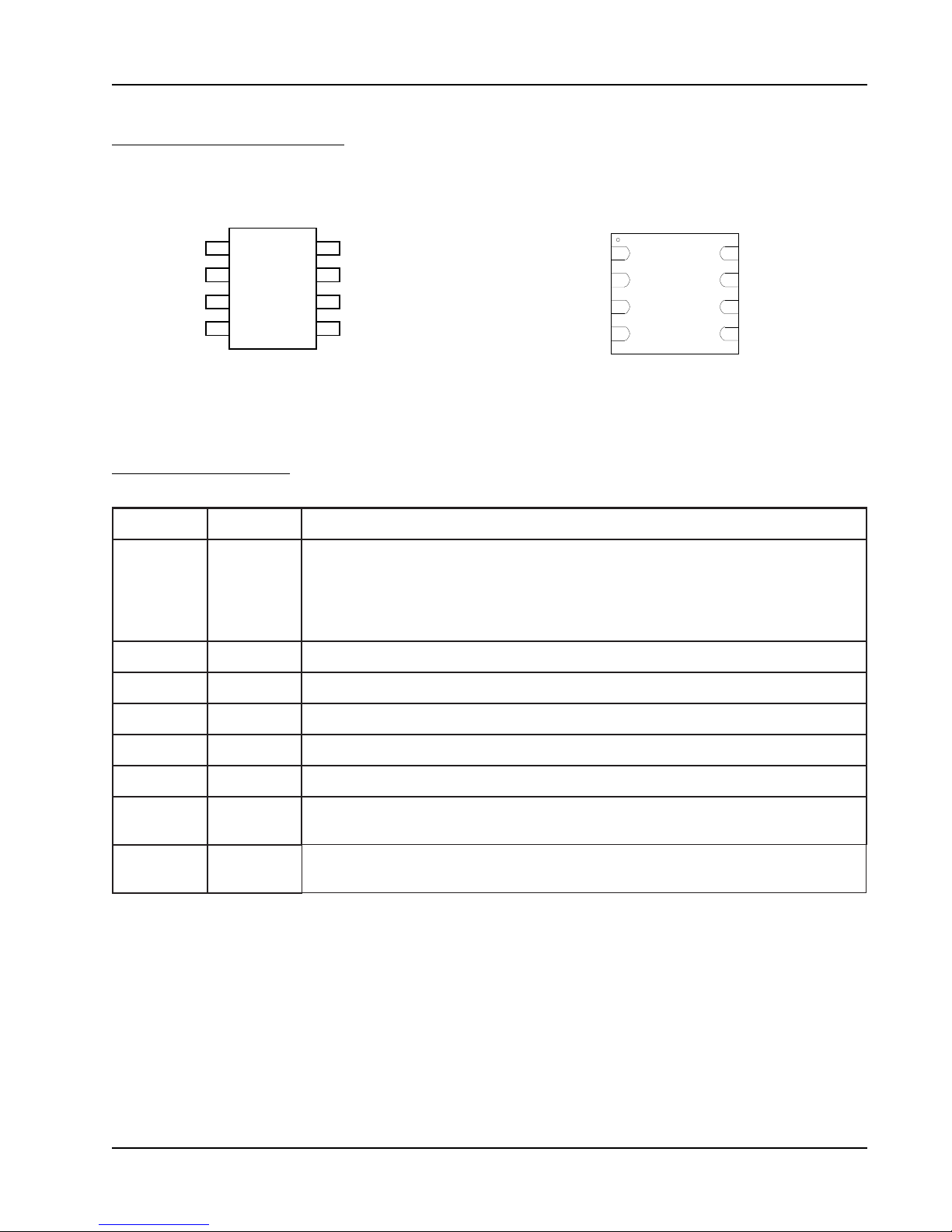

PRODUCT ORDERING INFORMATION

Pm25LVxxx -25 S C E

Environmental Attribute

E = Lead-free (Pb-free) Package

Blank = Standard Package

Temperature Range

C = Commercial (0°C to +85°C)

Package Type

S = 8-pin SOIC (8S)

Q = 8-contact WSON (8Q)

Operating Speed

25 MHz

PMC Device Number

Pm25L V512 (512 Kbit)

Pm25L V010 (1 Mbit)

Part Number Operating Frequency (MHz) Package Temperature Range

Pm25LV512-25SCE

Pm25LV512-25SC

Pm25LV512-25Q CE

Pm25LV010-25SCE

Pm25LV010-25SC

Pm25LV010-25Q CE

25

25

8S

8Q

8S

8Q

Commercial

o

C to + 85oC)

(0

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

3

Page 4

PMC Pm25LV512/010

y

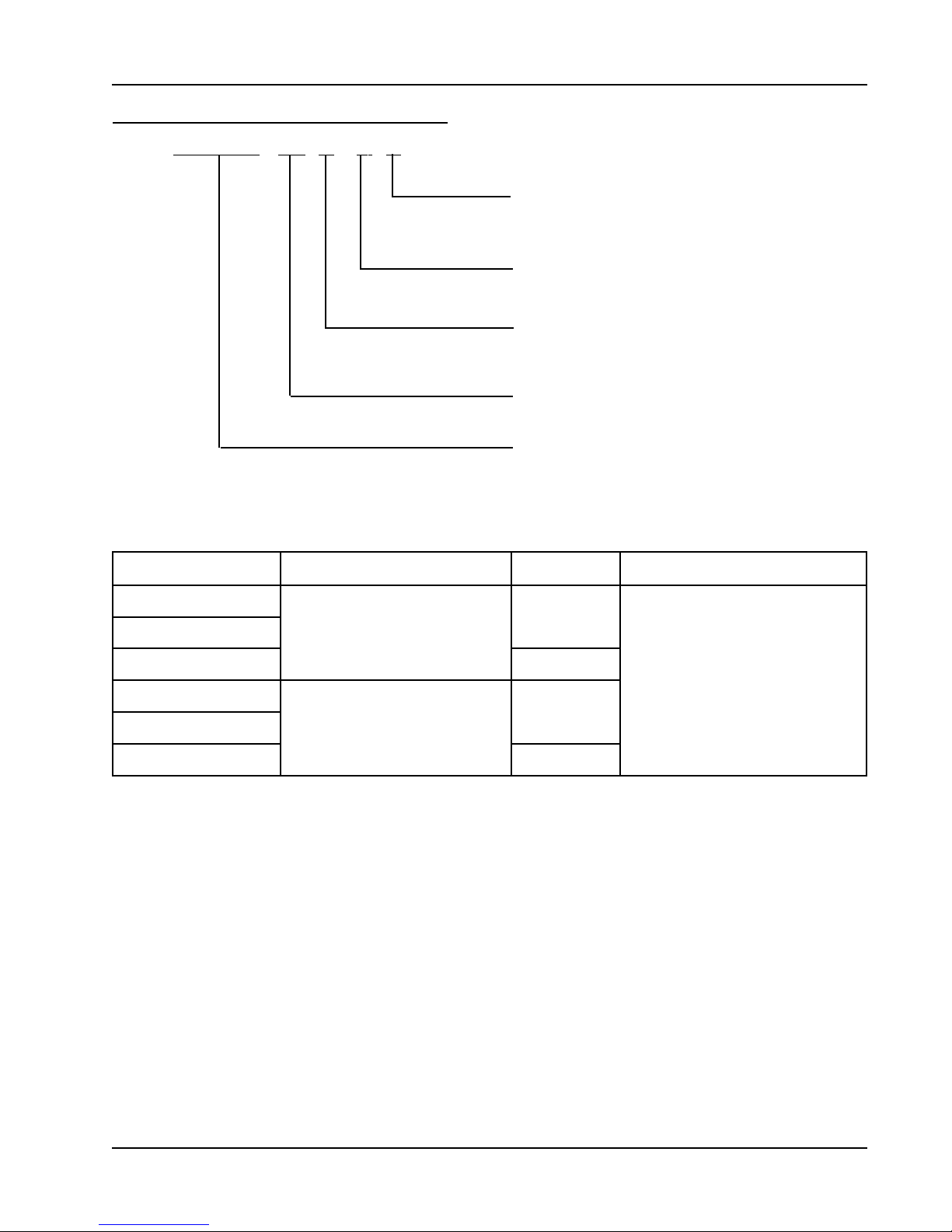

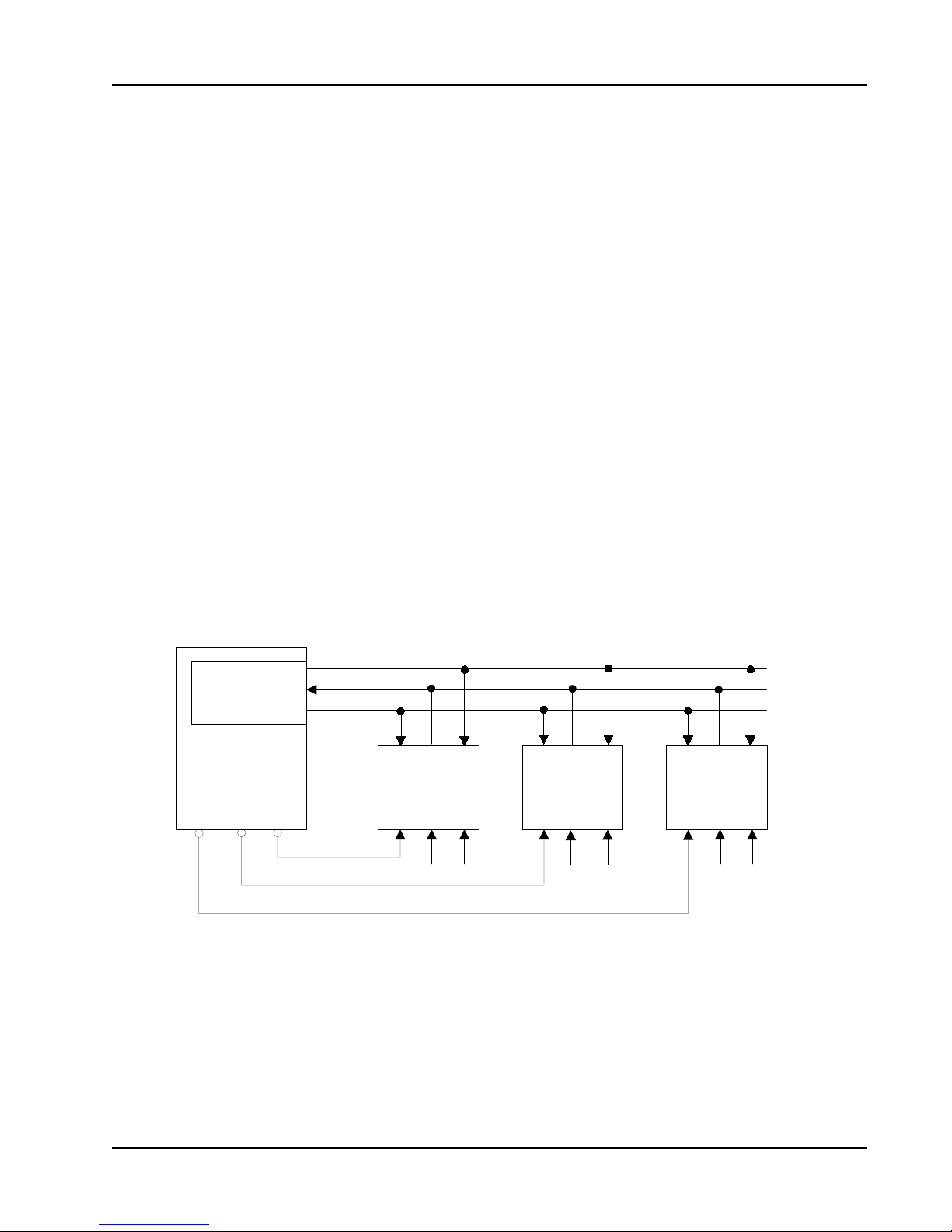

BLOCK DIAGRAM

SPI Chip Block Diagram

High Voltage

Generator

Control Logic

Instruction Decoder

Serial /Parallel convert Logic

Address Latch

& Counter

Y-DECODER

2KBit Page Buffer Status

Register

Memory Arra

X-DECODER

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

4

Page 5

PMC Pm25LV512/010

g

SERIAL INTERFACE DESCRIPTION

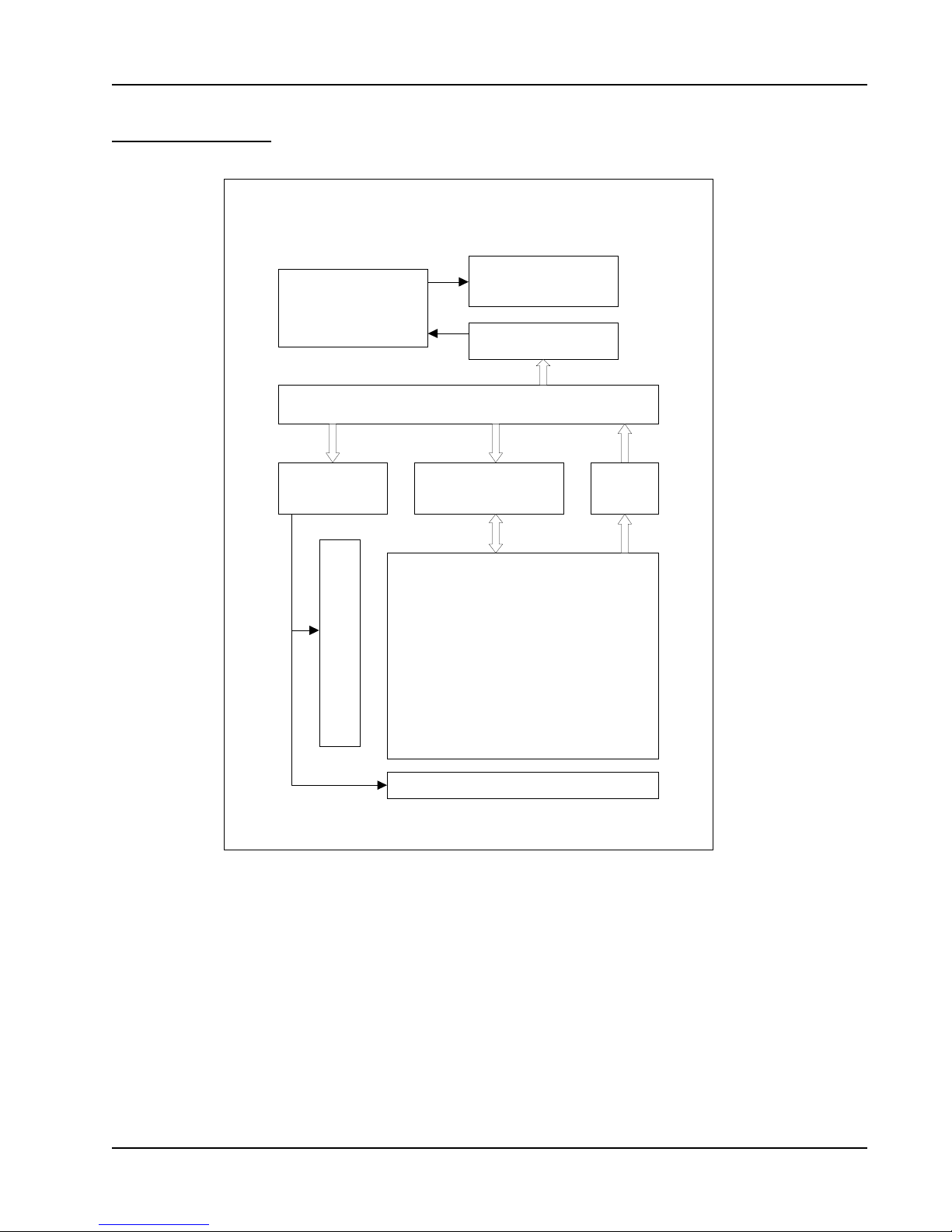

Pm25L V512/010 can be driven by a microcontroller on the SPI bus as shown in Figure 1. The serial communication

term definitions are in the following section.

MASTER: The device that generates the serial clock.

SLA VE: Because the Serial Clock pin (SCK) is always an input, the Pm25L V512/010 always operates as a slave.

TRANSMITTER/RECEIVER: The Pm25L V512/010 has separate pins designated for data transmission (SO) and

receptio n (S l).

MSB: The Most Significant Bit (MSB) is the first bit transmitted and received.

SERIAL OP-CODE: After the device is selected with CE# going low, the first byte will be received. This byte

contains the op-code that defines the operations to be performed.

INV ALID OP-CODE: If an invalid op-code is received, no data will be shifted into the Pm25L V512/010, and the serial

output pin (SO) will remain in a high impedance state until the falling edge of CE# is detected again. This will

reinitialize the serial communication.

Figure 1. Bus Master and SPI Memory Devices

SDO

SPI Interface with

(0, 0) or (1, 1)

Bus Master

CS3 CS2 CS1

Note: 1. The Write Protect (WP#) and Hold (HOLD#) si

SDI

SCK

SCK SO SI

SPI Memory

Device

CE# WP# HOLD# HOLD# HOLD#

SCK SO SI SCK SO SI

SPI Memory

Device

CE# WP# CE# WP#

nals should be driven, High or Low as appropriate.

SPI Memory

Device

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

5

Page 6

PMC Pm25LV512/010

SERIAL INTERFACE DESCRIPTION (CONTINUED)

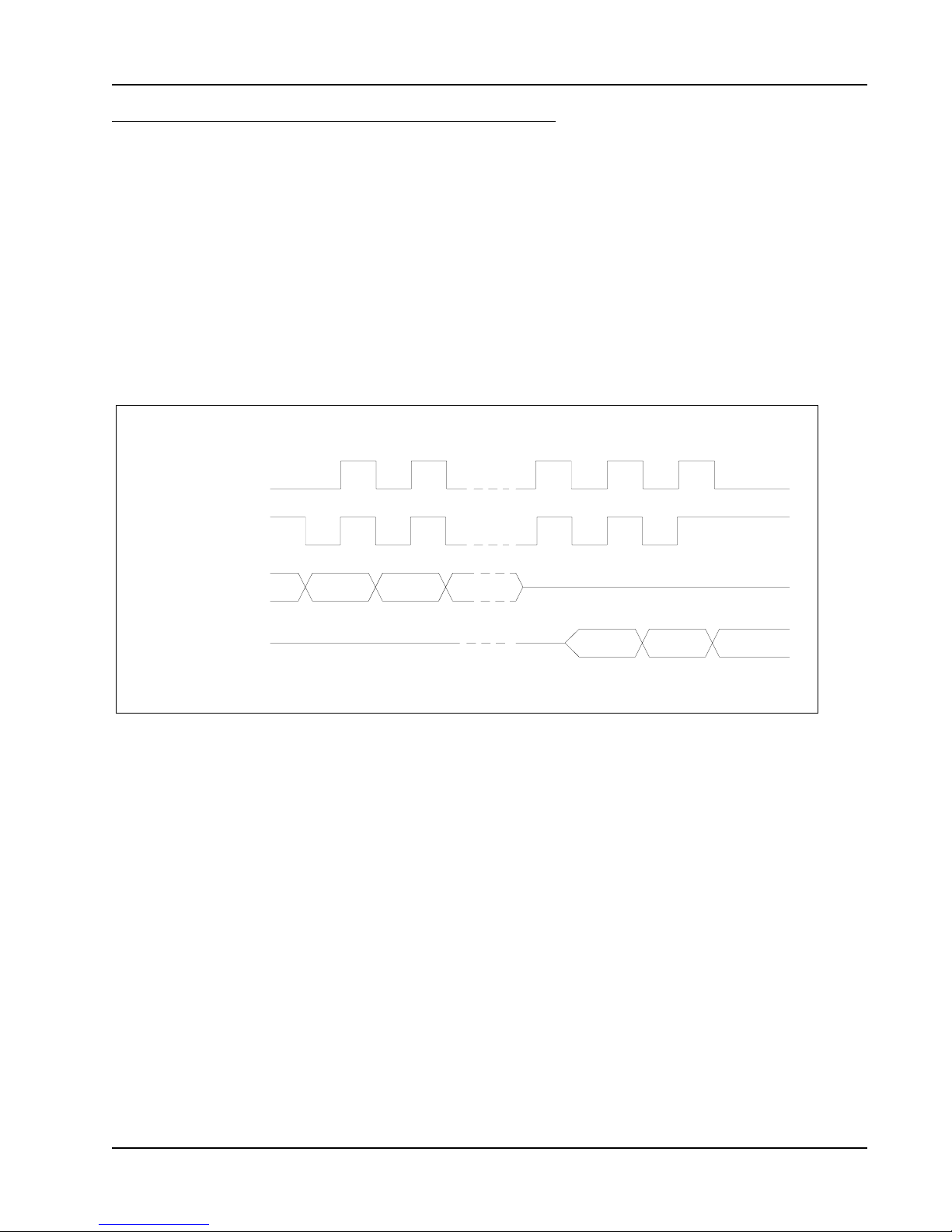

SPI MODES

These devices can be driven by microcontroller with its

SPI peripheral running in either of the two following modes:

Mode 0 = (0, 0)

Mode 3 = (1, 1)

For these two modes, input data is latched in on the

rising edge of Serial Clock (SCK), and output data is

Figure 2. SPI Modes

available from the falling edge of Serial Clock (SCK).

The difference between the two modes, as shown in

Figure 2, is the clock polarity when the bus master is in

Stand-by mode and not transfering data:

- Clock remains at 0 (SCK = 0) for Mode 0 (0, 0)

- Clock remains at 1 (SCK = 1) for Mode 3 (1, 1)

Mode 0 (0 0)

Mode 3 (1 1)

SCK

SCK

SI

SO

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

6

Page 7

PMC Pm25LV512/010

DEVICE OPERATION

The Pm25L V512/010 is designed to interface directly with the synchronous serial peripheral interface (SPI) of the

6800 type series of microcontrollers.

The Pm25LV512/010 utilizes an 8-bit instruction register. The list of instructions and their operation codes are

contained in Table 1. All instructions, addresses, and data are transferred with the MSB first and start with a highto-low transition.

Write is defined as program and/or erase in this specification. The following commands, P AGE PROGRAM,

SECTOR ERASE, BLOCK ERASE, CHIP ERASE, and WRSR are write instructions for Pm25L V512/010.

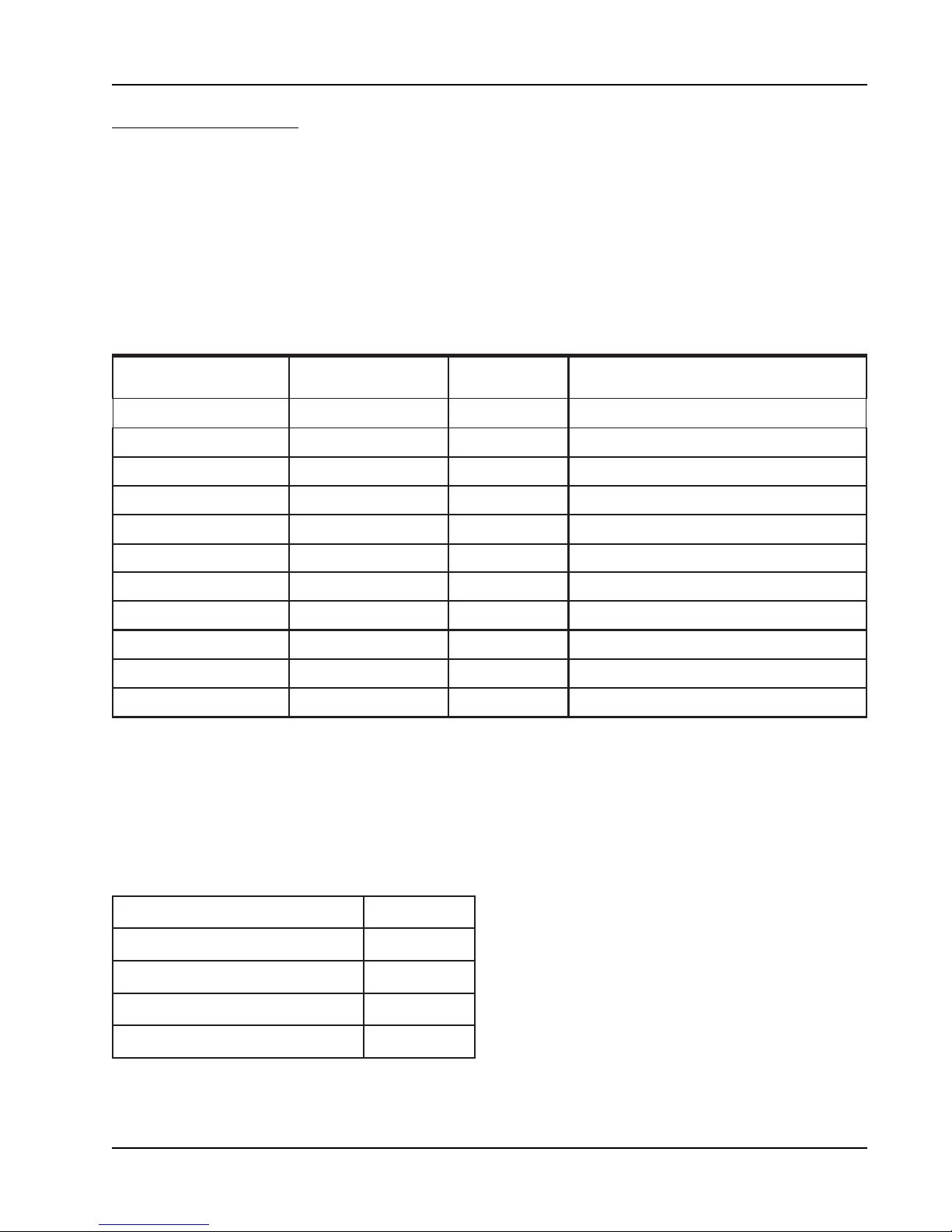

Table 1. Instruction Set for the Pm25LV512/010

emaNnoitcurtsnItamroFnoitcurtsnIedoCxeHnoitarepO

NERW01100000h60hctaLelbanEetirWteS

IDRW00100000h40hctaLelbanEetirWteseR

RSDR10100000h50retsigersutatSdaeR

RSRW10000000h10retsigeRsutatSetirW

DAER11000000h30yrarrAyromeMmorfataDdaeR

DAER_TSAF11010000hB0deepSrehgiHtayromeMmorfataDdaeR

GORP_GP01000000h20yarrAyromeMotnIataDmargorP

ESARE_ROTCES11101011h7DyarrAyromeMnirotceSenOesarE

ESARE_KCOLB00011011h8DyarrAyromeMnikcolBenOesarE

ESARE_PIHC11100011h7CyarrAyromeMeritnEesarE

DIDR11010101hBADItcudorPdnarerutcafunaMdaeR

READ PRODUCT ID (RDID): The RDID instruction allows the user to read the manufacturer and product ID of the

device. The instruction code is followed by three dummy bytes, each bit being latched-in on Serial Data Input (SI)

during the rising edge of Serial Clock (SCK). Then the first manufacturer ID (9Dh) is shifted out on Serial Data

Output (SO), followed by the device ID (7Bh = Pm25L V512; 7Ch = Pm25LV010) and the second manufacturer ID

(7Fh), each bit been shifted out during the falling edge of Serial Clock (SCK).

Table 2. Product Identification

noitacifitnedItcudorPataD

DIrerutcafunaMhD9

:DIeciveD

215VL52mPhB7

010VL52mPhC7

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

7

Page 8

PMC Pm25LV512/010

WRITE ENABLE (WREN): The device will power up in the write disable state when Vcc is applied. All write

instructions must therefore be preceded by the WREN instruction.

WRITE DISABLE (WRDI): T o protect the device against inadvertent writes, the WRDI instruction disables all write

commands. The WRDI instruction is independent of the status of the WP# pin.

READ ST ATUS REGISTER (RDSR): The RDSR instruction provides access to the status register. The READY/

BUSY and write enable status of the device can be determined by the RDSR instruction. Similarly, the Block Write

Protection bits indicate the extent of protection employed. These bits are set by using the WRSR instruction.

During internal write cycles, all other commands will be ignored except the RDSR instruction.

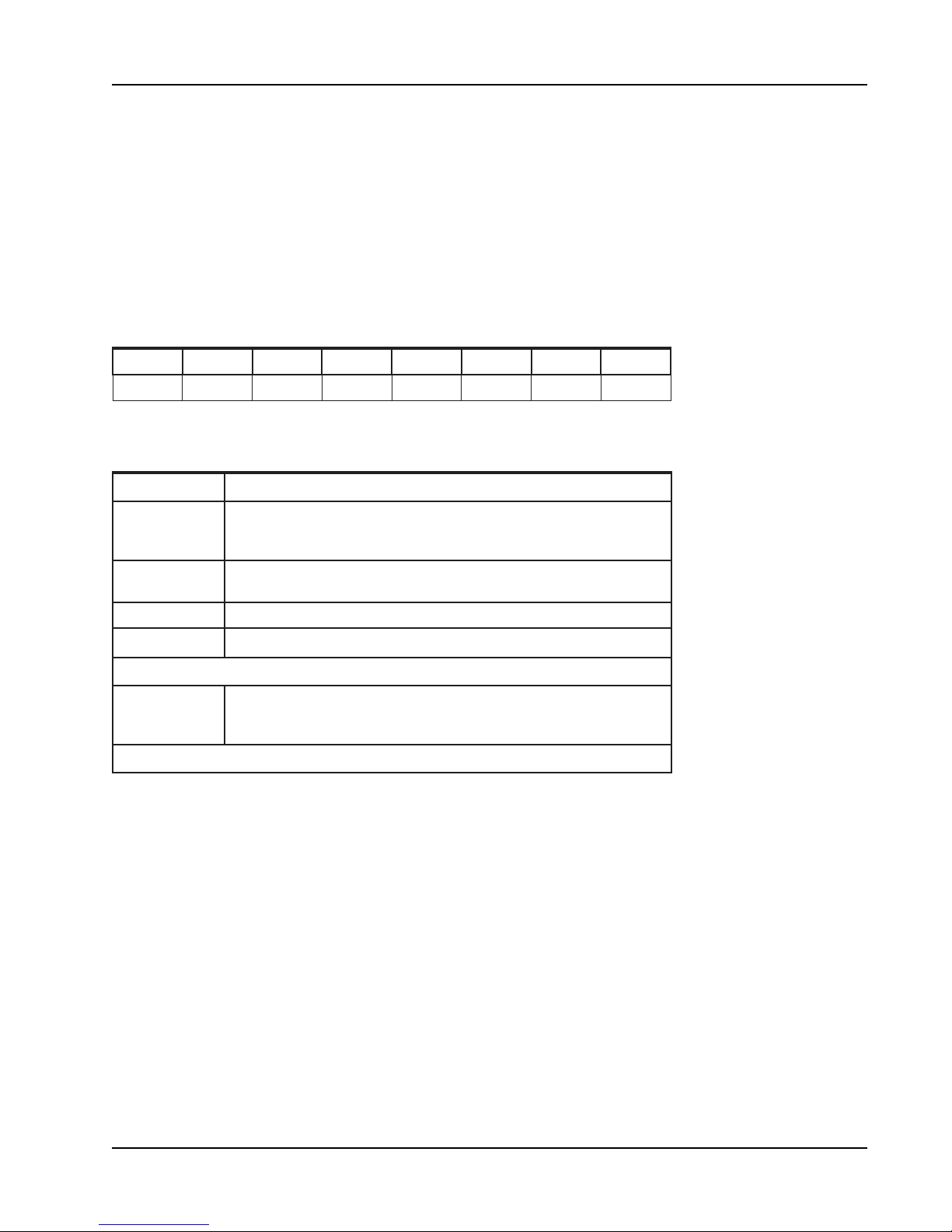

Table 3. Status Register Format

7tiB6tiB5tiB4tiB3tiB2tiB1tiB0tiB

NEPW XXX 1PB0PBNEWYDR

Table 4. Read Status Register Bit Definition

tiBnoitinifeD

.YDAERsiecivedehtsetacidni0=0tiB

)YDR(0tiB

)NEW(1tiB

)0PB(2tiB.5elbaTeeS

.YSUB

.DELBANEETIRWtonsiecivedehtsetacidni0=1tiB

.DELBANEETIRWsiecivedehtsetacidni1=1tiB

siecivedehtdnassergorpnisielcycetirwehtsetacidni1=0tiB

)1PB(3tiB.5elbaTeeS

.elcycetirwlanretninanitonsiecivednehws0era6-4stiB

.)#PW(niptcetorPetirWfonoitcnufehtskcolb0=NEPW

)NEPW(7tiB

.sliatedrof6elbaTeeS

.elcycetirwlanretninagniruds1era7-0stiB

.)#PW(niptcetorPetirWehtsetavitca1=NEPW

WRITE ST A TUS REGISTER (WRSR): The WRSR instruction allows the user to select one of four levels of protection for the Pm25L V010. The Pm25L V010 is divided into four blocks where the top quarter (1/4), top half (1/2), or all

of the memory blocks can be protected (locked out) from write. The Pm25L V512 is divided into 2 blocks where all

of the memory blocks can be protected (locked out) from write. Any of the locked-out blocks will therefore be READ

only . The locked-out block and the corresponding status register control bits are shown in Table 5.

The three bits, BP0, BP1, and WPEN, are nonvolatile cells that have the same properties and functions as the

regular memory cells (e.g., WREN, RDSR).

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

8

Page 9

PMC Pm25LV512/010

Table 5. Block Write Protect Bits

stiBretsigeRsutatS215VL52mP010VL52mP

sesserddAyarrA

leveL

000

)4/1(101 FFFF10-0008104kcolB

)2/1(210 FFFF10-0000104,3kcolB

)llA(311 FFFF00-000000

1PB0PB

tuOdekcoL

enoNenoN

tuo-dekcoL

)s(kcolB

skcolBllA

)2-1(

sesserddAyarrA

tuOdekcoL

enoNenoN

FFFF10-000000

tuo-dekcoL

)s(kcolB

skcolBllA

)4-1(

The WRSR instruction also allows the user to enable or disable the Write Protect (WP#) pin through the use of the

Write Protect Enable (WPEN) bit. Hardware write protection is enabled when the WP# pin is low and the WPEN bit

is "1". Hardware write protection is disabled when either the WP# pin is high or the WPEN bit is "0." When the

device is hardware write protected, writes to the Status Register, including the Block Protect bits and the WPEN

bit, and the locked-out blocks in the memory array are disabled. Write is only allowed to blocks of the memory

which are not locked out. The WRSR instruction is self-timed to automatically erase and program BP0, BP1, and

WPEN bits. In order to write the status register, the device must first be write enabled via the WREN instruction.

Then, the instruction and data for the three bits are entered. During the internal write cycle, all instructions will be

ignored except RDSR instructions. The Pm25LV512/010 will automatically return to write disable state at the

completion of the WRSR cycle.

Note: When the WPEN bit is hardware write protected, it cannot be changed back to "0", as long as the WP# pin

is held low.

T able 6. WPEN Operation

NEPWPWNEWskcolBdetcetorPskcolBdetcetorpnUretsigeRsutatS

0X0 detcetorPdetcetorPdetcetorP

0X 1 detcetorPelbatirWelbatirW

1woL0 detcetorPdetcetorPdetcetorP

1woL1 detcetorPelbatirWdetcetorP

XhgiH0 detcetorPdetcetorPdetcetorP

XhgiH1 detcetorPelbatirWelbatirW

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

9

Page 10

PMC Pm25LV512/010

READ: Reading the Pm25LV512/010 via the SO (Serial Output) pin requires the following sequence. After the CE#

line is pulled low to select a device, the READ instruction is transmitted via the Sl line followed by the byte address

to be read (Refer to Table 7). Upon completion, any data on the Sl line will be ignored. The data (D7-D0) at

the specified address is then shifted out onto the SO line. If only one byte is to be read, the CE# line should be

driven high after the data comes out. The READ instruction can be continued since the byte address is automatically incremented and data will continue to be shifted out. For the Pm25L V512/010, when the highest address is

reached, the address counter will roll over to the lowest address allowing the entire memory to be read in one

continuous READ instruction.

FAST_READ: The device is first selected by driving CE# low. The F AST READ instruction is followed by a 3-byte

address (A23-A0) and a dummy byte, each bit being latched-in during the rising edge of SCK (Serial Clock). Then

the memory contents, at that address, is shifted out on SO (Serial Output), each bit being shifted out, at a

maximum frequency fFR, during the falling edge of SCK (Serial Clock).

The first byte addressed can be at any location. The address is automatically incremented to the next higher

address after each byte of data is shifted out. When the highest address is reached, the address counter will roll

over to the lowest address allowing the entire memory to be read with a single FAST READ instruction. The FAST

READ instruction is terminated by driving CE# high.

PAGE PROGRAM (PG_PROG): In order to program the Pm25LV512/010, two separate instructions must be

executed. First, the device must be write enabled via the WREN instruction. Then the P AGE PROGRAM instruction can be executed. Also, the address of the memory location(s) to be programmed must be outside the protected address field location selected by the Block Write Protection Level. During an internal self-timed programming cycle, all commands will be ignored except the RDSR instruction.

The P AGE PROGRAM instruction requires the following sequence. After the CE# line is pulled low to select the

device, the P AGE PROGRAM instruction is transmitted via the Sl line followed by the address and the data (D7-D0)

to be programmed (Refer to Table 7). Programming will start after the CE# pin is brought high. The low-to-high

transition of the CE# pin must occur during the SCK low time immediately after clocking in the D0 (LSB) data bit.

The READY/BUSY status of the device can be determined by initiating a RDSR instruction. If Bit 0 = 1, the program

cycle is still in progress. If Bit 0=0, the program cycle has ended. Only the RDSR instruction is enabled during the

program cycle. A single PROGRAM instruction programs 1 to 256 consecutive bytes within a page if it is not write

protected. The starting byte could be anywhere within the page. When the end of the page is reached, the address

will wrap around to the beginning of the same page. If the data to be programmed are less than a full page, the data

of all other bytes on the same page will remain unchanged. If more than 256 bytes of data are provided, the address

counter will roll over on the same page and the previous data provided will be replaced. The same byte cannot be

reprogrammed without erasing the whole sector/block first. The Pm25LV512/010 will automatically return to the

write disable state at the completion of the PROGRAM cycle.

Note: If the device is not write enabled (WREN) the device will ignore the Write instruction and will return to the

standby state, when CE# is brought high. A new CE# falling edge is required to re-initiate the serial

communication.

Table 7. Address Key

sserddA215VL52mP010VL52mP

A

N

stiBeraCt'noDA

A51A-

32

0

A-

61

A61A-

A32A-

0

71

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

10

Page 11

PMC Pm25LV512/010

SECTOR_ERASE, BLOCK_ERASE: Before a byte can be reprogrammed, the sector/block which contains the

byte must be erased. In order to erase the Pm25L V512/010, two separate instructions must be executed. First, the

device must be write enabled via the WREN instruction. Then the SECTOR ERASE or BLOCK ERASE instruction

can be executed.

Table 8. Block Addresses

sserddAkcolBkcolB215VL52mPkcolB010VL52mP

FFF700ot0000001kcolB1kcolB

FFFF00ot0008002kcolB2kcolB

FFF710ot000010A/N3kcolB

FFFF10ot000810A/N4kcolB

The BLOCK ERASE instruction erases every byte in the selected block if the block is not locked out. Block

address is automatically determined if any address within the block is selected. The BLOCK ERASE instruction

is internally controlled; it will automatically be timed to completion. During this time, all commands will be ignored,

except RDSR instruction. The Pm25L V512/010 will automatically return to the write disable state at the completion

of the BLOCK ERASE cycle.

CHIP_ERASE: As an alternative to the SECTOR and BLOCK ERASE, the CHIP ERASE instruction will erase

every byte in all blocks that are not locked out. First, the device must be write enabled via the WREN instruction.

Then the CHIP ERASE instruction can be executed. The CHIP ERASE instruction is internally controlled; it will

automatically be timed to completion. The CHIP ERASE cycle time maximum is 100 miliseconds. During the

internal erase cycle, all instructions will be ignored except RDSR. The Pm25L V512/010 will automatically return to

the write disable state at the completion of the CHIP ERASE.

HOLD: The HOLD# pin is used in conjunction with the CE# pin to select the Pm25L V512/010. When the device is

selected and a serial sequence is underway, HOLD# pin can be used to pause the serial communication with the

master device without resetting the serial sequence. T o pause, the HOLD# pin must be brought low while the SCK

pin is low. To resume serial communication, the HOLD# pin is brought high while the SCK pin is low (SCK may still

toggle during HOLD). Inputs to the Sl pin will be ignored while the SO pin is in the high impedance state.

HARDWARE WRITE PROTECT: The Pm25LV512/010 has a write lockout feature that can be activated by asserting the write protect pin (WP#). When the lockout feature is activated, locked-out sectors will be READ only. The

write protect pin will allow normal read/write operations when held high. When the WP# is brought low and WPEN

bit is "1", all write operations to the status register are inhibited. WP# going low while CE# is still low will interrupt

a write to the status register. If the internal status register write cycle has already been initiated, WP# going low will

have no effect on any write operation to the status register. The WP# pin function is blocked when the WPEN bit in

the status register is "0". This will allow the user to install the Pm25L V512/010 in a system with the WP# pin tied

to ground and still be able to write to the status register. All WP# pin functions are enabled when the WPEN bit is

set to "1".

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

11

Page 12

PMC Pm25LV512/010

ABSOLUTE MAXIMUM RATINGS

saiBrednUerutarepmeT 56-

erutarepmeTegarotS 56-

)2(

V

CC

(1)

egakcaPdradnatS042

erutarepmeTgniredloSdaeLtnuoMecafruS

egakcaPeerf-daeL062

)2(

sniPllAnodnuorGottcepseRhtiwegatloVtupnI

dnuorGottcepseRhtiwegatloVtuptuOllA VotV5.0-

o

o

o

o

VotV5.0-

CC

CC

Notes:

1. Stresses under those listed in “Absolute Maximum Ratings” may cause permanent damage

to the device. This is a stress rating only. The functional operation of the device or any other

conditions under those indicated in the operational sections of this specification is not

implied. Exposure to absolute maximum rating condition for extended periods may affected

device reliability.

2. Maximum DC voltage on input or I/O pins are VCC + 0.5 V. During voltage transitioning

period, input or I/O pins may overshoot to VCC + 2.0 V for a period of time up to 20 ns.

Minimum DC voltage on input or I/O pins are -0.5 V. During voltage transitioning period,

input or I/O pins may undershoot GND to -2.0 V for a period of time up to 20 ns.

o

521+otC

C

o

521+otC

C

sdnoceS3C

sdnoceS3C

V5.0+

V5.0+

V0.6+otV5.0-

DC AND AC OPERATING RANGE

rebmuNtraP 010/215VL52mP

erutarepmeTgnitarepO 0

ylppuSrewoPccV V6.3-V7.2

o

o

58otC

C

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

12

Page 13

PMC Pm25LV512/010

S

DC CHARACTERISTICS

Applicable over recommended operating range from:

TAC = 0°C to +85°C, VCC = +2.7 V to +3.6 V (unless otherwise noted).

Symbol Parameter Min Typ Max Units

= 3.6V at 25 MHz, SO = Open

I

CC1

I

CC2

I

SB1

I

SB2

I

LI

I

LO

V

V

V

V

IL

IH

OL

OH

Vcc Active Read Current 10 15 mA

Vcc Program/Erase Current 15 30 mA

Vcc Standby Current CMO

Vcc Standby Current TTL 0.05 3 mA

Input Leakage Current 1 µA

Output Leakage Current 1 µA

Input Low Voltag e -0.5 0.8 V

Input HIgh Voltage 0.7V

Output Low Voltage IOL = 2.1 mA 0.45 V

Output High Voltage IOH = -100 µAVCC - 0.2 V

V

CC

= 3.6V at 25 MHz, SO = Open

V

CC

= 3.6V, CE# = V

V

CC

V

= 3.6V, CE# = VIH to V

CC

VIN = 0V to V

VIN = 0V to VCC, TAC = 0oC to 85oC

2.7V < V

Condition

CC

< 3.6V

CC

CC

CC

0.1 5 µA

CC

VCC + 0.3 V

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

13

Page 14

PMC Pm25LV512/010

AC CHARACTERISTICS

Applicable over recommended operating range from TA = 0°C to +85°C, VCC = +2.7 V to +3.6 V

CL = 1TTL Gate and 30 pF (unless otherwise noted).

lobmySretemaraPniMpyTxaMstinU

f

RF

f

R

t

IR

t

IF

t

HKC

DAER_TSAF

rofycneuqerFkcolC

snoitcurtsniDAERrofycneuqerFkcolC002zHM

emiTesiRtupnI 02sn

emiTllaFtupnI 02sn

emiThgiHKCS02sn

052zHM

t

LKC

t

HEC

t

SC

t

HC

t

SD

t

HD

t

SH

t

DH

t

V

t

HO

t

ZL

t

ZH

t

SID

t

CE

t

pp

t

w

emiTwoLKCS02sn

emiThgiHEC52sn

emiTputeSEC52sn

emiTdloHEC52sn

emiTputeSnIataD5sn

emiTdloHniataD5sn

emiTputeSdloH51sn

emiTdloH51sn

dilaVtuptuO 51sn

emiTdloHtuptuO0sn

ZwoLtuptuOotdloH 002sn

ZhgiHtuptuOotdloH 002sn

emiTelbasiDtuptuO 001sn

emiTesarEpihC/kcolB/retceS04001sm

emiTmargorPegaP25sm

emitretsigeRsutatSetirW04001sm

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

14

Page 15

PMC Pm25LV512/010

AC CHARACTERISTICS (CONTINUED)

AC WAVEFORMS

CE#

SCK

V

V

V

V

V

(1)

IH

IL

t

CS

IH

IL

t

IH

DS

SI

V

IL

V

OH

SO

HI-Z

V

OL

Note: 1. For SPI Mode 0 (0,0)

VALID IN

t

CKH

t

CEH

t

CH

t

CKL

t

DH

t

V

t

OH

t

DIS

HI-Z

OUTPUT TEST LOAD INPUT TEST WA VEFORMS

AND MEASUREMENT LEVEL

3.3 V

3.0 V

1.8 K

1.3 K

OUTPUT PIN

30 pF

Input

0.0 V

1.5 V

AC

Measurement

Level

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

15

Page 16

PMC Pm25LV512/010

AC CHARACTERISTICS (CONTINUED)

HOLD Timing

CE#

t

HD

t

LZ

SCK

HOLD#

SO

t

HD

t

HS

t

HS

t

HZ

PIN CAP ACITANCE ( f = 1 MHz, T = 25°C )

pyTxaMstinUsnoitidnoC

C

NI

C

TUO

46 FpV

821FpV

Note: These parameters are characterized but not 100% tested.

V0=

NI

V0=

TUO

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

16

Page 17

PMC Pm25LV512/010

TIMING DIAGRAMS

RDID Timing

CE#

SCK

SI

SO

WREN Timing

CE#

SCK

SI

01 8

INSTRUCTION

1010 1011b

HIGH IMPEDANCE

3 Dummy Bytes

97

31

Manufacture ID1 Device ID

INSTRUCTION = 0000 0110b

38 39

46

47 54

Manufacture ID2

SO

HI-Z

WRDI Timing

CE#

SCK

SI

SO

INSTRUCTION = 0000 0100b

HI-Z

nnnnnnN

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

17

Page 18

PMC Pm25LV512/010

RDSR Timing

CE#

SCK

SI

SO

WRSR Timing

CE#

SCK

SI

12 3

0

INSTRUCTION = 0000 0101b

HIGH IMPEDANCE

0 1 2 3 5 6 7 8 9 10 11 12 13 144 15

INSTRUCTION = 0000 0001b

5678

4

MSB

7654

9

10 11 12 13 14

DATA OUT

765432 10

DATA IN

32

10

SO

HIGH IMPEDANCE

READ Timing

CE#

0 1 2 3 4 5 6 7 8 9 10 11 28 29 30 31 32 33 34 3635 37 38

SCK

3-BYTE ADDRESS

SI

SO

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

INSTRUCTION = 0000 0011b

HIGH IMPEDANCE

23 22 21 3 2 1 0

...

76543210

18

Page 19

PMC Pm25LV512/010

FAST READ T iming

CE#

0 1 2 3 4 5 6 7 8 9 10 11 28 29 30 31

SCK

3-BYTE ADDRESS

SI

SO

INSTRUCTION = 0000 1011b

HIGH IMPEDANCE

CE#

32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47

SCK

DUMMY BYTE

SI

SO

765

HIGH IMPEDANCE

23 22 21 3 2 1 0

3

4 1

2

...

0

DATA OUT 1 DATA OUT 2

76543210

76543210

P AGE PROGRAM Timing

CE#

0 1 2 3 4 5 6 7 8 9 10 11 28 29 30 31 32 33 34

SCK

SI

SO

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

INSTRUCTION = 0000 0010b

HIGH IMPEDANCE

3-BYTE ADDRESS

19

1st BYTE DATA-IN

076532 21143023 22 21

2075

2076

2077

2078

2079

256th BYTE DATA-IN

Page 20

PMC Pm25LV512/010

SECTOR ERASE Timing

CE#

0 1 2 3 4 5 6 7 8 9 10 11 28 29 30 31

SCK

3-BYTE ADDRESS

SI

INSTRUCTION = 1101 0111b

...

0123212223

SO

BLOCK ERASE Timing

CE#

SCK

SI

SO

CHIP ERASE Timing

HIGH IMPEDANCE

01 234 56789101128 29 30 31

3-BYTE ADDRESS

INSTRUCTION = 1101 1000b

HIGH IMPEDANCE

...

0123212223

CE#

SCK

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

SI

SO

01234567

INSTRUCTION = 1100 0111b

HIGH IMPEDANCE

20

Page 21

PMC Pm25LV512/010

PROGRAM/ERASE PERFORMANCE

retemaraPtinUpyTxaMskrameR

emiTesarErotceSsm04001noitelpmocesareotdnammocesaregnitirwmorF

emiTesarEkcolBsm04001noitelpmocesareotdnammocesaregnitirwmorF

emiTesarEpihCsm04001noitelpmocesareotdnammocesaregnitirwmorF

emiTgnimmargorPegaPsm25

noitelpmoc

Note: These parameters are characterized and are not 100% tested.

RELIABILITY CHARACTERISTICS

(1)

retemaraPniMpyTtinUdohteMtseT

ecnarudnE000,001

)2(

selcyC711AdradnatSCEDEJ

noitneteRataD02sraeY301AdradnatSCEDEJ

ledoMydoBnamuH-DSE000,2stloV411AdradnatSCEDEJ

ledoMenihcaM-DSE002stloV511AdradnatSCEDEJ

pU-hctaL

I+001

1CC

Am87dradnatSCEDEJ

Note: 1. These parameters are characterized and are not 100% tested.

2. Preliminary specification only and will be formalized after cycling qualification test.

margorpotdnammocmargorpgnitirwmorF

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

21

Page 22

PMC Pm25LV512/010

PACKAGE TYPE INFORMA TION

8S

8-Pin JEDEC Small Outline Integrated Circuit (SOIC) Package (measure in millimeters)

Top View

4.00

3.80

6.20

5.80

End View

45º

Side View

0.51

0.33

5.00

4.80

1.27 BSC

0.25

0.10

1.75

1.35

0.25

0.19

1.27

0.40

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

22

Page 23

PMC Pm25LV512/010

PACKAGE TYPE INFORMATION (CONTINUED)

8Q

8-Contact Ulta-Thin Small Outline No-Lead (WSON) Package (measure in millimeters)

Top View

6.00

BSC

Bottom View

4.00

3.40

0.75

0.50

5.00

BSC

Pin 1

Side View

0.25

0.19

0.80

0.70

1.27

BSC

0.48

0.35

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

23

Page 24

PMC Pm25LV512/010

REVISION HISTORY

etaD.oNnoisiveRsegnahCfonoitpircseD.oNegaP

2002,rebotcO0.1cepSyranimilerP,noitacilbupweNllA

2002,rebmeceD1.1esaeleRlamroFllA

3002,nuJ2.1noitpoegakcapNOSWdeddA32,3,2,1

snoitpoegakcapeerf-daeLdeddA21,3,1

3002,rebmeceD3.1

4002,yraurbeF4.1egnarerutarepmetnoitarepoevorpmIllA

)yranimilerp(000,001ot

noisnemidegakcapdewarderdnadetadpU32,22

000,05morfselcycesare/margorpdeetnarugdedargpU

12,1

Programmable Microelectronics Corp. Issue Date: February, 2004, Rev: 1.4

24

Loading...

Loading...