Page 1

EL4836HB and EL4836HB-ICEEL4836HB and EL4836HB-ICE

A

EL4836HB and EL4836HB-ICE

EL4836HB and EL4836HB-ICEEL4836HB and EL4836HB-ICE

276 x 128 Pixel Electroluminescent Display276 x 128 Pixel Electroluminescent Display

276 x 128 Pixel Electroluminescent Display

276 x 128 Pixel Electroluminescent Display276 x 128 Pixel Electroluminescent Display

Product ProfileProduct Profile

Product Profile

Product ProfileProduct Profile

The EL4836HB and the EL4836HB-ICE displays are

low power, rugged, high-resolution electroluminescent

(TFEL) flat panel displays. They replace the LCD or bulky

CRT in instrument product designs. Their compact

dimensions save space that can allow addition of features

or reductions in overall size. They are designed to

function in extreme environments, and the crisp displays

are viewable under most lighting conditions at wide

viewing angles. Their ease of installation reduces system

integration costs.

The EL4836HB and the EL4836HB-ICE are 276

column by 128 row displays with a resolution of 48 dots

per inch. The pixel aspect ratio is 1:1. The LCD-type

interface is TTL-compatible and is designed for hardware

compatibility with the Hitachi HD61830B or equivalent

LCD controller. These displays may be driven at frame

rates up to 120 Hz for applications requiring extra

brightness.

The displays require +5V/+12VDC or +12VDC

only power and four basic signals to operate:

1. Video Data or pixel information (VID)

2. Video Clock, pixel clock, or dot clock (VCLK)

3. Horizontal Sync (HS)

4. Vertical Sync (VS)

EL TechnologyEL Technology

EL Technology

EL TechnologyEL Technology

A display consists of an electroluminescent glass

panel and a mounted circuit board with control electronics.

LUMINUM ROW

ELECTRODE

DIELECTRIC

LAYERS

1 micron

1 mm

LIGHT EMITTING LAYER

TRANSPARENT

COLUMN ELECTRODE

GLASS SUBSTRATE

VIEW

Operations ManualOperations Manual

Operations Manual

Operations ManualOperations Manual

The EL glass panel is a solid-state device with a thin

film luminescent layer sandwiched between transparent

dielectric layers and a matrix of row and column

electrodes. The row electrodes, in back, are aluminum;

the column electrodes, in front, are transparent. The

entire thin film device is deposited on a single glass

substrate. A circuit board is connected to the back of the

glass substrate. Components are mounted on this circuit

board within the same area as the electroluminescent

viewing area on the glass panel. The circuit board is

connected to the glass with metal-on-elastomer

interconnect technology. The result is a flat, compact,

reliable and rugged display device.

The EL4836HB-ICE display includes a light absorbing

Integral Contrast Enhancement (ICETM) construction of

the display glass. ICETM background significantly improves

the luminance contrast of the display in bright ambients,

and makes the display easier to read by increasing the

crispness of the pixels.

The 276 column electrodes and 128 row electrodes

are arranged in an X-Y formation with the

intersecting areas performing as pixels. Voltage

is applied to both the correct row electrode and

V(t)

the correct column electrode to cause a lit pixel.

Special operating voltages required are provided

by a DC/DC converter.

®

The Definition of Quality ®

Page 2

2EL4836HB, EL4836HB-ICE

Electrical CharacteristicsElectrical Characteristics

Electrical Characteristics

Electrical CharacteristicsElectrical Characteristics

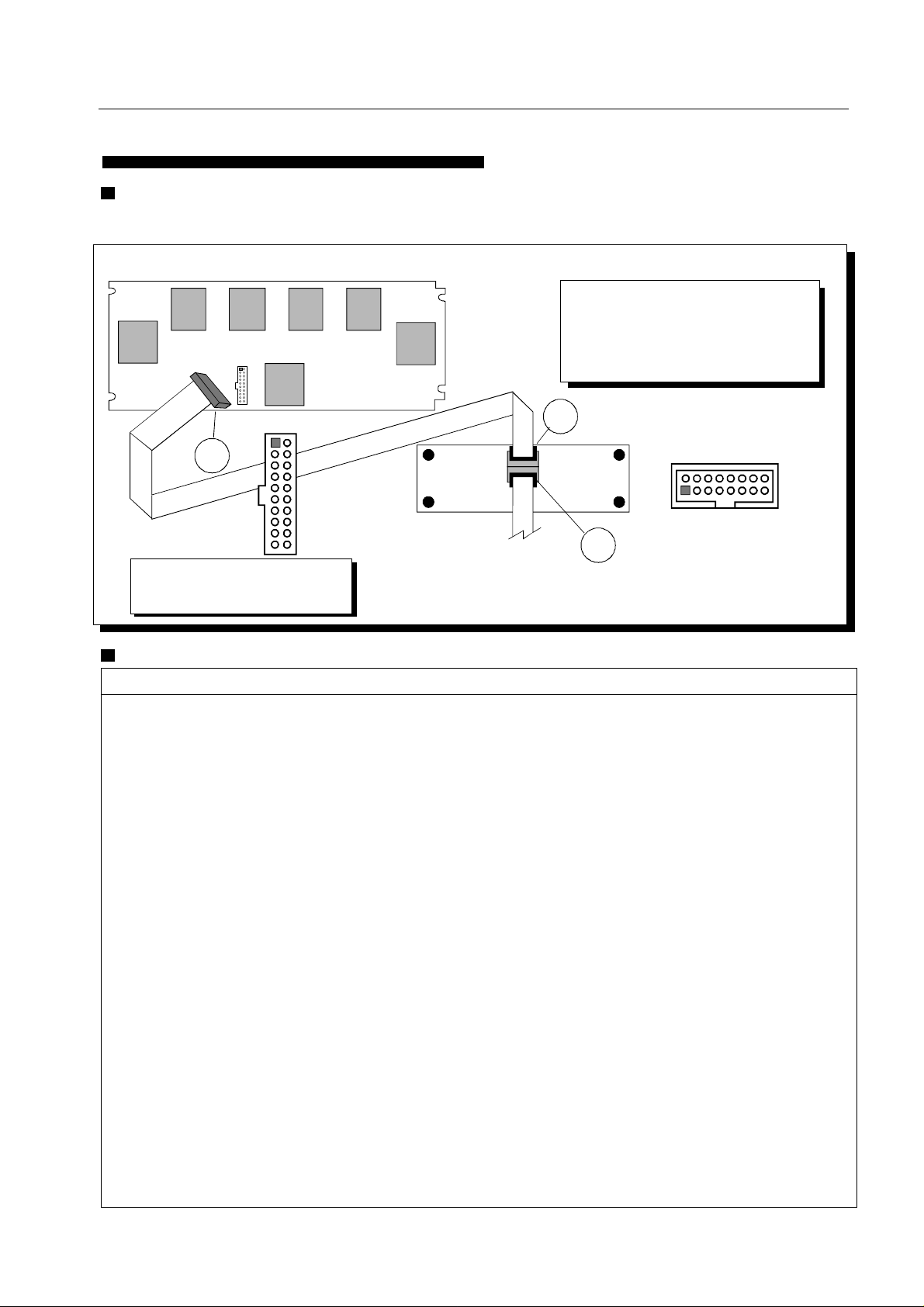

DisplayDisplay

Display

DisplayDisplay

The EL4836HB and EL4836HB-ICE products consist of a display, a DC/DC converter, and interconnecting cable

as shown below.

Back of DisplayBack of Display

Back of Display

Back of DisplayBack of Display

WARNINGWARNING

WARNING

WARNINGWARNING

The display generates potentially

dangerous voltages, up to 200 volts.

J1

Do not touch the display electronics

during operation!

P1

CAUTIONCAUTION

CAUTION

CAUTIONCAUTION

1

J1

19 20

2

Maximum

cable length is

24"

P3

J3

J0

P0

DC/DC ConverterDC/DC Converter

DC/DC Converter

DC/DC ConverterDC/DC Converter

2

1

J0

16

15

Connector J1 is not polarized.

Input to the Display at P0Input to the Display at P0

Input to the Display at P0

Input to the Display at P0Input to the Display at P0

PinsPins

Pins

PinsPins

1, 2 Voltage VH +12V. See also the descriptions of DC power requirements on page 4.

3, 4 Voltage VL +5V optional input, see page 4.

5 not connected

6 not connected

7, 8, 10

12, 14, 16 Ground GND Signal return.

9 Vertical Sync VS VS initiates a new frame scan. To properly position the displayed data, VS rising edge must

11 Horizontal Sync HS HS marks the last pixel of a horizontal scan line.

13 Video Clock VCLK VID and HS are referenced to VCLK. Data latching occurs on the falling edge of VCLK. This

15 Video Data VID VID contains the serial video data to be displayed. A logic high corresponds to a lit pixel. Pixel

SignalSignal

Signal

SignalSignal

SymbolSymbol

Symbol

SymbolSymbol

DescriptionDescription

Description

DescriptionDescription

be high at the end of the first horizontal scan line of the frame . This signal passes directly

from the video source to the display via the DC/DC converter. It is not buffered or terminated

within the DC/DC converter.

tVCLK. The last 276 pixels prior to the falling edge of HS will be visible on the display. This

signal passes directly from the video source to the display via the DC/DC converter. It is not

buffered or terminated within the DC/DC converter.

signal passes directly from the video source to the display via the DC/DC converter. It is not

buffered or terminated within the DC/DC converter.

information on VID is supplied from left to right and from top to bottom; the first bit of data

on VID following HS is displayed as the pixel at the upper left corner of the display. Bit number

240 is at the upper right corner. Bit number 276 is directly beneath pixel number 1 and so

on. This signal passes directly from the video source to the display via the DC/DC converter.

It is not buffered or terminated within the DC/DC converter.

HS period must be an even multiple of 4

Page 3

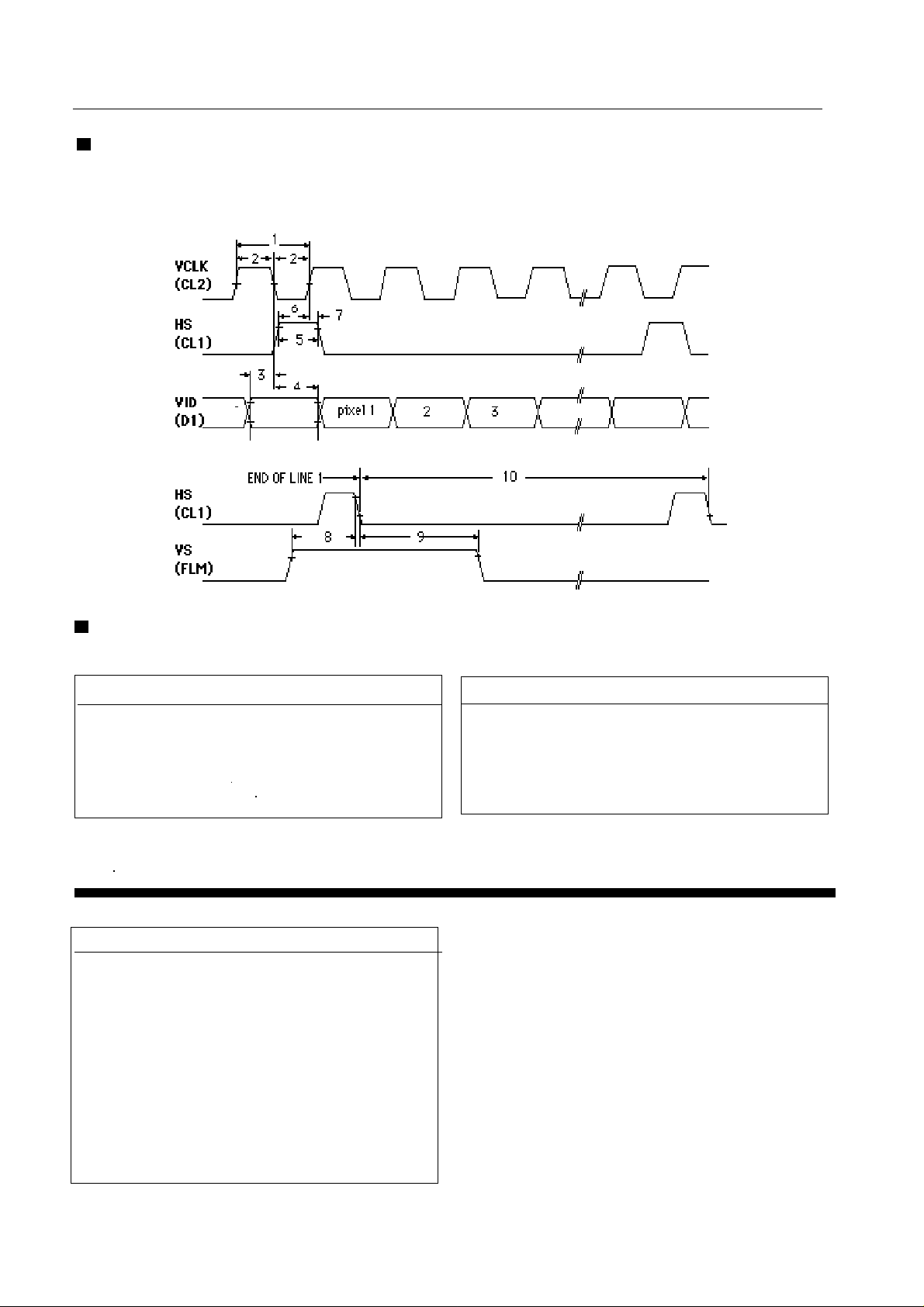

Hitachi 61830B LCD ControllerHitachi 61830B LCD Controller

Hitachi 61830B LCD Controller

Hitachi 61830B LCD ControllerHitachi 61830B LCD Controller

Compatible Video Timing Input at POCompatible Video Timing Input at PO

Compatible Video Timing Input at PO

Compatible Video Timing Input at POCompatible Video Timing Input at PO

3 EL4836HB, EL4836HB-ICE

275

Video ParametersVideo Parameters

Video Parameters

Video ParametersVideo Parameters

ParameterParameter

Parameter

ParameterParameter

1 Video clock (CL2) period (tVCLK) 235 630 ns

2 VCLK lowtime (tWL) 100 — n s

VCLK high time (tWH) 100 — ns

3 VID setup to VCLK (tDS) 50 — n s

4 VID hold from VCLK (tDH) 50 — n s

5 HS (CL1) high time (tHS high) 100 tVCLK ns

(Symbol)(Symbol)

(Symbol)

(Symbol)(Symbol)

276

Min.Min.

Min.

Min.Min.

Max.Max.

Max.

Max.Max.

UnitsUnits

Units

UnitsUnits

ParameterParameter

Parameter

ParameterParameter

6 HS setup time (tHSS) 100 tWL n s

7 HS hold from VCLK (tHSH) 0 tWH ns

8 VS (FLM) setup to HS (tHSD) 400 — ns

9 VS hold from HS (tVSD) 1000 — ns

HS (CL1) period (tHS) 276 — tVCLK

VS period (tVS) 128 — tHS

Frame Rate (1/VS period) 120 H z

(Symbol)(Symbol)

(Symbol)

(Symbol)(Symbol)

Min.Min.

Min.

Min.Min.

Max.Max.

Max.

Max.Max.

UnitsUnits

Units

UnitsUnits

Video Electrical SpecificationsVideo Electrical Specifications

Video Electrical Specifications

Video Electrical SpecificationsVideo Electrical Specifications

SymbolSymbol

Symbol

SymbolSymbol

VIL low-level input voltage - 0.3 0.8 V

VIH high-level input voltage 2.4 5.0 V

IILlow-level input current — - 0.4 mA

IIH high-level input current — 10 µA

VOH output high voltage 2.0 V

VOL output low voltage 0.4 V

ParameterParameter

Parameter

ParameterParameter

maximum input voltage — 5.5 V

@ IOH= 0.4 mA

@ IOL = 2.1 mA

Min.Min.

Min.

Min.Min.

Max.Max.

Max.

Max.Max.

UnitsUnits

Units

UnitsUnits

Note: All inputs are TTL-compatible CMOS with

24KΩ pull-up resistors and 100Ω series resistors to

minimize under- and over-shoot of input signals.

Page 4

4EL4836HB, EL4836HB-ICE

DC/DC Converter - PS512-1DC/DC Converter - PS512-1

DC/DC Converter - PS512-1

DC/DC Converter - PS512-1DC/DC Converter - PS512-1

The display and the separate DC/DC converter are calibrated together at the factory. Replacements to these

matched units must be adjusted according to specifications. Consult Planar for design specifications.

DC Power ConsumptionDC Power Consumption

DC Power Consumption

DC Power ConsumptionDC Power Consumption

Power is dependent on the actual text or graphics displayed. For a typical screen of text and graphics, power is

under 2.1 watts. Maximum power is 3.0 watts at 60 Hz frame rate and 5.3 watts at 120 Hz.

DC Power Input SpecificationsDC Power Input Specifications

DC Power Input Specifications

DC Power Input SpecificationsDC Power Input Specifications

DescriptionDescription

Description

DescriptionDescription

Input voltage (VH) 10.8 12.0 13.2 VDC

Input voltage

absolute max. (VH) — — 15.0 VDC

Input current (IH)

VH=Min, 120 Hz frame rate — — 0.4 A

Optional 5V (VL) 4.75 5.0 5.25 VDC

Absolute max. (VL) — — 7.5 VDC

Input current (IL) — — 0.04 A

DC/DC Converter Calibration - PS512-1DC/DC Converter Calibration - PS512-1

DC/DC Converter Calibration - PS512-1

DC/DC Converter Calibration - PS512-1DC/DC Converter Calibration - PS512-1

The DC/DC converter cannot be tested separately.

It requires an active low enable signal from the display

to activate the high voltage section. The display provides this signal after detecting the presence of video

signals at its input.

The DC/DC converter has been properly calibrated

at the factory to the EL display by means of a voltage

output adjustment. The converter should not need

adjustment in the field. If the DC/DC converter and

display become separated the following procedure can

be used to set the converter to the proper voltage:

1. Ensure power to the DC/DC converter is off.

2. Turn trimpot R20 on the DC/DC converter fully

counterclockwise (ccw). Do not adjust R19.

3. Connect the DC/DC converter to the display

using the flat cable.

Min. Nom. Max.Min. Nom. Max.

Min. Nom. Max.

Min. Nom. Max.Min. Nom. Max.

UnitsUnits

Units

UnitsUnits

J1 Jumper Function on PS512-1J1 Jumper Function on PS512-1

J1 Jumper Function on PS512-1

J1 Jumper Function on PS512-1J1 Jumper Function on PS512-1

INT

J1

1

J1

2

3

EXT = +5V (VL) supplied by customer from an

external source.

INT = +5V (VL) generated from VH within the

DC/DC converter. Shipped set for INT from

factory.

4. Apply a full on video pattern to the display (full

white field). At the factory, calibration is done with all

pixels on.

5. Set the DVM to measure a 250VDC voltage.

6. Connect the DVM positive and negative leads

to the test points marked HV2 and GND respectively

on the DC/DC converter. See drawing on p. 7.

7. Apply power to the DC/DC converter.

8. Note the voltage statement

on the display as shown:

9. Adjust trimpot R20 on the DC/DC converter

clockwise (cw) until the voltage reading of the DVM

is equal to the V (ALL ON) voltage ±1V, as specified

on the display. Do NOT exceed 235V. Do NOT

adjust R19.

10. Calibration is complete.

EXT

1

2

3

PS SN: __________PS SN: __________

PS SN: __________

PS SN: __________PS SN: __________

V(ALL ON):+______V(ALL ON):+______

V(ALL ON):+______

V(ALL ON):+______V(ALL ON):+______

Page 5

Operational SpecificationsOperational Specifications

Operational Specifications

Operational SpecificationsOperational Specifications

EnvironmentalEnvironmental

Environmental

EnvironmentalEnvironmental

TemperatureTemperature

Temperature

TemperatureTemperature

Operating 0°C to +55°C

Operating Survival-20°C to +70°C

Non-Operating -40°C to +75°C

HumidityHumidity

Humidity 95% MIL-STD-202F method 106E

HumidityHumidity

AltitudeAltitude

Altitude

AltitudeAltitude

Operating 15,000 ft. (4,572 m) above sea level

Non-Operating 50,000 ft. (17,678 m) above sea

Vibration (RandomVibration (Random

Vibration (Random

Vibration (RandomVibration (Random

20-500 Hz

ASD Level 0.02 g2/Hz, 30 minutes each axis

ShockShock

Shock

ShockShock

Magnitude 50 g peak acceleration

Duration 4 ms (half sine wave)

Number of tests 3 on each of 6 surfaces

Mean Time to FailureMean Time to Failure

Mean Time to Failure

Mean Time to FailureMean Time to Failure

Greater than 30,000 hours

tests performed for 8 hours

level

))

)

))

5 EL4836HB, EL4836HB-ICE

Optical Display Color Optical Display Color

Optical Display Color

Optical Display Color Optical Display Color

Peak wavelength (typ) 585 nm, Yellow-Orange

Pixel LuminancePixel Luminance

Pixel Luminance

Pixel LuminancePixel Luminance

ON luminance Typ. Min.

EL4836HB

at 60 Hz 50 fL (171)* 30fL (103)*

at 120 Hz 100 fL (342)* 60fL (206)*

EL4836HB-ICE

at 60 Hz 16.5 fL (56)* 9.0fL(30.8)*

at 120 Hz 33.0 fL(112)* 18.0fL(61.6)*

*cd/m

Luminance measured at center of display screen,

full ON pattern, 25°C ambient. Note: the Hitachi

61830B LCD controller is limited in frame rate and

will not drive the display to its maximum brightness

potential.

OFF luminance

EL4836HB 0.3 fL maximum (0.7)*

EL 4 83 6H B- I CE 0.1 fL maximum (0.25)*

Luminance measured at center of display screen,

60 Hz frame rate, full OFF pattern, 25°C ambient.

2

Electromagnetic CompatibilityElectromagnetic Compatibility

Electromagnetic Compatibility

Electromagnetic CompatibilityElectromagnetic Compatibility

The display is capable of being operated in a final

product that complies with FCC Docket, Part 15, Subpart

J, class B. The bezel is electrically isolated from the

display circuit nodes.

SafetySafety

Safety

SafetySafety

The display will not inhibit the end product from obtaining

any of the following certifications: UL114/478, CSA

154, IEC 380.

HealthHealth

Health

HealthHealth

An inert, non-toxic, silicon-based oil is used in the

construction of the electroluminescent panel.

Viewing AngleViewing Angle

Viewing Angle

Viewing AngleViewing Angle

Greater than 160° viewing angle.

ICEICE

ICE

ICEICE

TMTM

TM

TMTM

Integral Contrast Enhancemen (ICETM) incorporates a new thin film layer in the EL structure which significantly

reduces light reflections from the display's rear electrode. The EL4836HB-ICE is the ICETM version of the EL4836HB

display, and offers the following performance advantages:

-inherently higher display contrast

-crisper display images

-a lower cost of display system solution for the user

ON luminance uniformity, maximum difference

<26%

Measured between any two of five points (corners

and center): Non-uniformity % = (1 - min luminance/

max luminance) x 100.

ON luminance variation (temp.) max. variation

±15%

from 25°C over 0°C to +55°C range.

ON luminance variation (time), max. difference

±10%

at 25°C within 10,000 hours.

Luminanace Contrast Ratio (ICELuminanace Contrast Ratio (ICE

Luminanace Contrast Ratio (ICE

Luminanace Contrast Ratio (ICELuminanace Contrast Ratio (ICE

TypicalTypical

Typical

TypicalTypical

TMTM

TM

TMTM

))

)

))

8:1 min, @ 500 lux

3:1 min, @ 2000 lux

Fill FactorFill Factor

Fill Factor

Fill FactorFill Factor

57% luminance area/total active area.

Page 6

6EL4836HB, EL4836HB-ICE

Installation and HandlingInstallation and Handling

Installation and Handling

Installation and HandlingInstallation and Handling

Unpacking Unpacking

Unpacking

Unpacking Unpacking

Electrostatic CautionElectrostatic Caution

Electrostatic Caution

Electrostatic CautionElectrostatic Caution

The Planar display and DC/DC converter

assemblies use CMOS and power MOS-FET

devices. These components are electrostatic

sensitive. Unpack, assemble and examine

these assemblies in a static-controlled area

only. When shipping either assembly, use

packing materials designed for protection of

electrostatic-sensitive components.

Unpack and check contents of shipping

container against invoice in a static-controlled

area. Use anti-static bags for storage of displays

and DC/DC converters awaiting assembly

processes. Any discrepancies in materials

received and invoiced should be noted to Planar

within 10 days.

Mounting and Mounting and

Mounting and

Mounting and Mounting and

This display has no mounting holes and is

designed for clamp mounting similar to an LCD.

Do NOT clamp the display by its circuit board.

Mounting compression should be made only on

the metal bezel itself. Connector locations are

shown on Page 7. Contact Planar application

engineers for more information.

CleaningCleaning

Cleaning

CleaningCleaning

Connector Connector

Connector

Connector Connector

LocationsLocations

Locations

LocationsLocations

Mechanical CharacteristicsMechanical Characteristics

Mechanical Characteristics

Mechanical CharacteristicsMechanical Characteristics

Display External DimensionsDisplay External Dimensions

Display External Dimensions

Display External DimensionsDisplay External Dimensions

Height 3.885 in. 98.68 mm

Width 6.964 in. 176.88 mm

Depth 0.575 in. 14.60 mm

Weight (max) 9.5 oz. 270 grams

Recommended air gap behind display places

total depth at 0.75 in (19.04 mm).

DC/DC Converter CharacteristicsDC/DC Converter Characteristics

DC/DC Converter Characteristics

DC/DC Converter CharacteristicsDC/DC Converter Characteristics

Height 2.00 in. 50.8 mm

Width 5.25 in. 133.4 mm

Depth 0.75 in. 19.1 mm

Weight 3 oz. 85 grams

Viewing Area CharacteristicsViewing Area Characteristics

Viewing Area Characteristics

Viewing Area CharacteristicsViewing Area Characteristics

Active area

Width 5.732 in 145.6 mm

Height 2.653 in 67.39 mm

Pixel pitch

Width 0.021 in 0.533 mm

Height 0.021 in 0.533 mm

Pixel size

Width 0.016 in 0.399 mm

Height 0.016 in 0.399 mm

Pixel matrix

Width 276 pixels

Height 128 pixels

Display Face Any non-abrasive mild

glass cleaner can be used.

Circuit Boards Only isopropyl alcohol should

be used on the ECB assemblies.

Avoiding Burn-inAvoiding Burn-in

Avoiding Burn-in

Avoiding Burn-inAvoiding Burn-in

As with any other display, it is prudent to use

screen-saver software to avoid burn-in of images

that remain on the screen for extended periods.

InterconnectionsInterconnections

Interconnections

InterconnectionsInterconnections

J0 Connector: J0 Connector:

J0 Connector: T & B Ansley 609-1627 or equivalent

J0 Connector: J0 Connector:

P0 Mating Connector: P0 Mating Connector:

P0 Mating Connector: T & B Ansley 609-1630 or equivalent.

P0 Mating Connector: P0 Mating Connector:

(customer supplied)

J3 Connector: J3 Connector:

J3 Connector: T & B Ansley 609-2627 or equivalent.

J3 Connector: J3 Connector:

P1 Connector:P1 Connector:

P1 Connector: 3M 3399-7626 or equivalent

P1 Connector:P1 Connector:

Properly mounted, this display can withstand

high shock loads s well as severe vibration in

aggressive environments. However, the glass

panel used in this display will break when

subjected to bending stresses, high impact or

excessive loads.

To prevent injury in the event of glass

breakage, a protective overlay should be

used on the viewer side of the display.

+5V opt.

+12V

VID

VCLK

HS

VS

CautionCaution

Caution

CautionCaution

P0 J3

DC/DC

Converter

J1J0 P3 P1

Display

Page 7

7 EL4836HB, EL4836HB-ICE

Loading...

Loading...