Page 1

SERVICE MANUAL

8M51B CHASSIS

MUTE

FREEZE

POWER

P.P

S.M

SLEEP

ZOOM

HOME

REC CH.LIST FAV EPG

T.SHIFT

INFO

INDEX

SUBTITLE

AUDIO

MTSCC

RETURN

EXIT

OK

MENU

CH

VOL

SOURCE

3

12

6

4

5

789

.

0

Design and specifications are subject to change without prior notice.

(Only Referrence)

SIZE:A5

Description:

MODEL.

JOB NO.

Engineering Dept:

Artwork By:

Checked By:

Approved By:

SERVICE MANUAL 8M51B

Brand Name:

SKYWORTH

Date:

Date:

Date:

2012-5-23

Page 2

Content--------------------------------------------------------------2

11-17

18

19-20

21-28

29-45

46-49

50-57

Page 3

LED 8M51B

Page 4

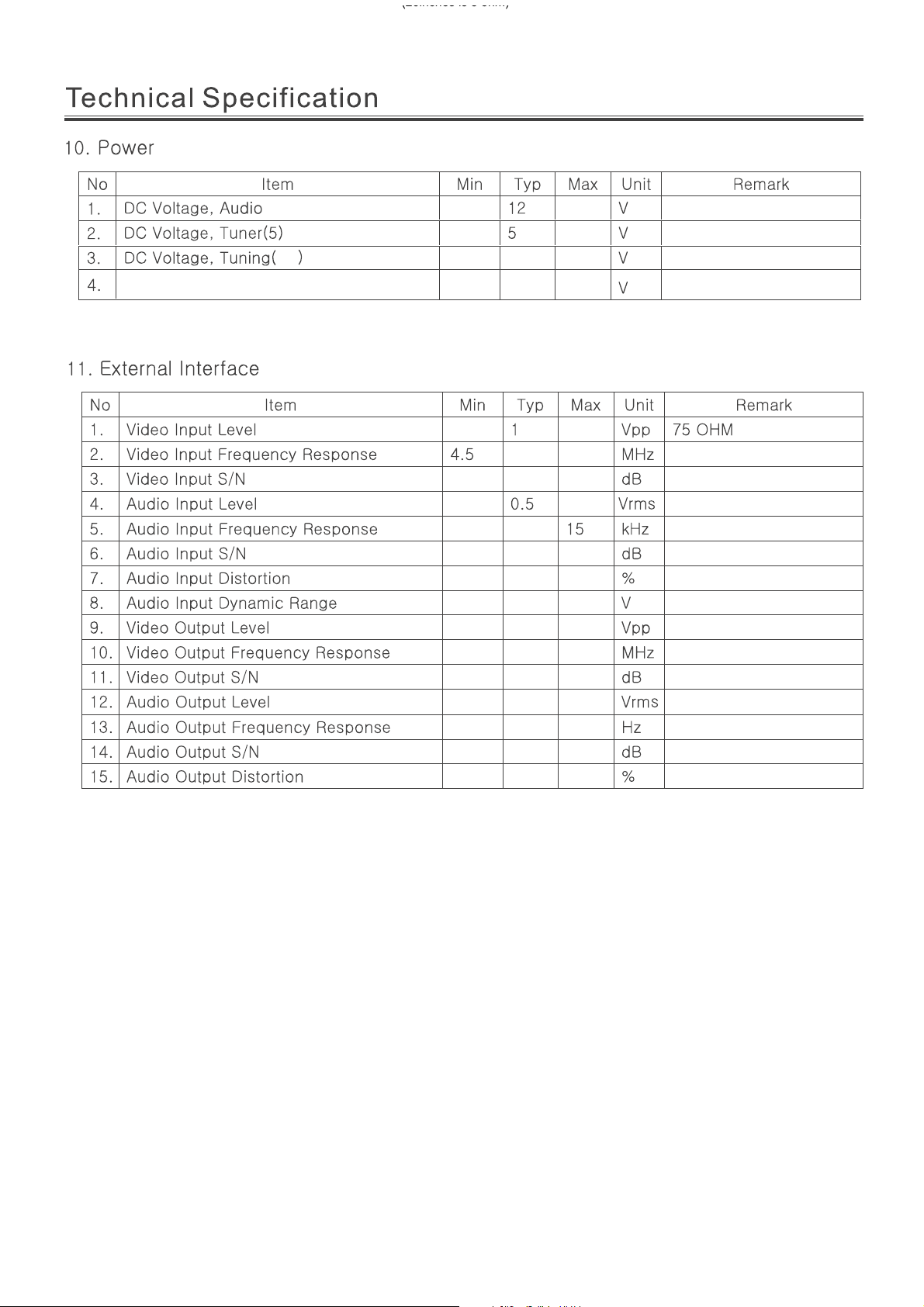

NTSC-M PAL-M PAL-N

Component

VHF LOW 2~B

VHF HIGH C~W+11

VHF W+12~69

TOSHIBA CODE

55.25MHz ~ 127.25MHz

133.25MHz ~ 311.25MHz

367MHz ~ 801.25MHz

Page 5

65

120

140

For 32” LED

For 42” LED

For 47” LED

Page 6

8

8

6

Page 7

(26inches is 8 ohm)

3.3

3.3

DC Voltage, PANEL(12)

80

12

40

40

3

2

1

4.2

50

0.5

12000

40

3

Page 8

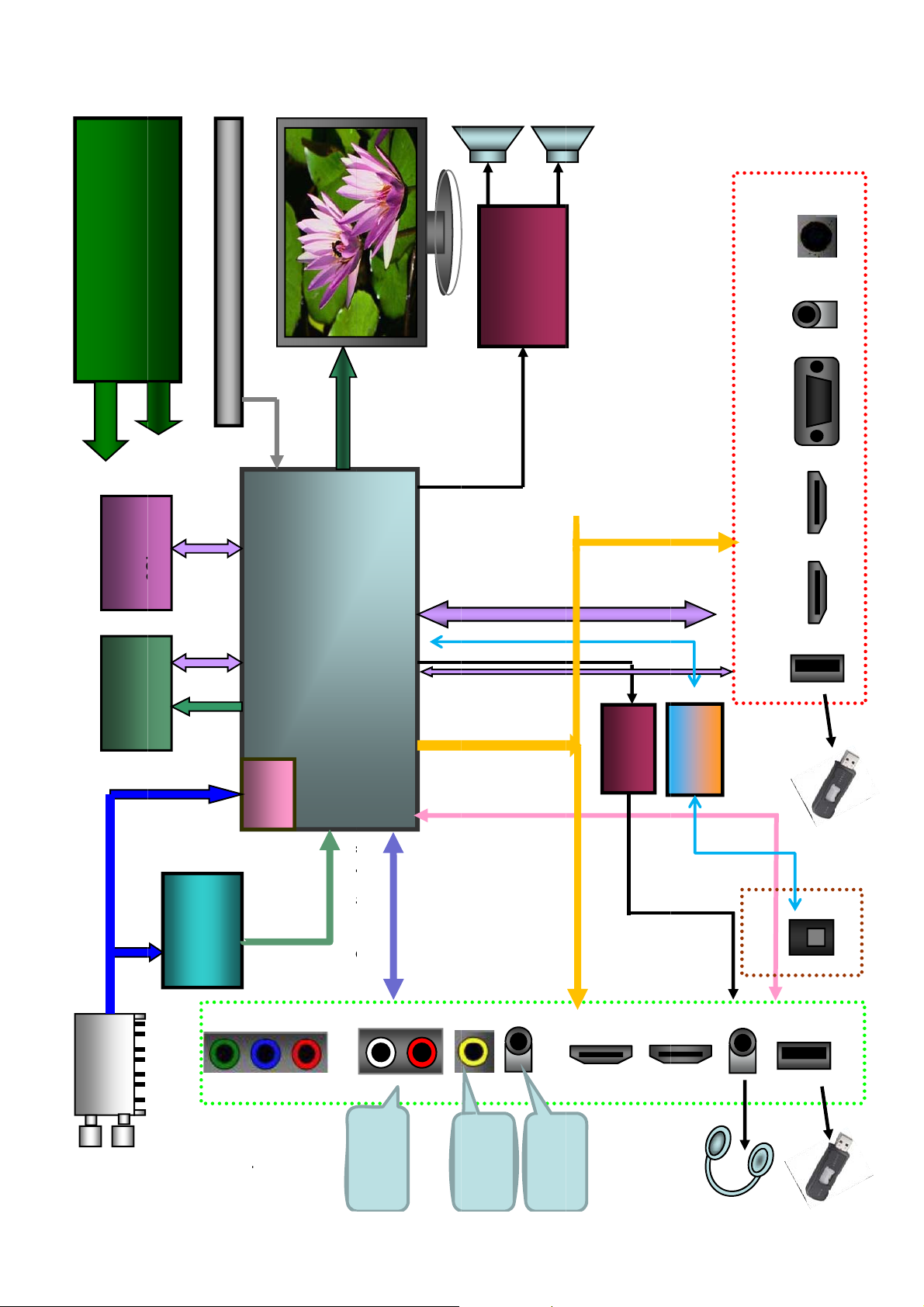

Standard

Standard

20

40

NO

YES

8

6

46

46

NO

Spanish

Page 9

4

2

4

0 40 7 0

0 40 7 0

0 40

40 85

-Y 0 5 0

30000

Page 10

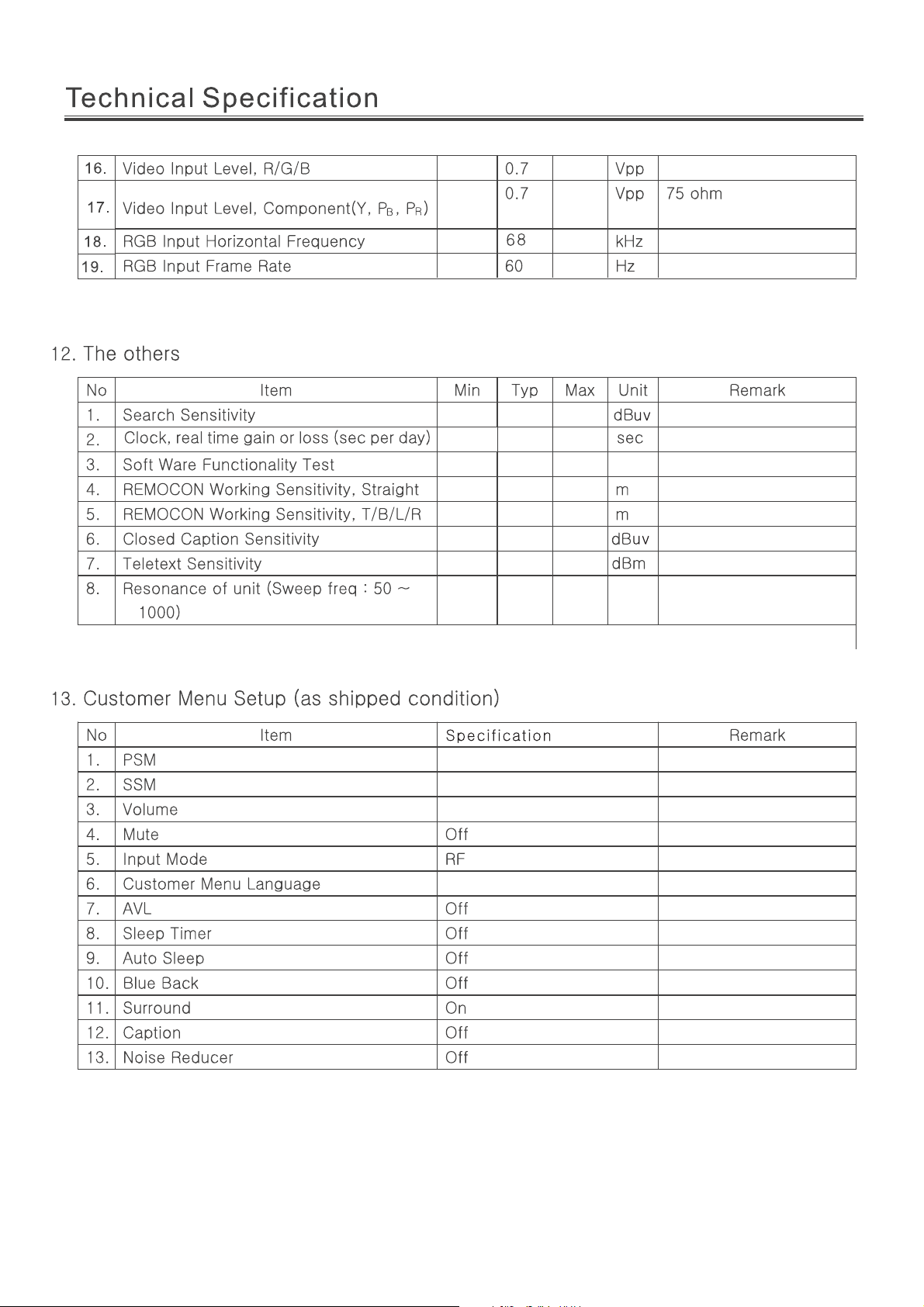

SYSTEM

p

CitAdi

C

it

A

di

Rear Terminal

AMP5707

8W + 8W

KEY PAD, IR Receiver

VGA-Audio

-

FLASH

DDRIII

2Gbx1+1Gbx1

IF+/-

MSD6329

Ultra high speed 32-bi RISC CPU

IF Demo. Build in

MPEG1/2/4 /H.264 Decoder

Analog

Demo

o

u

e +

LED

JPEG MP3 Decoder

PANEL

S

2

I

USB2

USB1

8M51B

.

HP AMP.

BH3544

Transformer

IP101A

R/L

HDMI1

HDMI2

USB2

IF+/-

TC90527

ISDB-T

Demodulator

Block Diagram for 8M51B series

ISDB-T

Analog IF

TUNER

Side Terminal

onent

Com

Serial TS

ompos

L/R

Audio L/R

Composite

HDMI data

Composite

HDMI4

LAN

USB1

HDMI3

Page 11

IC Block Diagram

U2(3.3V/1A 3-TERMINAL POSITIVE VOL TAGEREGULATOR) LD1117-3.3 SOT-223

INPUT

-

Thermal

Shutdown

Ou t

+

-

OUTPUT

GND (Fixed Output)

ADJ (Adjustable Output)

U50 (1.1V/3A LOW DROPOUT LINEARAR REGULATOR)AOZ1051PI SO-8

EN

SS

FB

Reference

& Bias

0.8V

UVLO

& POR

+

EAmp

–

5V LDO

Regulator

Softstart

SS

5μA

Internal

+

PWM

–

Comp

+

+5V

OTP

ILimit

PWM

Control

Logic

Level

Shifter

+

FET

Driver

COMP

500kHz

Oscillator

ISen

VIN

+

–

Q1

LX

Q2

AGND

PGND

Page 12

U3 (2.5V/1A )AS1117L-ADJ A1 SOT-223

Thermal

Shutdown

INPUT

Out

+

-

OUTPUT

GND (Fixed Output)

ADJ (Adjustable Output)

U19 (1.2V/1A)AP1122EG-13 SOT223-3L

Vin

3

Thermal

Shutdown

2 Vout

+

+

CURRENT

LIMIT

1.2V

+

+

GND

1

Page 13

IC Block Diagram

U9(LCDTV CONTROLLER WITH VIDEO ECODE)MSD6329SV-Z1-SVN MSTAR

DVB Digita l T e l evision System -on -Chip

Preliminary PinDiagram /De scrip tion an d Me chan ica l D im ensions Vers ion 0.2

PIN DIAGR AM (M SD 632 9SV)

Top V iew

12345678910111213

A NC LVB0N LVB1P LVBCKN LVB3P LVA 0N LVA 1P LVACKN LVA 3P GN D G ND GN D

B USB0_DM N C N C LVB1N LVB2P LVB3N LVB4P LVA 1N LVA2P LVA3N

C USB0_DP NC NC LVB0P LVB2N LVBCKP LVB4N LVA 0P LVA2N LVACKP LVA 4P

[5 ]

RT C _X OU

GPIO _PM

D NC RTC_XIN

E HW RESET

F SDO

G SD I S C K BIN0P SPD IFO S PD IFI G PIO 198 G PIO 193 GN D GN D G PIO 195 G PIO 183 GN D GN D

H BIN0M SO G IN0 GIN 0P

J GIN 0M R IN0P R IN0M

K B IN1P B IN1M SO G IN1

L GIN 1P GIN 1M R IN1P

M R IN1M B IN2P B IN2M IRIN A V _LINK

N SO G IN2 GIN 2P GIN 2M VSY N C0 H S YN C0 SA R2

GPIO _PM

GPIO _PM

[6 ]/S C Z 1

GPIO 204 GN D GPIO197 GPIO 194 GPIO190 GPIO 202 GPIO 187 LVA4N

T

GPIO 203 GPIO 185 GN D GN D GPIO 199 GPIO189 GPIO 186 GPIO 188

[8 ]

SCZ0 G PIO200 G PIO192 G PIO196 GN D G N D G PIO 191 G PIO201 G PIO 184 GN D GN D

GPIO _PM

GPIO _PM

GPIO _PM

GPIO _PM

[1 0 ]

ET_TX D [1

[1 3 ]

[4 ]

ET_RX D [1]GPIO _PM

[2 ]

ET_R EF_

CLK

]

ET_M DC

ET_TX D [0]ET_TX_E

ET_M D IO

ET_RX D [0]GPIO _PM

[1 ]

GPIO _PM

[3 ]

N

ET_CR S_

DV

[0 ]

GPIO _PM

[1 2 ]

DD CA _D A/

UART0_TX

DD CA _ CK/

UART0_RX

GN D GN D GN D GN D GN D GN D

GN D GN D GN D GN D GN D GN D

GN D GN D GN D GN D GN D GN D

GN D GN D GN D GN D GN D GN D

GN D GN D GN D GN D GN D GN D

GN D GN D GN D GN D GN D GN D

A_DD R3_

A[1]

MSD6329SV

A_DD R3_

A_DD R3_

A_DD R3_

A_DD R3_

A[14]

A[12]

A[11]

A[8]

A_M C LKZ

A_DD R3_

A_DD R3_

A_DD R3_

BA[1]

A[6]

A[4]

P R IN2P R IN2M CV BS5 SA R 0 S AR1 V SY N C1 SA R 3 G N D GN D G N D GN D G N D GN D

R C V B S2 CV BS4 C V B S3 H SY N C1 N C N C PG A_ C OM BY P ASS GN D G N D GN D G N D GN D

NC

IV E

MP LL

[6 ]

[4 ]

[5 ]

AVD D _AU

33

AVD D _EA

R33

GN D G N D GN D

TS1DATA

[1 ]

TS1DATA

[0 ]

TS0DATA

[7 ]

VD D C GN D GN D GN D

GN D GN D GN D

TS 1V A LID T S1 CLK G P IO 137

TS1DATA

[3 ]

TS1DATA

[2 ]

TS1DATA

[4 ]

TS1DATA

TS0VA LID TS0CLK

TS1DATA

[5 ]

[6 ]

TS0DATA

[2 ]

TS1DATA

[7 ]

PCMA D R[1

2]/CI_A[12

]

TS0DATA

[1 ]

TS0DATA

[0 ]

TS0SYNC

C25

NC

AVD D _M

AVD D _AD

AVD D _DV

TS2VALID

K

HOTPLUG

T CV BS1 VCO M CVBS0 AUR0 AU L0

CVBSO UT0CVBSO UT

U

V AU VRM AU VAG AU L2

W AUR2 A U L3 AUR3 G N D GN D G N D N C G N D

Y AUL4 AUR4 AU L1

AA AUR1 AUO UTL1 AUOUTR1

AB AUO UT L0 AUO UTR0

EAR_O UT

AC

R

AD GPIO 180 GPIO 181 GPIO 182

AE G PIO 179 IP VIFM SIFM N C N C

AF IM VIFP SIFP NC NC CEC RXCCKP RXC1N RXC2P RXD0N RXD1P RXBCKN

12345678910111213

XIN XO UT

AUVRP

1

EAR _O UTLDDCDD_CKDDCDB_DADD CD A_C

AVD D _RE

AVD D _DV

DDCDC_CKDDCDC_DADD CD A_DAHOTPLUGBTS0DATA

HOTPLUGCDDCDB_C

DDCDD_

RF_AGC/

F25

I_ U SB

DA

TAGC

AVD D _AD

AVD D _DV

I_ U SB

IF_ A GC A R C0

OD33

C25

I_ U SB

K

D

AVD D _PG

A25

AVD D _AL

NC

AVD D _MPLLAVD D _D

TS2DATA

TS2CLK TS2SYNC TS1SYNC

TS0DATA

RX CC KN RX C 0P RX C 2N RX D C KP RX D 1N RX D 2P RX B 0N

HOTPLUG

TS0DATA

[0 ]

TS0DATA

[3 ]

RX C 0N RX C1P RX D C KN RX D 0P RX D 2N RX B CKP

A

D o c. N o .:20120 10163

Copyright

1/25/2011

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

Page 14

MSD6329SV

20120 1 0163

DVB Digita l T e l evision System -on -Chip

Preliminary PinDiagram /De scrip tion an d Me chan ica l D im ensions Vers ion 0.2

14 15 16 1 7 18 19 20 21 22 23 24 25 2 6

GN D G N D GN D G N D GN D GN D GN D GN D GN D GN D GN D GN D G N D A

A[10]

A_DD R3_

DQL[5]

A_DD R3_

DQL[7]

A_RASZ A_CA SZ

A_M C LK

A_M CLKE

A_DD R3_

A_O DT A_W EZ

GN D G N D GN D G N D GN D GN D GN D GN D

GN D G N D GN D G N D GN D GN D GN D GN D

GN D G N D GN D G N D GN D GN D GN D GN D

GN D G N D GN D G N D GN D GN D GN D GN D

GN D G N D

GN D G N D GN D

GN D G N D GN D

GN D G N D GN D

GN D G N D GN D G N D GN D GN D GN D GN D

GN D G N D GN D G N D GN D GN D GN D

GN D G N D GN D G N D GN D VD D C GN D GN D

GN D G N D GN D G N D GN D

VDDC VDDC

GN D G N D GN D G N D GN D VD D C A V D D _11

]

NF_AD[1]/P

CMA D R[1]/

CI_A[1]

NF_AD[4]/P

CMA D R[4]/

CI_A[4]

PCMA D R [1

4]/CI_A[14

GPIO 138

NF _ W PZ G PIO 140

PCMA D R [1

1]/CI_A[11

PCMR EG/

CI_CLK

]

RX B 1P RX AC KN RX A 0P RX A 2N

RX B 1N RX B2P RX A0N RX A1P

RX B 0P RX B 2N RX AC KP RX A 1N RX A 2P PC M W EN P C M O EN

14 15 16 1 7 18 19 20 21 22 23 24 25 2 6

A_DD R3_

DQL[1]

A_DD R3_

DQL[3]

AVD D _DDR0AVD D _DDR0AVD D _DDR0AVD D _DD

A_DD R3_

DQU[2]

A_DD R3_

DQML

A_DD R3_

BA[0]

A_DD R3_

A[3]

A_DD R3_

DQU[6]

A_DD R3_

DQU[0]

A_DD R3_

A[5]

A_DD R3_

A[7]

A_DD R3_

DQSBU

A_DD R3_

DQU[4]

A_RESET

A_DD R3_

A[9]

R0

AVD D _DDR0AVD D _DDR1AVD D _DD

R1

AVD D _DDR1AVD D _DD

R1

AVD D _DD

R1

GN D G N D GN D GN D

GN D GN D GN D

DVDD_D

DR

DVDD_D

DR

NF_AD[0]/P

CMA D R[0]/

CI_A[0]

NF_AD[2]/P

CMA D R[2]/

CI_A[2]

NF_AD[7]/P

CMA D R[7]/

CI_A[7]

NF_AD[5]/P

CMA D R[5]/

CI_A[5]

NF_CEZ NF_CEZ1 GN D VD DC N C VD DP VDD P

NF_AD[3]/P

CMA D R[3]/

CI_A[3]

NF_AD[6]/P

CMA D R[6]/

CI_A[6]

GPIO 139

NF _R EZ GN D VD D C VD D C V D D C VD D C PW M2 PW M4 PW M1 AA

NF_RBZ NF_ALE GPIO 40 NC VDDC VDDC PW M3 PW M0 USB1_DP AB

PCMA D R[1

3]/CI_A[13

PCM IRQ/

CI_INT

PCM W AIT

/C I_ W A C

NF _ C LE NF _W EZ G PIO 39

]

PCM IO R/

CI_RD

PCM IO W/

CI_WR

K

A_DD R3_

A_DD R3_

DQSBL

A_DD R3_

A_DD R3_

DQSU

A[13]

DQU[1]

A_DD R3_

DQSL

A_DD R3_

GN D GN D

GN D GN D

BY P ASS_

VCO RE

A[2]

A_DD R3_

DQU[7]

A_DD R3_

DQU[3]

A_DD R3_

A[0]

B_DD R3_

A[14]

B_DD R3_

A[8]

B_DD R3_

A[4]

B_DD R3_

BA[1]

B_DD R3_

A[3]

B_DD R3_

A[7]

B_DD R3_

A[9]

B_DD R3_

A[2]

B_DD R3_

BA[2]

A_DD R3_

DQMU

A_DD R3_

DQU[5]

A_DD R3_

BA[2]

B_M C LKE

B_DD R3_

A[1]

B_DD R3_

A[11]

B_DD R3_

A[6]

B_DD R3_

A[12]

B_DD R3_

A[10]

B_DD R3_

BA[0]

B_DD R3_

A[5]

B_RESET

B_DD R3_

A[13]

B_DD R3_

A[0]

A_DD R3_

DQL[0]

A_DD R3_

DQL[2]

B_DD R3_

DQL[7]

B_DD R3_

DQL[3]

B_DD R3_

DQML

B_DD R3_

DQU[0]

B_DD R3_

DQU[4]

B_DD R3_

DQSBL

B_DD R3_

DQSL

B_DD R3_

DQU[3]

B_DD R3_

DQU[5]

B_DD R3_

DQL[2]

B_DD R3_

DQL[6]

B_ODT B_RASZ GND R

B_ W EZ B_ C A SZ GND T

GN D GN D GN D GN D N C N C

GN D GN D GN D GN D

GPIO 45

PCM CEN/

CI_CS

AVD D _LP

LL

PCMA D R [5]

/CI_A[5]

PCMA D R [0]

/CI_A[0]

GPIO 44/U

ART2_RX

GN D GN D G P IO 102

GPIO 42/U

ART1_TX

PCMA D R [2]

/CI_A[2]

PCMA D R [6]

/CI_A[6]

PCMA D R [1]

/CI_A[1]

GPIO 41/U

ART1_RX

PCMA D R [3]

/CI_A[3]

PCMA D R [4]

/CI_A[4]

CI_RST G P IO 141

I2 S _ O U T

_BCK

I2 S _ I N _ W

S

USB1_DM USB2_DP U SB2_DM AC

PCMA D R [8]

/CI_A[8]

PCMA D R [7]

/CI_A[7]

A_DD R3_

DQL[4]

A_DD R3_

DQL[6]

B_DD R3_

DQL[5]

B_DD R3_

DQL[1]

B_DD R3_

DQU[2]

B_DD R3_

DQU[6]

B_DD R3_

DQSBU

B_DD R3_

B_DD R3_

DQU[1]

B_DD R3_

DQU[7]

B_DD R3_

DQMU

B_DD R3_

DQL[0]

B_DD R3_

DQL[4]

I2 S _ O U T

I2 S _ I N _ SDI2 S _ I N _ B

DQSU

_WS

B_M CLKZ B

B_M CLK C

GND D

GND E

GND F

GND G

GND H

GND J

GND K

GND L

GND M

GND N

GND P

I2 S _ O U T

_SD

I2 S _ O U T

_M CK

CK

DDCR_ CK DDCR_DA Y

PCMA D R [1

0]/CI_A[10

CI_CD

GPIO 43/UA

RT2_TX

]

GPIO 38 AD

PCMA D R [9]

/CI_A[9]

U

V

W

AE

AF

Doc.No.:

Copyright

1/25/2011

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

Page 15

MSD6329SV

20120 1 0163

DVB Digita l T e l evision System -on-Chip

Preliminary P inDiagram /De scription an d Me chan ical D im ension s Version 0.2

Pin N ame Pin Type Fun ction Pin

G PIO [40:38 ] I/O w / 5V -tolerant G eneralPurpose Input/O utput; 4m A driving strength AB 20,A C21,

AD26

G PIO _P M[ 1 3:12] I/O w / 5V -tolerant G eneralPurpose Input/O utput; 4m A driving strength J4, L7

GPIO_PM[10] I/O w/5V-tolerant G eneralPurpose Input/O utput; 4m A driving strength H 4

G PIO _PM[ 8] I/O w / 5V -tolerant G eneralPurpose Input/O utput; 4m A driving strength E3

G PIO _PM[ 6]/

SCZ1

I/O w / 5 V -t o l erant G eneralPurpose Input/O utput; 4m A driving strength /

ExternalSPI Flash C hipSelect

F2

G PIO _P M[ 5 :0] I/O w / 5V -tolerant G eneralPurpose Input/O utput; 4m A driving strength E2,K4, M 6,L4,

L6, K7

PW M 4 O utput PulseWidth M odulation O utput; 4m A driving strength

AA25

PW M 3 O utput PulseWidth M odulation O utput; 4m A driving strength A B 24

PW M 2 O utput PulseWidth M odulation O utput; 4m A driving strength A A 2 4

PW M 1 O utput PulseWidth M odulation O utput; 4m A driving strength A A 2 6

PW M 0 O utput PulseWidth M odulation O utput; 4m A driving strength A B 25

SAR3 Analog Input SAR Low Speed AD C Input 3;

P7

G eneralPurpose Input/O utput

SAR2 Analog Input SAR Low Speed AD C Input 2;

N6

G eneralPurpose Input/O utput

SAR1 Analog Input SAR Low Speed AD C Input 1;

P5

G eneralPurpose Input/O utput

SAR0 Analog Input SAR Low Speed AD C Input 0;

P4

G eneralPurpose Input/O utput

Doc.No.:

Copyright

1/25/2011

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

Page 16

DVB Digita l T e l evision System -on-Chip

20120 1 0163

Preliminary P inDiagram /De scription an d Me chan ical D im ension s Version 0.2

DR AM Interfa ce

Pin N ame Pin Type Fun ction Pin

MSD6329SV

A_DD R3_A

[1 4 :0]

O utput D RAM M em ory Address B12,D20,C12,

D 12, D 14,E19,

E12,E18,D 13,

D 18, E13, E 17,

D21,B11,D22

A_DD R3_BA

O utput D R A M M em ory B ank A dd ress D 23, C 13, D 17

[2 :0]

A_M CLKE O utput D R A M M em ory C lock Enable C14

A_O D T I/O Reserved for future O n-D ieTermination E15

A_W EZ O utpu t W rite Enable; active low E16

A_R ASZ O utput Row Address Strobe; active low D 15

A_CASZ O utput Column Add re ss Strobe; active low D 16

A_M CLK O utput D RAM M em ory Positiv e D iffe re n t i alClock B1 4

A_M CLKZ Output DRAM M em ory Negative D ifferentialClock B13

A_DD R3_D Q MU O utput D ata M ask forLow Byte; active high B23

A_DD R3_D Q ML O utput D ata M ask forLow Byte; active high C17

A_DD R3_D Q SU I/O D ata Strobe B20

A_DD R3_D Q SL I/O Data Strobe C 21

A_DD R3_D Q SBU I/O D ata Strobe Inverse B19

A_DD R3_D Q SBL I/O D ata Strobe Inverse C 20

A_DD R3_D QU

[7 :0]

I/O D RAM M em ory D ata Bus B22,B18,C23,

C19,C22,B17,

B21, C18

A_DD R3_D QL

[7 :0]

I/O D R A M M e m o ry D a ta B u s C 1 5 , C 2 5 , B 1 5 ,

B25, C16,C 24,

B16, B24

A_R ESET Input D R A M M em ory R eset; active low D 19

B_D DR 3_A

[1 4 :0]

O utput D RA M M em ory Address G 22, R2 3,K23,

H 23, L23, P22,

H22,N22,J23,

N23,J22,M 22,

R22,G 23,T23

B_D DR 3_BA

O utput D R A M M em ory B ank A ddress T 22,K 22,M 23

[2 :0]

B_M CLKE O utput D R A M M em ory C lock Enable E23

B_O D T I/O Reserved for future O n-D ieTermination R 24

Doc.No.:

Copyright

1/25/2011

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

Page 17

DVB Digita l T e l evision System -on-Chip

20120 1 0163

Preliminary P inDiagram /De scription an d Me chan ical D im ension s Version 0.2

Pin N ame Pin Type Fun ction Pin

B_W EZ O utput W rite Enable; active low T24

B_R ASZ O utput R ow Address Strobe; active low R 25

B_CASZ O utput Column Address Strobe; active low T25

B_M CLK Output D RAM M em ory Positiv e D ifferen tialClock C26

B_ M CLK Z O utput D R A M M em ory N egative D ifferential C lock B 26

B_D D R 3_D Q MU O utput D ata M ask for Low Byte; active h igh M 25

B_DDR3_DQML Output Data Mask forLow Byte;active high F24

B_DDR3_DQSU I/O Data Strobe J25

B_DDR3_DQSL I/O Data Strobe K24

B_DDR3_DQSBU I/O Data Strobe Inverse H 25

B_DDR3_DQSBL I/O Data Strobe Inverse J24

MSD6329SV

B_D DR 3_DQU

[7 :0]

I/O D R A M M em ory D ata B u s L25, G 2 5, M 24,

H 24 , L24, F25,

K25, G 24

B_D DR 3_DQL

[7 :0]

I/O D RA M M em ory D ata Bus D 24, P24,D 25,

P25,E24,N 24,

E25,N 25

B_ RE SET In put D R A M M em ory R eset; active low P23

Ethernet RM IIInterface

Pin N ame Pin Type Fun ction Pin

ET_CR S_D V I/O w / 5V-tolerant Eth ernet M AC Ca rrier Sense/R eceive D ata Valid J7

ET_TXD [1:0] O utput w / 5V -toleran t E thernet M A C T ran sm itD ata B u s J5 ,H6

ET_TX_EN O utput w / 5V -toleran t E thernet M A C T ran sm itEnable H7

ET _R EF_C LK Input w / 5V-tolerant Ethernet M AC Synchronous C lock R eferen ce for R eceive,

Transm itand ControlInterface

ET_R XD [1:0] Input w / 5V-toleran t E th ern et M AC R eceive Da ta Bus L5, K6

ET_M D C O utput w / 5V-toleran t E thernet M A C M anagem en t Da ta Clock K5

ET_M D IO I/O w / 5V-tolerant Ethernet M AC M anagem entD ata Bus J6

H5

Doc.No.:

Copyright

1/25/2011

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

Page 18

MSD6329SV

20120 1 0163

DVB Digita l T e l evision System -on-Chip

Preliminary P inDiagram /De scription an d Me chan ical D im ension s Version 0.2

USB Interface

Pin N ame Pin Type Fun ction Pin

USB0_DP Analog I/O U SB N on Inverting D ata Input/O utputfor Port0 C1

USB0_DM Analog I/O U SB In verting Da ta Input/O utput for Port 0 B1

USB1_DP Analog I/O U SB N on Inverting D ata Input/O utputfor Port1 AB26

USB1_DM Analog I/O U SB In verting Da ta Input/O utput for Port 1 AC 24

USB2_DP Analog I/O U SB N on Inverting D ata Input/O utputfor Port2 AC25

USB2_DM Analog I/O U SB In verting Da ta Input/O utput for Port 2 AC 26

UART Interface

Pin N ame Pin Type Fun ction Pin

GPIO44/

U ART2_RX

GPIO43/

U ART2_TX

GPIO42/

U ART1_TX

GPIO41/

U ART1_RX

D D CA _DA/

U ART0_TX

DDCA_CK/

U ART0_RX

I/O w / 5 V -t o l erant G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchronous R eceiver 2

I/O w / 5 V -t o l erant G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchronous Transm itte r 2

I/O w / 5 V -t o l erant

G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchronous T ransm itte r 1

I/O w / 5 V -t o l erant

G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchron ous R eceiver 1

I/O w / 5 V -t o l erant DDC D ata for A n alog port /

UniversalAsynchronous T ransm itte r 0

I/O w / 5 V -t o l eran t DDC C lock for A n alog port /

UniversalAsynchron ous R eceiver 0

AF21

AF25

AC22

AC23

M7

N7

VIF Interface

Pin N ame Pin Type Fun ction Pin

VIFM Analog Input N egative Video IF Input AE3

VIFP Analog Input P ositive Video IF Input AF3

RF_AGC/

TAGC

Analog O utput R F A G C /

Tun erA utom aticG ainControlO utput

AD4

PGA_CO M Analog Input V IF PG A N egative Source R7

Doc.No.:

Copyright

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

1/25/2011

Page 19

MSD6329SV

20120 1 0163

DVB Digita l T e l evision System -on-Chip

Preliminary P inDiagram /De scription an d Me chan ical D im ension s Version 0.2

Misc.Inter face

Pin N ame Pin Type Fun ction Pin

D D CA _DA/

U ART0_TX

DDCA_CK/

U ART0_RX

I/O w / 5 V -tol era nt D DC Da ta for A nalog p ort /

UniversalAsynchronous Transm itte r 0

I/O w / 5 V -tol erant DDC Clock for A n alog port /

UniversalAsynchronous Receiver 0

M7

N7

D D CDA _DA I/O w / 5V -tolerant H DC P SerialBus Data /DDC Data ofDVI/HDMIPortA Y6

D D CDA _CK Input w / 5V -toleran t HDC P SerialBus C lock / D D C ClockofDVI/HDMIPortA AB6

DDCDB_DA I/O w/5V-tolerant H DC P SerialBu s D ata / D D C Da ta of D VI/HD M I Port B A B5

DDCDB_CK Inputw/5V-tolerant H DC P S erialBu s C lock / D D C C lockofDVI/HDMIPortB AA5

D D CDC _DA I/O w / 5V -tolerant H DC P SerialBu s D ata / D D C Da ta of D VI/HD M I Port C Y5

D D CDC _CK Input w / 5V -toleran t HDC P SerialBus C lock / D D C ClockofDVI/HDMIPortC Y4

D D CDD _DA I/O w / 5V-tolerant H DC P SerialB us D ata / D D C Da ta o f D VI/H D M I P o rt D AC 4

D D CDD _CK Input w / 5V-tolerant H DC P S erialBus C lock / D D C C lockofDVI/HDMIPortD AB4

HOTPLUGA I/O w/5V-tolerant H ot-plug controlforDVI/HDMIPortA AE7

H O T PLU GB I/O w / 5V -tolerant H ot-plug controlfo r D VI/H D M I Po rt B Y7

HOTPLUGC I/O w/5V-tolerant H ot-plug controlforDVI/HDMIPortC AA4

HOTPLUGD I/O w/5V-tolerant H ot-plug controlforDVI/HDMIPortD AD6

D D C R _DA I/O w / 5V -toleran t D DC Da ta fo r R O M Y 26

D D C R _C K I/O w / 5V-tolerant D DC Clock for RO M Y25

XIN C rystalO scillator Inpu t CrystalO scillator Inpu t A C2

XO UT C rystalO scillator O utput C rystalO scillator O utput A C3

RTC_XOU T CrystalOscillator O u tput R TC 32KH z CrystalO utput D3

RTC_XIN CrystalOscillator Input RT C 32K H z C rystalInp ut D2

IR IN Input w / 5V-tolerant IR R eceiverInput M4

H W R ESET Schm ittTriggerInput w /

Hardware Reset;active high E1

5V-tolerant

BYP A SS For ExternalBypass Capacito r R 8

IF_AG C O utput w / 5V -tolerant IF AG C A C5

RF_AGC/

TAGC

O utput w / 5V -tolerant R F A G C /

Tun erA utom aticG ainControlO u tpu t

AD4

CEC I/O Consum er ElectronicsControl AF7

AV_LINK

BYP ASS_VCO RE

I/O

Output

AV Link

In tern al VCO R E Volta g e T e st ing Point

M5

R21

Doc.No.:

Copyright

1/25/2011

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

Page 20

DVB Digita l T e l evision System -on-Chip

20120 1 0163

Preliminary P inDiagram /De scription an d Me chan ical D im ension s Version 0.2

Pow er Pins

Pin N ame Pin Type Fun ction Pin

AVDD _LP LL 3 .3V P ow er LPLL P ow er W 21

A V DD _D M PLL 3.3V P ow er CrystalPow er V8

A V DD _M PLL 3.3V Pow er M PLL Pow er V7

AVDD _ALIVE 3.3V Pow er Alive D om ainIO Power U8

AV DD _D VI_U SB 3.3V Pow er D VI U SB Pow er V4-V6

AV DD _EAR 33 3.3V Pow er Earphone D river Pow er U 9

A V DD _A U 33 3.3V P ow er Audio Pow er T9

AV DD _AD C25 2.5V Pow er V ideo AD C Pow er U 5, U6

AV DD _REF25 2.5V Pow er D em od AD C Pow er U 4

AV DD _M O D 33 3.3V Pow er M O D 3.3V Pow er T6

AV DD _PG A25 2.5V Pow er Dem od PG A Pow er T 7

AVDD _11 1.1V Pow er A nalog 1.1V Pow er W 20

AVDD _DD R0 1.5V Pow er D D R3 Pow er K1 6-K19,L17

MSD6329SV

AVDD _DD R1 1.5V Pow er D D R3 Pow er L18, L19,M 17,M 18,N 17

D V DD _DDR 1.1V Pow er D D R 1.1V Pow er U19,V 19

VD DP 3.3V Pow er D igitalInput/O utput Pow er Y22,Y 23

VDDC 1.1V Pow er D igitalCore Pow er T10,T 19,V14, V16,W 19,Y20,

AA20-AA23,AB22,AB23

G ND G round Ground A11-A 26,D 5,D 26, E6,E7,E26,F7,

F8, F12-F21, F26, G 8, G 9, G 12-G 2 1,

G26,H8-H21,H26,J8-J21,J26,

K8-K15,K 20,K21,K26, L8-L16,L20,

L21 , L26, M 8-M 16 , M 19-M 21, M 26,

N 8-N 16,N 18-N 21, N 26,P8-P21,P2

R 9-R 20, R 2 6, T11-T18,T 2 0, T 21,

T26,U10,U12-U18,U20-U23,

V 9 -V 1 1 , V 2 0 -V 2 3 , W 9 - W 1 1 ,

W 13-W 18,W 22,W 23,Y19,AA 19

No Connects

Pin N ame Pin Type Fun ction Pin

NC No conn ect A2,B2,B3,C2,C3,D 1,R5,R6,T8,

U 7,U24,U 25,W 12,Y21,AB21,

A E5, AE6, AF 5, A F6

AD5 ,

6,

Doc.No.:

Copyright

1/25/2011

2011 M Star Sem icond ucto r, Inc . A llri gh ts re s e rv e d .

Page 21

IC Block Diagram

U1(DUAL BTLCLASS D AUDIO AMPLIFIER) TAS5707

SDIN

MCLK

SCLK

LRCLK

SDA

SCL

Serial

Audio

Port

Sample Rate

Autodetect

and PLL

Serial

Control

Terminal Control

L

7BQ

R

7BQ

Microcontroller

Based

System

Control

mDAP

V

O

L

U

M

E

DRC

Click and Pop

Control

S

R

C

th

4

Order

Noise

Shaper

and

PWM

2HB´

FET Out

2HB´

FET Out

Protection

Logic

OUT_A

OUT_B

OUT_C

OUT_D

Page 22

U4 ˄1.5V/5A˅AS1084R/TRͲLFADJUSTABLETOͲ252

U52 ǃU59˄5V/2A˅MP1494DJͲLFͲZTSOTͲ23Ͳ8

U18 ˄3.3V/5A˅AS1084RͲ3.3/TRͲLFTOͲ252

Page 23

Page 24

U1664MX16BITGͲDIEDDR3Ͳ1333SDRAMFBGAͲ96

Page 25

U17128MX16BITGͲDIEDDR3Ͳ1333SDRAMFBGAͲ96

Page 26

U816MBSPIFLASHSOPͲ8

U212GBITCMOSNANDEEPROMTSOPI48

Page 27

Page 28

Main PCB Top/Bottom Layer

Page 29

Main PCB Top/Bottom Layer

Page 30

8M51B

Service Adjustment

(V0. 1)

Page 31

1. How to enter and exit factory mode

Press Source button, and then press digital button “3”, “1”, “9”, “5” in turns to enter the factory menu. Press ©

and ª button to choose the item

In the factory mode, press “menu” key can exit the factory mode.

Software information:

Enter factory mode, you can get the software information from the bottom of menu.

ˈpress OK button to enter the submenu and press ¨ button to adjust the value.

Panel information:

Enter factory mode, enter “PANEL CONTROL” item, you can get the panel information from the bottom of

menu.

Aging mode

Enter factory mode, select “SYSTEM SETTING” item, press OK button enter, select “AGING MODE” item,

press ¨ button open aging mode.

Note: You can press the shortcut key in the factory remote control to open or close the aging mode.

4. How to adjust ADC

Before adjusting, enter the channel you want to adjust and input adjust signal (YPBPR channel: 576P and 720P,

100% color bar; VGA channel: 1366*768, tessellated white and black). Select “AUTO ADC”, press¨button to

auto adjusts the ADC value.

100% color bar

Page 32

Tessellated white and black

Note: 1. The YPBPR and VGA’s Auto White Balance adjust (AUTO ADC) must be done on the product line.

2. In YPBPR channel, must adjust the SD and HD two modes.

5. How to adjust White Balance

Enter factory mode, select W/B ADJUST and go to the “MODE” item to select the channel which you want to

adjust then select the color temperature (Medium, Warm, Favorite and Cool). Then press ª Key to go to these

items you want to adjust:

R Gain

G Gain

B Gain

R Offset

G Offset

B Offset

Press § or ¨ key can adjust the value to the best effect.

COPY ALL: Copy there values to all source!

6. How to update MBoot

MBoot: The boot software, which is stored in the SPI flash.

(1) Open MSTAR ISP Utility tool.

Page 33

(2) Connect the debug tool to the device, turn on TV. Press “Connect” button.

(3) Press “Read” button to choose the MBoot file.

Page 34

(4) Press “Auto” button, set parameter.

(5) Press “Run” button to begin program.

(6) If program success, it will show “Pass” message, otherwise, you need to reconnect and try again.

Page 35

7. How to update main software (by USB):

˖

˖

(1) Copy the new software (name by “MstarUpgrade.bin”) to the root directory of USB drive.

(2) Plug the drive to the USB socket.

(3) Enter factory, select “Software Update (USB)” item and press OK button to begin update.

(4) TV set will restart when finish.

Note:

(1) You need to do “Restore Default” in the factory mode after software update.

(2) You need to restart the TV set again by AC power.

8. HDCP key and MAC address burning

(1) Turn on TV and insert the bus wire of burning tool to main board of CON32.

(2) Enter into factory mode then set the “I2C BUS” to off.

(3) Put the code bar spear on the code bar then press the switch to begin burning.

(4) After burning, set the “I2C BUS” to on.

9. ESN master(24C08 E2PROM)

Note: 8M51B use the 24C04 on the board.

Page 36

ADC ADJUST MODE

NIAG-R

NIAG-G

NIAG-B

TESFFO-R

TESFFO-G

TESFFO-B

CDAOTUA

W/B ADJUST MODE

looC/mraW/muideMERUTAREPMET

NIAG-R

NIAG-G

NIAG-B

TESFFO-R

TESFFO-G

TESFFO-B

LLAYPOC

Panel control TI Mode On/Off On/Off : adjust the TI mode of LVDS

hctiwslennahcneve-ddoffO/nOSDVL

)tib03(01/)tib42(8retemaraPffO/nOtroP

ecrruoSputratSNACSREVO

porCthgiR

porCpU

porCnwoD

SYSTEM SETTING Fac.Hotkey On/Off Factory hot key enable

ffO/nOedoMgnigA

OSD Language English On/Off

ffO/nOHCNERF

ffO/nOESEUGUTROP

ffO/nOHSINAPS

Input Sourrce AV1 On/Off

ffO/nO2VA

ffO/nO1IMDH

ffO/nO2IMDH

ffO/nO3IMDH

ffO/nO4IMDH

ffO/nO1VUY

ffO/nO2VUY

ffO/nOBGR-CP

Top/Bottom/Left/Right

HCNERF/ESEUGUTROP/HSINAPS/hsilgnEegaugnaLtluafeD

elihC/ureP/anitnegrA/lizarByrtnuoC

/nOrewoP/yromeM/ybdnatSedoMnOrewoP

gnikrowlamron-no,neposub-ffOffO/nOSUBC2I

latesertluafeDerotseR l value to factory default

tluafedotlennahcteserslennahcteserP

ehtfoezisehttsujdanacsmetiesehTporCtfeL

Page 37

Analog Curve Mode

BRIGHTNESS

CONTRAST

SATURATION

HUE

SHARPNESS

VOLUME

PICTURE MODE Startup Source

MODE Natural/Cinema/Favorite/Game/Dynamic

BRIGHTNESS

CONTRAST

COLOR

SHARPNESS

TINT

Mac Address Update

HDCP Key Update

CI PLUS Key UPDATE No use

SOFTWARE UPDATE(USB)

SW INFORMATION

SSC SETTING

VIF INITIALIZATION

PIP/POP PIP/POP

PIP Border Width

3D 3D

3D Output Mode

CUSTOMER SETTING

WHITE PATTERN

WDT

PVR RECORD ALL

UART ENABLE

CI+Credential Mode No use

Power on LOGO Select the logo

Stagecraft 1.2 certification

Audio Hidev Mode No use

Others

Netflix Key Update

2Q2II

2Q2II

2Q2II

2Q2II

2Q2II

Tes t pat t ern

Watch dog

Off- close the UART debug. On- open

Page 38

External Schematic and Connections

Note: The graphics are for representation only.

Front view

3

21

5 4 367

1

Power indicator / Remote sensor

2

Speakers

3

Standby Button

4

Source Button

5

Menu Button

6

Volume Down/Up Button

7

Channel Down/Up Button

1

2

Page 39

External Schematic and Connections

Note: The graphics are for representation only.

Back view

Side and Rear AV terminals view

1

LAN

2

USB1/2

3

HDMI1/2/3/4

4

PC-RGB input

5

PC-RGB audio input

6

RF input

7

YPbPr input

8

AV input

9

Earphone output

10

S/PDIF output

LAN IN

USB1

5V 500mA

HDMI1

1 2 3 4 5 6

HDMI IN

HDMI2

PC-RGB

IN

PC-RGB

AUDIO IN

CABLE AIR

RF IN

Y

b

7

P

YPbPrIN

r

P

LEFT

8

AV IN

VIDEO RIGHT

HDMI4

3

HDMIIN

HDMI3

9

2

USB2

5V 500mA

S/PDIF

10

Page 40

Remote Control Descriptions

13

1

POWER

MUTE

ZOOM

FAV EPG

3

S.M

5

7

8

10

12

FREEZE

2

SLEEP

REC

P.P

HOME

CH.LIST

4

6

9

11

T.S HIF T

1. Standby( )

Press to turn the TV on or off(standby).

2. Freeze

Press to freeze or unfreeze the picture.

Note: This button is in USB channel.useless

3. Mute

Press to mute or restore the volume.

4. Picture Mode( P.P )

Press to select the desired picture

mode.

INFO

EXIT

SUBTITLE

CC

INDEX

AUDIO

MTS

RETURN

5. Sound Mode( S.M )

Press to select the desired sound mode.

6. Sleep

Press to set the time to switch the TV to

standby mode.

OK

7. Zoom

Press to select the desired picture aspect ratio.

8. Home

MENU

VOL

SOURCE

12

4

5

7

89

.

0

CH

3

6

Enter the home .desktop

9. Record(REC)

Press to record the current DTV program.

10. EPG

Press to display the EPG information in DTV

program.

11. Channel List(CH LIST)

Press to display the available channel list.

12. Favorite Channel(FAV)

Press to view your assigned favorite channels.

Press Up/Down buttons to cycle through your

assigned favorite channels, press OK to confirm.

13.Color buttons

Press to execute the prompt function.

Page 41

14

15

17

19

FREEZE

POWER

P.P

SLEEP

HOME

CH.LIST

REC

T.S HIF T

INDEX

SUBTITLE

CC

EXIT

OK

MENU

VOL

SOURCE

12

4

5

7

89

.

0

Remote Control Descriptions

14. ButtonsControl

MUTE

S.M

ZOOM

FAV EP G

INFO

AUDIO

MTS

CH

3

6

RETURN

16

18

20

Fast Backward ( )

Press to fast reverse.

Fast Forward ( )

Press to fast forward.

Previous ( )

Press to play the previous file.

Next ( )

Press to play the next file.

Play & Pause ( )

Press to pause playback,

press again to continue playback.

Stop ( )

Press to stop the playing.

15. Index

Press to view the PVR files list in AIR source.

16. INFO

Press to display relevant information such as

screen format, source, etc.

17. Closed Caption(CC)

Press to turn switch the mode of Closed Caption.

Subtitle

Press to open or close the video subtitle in

USB status.

18. MTS

Press to select desired sound output(Mono,

Stereo or SAP)depending on the broadcasting

channel.

AUDIO

Switch audio channel if there is a multichannel

program.

19. Exit

Press to exit from any menu.

20. Return

Return to previous menu in Ginga mode.

Page 42

Remote Control Descriptions

POWER

HOME

OK

MENU

SOURCE

5

0

MUTE

S.M

ZOOM

FAV EP G

INFO

AUDIO

MTS

CH

3

6

21

RETURN

23

26

25

27

FREEZE

P.P

SLEEP

CH.LIST

REC

T.S HIF T

INDEX

SUBTITLE

CC

EXIT

22

24

VOL

12

28

4

789

29 30

.

21. NETFLIX

Connect to Netflix.

22. Up/Down/Left/Right Cursor

( / / / )

Press to the desired item

select and adjust

on the menu.

Note: In USB mode, press " " can show

the control menu, press " " can hide the

control menu.

23. OK

Press to confirm and execute the selection.

24. Volume Up/Down (VOL+/-)

Press to adjust the volume.

25. Channel

Press to select channel.

Up/Down (CH+/- )

Next/Previous

26. Menu

Press to enter or exit from the TV menu.

27. Source

Press to select the input source mode.

Note:It is no work in the net application or USB.

28. Program Select (0-9)

Press to select the TV channel directly.

29.

Press to select the digital sub program.

30.

Press to review the last program.

Page 43

Welcome setting & Home

Initial setup

The first time you power on the TV, there will show a setup wizard, please follow the wizard:

Step 1.Select the language you need.

Step 2.Select the time zone of you place. (Note 1)

Step 3.Select the picture mode you like.

Step 4.Select the tuner mode. Press "OK" to scan the program.

Home

Presses "HOME" enter the home menu. There are some shortcuts in the desktop:

SETTING - Change the TV setting, including:

Advanced Option:

Menu Language - Change the menu language

Time Zone - Change the time zone of you place. (Note 1)

DivX Registration - Register TV set to play DivX video. (Note 1)

DivX Deactivation - Deactivate DivX. (Note 1)

Netflix Registration - Register Netflix. (Note 1)

Netflix Deactivation - Deactivate Netflix. (Note 1)

Network Setting: Change the setting of wire and wireless net.

Info: Show the information about the TV set.

SOURCE - Open the source list, select and switch the TV source.

DLNA - Begin the Digital Living Network Alliance application. (Note 1)

VIDEO - Enter the USB state, play the video file.

MUSIC - Enter the USB state, play the music file.

PHOTO - Enter the USB state, view the photo file.

FILE - Enter the USB state, view the text file.

Netflix - Begin the Netflix application, connect to Netflix. (Note 1)

Facebook - Begin the Facebook application, connect to Facebook. (Note 1)

Picasa - Begin the Picasa application, connect to Picasa. (Note 1)

Youtube - Begin the Youtube application, connect to Youtube. (Note 1)

Terratv - Begin the Terratv application, connect to Terratv.(Note 1)

Twitter - Begin the Twitter application, connect to Twitter.(Note 1)

Web Browser - Open the web browser.

(Note 2)

Note 1, Option item, no visibility to some TV set.

Note 2, Web Browser only supports the HTML5 video file format.

Netflix

Facebook

AIR

SETTING SOURCE DLNA VIDEO MUSIC PHOTO FILE

Youtu be Terratv

WebBr owser

Picasa

Twitter

Page 44

Welcome setting & Home

Network setting

Wi-Fi Network

Plug a Wi-Fi dongle to the USB socket.

Press "HOME" key enters the home page.

Select SETTING item, press "OK"key to open the SETTING page.

Select "Network Setting" item, press "OK" key to open the page.

Press " " key to select "Wi-Fi Network" item.

Press " " key to select "Wi-Fi Switch" item.

Press " " key to select on, press "OK" to confirm setting.

Press "MENU" exits "Wi-Fi Switch" item.

Press " " key to select "Station" item.

Press " " key to select your base station, press "OK" to enter connection page.

If the base station need password, select "Password" item, press "OK" to input the

password.

Press blue color key to connect the base station.

Notes:

Please use the Wi-Fi dongle which is equipped with the TV set. No all Wi-Fi dongle is

supported.

Not guarantee that all can use the keyboard and mouse more varieties.

Wired Network

Plug the network wire to the LAN socket.

Press "HOME" enters the home page.

Press " " key to select SETTING item then press "OK" to open the SETTING page.

Press " " key to select "Network Setting", press "OK" to open the page.

Press " " key to select "Configuration" item, press " " enters into the page.

Select "Connect" item, press "OK" to test the status.

Page 45

PVR & Time Shift

PVR

Press "REC" key to record.

Press [ ] key to exit record.

Press [ ] key to play or pause the recording program.

Press [ ] / [ ] key to display or hide the control menu.

Press button to Press button

[INDEX] display the list of recorded programs. OK to play.

Press red button to note

can jump directly to the end of the segment play.

Press button to

green show or hide the camera picture. select any pictures, you can play

the beginning of the period of time in the picture. OK to play as a starting

point in this picture when elected in the picture.

Press button to

yellow remove the camera pictures.

Press button to

blue take the current screen.

Pre ss [ ] / [ ]

button to fast rewind or fast forward when the cursor to above the playback

progress bar.

Notes:

PVR only works with the digital signal program.

Before you recording, please make sure that the USB disk has enough free memory.

Please use a high speed USB device.

The file can be played in the AIR or USB source, can't be played in other player,

including PC.

This TV can only support the FAT16, FAT32 format USB device.

The recorded files can only be played in this TV, does not ensure normal playback in

other TV.

the initial segment and end segment, when the replay, you

Press button

T-SHIFT

00:00 03:38

80

Time Shift

Press "T.SHIFT" key to begin time shift.

Press [ ] key to exit time shift.

Press [ ] key to play or pause the time shift.

Press [ ] / [ ] key to display or hide the control menu.

Notes:

Time shift only works with the digital signal program.

Before you start time shift, please make sure that the USB disk has enough free

memory.

Please use a high speed USB device.

Page 46

MENU setting

Menu Operation

Press "MENU" key to enter the main menu .

Press the[ ] / [ ] guide key to select desired item.

Press "OK" key to enter the item.

Press "MENU" key to exit the item.

Picture

Picture Mode Cine ma

Color Temperature

Picture Size

Noise Reduction

MPEG Noise Reduction

Dynamic Contrast

Film Mode

PICTURE

Picture Mode: Contain "Natural", "Cinema", "Favorite", "Game" and "Dynamic".

("Game" mode is no useful at the AIR, CABLE and USB source.)

Color Temperature: Contain "Normal", "Warm", "Favorite" and "Cool".

Picture Size: Contain "Auto", "4:3", "16:9", "ZOOM1", "ZOOM2", "Panoramic" and

"Just Scan". (Some option is no visible at some source.)

Noise Reduction: Contain "Off", "Low", "Middle" and "High" four modes .

(No useful at PC-RGB source)

MPEG Noise Reduction: it contain "Off", "Low", "Middle", "High".

(No useful at PC-RGB source)

Dynamic Contrast: Contain On and Off. (No useful at PC-RGB source.)

Film Mode: Contain On and Off. (No useful at PC-RGB source.)

RGB Mode Setup: Contain the follow option.

Auto Adjust: Adjust the screen automatically.

H Position: Adjust the horizontal position.

V Position: Adjust the vertical position.

Clock Phase: Adjust phase.

H Clock: Adjust the synchronous clock.

Page 47

MENU setting

Audio

Sound Mode Standard

Balance

surround sound

PerfectVolume

DigitalAudio Output

Audio Delay

AUDIO

Sound Mode: Contain "Standard", "Music", "Movie", "Speech" and "Favorite".

Balance: Control the sound balance between the right and left loudspeaker (earphone).

Surround Sound: Contain On and Off.

Perfect Volume: Contain On and Off. Adjust the volume corresponding to the input

audio level.

Digital Audio Output: Contain AUTO and PCM

Audio Delay: Adjust the speaker delay time to synchronize with video

(Only Useful at DTV source).

Time

Auto Sync Off

00:00

Clock

Power Off Time

Power On Time

Sleep Timer

Auto Sleep

TIME

Auto Sync: Can set TV time synchronize with the system or not. It is working when

you receive DTV signal.

Clock: Set the time of TV set by manually when the "Auto sync" is set to "Off".

Power Off Time: Set the time of TV set auto standby.

Power On Time: Set the time of TV set auto power on.

Sleep Timer: Contain off, 10, 20,30,60,90,120,180,240 minutes.

Auto Sleep: TV set auto to standby when there is no signal. Contain On and Off.

Page 48

MENU setting

Setup

Auto Tnuing

DTV ManualTuning

TV ManualTuning

ChannelEdit

Signal Information

SETUP

Auto Tuning: Search and save all programs at current source by automatically.

DTV Manual Tuning: Search and save the digital programs at AIR source by manually.

TV Manual Tuning: Search and save the analog programs at current source by manually.

Channel Edit: Edit the programs. You can skip the programs or add the programs in the

favorite list.

Signal Information: Showing the information of current DTV channel.

Function

Audio Language English

Subtitle

PVR File System

Closed Caption

HDMICEC

DTVisetup

Restore Factory Default

FUNCTION

Audio Language: Set the primary or secondary digital audio language corresponding

to the signal.

Subtitle: Contain On and Off.

PVR File System: Personal Video Record setting. If you want to use this function, you

must receive a digital program and plug a USB disk.

Closed Caption: Analog closed caption, contain CC1, CC2, CC3, CC4, TT1, TT2, TT3

and TT4.

HDMI CEC: HDMI linking setting.

DTVi Setup: Ginga switch, contain On and Off.

Restore Factory Default: Restore user setting to the default.

Page 49

MENU setting

Lock

Lock System Off

SetPassword

Block Program

Parental Guidance

LOCK

Lock system: Switch the lock system between On and Off.

Set Password: Reset the password.

Block Program: Set the blocked programmers you desired.

Parental Guidance: Set the parental controlling level.

Page 50

USB Control

Gentle Reminder When Using The USB Player

1.Some USB storage devices may not be compatible to operate smoothly with this TV.

2.Back up all of the data in the USB storage device in case if data was lost due to unexpected

accident. We do not assume any liability for the losses by misuse or malfunction. Data backup

is consumer's responsibility.

3.For large file sizes, the loading speed may be slightly longer.

4.The recognition speed of a USB storage device may depend on each device.

5.When connecting or disconnecting the USB storage device, ensure that the TV is not in USB

mode otherwise the USB storage device or the files stored in it may be damaged.

6.Please use only a USB storage device which is formatted in FAT16, FAT32, NTFS file system

provided with the Windows operating system. In case of a storage device formatted as a

different utility programme which is not supported by Windows, it may not be recognized.

7.When using a USB Hard Disk Drive which requires electric power source, ensure its power

does not exceed 500mA. If the power of the USB hard Disk exceed 500mA, the TV system will

the changed to standby mode, It must pull away the USB hand Disk and restart the TV system.

8.An "Unsupported File" message will be displayed if the file format is unsupported or corrupted.

Note:

In situation whereby the insertion of USB storage device is restricted, you may use the

USB extension cable provided. Media Input should not exceed by 7(H) x 18(W)mm.

Page 51

USB File Playback Support

USB Control

Video

File Extension

dat, mpg, mpeg MPG, MPEG Mpeg1,2 1080P @ 20Mbit/sec Main Profile

ts, trp, tp, m2ts

vob

mp4

mkv MKV

Container Video Codec SPEC

MPEG2,H.264,VC1,AVS

TS

MPEG2 -PS MPEG2

MPEG4

AVI, MP4

Divx 3.11, Divx 4.12, Divx 5.x,

Divx6, Xvid 1.00,

Xvid 1.01, Xvid 1.02, Xvid 1.03,

Xvid 1.10-beta1/2H.264

H.264,MPEG1,2,4

1080P @

30P

1080P @

1080P @

30P

1080P @

30P

Bit Rate Profile

H.264:Main Profile and High

20Mbit/sec

20Mbit/sec

20Mbit/sec

20Mbit/sec

Profile@Level 4.0

MPEG2: MP@HL

MPEG2: MP@HL

H.264:Main Profile and High

Profile@Level 4.0

MPEG4: Simple Profile and

Advanced Simple Profile @Level 5

H.264:Main Profile and High

Profile@Level 4.0

MPEG4: Simple Profile and

Advanced Simple Profile @Level 5

Music

Audio Codec

MPEG1 Layer1

MPEG1 Layer2

MPEG1 Layer3

File Extension Bit Rate

MP3

MP3

MP3

32Kbps ~ 448Kbps(Bit rate)

16KHz ~ 48KHz(Sampling rate)

8Kbps ~ 384Kbps(Bit rate)

16KHz ~ 48KHz(Sampling rate)

8Kbps ~ 320Kbps(Bit rate)

16KHz ~ 48KHz(Sampling rate)

Photo

Image

JPEG

PNG

BMP3

Photo

Base-line

Progressive

non-interlace

interlace

MP3

Resolution

(Mstar suggest)

15360x8640

1024x768

9600x6400

1200x800

9600x6400

Required

DRAM size

(Mbytes)

3.96

0.00

0.00

0.00

0.00

Document

Text file(*.txt), encode with English.

Page 52

USB Control

Play video

Press "HOME" enters the home page. Select

VIDEO item, press "OK" key to open the

desired content.

Press "OK" key to select the video file.

Press [ ] key to play or pause.

Press "EXIT" to exit playing or go back the

previous menu

Shortcut key:

Video Control Bar

Pause

Skip Previous

Fast Reverse

VIDEO

Return

Time Search

1/1

Display Mode

Stop

Repeat Play Mode

A-B Repeat

Skip Next

Zoom In

Zoom Out

Fast Forward

Move zoom picture

Current Information

- Press [ ] to display Video Control Bar while playing the video.

- Press [ ] / [ ] to select the desired settings.

- Press [ ] to exit from Video Control Bar.

- Press [ INFO ] Show the information of playing file.

Play List

Page 53

USB Control

Play music

Press "HOME" enters the home page. Select

MUSIC item, press "OK" key to open the

desired content.

Press "OK" key to select the music file.

Press [ ] key to play or pause.

Press "EXIT" to exit playing or go back the

previous menu

Music Control Bar

MUSIC

Return

TITLE: xxx

ALBUM: xxx

ARTIST: xx

YEAR:

SAMPLE FREQUENCY:44100

BIT RATE: 192

TOTAL TIME:233

1/1

Pause

Skip Previous

Stop

Fast Reverse

Skip Next

Repeat Play Mode

Fast Forward

Current Information

Play List

- Press [ ] to display Music Control Bar while playing the music.

- Press [ ] / [ ] to select the desired settings.

- Press [ ] to exit from music Control Bar.

- Press [ INFO ] Show the information of playing file.

Notes:

- This TV supports lyrics display (English).Maximum number of characters per line is 48.

- The filename of music and lyrics must be the same in order to display lyrics while the music is playing.

Page 54

USB Control

Browse photo

Press "HOME" enters the home page.

Select PHOTO item, press "OK" key to

open the desired content.

Press "OK" key to select the photo file.

Press [ ] key to play or pause.

Press "EXIT" to exit playing or go back the

previous menu

Photo Control Bar

PHOTO

Return

1/1

Pause

Skip Previous

Stop

Play List

Move zoom picture

Skip Next

Backdropmusic

Current Information

Rotate CW

Rotate CCW

Zoom In

- Press [ ] to display Photo Control Bar during photo slide show.

- Press [ ] / [ ] to select the desired settings.

- Press [ ] to exit from photo Control Bar.

- Press [ INFO ] Show the information of playing file.

Repeat Play Mode

Zoom Out

Page 55

USB Control

Read text

Press "HOME" enters the home page. Select

FILE item, press "OK" key to open the desired

content.

Press "OK" key to select the text file.

Press "EXIT" to exit reading or go back the

previous menu.

Press[ ] / [ ] Go to next page or pre page.

Text Control Bar

FILE

Return

Thanks for your purchase

of our digital high-definition

LED television!

1/1

Stop

Skip Next

Skip Previous

Fast Forward

Fast Reverse

Music

Jump to page

Current Information

Play List

- Press [ ] to display Text Control Bar while reading the file.

- Press [ ] / [ ] to select the desired settings.

- Press [ ] to exit from file Control Bar.

- Press [ INFO ] Show the information of playing file.

Note:

- It supports *.txt files.(English character)

- Please ensure that the text file is saved in an encoding standard. This may minimize the loss of characters

in a multiple-language content.

Page 56

Troubleshooting

NO PICTURE, NO SOUND

1. Check if the fuse or circuit breaker is working.

2. Plug another electrical device into the outlet to

make sure it is working or turned on.

3. Power plug is bad contact with the outlet.

4. Check the signal source.

NO COLOR

1. Change the color system.

2. Adjust the saturation.

3. Try another channel. Black-white program may

be received.

REMOTE CONTROL DOES NOT WORK

1. Change the batteries.

2. Batteries are not installed correctly.

3. Main power is not connected.

NO PICTURE, NORMAL SOUND

1. Adjust the brightness and contrast.

2. Broadcasting failure may happen.

NORMAL PICTURE, NO SOUND

1. Press the volume up button to increase volume.

2. Volume is set to mute, press MUTE to restore

sound.

3. Change the sound system.

4. Broadcasting failure may happen.

SNOWY DOTS AND INTERFERENCE

If the antenna is located in the fringe area of a

television signal where the signal is weak, the

picture may be marred by dots. When the signal

is extremely weak, it may be necessary to install

a special antenna to improve the reception.

1. Adjust the position and orientation of the

indoor/outdoor antenna.

2. Check the connection of antenna.

3. Fine tune the channel.

4. Try another channel. Broadcasting failure may

happen.

IGNITION

Black spots or horizontal streaks appear, or the

picture flutters or drifts. This is usually caused by

interference from car ignition system, neon lamps,

electric drills, or other electrical appliance.

GHOST

Ghosts are caused by the television signal

following two paths. One is the direct path, the

other is reflected from tall buildings, hills, or other

objects. Changing the direction or position of the

antenna may improve the reception.

RADIO FREQUENCY INTERFERENCE

This interference produces moving ripples or

diagonal streaks, and in some case, loss of

contrast in the picture. Find out and remove the

radio interference source.

UNORDERLY RIPPLES ON THE PICTURE

It is usually caused by local interference, such as

cars, daylight lamps and hair driers. Adjust the

antenna to minimize the interference.

BLANK SCREEN IN PC MODE

Perhaps the TV can not recognize the resolution set

by the PC. Suggest to change to the best resolution

or other standard resolutions of Windows system.

Set refresh rate to be 60Hz.

Page 57

Y

g

,

g

p

pp

y

b

p

pp

y

b

Q

pp

y

pp

y

Y

Check the

board

Check the 5V, 12V & 24V

N

Upgrade the

l

ower su

on

N

Y

software

Y

reen

led turns

YN

Press the “ON/OFF” on keyboard &

remote control

N

Change the

Done

“ON/OFF” voltage

on “CN7”, should

oard

power supply

be greater than 2.7V

Done

Change

the panel.

N

“U9” Pin"K4" if

it works well.

Check “Q39” &

Done

Y

Y

software

Upgrade the

N

39” or “U9”

Change the

“

Done

N

Change the “U9”

Y

N

Done

Upgrade the

Done

software

Done

ht

No audio & No backli

Led indicator “red” on

Y

Check the 5VSTB on “CN7”

N

Y

N

Upgrade the software

board

l

Done

Y

Y

N

Change the FLASH U8

Check the

supply board

fuse on power

Done

on U9

l

su

Check all DC power

Y

N

Done

Y

Change the

N

Y

N

Chang the power

Change the

power supply

Main IC “U9”

IC for U9

l

su

oard

N

Change the

Done

oard

Done

Main

Service Flow Chart

ower su

Check the AC input on

Change

Done

N

Change the

AC line

the fuse

Done Done

Page 58

Y

p

p

Done

Done

Has video but no audio

Check if the Volume has set to “0”

OK

Check the audio input line

ut circuit.

& the audio in

N

>0V

OK

Done

Check the voltage of “Mute” pin beside

lifier IC. It should not be 0V.

the am

=0V

Check the mute circuit

if it is OK.

Y

OK

Upgrade the software

N

IC “U9”

Change the main

or if theitismute

N

Service Flow Chart

N

N

Fix the mute circuit

Done

Change the mainboard Done

Done

Page 59

OK

r

y

gg

pp

y

Done

OK

YN

decreased to “0”

Has video but no colo

in picture menu if it has

Check the Color / Saturation

Increase the item

N

OK

to default “50”

Y

connected

Done

N

source if it is TV

OK

Done

uide.

Check the U18 circuit

Y

Adjust AGC

Y

follow the workin

N

OK

IC “U9”

of the tuner.

l

su

Check the DC power

N

Done

N

Check the U18 circuit

OK

Done

Fix the DC supply

N

Change the tuner

N

OK

Done

Change the U18

Done

OK

N

Done

N

Change the

mainboard

Service Flow Chart

Check the cable input if

it has exactl

N

Well connect the cable Check the current input

OK

Change the main

Done

Done

N

Change the

mainboard

Done

N

Change the mainboard

Page 60

OK

g

r

,

p

r

Done

Y

main IC U9

OK

N

N

Y

if it is connected

Check the LVDS line

N

Y

12V for 32”&42”

5V for 26”

Make sure the LVDS power is correct

N

N

OK

LVDS line

Safely connect the

Change the FLASH U8 U43

N

Correct the

Done

owe

Chane the

OK

Done

Done

Change the

oard

Done

main

Has audio but no video

Check if the backlight is on

N

Check the connector of

Y

ter connected

ht inve

ackli

N

Check the

“ON/OFF” voltage

on “CN7”, should

OK

be greater than 2.7V

Y

N

Done

Change

the panel.

Check “Q39” &

“U9” PinAB24 if

N

it works well.

N

Done

Y

Upgrade the

Change the

YY

software

N

39” or “U9”

“

N

Done

Change the “U9”

Done

Upgrade the

Done

software

Done

Service Flow Chart

Safely connect the

inverter line

N

OK

inverter line is 24V

Check the voltage of

Done

Page 61

V00.20

V00.20

V00.20

of

of

of

110Wednesday, May 09, 2012

110Wednesday, May 09, 2012

110Wednesday, May 09, 2012

1

DROP_DET 11

NC/1N4148D3NC/1N4148

LEDG 11

LEDG

D4

NC/1N4148D4NC/1N4148

D6

TL26 FB120RTL26 FB120R

Q3Q3

R2 NC/4.7KR2 NC/4.7K

12

NC/9V1D6NC/9V1

R83 NC/1KR83 NC/1K

+12V_ONLY

+5V_Normal+5V_Normal

TL27 FB120RTL27 FB120R

R11

NC/39K

R11

NC/39K

R13

NC/2.2K

R13

NC/2.2K

C5

C164

C164

NC/10nFC5NC/10nF

10uF

10uF

For AV interfere.

ࡴ⬉䎠㨑Ẕ⌟DŽ

C17

10uF

C17

+5V_Normal+5V

U2

4

LDO

R10

10K_1%

R10

10K_1%

Vout=0.8*(3.69K+10K)/10K=1.095V

C1

47nFC147nF

7

FB

SS

PGND

1

AGND

3

C25NCC25

NC

C2

2.2nFC22.2nF

U2

IN

IN

OUT

OUT

ADJ

ADJ

R34

R34

AMS1117-ADJ

AMS1117-ADJ

NC/200

NC/200

32

R61

NC/100K

R61

NC/100K

NC/0.1u

NC/0.1u

5

BST

NC/100K

NC/100K

CA16

7

R64 82KR64 82K

C84

C84

C13

C13

C83

C83

+

100uF/16V+CA16

100uF/16V

R650R65

0

C20

C20

0.1uF

0.1uF

C24

10uF/16V

C24

10uF/16V

Q6

20111216 by lin.

10uF

10uF

0.1uF

0.1uF

R76

R76

8

FB

GND4AAM1VCC

R55

10k

R55

10k

0.1uF

0.1uF

1

R70 0R70 0

Q53 NC/M2345Q53 NC/M2345

C21

C21

R52

R52

2

TP3TP3

+5V

R66

36K

R66

36K

L38 3.3uHL38 3.3uH

3

C19

1uF

C19

1uF

3

OUT

EN

IN

U59

MP1494

U59

MP1494

6

2

R7 10KR7 10K

DC/DC

+12V_ONLY

24V_AMP

NC/3904Q6NC/3904

2 3

1

R68 NC/0R68 NC/0

R72 NC/0R72 NC/0

R60 NC/10KR60 NC/10K

+5V +5V_Standby

STANDBYSTANDBY

+12V_ONLY

1.8A Max

+1.05V_VDDC

TP5TP5

6.8K

6.8K

L2 3.3uHL2 3.3uH

Vout=0.8*(36K+6.8K)/6.8K=5.02V

9

AOZ1051

AOZ1051

U50

U50

2

+12V_ONLY

FOR only 12V

VSENSE

R16 220ohm/NCR16 220ohm/NC

R6 3.3K_1%R6 3.3K_1%

OUT

EN

IN

6

8

R1 22KR1 22K

STANDBY

C156

10uF

C156

10uF

C4

0.1uFC40.1uF

+

CA1

100uF/16V+CA1

100uF/16V

C6

10uFC610uF

R9

390R9390

4

COMP5NC

R14

20K

R14

20K

C3

0.1uFC30.1uF

C15

10uF/16V

C15

10uF/16V

C155

10uF/16V

C155

10uF/16V

TP4TP4

350mA Max

+3.3V_Standby

3

2

1

720mA Max

+3.3V_Normal

TP6TP6

L8 3.3uHL8 3.3uH

3

SW

VIN

U5

SY8086U5SY8086

4

+5V_Normal

+

+

CA3

CA3

C9

C7

+

+

CA5

CA5

+5V_Standby

0/330

0/330

R33

R33

C154 10pFC154 10pF

R39 10kR39 10k

68K

68K

R24

R24

5

1

10uF

47uF/16V

47uF/16V

0.1uFC90.1uF

0.1uC70.1u

47uF/16V

47uF/16V

C93

C93

C27

C27

FB

EN

+

+

GND

CA4

CA4

C148

C148

C28

C28

+

+

CA8

CA8

10uF

10uF

0.1uF

0.1uF

100uF/16V

100uF/16V

R27

R27

2

15K

15K

20111216 by lin.

10uF

10uF

0.1uF

0.1uF

100uF/16V

100uF/16V

4

U3

U3

220mA Max

C10

2.2u

C10

2.2u

+2.5V_Normal

AMS1117-ADJ

AMS1117-ADJ

C8

0.1uC80.1u

3

IN

IN

2

OUT

OUT

1

ADJ

ADJ

R36

R36

Vout=0.6*(68K+15K)/15K=3.32V

C143

10uF

C143

10uF

+5V_Normal

330

330

R35

R35

330

330

TP7TP7

5V_USB

R45

36K

R45

36K

L9 3.3uHL9 3.3uH

C16

1uF

C16

1uF

3

OUT

EN

IN

U52

MP1494

U52

MP1494

6

2

R5 10KR5 10K

DC/DC

+12V_ONLY

STANDBY

+

+

CA11

100uF/16V

CA11

600mA Max

3

2

1

1k

+1.5V_DDR

+3.3V_Normal

C11

C11

C12

C12

C147

C147

R37

R37

100uF/16V

0.1uF

0.1uF

0.1u

0.1u

10u

10u

200

200

D3

R12 NC/11KR12 NC/11K

+5V_Standby DROP_DET

U4

U4

AMS1117-ADJ

AMS1117-ADJ

IN

IN

4

OUT

OUT

ADJ

ADJ

R381kR38

20111216 by lin.

CA23

100uF/16V+CA23

100uF/16V

+

C81

0.1uF

C81

0.1uF

C136

10uF

C136

10uF

R46

6.8K

R46

6.8K

R50

390

R50

390

8

5

FB

BST

7

R67 82KR67 82K

C22

C22

C82

C82

C135

C135

Vout=0.8*(36.39K+6.8K)/6.8K=5.08V

GND4AAM1VCC

R58

10k

R58

10k

0.1uF

0.1uF

0.1uF

0.1uF

10uF/16V

10uF/16V

POWER DROP DETECT

SYSTEM POWER

SYSTEM POWER

SYSTEM POWER

MSD6329SV

MSD6329SV

MSD6329SV

Custom

Custom

Custom

Title

Size Document Number Rev

Title

Size Document Number Rev

Title

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

1

2

3

4

+5V_Standby

R445

R445

4.7K

4.7K

1K

C179

C179

PB-ON/OFF

0.1u

0.1u

STANDBY

PB-ADJUST

R171KR17

1

Q40

Q40

MMBT3904

MMBT3904

+5V_Standby

+5V_Standby

R477 3.3KR477 3.3K

STANDBY

5

Power Input

12345678910111213

CN7

CN7

H:ON

L:OFF

2 3

+12V_ONLY

+12V_ONLY

+12V_ONLY

PWR-ON/OFF 2

R475 1KR475 1K

1

2 3

Q39

Q39

MMBT3904

MMBT3904

Note: Make sure the voltage

of STANDBY over 2.5V for all kind powers.

+

CA15

100uF/16V+CA15

100uF/16V

0.1u

0.1u

C132

C132

C18

10uF

C18

10uF

C125

0.1u

C125

0.1u

+5V_Standby

+24V

24V_AMP

+24V

R75 0/NCR75 0/NC

14

CON14_2.5

CON14_2.5

D D

R32

NC/10K

R32

NC/10K

PB-ON/OFF

1n

C3341nC334

R44 100RR44 100R

Q18

Q18

3904

3904

+5V_Normal

+3.3V_Normal

2 3

R20

10K

R20

10K

1

R40 1KR40 1K

R21

10K

R21

10K

L:ON

H:OFF

VBL_CTRL2

Inverter Interface

PB-ADJUST

100/10K

100/10K

R49

R49

R18 only for 3.3V PWM output

+5V_Normal

R48

10K

R48

10K

R126

NC/4.7K

R126

NC/4.7K

R163

NC/4.7K

R163

NC/4.7K

EXT_VBR2

PB-ADJUST

C335

C335

R18

R18

Q19

3904

Q19

3904

1

4.7K

4.7K

R47

R47

BRI_ADJ-PWM22

VCC-Panel

32

Q44 A03401Q44A03401

0.1u/NC

0.1u/NC

NC/20K

NC/20K

2 3

R74 NC/0R74 NC/0

R73 0/NCR73 0/NC

Note: Left C335 NC, R49 change to 100ohm if want to output PWM puls

+5V

+12V_ONLY

5

D18D17D26D2

S11S22S33G2

1

4

C14

0.1uF

C14

0.1uF

R51

R51

100K

100K

R480 100KR480 100K

PANEL POWER

C C

U6 STM9435/NCU6 STM9435/NC

Q7

1

R23 1KR23 1K

R22 10KR22 10K

+3.3V_Normal

3904Q73904

2 3

Q8

3904Q83904

2 3

1

R25 10KR25 10K

PANEL_ON/OFF

PANEL_ON/OFF2

B B

678

9

1

H11NCH11

234

5

NC

678

9

1

H10NCH10

H9NCH9

H8NCH8

NC

234

5

678

9

1

234

5

NC

678

9

1

234

5

NC

Test Point & MARK

4

H2NCH2

NC

1

H12NCH12

NC

1

H1NCH1

NC

1

H6NCH6

NC

1

H5NCH5

NC

1

H4NCH4

NC

1

H3NCH3

NC

1

A A

5

Page 62

V00.20

V00.20

V00.20

of

of

of

210Tuesday, May 22, 2012

210Tuesday, May 22, 2012

210Tuesday, May 22, 2012

MAIN IC

MAIN IC

MAIN IC

B-TMA[0:14] 3

1

B-TMA0

B-TMA1

B-TMA14

G23

T23

B-TMA2

R22

B-TMA3

M22

B-TMA4

B-TMDQL[0:7] 3

B-TMDQU[0:7] 3

B-TMCK 3

B-TMBA0 3

B-TMBA1 3

B-TMBA2 3

B-TMODT 3

B-TMDML 3

B-TMCKB 3

B-TMCKE 3

B-TMDMU 3

B-TMWEB 3

B-TMCASB 3

B-TMRASB 3

B-TMDQU0

B-TMDQU7

B-TMDQU2

B-TMDQU5

B-TMDQL2

B-TMDQL0

B-TMDQL7

B-TMDQL5

B-TMDQU4

B-TMDQU3

B-TMDQL3

B-TMDQL4

B-TMDQU1

B-TMDQU6

B-TMDQL6

B-TMDQL1

B-TMA5

B-TMA7

B-TMA12

B-TMA9

B-TMA6

B-TMA8

B-TMA11

B-TMA10

B-TMA13

J22

N23

J23

N22

H22

E24

K23

N25

E25

N24

P22

R23

L23

H23

B-TMCASB

B-TMRASB

R25

K25

F25

L24

M24

G25

L25

H24

G24

P25

T25

D25

P24

D24

B-TMWEB

B-TMDML

T24

F24

B-TMODT

B-TMDMU

M25

B-TMDQSL 3

B-TMDQSU 3

B-TMDQSLB 3

B-TMDQSUB 3

B-TMRESETB 3

B-TMBA2

B-TMCK

B-TMCKB

B-TMDQSUB

B-TMDQSU

B-TMCKE

B-TMBA0

B-TMDQSLB

B-TMDQSL

B-TMBA1

B-TMA14

B-TMRESETB

P23

J25

K24

R24

E23

H25

M23

T22

C26

K22

G22

J24

B26

MSD6329SV

MSD6329SV

MSD6329SV

Title

Size Document Number Rev

Title

Size Document Number Rev

Title

Size Document Number Rev

1

A1

A1

A1

Date: Sheet

Date: Sheet

Date: Sheet

B_DDR3_A1/DDR2_A6

B_DDR3_A3/DDR2_A3

B_DDR3_A0/DDR2_A13

B_DDR3_A2/DDR2_A14

A_DDR3_A0/DDR2_A13

A_DDR3_A1/DDR2_A6

A_DDR3_A2/DDR2_A14

A_DDR3_A3/DDR2_A3

U9A

U9A

B11

E17

D22

D21

A-TMA1

A-TMA3

A-TMA0

A-TMA2

A-TMA4

A-TMA14

2

A-TMA[0:14]3

TS_D[0:7] 7,9

TS_D1

TS_D2

TS_D0

TS_D4

TS_D3

AA9

AB10

AA10

TS1_D0

TS1_D1Y9TS1_D2

TS1_D3

3

U9B

U9B

PF_D[0]/ NAND_AD[0]/PCM_D[0]

PF_D[1]/ NAND_AD[1]/ PCM_D[1]

PF_D[2]/ NAND_AD[2]/ PCM_D[2]

PF_D[3]/ NAND_AD[3]/ PCM_D[3]

Y16

Y15

AA16

AA17

PCM_D2

PCM_D3

PCM_D4

PCM_D0

PCM_D1

PCM_D[7:0]7

4

AV1-Lin-IC

AV1-Rin-IC

HD_Rin-IC

HD_Lin-IC

T5

Y3

V3

T4

AA1

LINE_IN_0L

LINE_IN_1L

LINE_IN_2L

LINE_IN_0R

LINE_IN_1R

U9C

U9C

A_RX0N

A_RX0P

A_RX1N

A_RX1P

A_RX2N

AF17

AE16

AE17

AD16

AD17

HDMI1-RX1P

HDMI1-RX1N

HDMI1-RX0P

HDMI1-RX2P

HDMI1-RX0N

HDMI1-RX2N

5

HDMI1-SCL

HDMI1-SDA

HDMI_HP1

HDMI-CEC

HDMI-ARC

HDMI_HP14

HDMI-CEC4

HDMI-ARC4

HDMI1-SCL4

HDMI1-SDA4

HDMI Interface

B_DDR3_A4/DDR2_A0

B_DDR3_A5/DDR2_A7

B_DDR3_A6/DDR2_A2

B_DDR3_A7/DDR2_A5

B_DDR3_A8/DDR2_A4

B_DDR3_A9/DDR2_A12

B_DDR3_A13/DDR2_A9

B_DDR3_A11/DDR2_A11

B_DDR3_A10/DDR2_ODT

B_DDR3_A12/DDR2_CASZ

B_DDR3_DQL0/DDR2_DQL1

MIU0 MIU1

MIU0 MIU1

A_DDR3_A4/DDR2_A0

A_DDR3_A5/DDR2_A7

A_DDR3_A6/DDR2_A2

A_DDR3_A7/DDR2_A5

A_DDR3_A8/DDR2_A4

A_DDR3_A9/DDR2_A12

A_DDR3_A10/DDR2_ODT

A_DDR3_A11/DDR2_A11

A_DDR3_A12/DDR2_CASZ

A_DDR3_A13/DDR2_A9

A_DDR3_DQL0/DDR2_DQL1

E13

E18

E12

E19

B24

D18

D13

D14

D12

C12

D20

A-TMDQL0

A-TMA11

A-TMA12

A-TMA9

A-TMA5

A-TMA10

A-TMA7

A-TMA6

A-TMA8

A-TMA13

A-TMDQL[0:7]3

TS_VLD 7,9

TS_SYNC 7,9

TS_CLK 7,9

TS_VLD

TS_D6

TS_D7

TS_SYNC

TS_D5

TS_CLK

AB9

Y11

Y10

AC10

AA11