phyCORE-LPC3250

System on Module and Carrier Board

Hardware Manual

Document No:

Product No:

SOM PCB No:

CB PCB No:

Edition:

L-714e_1

PCM-040

1304.1

1305.2, 1305.3

January 27, 2009

A product of a PHYTEC Technology Holding Company

Table of Contents

L-714e_1

Table of Contents

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iii

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . v

Conventions, Abbreviations and Acronyms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .vi

Preface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .viii

Part I: PCM-040/phyCORE-LPC3250 System on Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2 View of the phyCORE-LPC3250 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3 Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.1 Primary System Power (VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.2 Secondary Battery Power (VBAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.3 Analog-to-Digital Converter Power (VCC_AD_EXT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.4 SDIO Controller Power (VCC_SDIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.5 On-board Voltage Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.5.1 Primary 1.2V and 1.8V Supplies (U23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.5.2 Adjustable Core Voltage Supply (U27) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.5.3 SDRAM and RTC Supplies (U22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.5.4 Selecting Shunt Resistors for Current Measurements. . . . . . . . . . . . . . . . . . . . . . 27

4.6 Voltage Supervisor (U16, U17) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5 Deep Sleep . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

6 External RTC (U26). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7 External Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

8 System Configuration and Booting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

8.1 Boot Process and Boot Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

8.1 Stage 1 Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

9 System Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

9.1 SDRAM (U10, U11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

9.2 NAND Flash (U8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

9.3 NOR Flash (U12, U13) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.4 NOR vs. NAND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.5 EEPROM (U9) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.6 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

10 Serial Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

10.1 RS-232 Transceiver (U25). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

10.2 Ethernet PHY (U6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

10.2.1 Configuring the PHY Operating Mode (J7, J8, J9) . . . . . . . . . . . . . . . . . . . . . . . 44

10.3 USB OTG Transceiver (U24). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

11 SDIO Controller (U14). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

12 Debug Interface (X1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

13 Bus Buffers (U1, U2, U3, U4, U5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

13.1 Buffered Memory Bus Voltage Select (J21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

14 Technical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

15 Hints for Handling the phyCORE-LPC3250 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

16 Component Placement Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

© PHYTEC America LLC 2009

i

Table of Contents

L-714e_1

Part II: PCM-967/phyCORE-LPC3250 Carrier Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

17 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

18 Overview of Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

19 Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

20 phyCORE-LPC3250 SOM Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

21 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

21.1 Wall Adapter Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

21.2 Power over Ethernet (PoE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

21.3 Lithium-Ion Battery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

21.3.1 Battery Charging Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

21.4 3.15V Supply (U9) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

21.5 1.8V Supply (U10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

21.6 5.0V Buck-Boost Supply (U21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

21.7 Power Path Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

21.8 Current Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

22 JTAG Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

23 Deep Sleep Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

23.1 3.0V Deep Sleep Supply (U11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

24 Audio Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

25 Ethernet Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

26 USB Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

27 LCD Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

28 GPIO Expansion Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

29 RS-232 Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

30 SD/MMC Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

31 SDIO Connectivity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

32 Keyboard Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

33 User Buttons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

34 User LEDs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

35 User ADC Potentiometer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

36 Boot Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

37 System Reset Button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

38 Watchdog Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Part III: PCM-988/GPIO Expansion Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

39 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

40 System Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

41 Memory Bus Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

42 LCD Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

43 UART Signal Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

44 I²C Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

45 GPIO Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

46 USB Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

47 SSP Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

48 I²S Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

49 Power Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

© PHYTEC America LLC 2009

ii

List of Tables

L-714e_1

List of Tables

Conventions, Abbreviations and Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .vi

Table 1-1. Abbreviations and Acronyms used in this Manual. . . . . . . . . . . . . . . . . . . . . . . . . . . . . vi

Part I: PCM-040/phyCORE-LPC3250 System on Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2-1. Pin Descriptions, phyCORE-Connector X2, Row A . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 2-4. Pin Descriptions, phyCORE-Connector X2, Row D . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 3-1. Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 4-1. U23 1.2V/1.8V Primary Voltage Regulator Jumper Settings. . . . . . . . . . . . . . . . . . . . 26

Table 4-2. U22 RTC/SDRAM Voltage Regulator Jumper Settings. . . . . . . . . . . . . . . . . . . . . . . . 27

Table 4-3. Primary System Supervisor Reset Thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 4-4. Sleep System Supervisor Reset Thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 9-1. Valid SDRAM Memory Address Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 9-2. NAND Flash Write Protection via Jumper J5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 9-3. Valid NOR Flash Memory Address Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 9-4. EEPROM Configuration Struct dramcfg Field Format . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 9-5. EEPROM Configuration Struct syscfg Field Format . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 9-6. phyCORE-LPC3250 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 10-1. UART 1/UART 5 TTL and RS-232 Level Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 10-2. Ethernet PHY Operating Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 10-3. Applicable USB Operating Mode Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 11-1. SDIO Controller to LPC3250 Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 11-2. SDIO Controller Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 13-1. Buffered Memory Bus Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 13-2. Buffered Memory Bus Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 14-1. Technical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 14-2. Static Operating Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Part II: PCM-967/phyCORE-LPC3250 Carrier Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 18-1. Connectors and Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 18-2. Description of the Buttons and Switches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 18-3. Description of LEDs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 18-4. Description of Potentiometers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 19-1. Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 21-1. Possible Ethernet PSE Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 22-1. LPC3250 JTAG Connector X12 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 22-2. Compatible JTAG Probes for the phyCORE-LPC3250 Carrier Board . . . . . . . . . . . 73

Table 27-1. LPC3250 LCD Port to Buffered CPLD Signal Mapping. . . . . . . . . . . . . . . . . . . . . . . 89

Table 27-2. LCD Mode Jumper Summary (JP48, JP49, JP50) . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 29-1. Connector P1A (UART5) Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 29-2. Connector P1B (UART3 and UART2) Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . 93

Table 29-3. UART3/UART2 Header Connector X13 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . 94

Table 29-4. Configuring DB-9 Connector P1B for UART3 or UART2 Operation . . . . . . . . . . . . . 95

Table 31-1. SDIO Easy Access Header Connector X23 Signal Descriptions . . . . . . . . . . . . . . 100

Table 32-1. Dip Switch S5 Positions and Associated Signals . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 32-2. Dip Switch S6 Positions and Associated Signals . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 32-3. Ethernet/Keyboard Easy Access Header Connector X11 Signal Descriptions . . . . 103

Part III: PCM-988/GPIO Expansion Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 39-1. Signals Removed from the GPIO Expansion Connector. . . . . . . . . . . . . . . . . . . . . 115

© PHYTEC America LLC 2009

iii

List of Tables

L-714e_1

Table 40-1. System Signal Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 41-1. Memory Bus Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 42-1. LCD Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 43-1. UART Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 44-1. I²C Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 45-1. GPIO Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 46-1. USB Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 47-1. SSP Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 48-1. I²S Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Table 49-1. Power Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Table 50-1. Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

© PHYTEC America LLC 2009

iv

List of Figures

L-714e_1

List of Figures

Part I: PCM-040/phyCORE-LPC3250 System on Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Fig. 1-1. phyCORE-LPC3250 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Fig. 1-2. Top View of the phyCORE-LPC3250 (Controller Side) . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Fig. 1-3. Bottom View of the phyCORE-LPC3250 (Connector Side) . . . . . . . . . . . . . . . . . . . . . . . 6

Fig. 2-1. Pin-out of the phyCORE-Connector (Top View, with Cross Section Insert) . . . . . . . . . . . 8

Fig. 3-1. Jumper Locations (Controller Side) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Fig. 3-2. Jumper Locations (Connector Side). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Fig. 3-3. Default Jumper Settings (Controller Side) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Fig. 3-4. Default Jumper Settings (Connector Side). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Fig. 4-1. phyCORE-LPC3250 On-board Powering Scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Fig. 5-1. Typical phyCORE-LPC3250 Sleep Enabled Powering Scheme . . . . . . . . . . . . . . . . . . 30

Fig. 8-1. Small Page SLC NAND Flash Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Fig. 10-1. Ethernet PHY Disconnection Resistors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Fig. 12-1. JTAG Interface X1 (Controller Side). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Fig. 14-1. phyCORE-LPC3250 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Fig. 16-1. phyCORE-LPC3250 Component Placement (Controller Side) . . . . . . . . . . . . . . . . . . 55

Fig. 16-2. phyCORE-LPC3250 Component Placement (Connector Side) . . . . . . . . . . . . . . . . . . 56

Part II: PCM-967/phyCORE-LPC3250 Carrier Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Fig. 17-1. phyCORE-LPC3250 Carrier Board Overview of Connectors and Interfaces . . . . . . . . 58

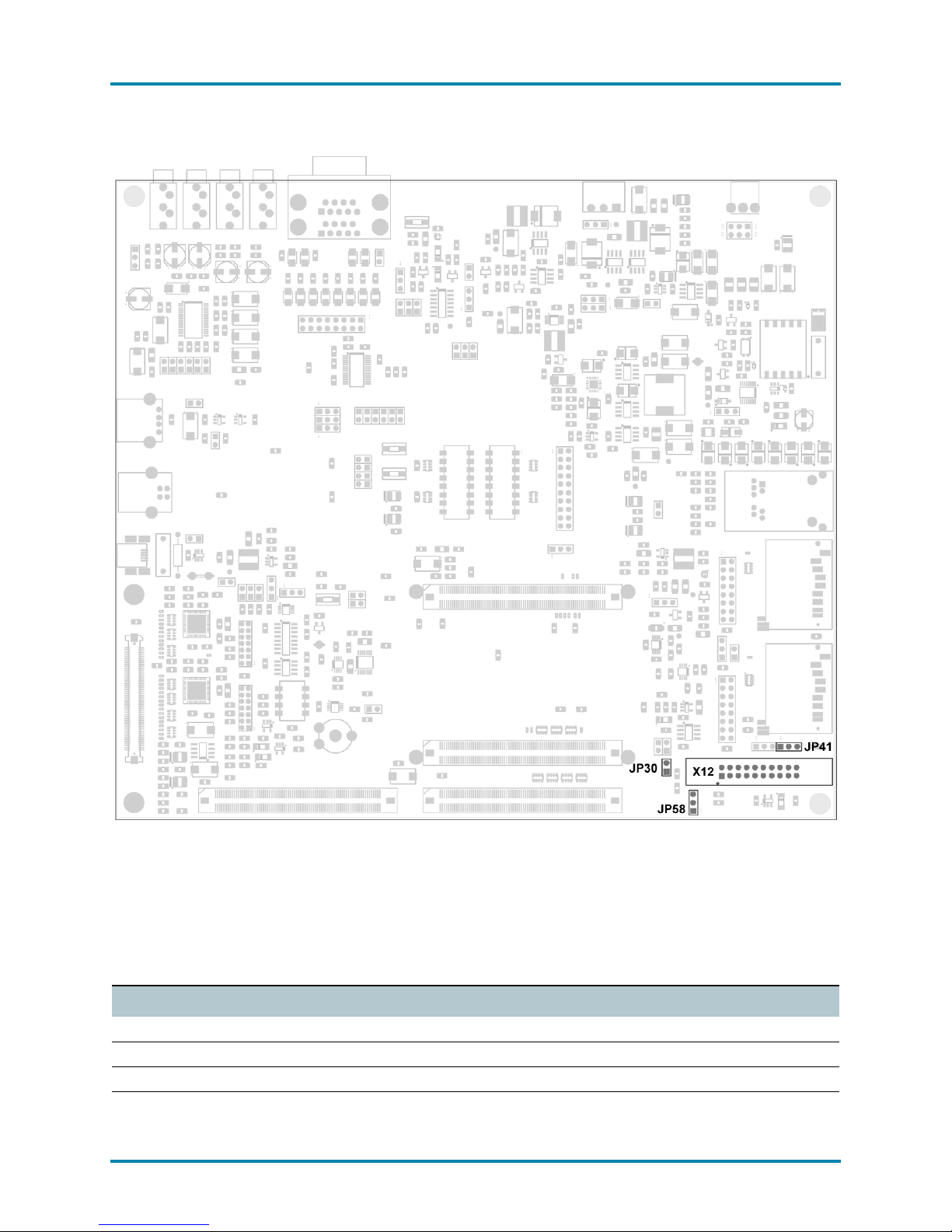

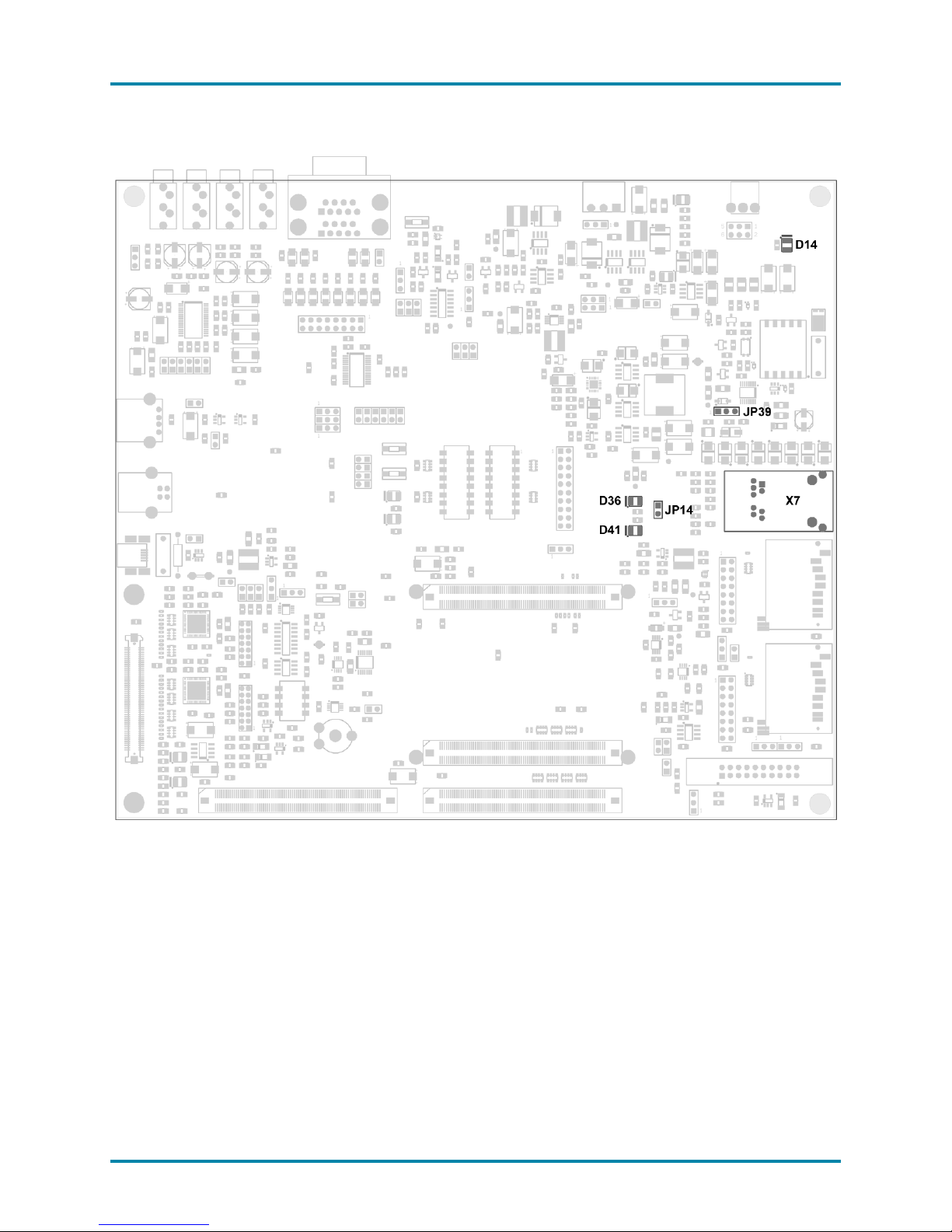

Fig. 19-1. Jumper Locations and Default Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Fig. 19-2. Typical Jumper Pad Numbering Scheme (Removable Jumpers) . . . . . . . . . . . . . . . . 62

Fig. 20-1. phyCORE-LPC3250 SOM Connectivity to the Carrier Board. . . . . . . . . . . . . . . . . . . . 65

Fig. 21-1. Powering Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Fig. 21-2. Powering Scheme Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Fig. 22-1. JTAG Probe Connectivity to the LPC3250 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Fig. 23-1. Deep Sleep Jumpers and Power Button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Fig. 23-2. Deep Sleep Circuit Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Fig. 23-3. Deep Sleep State Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Fig. 24-1. Audio Interface Connectors and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Fig. 25-1. Ethernet Interface Connectors and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Fig. 26-1. USB Interface Connectors and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Fig. 27-1. LCD Interface Connectors and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Fig. 27-2. LCD BLUE Signal Mapping in 24-bit Mode with a 24-Bit LCD . . . . . . . . . . . . . . . . . . . 87

Fig. 27-3. LCD BLUE Signal Mapping in 16-bit Mode with an 18-Bit LCD . . . . . . . . . . . . . . . . . . 87

Fig. 28-1. GPIO Expansion Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Fig. 29-1. RS-232 Interface Connectors and Jumpers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Fig. 29-2. DB-9 RS-232 Connectors P1A and P1B Pin Numbering . . . . . . . . . . . . . . . . . . . . . . . 93

Fig. 29-3. UART3/UART2 Header Connector X13 Pin Numbering . . . . . . . . . . . . . . . . . . . . . . . 94

Fig. 30-1. SD/MMC Interface Connectors and Jumpers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Fig. 31-1. SDIO Interface Connectors and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Fig. 32-1. Keyboard Interface Connector and Dip Switches. . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Fig. 33-1. User Buttons and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Fig. 34-1. User LEDs and Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Fig. 35-1. User ADC Potentiometer and Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Fig. 36-1. Boot Mode Selection Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Fig. 37-1. System Reset Button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Fig. 38-1. Watchdog Enable Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Part III: PCM-988/GPIO Expansion Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Fig. 39-1. PCM-988/GPIO Expansion Board and Patch Field . . . . . . . . . . . . . . . . . . . . . . . . . . 114

© PHYTEC America LLC 2009

v

Conventions, Abbreviations and Acronyms

L-714e_1

Conventions, Abbreviations and Acronyms

Conventions

The conventions used in this manual are as follows:

• Signals that are preceded by a “/” character are designated as active low signals. That is, their

active state is when they are driven low, or are driving low; e.g., /RESET.

• Tables which describe jumper settings show the default position in bold, teal text.

•Text in blue indicates a hyperlink within, or external to the document. Click these links to quickly

jump to the applicable URL, part, chapter, table, or figure.

• References made to the phyCORE-Connector always refer to the high density molex connectors

on the underside of the phyCORE-LPC3250 System on Module.

Abbreviations and Acronyms

Many acronyms and abbreviations are used throughout this manual. Use the table below to navigate

unfamiliar terms used in this document.

Table 1-1. Abbreviations and Acronyms used in this Manual

Abbreviation Definition

GPIO General purpose input and output.

GPI General purpose input.

GPO General purpose output.

BTN1 User button 1; used in reference to one of the two available user buttons on the Carrier

Board.

BTN2 User button 2; used in reference to one of the two available user buttons on the Carrier

Board.

CB Carrier Board; used in reference to the PCM-967/phyCORE-LPC3250 Carrier Board.

DFF D flip-flop.

EMB External memory bus.

EMI Electromagnetic Interference.

GPIOEBPF GPIO Expansion Board Patch Field; used in reference with the PCM-988/GPIO Expan-

sion Board and its associated patch field.

IRAM Internal RAM; the internal static RAM on the LPC3250 processor.

J Solder jumper; these types of jumpers require solder equipment to remove and place.

JP Solderless jumper; these types of jumpers can be removed and placed by hand with no

special tools.

KS Kickstart; the second level bootloader flashed on the phyCORE-LPC3250 SOM.

PCB Printed circuit board.

PoE Power-over-Ethernet.

POT Potentiometer.

PSE Power sourcing equipment; the device in a PoE network that provides power to con-

nected devices--usually a switch, router, or stand alone power injector.

RTC Real-time clock.

S1L Stage 1 Loader; the third level bootloader flashed on the phyCORE-LPC3250 SOM.

SMT Surface mount technology.

© PHYTEC America LLC 2009

vi

Conventions, Abbreviations and Acronyms

L-714e_1

Table 1-1. Abbreviations and Acronyms used in this Manual (Continued)

Abbreviation Definition

SOM System on Module; used in reference to the PCM-040/phyCORE-LPC3250 System on

Module.

VBAT SOM battery supply input

VFP Vector floating point.

© PHYTEC America LLC 2009

vii

L-714e_1

Preface

This phyCORE-ARM9/LPC3250 Hardware Manual describes the single board computer's design and

functions. Precise specifications for the NXP Semiconductors LPC3250 processor can be found in the

enclosed processor Data Sheet/User's Manual. If software is included please also refer to additional

documentation for this software.

In this hardware manual and in the attached schematics, low active signals are denoted by a "/" preceding

the signal name (i.e.: /RD). A "0" indicates a logic-zero or low-level signal, while a "1" represents a logicone or high-level signal.

Declaration of Electro Magnetic Conformity of the PHYTEC

phyCORE-LPC3250

PHYTEC System on Modules (SOMs) are designed for installation in electrical appliances or, combined

with the PHYTEC Carrier Board, can be used as dedicated Evaluation Boards (i.e.: for use as a test and

prototype platform for hardware/software development) in laboratory environments.

CAUTION:

PHYTEC products lacking protective enclosures are subject to damage by ESD and, hence, may only be

unpacked, handled or operated in environments in which sufficient precautionary measures have been

taken in respect to ESD-dangers. It is also necessary that only appropriately trained personnel (such as

electricians, technicians and engineers) handle and/or operate these products. Moreover, PHYTEC

products should not be operated without protection circuitry if connections to the product's pin header

rows are longer than 3 m.

PHYTEC products fulfill the norms of the European Union's Directive for Electro Magnetic Conformity only

in accordance to the descriptions and rules of usage indicated in this hardware manual (particularly in

respect to the pin header row connectors, power connector and serial interface to a host-PC).

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of

PHYTEC products, is subject to renewed establishment of conformity to, and certification of, Electro

Magnetic Directives. Users should ensure conformance following any modifications to the products as

well as implementation of the products into target systems.

The phyCORE-LPC3250 is one of a series of PHYTEC System on Modules that can be populated with

different controllers and, hence, offers various functions and configurations. PHYTEC supports a variety of

8-/16- and 32-bit controllers in two ways:

1. As the basis for Rapid Development Kits which serve as a reference and evaluation platform.

2. As insert-ready, fully functional phyCORE OEM modules, which can be embedded directly into the

user's peripheral hardware, design.

Implementation of an OEM-able SOM subassembly as the "core" of your embedded design allows you to

focus on hardware peripherals and firmware without expending resources to "re-invent" microcontroller

circuitry. Furthermore, much of the value of the phyCORE module lies in its layout and test.

Production-ready Board Support Packages (BSPs) and Design Services for our hardware further reduce

development time and expenses. Take advantage of PHYTEC products to shorten time-to-market, reduce

development costs, and avoid substantial design issues and risks. For more information go to:

http://www.phytec.com/services/phytec-advantage.html

© PHYTEC America LLC 2009 viii

PCM-040/phyCORE-LPC3250 System on Module

L-714e_1

Part I: PCM-040/phyCORE-LPC3250 System on

Module

Part 1 of this 3 part manual provides detailed information on the phyCORE-ARM9/LPC3250 System on

Module (SOM) designed for custom integration into customer applications.

The information in the following chapters is applicable to the 1304.1 PCB revision of the phyCORELPC3250 SOM.

© PHYTEC America LLC 2009

1

Part I, Chapter 1: Introduction

L-714e_1

1 Introduction

The phyCORE-LPC3250 belongs to PHYTEC’s phyCORE System on Module (SOM) family. The

phyCORE SOMs represent the continuous development of PHYTEC SOM technology. Like its mini-,

micro- and nanoMODUL predecessors, the phyCORE boards integrate all core elements of a

microcontroller system on a subminiature board and are designed in a manner that ensures their easy

expansion and embedding in peripheral hardware developments.

As independent research indicates that approximately 70% of all EMI (Electro Magnetic Interference)

problems stem from insufficient supply voltage grounding of electronic components in high frequency

environments, the phyCORE board design features an increased pin package. The increased pin package

allows dedication of approximately 20% of all connector pins on the phyCORE boards to ground. This

improves EMI and EMC characteristics and makes it easier to design complex applications meeting EMI

and EMC guidelines using phyCORE boards even in high noise environments.

phyCORE boards achieve their small size through modern SMD technology and multi-layer design. In

accordance with the complexity of the module, 0402-packaged SMD components and laser-drilled

Microvias are used on the boards, providing phyCORE users with access to this cutting edge

miniaturization technology for integration into their own design.

The phyCORE-LPC3250 is a sub-miniature (70 x 58 mm) insert-ready SOM populated with the NXP

LPC3250 ARM926EJ-S core processor. Its universal design enables its insertion in a wide range of

embedded applications. All processor signals and ports extend from the processor to high-density pitch

(0.635 mm) connectors aligning two sides of the board, allowing it to be plugged like a "big chip" into a

target application.

Precise specifications for the processor populating the board can be found in the applicable processor

User’s Manual or datasheet. The descriptions in this manual are based on the NXP Semiconductors

ARM9/LPC3250 processor. No description of compatible processor derivative functions is included, as

such functions are not relevant for the basic functioning of the phyCORE-LPC3250.

The phyCORE-LPC3250 offers the following features:

• Insert-ready, sub-miniature (70 x 58 mm) System on Module (SOM) subassembly in low EMI

design, achieved through advanced SMD technology

• Populated with the NXP LPC3250 processor (296-ball BGA packaging)

• Improved interference safety achieved through multi-layer PCB technology and dedicated ground

pins

• Controller signals and ports extend to two 160-pin high-density (0.635 mm) Molex connectors

aligning two sides of the board, enabling it to be plugged like a "big chip" into target application

• Max. 208 MHz core clock frequency

• Vector Floating Point coprocessor supporting single-precision and double-precision add, subtract,

multiply, divide, and multiply-accumulate at CPU clock speeds.

• Memory Management Unit (MMU), Memory and DMA controllers

• 64 MB of external address space, with bus buffers to condition and protect signal load of

peripherals on the LPC3250 external memory bus

• 1 to 8 MB of on-board NOR Flash operating at 1.8V or 3.15V

• 16 to 128 MB of on-board NAND flash at 1.8V

• 16 to 128MB of on-board 1.8V mobile SDRAM at 104 MHz

• 32 KByte SPI bootable EEPROM

• USB OTG transceiver for embedded USB host/peripheral functionality

• 6 rail voltage supervision with deep sleep supervision support

• On-board high efficiency switching regulators generating 1.8, 1.2, and an adjustable 0.9-1.2

voltage supplies

• Processor independent watchdog with disable, normal, and extended modes

© PHYTEC America LLC 2009

2

Part I, Chapter 1: Introduction

• Support for ETM9 and Embedded ICE-RT debug through JTAG interface

• Keyboard support for up to 64 keys in an 8 x 8 matrix (Ethernet must be disabled to support this

feature)

• 2x SPI ports

• 2x SSP ports

• 7x UARTs – 3 high speed (920kbps), 4 standard speed (460kbps), 1 supporting IrDA with 2x at

RS-232 levels

•2x I²S ports

• 2x I²C ports

• 10/100 Ethernet with HP Auto MDIX support

• 24-bit LCD controller supporting STN and TFT panels at up to 1024x768 display resolution

• Integrated LCD touch screen controller

• SD/MMC card interface

• SDIO controller

• Internal controller based RTC with 32 byte scratch pad memory

• External processor independent ultra low power RTC consuming 275nA @ 3.0V typical

• 32-bit high speed timer

• 4x timer/counters with capture inputs and match outputs

• 32-bit millisecond timer driven from the RTC clock

• Processor based watchdog timer

• 12x PWM outputs

• JTAG interface for debugging and download of user code

• Single supply voltage of 3.15V with on-board power management

• Industrial temperature range (-40°...+85°)

L-714e_1

© PHYTEC America LLC 2009

3

Part I, Chapter 1: Introduction

Fig. 1-1. phyCORE-LPC3250 Block Diagram

1.1 Block Diagram

L-714e_1

© PHYTEC America LLC 2009

4

Part I, Chapter 1: Introduction

Fig. 1-2. Top View of the phyCORE-LPC3250 (Controller Side)

1.2 View of the phyCORE-LPC3250

L-714e_1

© PHYTEC America LLC 2009

5

Part I, Chapter 1: Introduction

Fig. 1-3. Bottom View of the phyCORE-LPC3250 (Connector Side)

L-714e_1

© PHYTEC America LLC 2009

6

Part I, Chapter 2: Pin Description

L-714e_1

2 Pin Description

Please note that all module connections are not to exceed their expressed maximum voltage or current.

Maximum signal input values are indicated in the corresponding controller manuals/data sheets. As

damage from improper connections varies according to use and application, it is the user's responsibility to

take appropriate safety measures to ensure that the module connections are protected from overloading

through connected peripherals.

All controller signals extend to surface mount technology (SMT) connectors (0.635 mm) lining two sides of

the module (referred to as the phyCORE-Connector). This allows the phyCORE-LPC3250 to be plugged

into any target application like a "big chip".

The numbering scheme for the phyCORE-Connector is based on a two dimensional matrix in which

column positions are identified by a letter and row position by a number. Pin 1A, for example, is always

located in the upper left hand corner of the matrix. The pin numbering values increase moving down on the

board. Lettering of the pin connector rows progresses alphabetically from left to right (refer to Figure 2-1).

The numbered matrix can be aligned with the phyCORE-LPC3250 (viewed from above; phyCOREConnector pointing down) or with the socket of the corresponding phyCORE Carrier Board/user target

circuitry. The upper left-hand corner of the numbered matrix (pin 1A) is thus covered with the corner of the

phyCORE-LPC3250 marked with a white triangle. The numbering scheme is always in relation to the PCB

as viewed from above, even if all connector contacts extend to the bottom of the module.

The numbering scheme is thus consistent for both the module’s phyCORE-Connector as well as mating

connectors on the phyCORE Carrier Board or target hardware, thereby considerably reducing the risk of

pin identification errors.

Since the pins are exactly defined according to the numbered matrix previously described, the phyCOREConnector is usually assigned a single designator for its position (X1 for example). In this manner the

phyCORE-Connector comprises a single, logical unit regardless of the fact that it could consist of more

than one physical socketed connector. The location of row 1 on the board is marked by a white triangle on

the PCB to allow easy identification.

Figure 2-1 illustrates the numbered matrix system. It shows a phyCORE-LPC3250 with SMT phyCORE-

Connectors on its underside (defined as dotted lines) mounted on a Carrier Board. In order to facilitate

understanding of the pin assignment scheme, the diagram presents a cross-view of the phyCORE module

showing these phyCORE-Connectors mounted on the underside of the module’s PCB.

© PHYTEC America LLC 2009

7

Part I, Chapter 2: Pin Description

Fig. 2-1. Pin-out of the phyCORE-Connector (Top View, with Cross

Section Insert)

Table 2-1. Pin Descriptions, phyCORE-Connector X2, Row A

L-714e_1

Pin # Signal I/O SL Description

1A N/C - - Not connected

2A GND - - Ground

3A N/C - - Not connected

4A N/C - - Not connected

5A b_/CS0 O VCC_EMB Buffered µC signal /CS0 (memory bus chip select 0)

6A b_/CS1 O VCC_EMB Buffered µC signal /CS1 (memory bus chip select 1)

7A GND - - Ground

8A b_/WR O VCC_EMB Buffered µC signal /WR (memory bus write enable)

9A b_A1 O VCC_EMB Buffered µC signal A1 (memory bus address bit A1)

10A b_A2 O VCC_EMB Buffered µC signal A2 (memory bus address bit A2)

11A b_A4 O VCC_EMB Buffered µC signal A4 (memory bus address bit A4)

12A GND - - Ground

13A b_A7 O VCC_EMB Buffered µC signal A7 (memory bus address bit A7)

14A b_A9 O VCC_EMB Buffered µC signal A9 (memory bus address bit A9)

15A b_A10 O VCC_EMB Buffered µC signal A10 (memory bus address bit A10)

16A b_A12 O VCC_EMB Buffered µC signal A12 (memory bus address bit A12)

17A GND - - Ground

18A b_A15 O VCC_EMB Buffered µC signal A15 (memory bus address bit A15)

19A b_D1 I/O VCC_EMB Buffered µC signal D1 (memory bus data bit D1)

20A b_D2 I/O VCC_EMB Buffered µC signal D2 (memory bus data bit D2)

21A b_D4 I/O VCC_EMB Buffered µC signal D4 (memory bus data bit D4)

22A GND - - Ground

23A b_D7 I/O VCC_EMB Buffered µC signal D7 (memory bus data bit D7)

© PHYTEC America LLC 2009

8

Part I, Chapter 2: Pin Description

Table 2-1. Pin Descriptions, phyCORE-Connector X2, Row A (Continued)

Pin # Signal I/O SL Description

24A b_A17 O VCC_EMB Buffered µC signal A17 (memory bus address bit A17)

25A b_A18 O VCC_EMB Buffered µC signal A18 (memory bus address bit A18)

26A b_A20 O VCC_EMB Buffered µC signal A20 (memory bus address bit A20)

27A GND - - Ground

28A b_A23 O VCC_EMB Buffered µC signal A23 (memory bus address bit A23)

29A b_D9 I/O VCC_EMB Buffered µC signal D9 (memory bus data bit D9)

30A b_D10 I/O VCC_EMB Buffered µC signal D10 (memory bus data bit D10)

31A b_D12 I/O VCC_EMB Buffered µC signal D12 (memory bus data bit D12)

32A GND - - Ground

33A b_D15 I/O VCC_EMB Buffered µC signal D15 (memory bus data bit D15)

34A b_BLS0 O VCC_EMB Buffered µC signal BLS0 (memory bus byte lane select 0)

35A b_BLS2 O VCC_EMB Buffered µC signal BLS2 (memory bus byte lane select 2)

36A N/C - - Not connected

37A GND - - Ground

38A b_D17 I/O VCC_EMB Buffered µC signal D17 (memory bus data bit D17)

39A b_D19 I/O VCC_EMB Buffered µC signal D19 (memory bus data bit D19)

40A b_D20 I/O VCC_EMB Buffered µC signal D20 (memory bus data bit D20)

41A b_D22 I/O VCC_EMB Buffered µC signal D22 (memory bus data bit D22)

42A GND - - Ground

43A b_D25 I/O VCC_EMB Buffered µC signal D25 (memory bus data bit D25)

44A b_D27 I/O VCC_EMB Buffered µC signal D27 (memory bus data bit D27)

45A b_D28 I/O VCC_EMB Buffered µC signal D28 (memory bus data bit D28)

46A b_D30 I/O VCC_EMB Buffered µC signal D30 (memory bus data bit D30)

47A GND - - Ground

48A LCD21 O VCC µC signal LCD21 (blue color bit)

49A LCD20 O VCC µC signal LCD20 (blue color bit)

50A LCD19 O VCC µC signal LCD19 (blue color bit)

51A LCD17 O VCC µC signal LCD17 (blue color bit)

52A GND - - Ground

53A LCD14 O VCC µC signal LCD14 (green color bit)

54A LCD13 O VCC µC signal LCD13 (green color bit)

55A LCD11 O VCC µC signal LCD11 (green color bit)

56A LCD10 O VCC µC signal LCD10 (green color bit)

57A GND - - Ground

58A LCD7 O VCC µC signal LCD7 (red color bit)

59A LCD4 O VCC µC signal LCD4 (red color bit)

60A LCD3 O VCC µC signal LCD3 (red color bit)

61A LDC0 O VCC µC signal LCD0 (red color bit)

L-714e_1

© PHYTEC America LLC 2009

9

Part I, Chapter 2: Pin Description

Table 2-1. Pin Descriptions, phyCORE-Connector X2, Row A (Continued)

Pin # Signal I/O SL Description

62A GND - - Ground

63A LCDFP O VCC µC signal LCDFP (STN frame pulse/TFT vertical sync)

64A LCDLP O VCC µC signal LCDLP (STN line pulse/TFT horizontal sync)

65A LCDCP O VCC µC signal LCDCP (pixel clock)

66A LCDLE O VCC µC signal LCDLE (line end)

67A GND - - Ground

68A MS_DIO0 I/O VCC µC signal MS_DIO0 (MMC/SD data I/O 0)

69A MS_DIO2 I/O VCC µC signal MS_DIO2 (MMC/SD data I/O 2)

70A MS_BS I/O VCC µC signal MS_BS (MMC/SD command I/O)

71A MS_SCLK O - µC signal MS_SCLK (MMC/SD clock output)

72A GND - - Ground

73A TMS I VCC µC signal TMS (JTAG test mode select)

74A TDI I VCC µC signal TDI (JTAG test data input)

75A /TRST I VCC µC signal /TRST (JTAG test logic reset)

76A N/C - - Not connected

77A GND - - Ground

78A N/C - - Not connected

79A N/C - - Not connected

80A N/C - - Not connected

L-714e_1

Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B

Pin # Signal I/O SL Description

1B N/C - - Not connected

2B N/C - - Not connected

3B N/C - - Not connected

4B GND - - Ground

5B b_/CS3 O VCC_EMB Buffered µC signal /CS3 (memory bus chip select 3)

6B b_/CS2 O VCC_EMB Buffered µC signal /CS2 (memory bus chip select 2)

7B b_/OE O VCC_EMB Buffered µC signal /OE (memory bus output enable)

8B b_A0 O VCC_EMB Buffered µC signal A0 (memory bus address bit A0)

9B GND - - Ground

10B b_A3 O VCC_EMB Buffered µC signal A3 (memory bus address bit 3)

11B b_A5 O VCC_EMB Buffered µC signal A5 (memory bus address bit A5)

12B b_A6 O VCC_EMB Buffered µC signal A6 (memory bus address bit A6)

13B b_A8 O VCC_EMB Buffered µC signal A8 (memory bus address bit A8)

14B GND - - Ground

15B b_A11 O VCC_EMB Buffered µC signal A11 (memory bus address bit A11)

© PHYTEC America LLC 2009

10

Part I, Chapter 2: Pin Description

Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B (Continued)

Pin # Signal I/O SL Description

16B b_A13 O VCC_EMB Buffered µC signal A13 (memory bus address bit A13)

17B b_A14 O VCC_EMB Buffered µC signal A14 (memory bus address bit A14)

18B b_D0 I/O VCC_EMB Buffered µC signal D0 (memory bus data bit D0)

19B GND - - Ground

20B b_D3 I/O VCC_EMB Buffered µC signal D3 (memory bus data bit D3)

21B b_D5 I/O VCC_EMB Buffered µC signal D5 (memory bus data bit D5)

22B b_D6 I/O VCC_EMB Buffered µC signal D6 (memory bus data bit D6)

23B b_A16 O VCC_EMB Buffered µC signal A16 (memory bus address bit A16)

24B GND - - Ground

25B b_A19 O VCC_EMB Buffered µC signal A19 (memory bus address bit A19)

26B b_A21 O VCC_EMB Buffered µC signal A21 (memory bus address bit A21)

27B b_A22 O VCC_EMB Buffered µC signal A22 (memory bus address bit A22)

28B b_D8 I/O VCC_EMB Buffered µC signal D8 (memory bus data bit D8)

29B GND - - Ground

30B b_D11 I/O VCC_EMB Buffered µC signal D11 (memory bus data bit D11)

31B b_D13 I/O VCC_EMB Buffered µC signal D13 (memory bus data bit D13)

32B b_D14 I/O VCC_EMB Buffered µC signal D14 (memory bus data bit D14)

33B b_BLS1 O VCC_EMB Buffered µC signal BLS1 (memory bus byte lane select 1)

34B GND - - Ground

35B b_BLS3 O VCC_EMB Buffered µC signal BLS3 (memory bus byte lane select 3)

36B N/C - - Not connected

37B b_D16 I/O VCC_EMB Buffered µC signal D16 (memory bus data bit D16)

38B b_D18 I/O VCC_EMB Buffered µC signal D18 (memory bus data bit D18)

39B GND - - Ground

40B b_D21 I/O VCC_EMB Buffered µC signal D21 (memory bus data bit D21)

41B b_D23 I/O VCC_EMB Buffered µC signal D23 (memory bus data bit D23)

42B b_D24 I/O VCC_EMB Buffered µC signal D24(memory bus data bit D24)

43B b_D26 I/O VCC_EMB Buffered µC signal D26 (memory bus data bit D26)

44B GND - - Ground

45B b_D29 I/O VCC_EMB Buffered µC signal D29 (memory bus data bit D29)

46B b_D31 I/O VCC_EMB Buffered µC signal D31 (memory bus data bit D31)

47B LCD23 O VCC µC signal LCD23 (blue color bit)

48B LCD22 O VCC µC signal LCD22 (blue color bit)

49B GND - - Ground

50B LCD18 O VCC µC signal LCD18 (blue color bit)

51B LCD16 O VCC µC signal LCD16 (blue color bit)

52B LCD15 O VCC µC signal LCD15 (green color bit)

53B LCD12 O VCC µC signal LCD12 (green color bit)

L-714e_1

© PHYTEC America LLC 2009

11

Part I, Chapter 2: Pin Description

L-714e_1

Table 2-2. Pin Descriptions, phyCORE-Connector X2, Row B (Continued)

Pin # Signal I/O SL Description

54B GND - - Ground

55B LCD9 O VCC µC signal LCD9 (green color bit)

56B LCD8 O VCC µC signal LCD8 (green color bit)

57B LCD6 O VCC µC signal LCD6 (red color bit)

58B LCD5 O VCC µC signal LCD5 (red color bit)

59B GND - - Ground

60B LCD2 O VCC µC signal LCD2 (red color bit)

61B LCD1 O VCC µC signal LCD1 (red color bit)

62B LCDPWR O VCC µC signal LCDPWR (panel power enable)

63B LCDCLKIN I VCC µC signal LCDCLKIN (optional clock input signal)

64B GND - - Ground

65B LCDAC O VCC µC signal LCDAC (STN AC bias/TFT data enable)

66B MS_DIO1 I/O VCC µC signal MS_DIO1 (MMC/SD data I/O 1)

67B MS_DIO3 I/O VCC µC signal MS_DIO3 (MMC/SD data I/O 3)

68B N/C - - Not connected

69B GND - - Ground

70B TDO O VCC µC signal TMS (JTAG test data output)

71B TCK I VCC µC signal TMS (JTAG test clock input); Internal 10k pull-down

72B RTCK O VCC µC signal TMS (JTAG test clock return output); Internal 10k pull-

down

73B DBGEN I VCC µC signal DBGEN (JTAG/boundary scan select)

74B GND - - Ground

75B N/C - - Not connected

76B N/C - - Not connected

77B N/C - - Not connected

78B N/C - - Not connected

79B GND - - Ground

80B N/C - - Not connected

Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C

Pin # Signal I/O SL Description

1C VCC I 3.15V 3.15V primary voltage supply input

2C VCC I 3.15V 3.15V primary voltage supply input

3C GND - - Ground

4C VCC_SDIO I

5C VCC_SDIO I

© PHYTEC America LLC 2009

2.25 – 3.6V

2.25 – 3.6V

a

SDIO controller voltage interface select

b

SDIO controller voltage interface select

12

Part I, Chapter 2: Pin Description

L-714e_1

Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C (Continued)

Pin # Signal I/O SL Description

6C VBAT I 3.0V 3.0V battery backup input for sleep conditions. This

supply must be present for deep sleep.

7C GND - - Ground

8C N/C - - Not connected

9C /SERVICE I 3.15V µC signal /SERVICE/GPI_01. This signal has an inter-

nal 100k pull-up.

10C /RESET_SYS O 3.15V Open-drain system reset output with internal 10k pull-

up. Connect this to external 3.15V devices requiring a

power-up, power-fail, or power-down reset.

11C /RESOUT O 1.8V µC generated reset output. Connect this to external

1.8V devices required a power-up, power-fail, or

power-down reset.

12C GND - 0 Ground

13C /RESET_BAT O 3.0V Open-drain RTC and SDRAM power supply supervisor

reset output with internal 10k pull-up. Connect this to

external 3.0V devices requiring a power-up, power-fail,

or power-down reset. This signal is typically used with

external deep sleep control logic.

14C N/C - - Not connected

15C N/C - - Not connected

16C N/C - - Not connected

17C GND - - Ground

18C /FLASH_WP I VCC_EMB NOR flash write protect input with internal 10k pull-up.

Drive this signal low to prevent write access to the NOR

flash.

19C U5_RX I 3.15V µC signal U5_RX

20C U5_TX O 3.15V µC signal U5_TX

21C U5_RX_RS232 I

6.4V

c

U5_RX converted to RS-232 levels

22C GND - - Ground

23C U5_TX_RS232 O

6.4V

c

U5_TX converted to RS-232 levels

24C U3_TX O 3.15V µC signal U3_TX

25C U3_RX 3.15V µC signal U3_RX

26C U3_CTS I 3.15V µC signal U3_CTS/U2_HCTS

27C GND - - Ground

28C U3_DCD I 3.15V µC signal U3_DCD/GPI_05

29C U6_IRTX O 3.15V µC signal U6_IRTX

30C I2C2_SCL O 1.8V µC signal I2C2_SCL. This signal has an internal 2.2k

pull-up.

31C I2C1_SCL O 3.15V µC signal I2C1_SCL. This signal has an internal 2.2k

pull-up.

32C GND - - Ground

© PHYTEC America LLC 2009

13

Part I, Chapter 2: Pin Description

L-714e_1

Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C (Continued)

Pin # Signal I/O SL Description

33C ENET_LINK O 3.15V Ethernet link status output. Typically this is connected

to a link LED to indicate Ethernet link status.

34C ENET_ACTIVITY O 3.15V Ethernet activity status output. Typically this is con-

nected to an activity LED to indicated Ethernet activity

status.

35C ENET_RXN I

36C ENET_RXP I

Note

Note

d

d

Ethernet negative differential receive input

Ethernet positive differential receive input

37C GND - - Ground

38C GPIO_0 I/O 3.15V µC signal GPIO_00

39C GPI_3 I 1.8V µC signal GPI_03

40C GPI_19 I 3.15V µC signal GPI_19

41C GPO_0 O 1.8V µC signal GPO_00/TST_CLK1

42C GND - - Ground

43C GPO_5 O 1.8V µC signal GPO_05

44C GPO_14 O 1.8V µC signal GPO_14

45C GPO_19 O 1.8V µC signal GPO_19. This signal defaults to NAND Flash

write protection control via jumper J5 with an internal

100k pull-up. See section 9.2 for details.

46C USB_ADR/PSW I/O 1.8V USB OTG address select input/power supply control

output. On power-up this signal is latched as the lower

USB transceiver address bit and can be reconfigured

as a power supply control output to control an external

5.0V power supply in HOST mode. This signal has an

internal 100k pull-down.

47C GND - - Ground

48C USB_VBUS I/O 5.0V USB OTG VBUS input and output. This signal supplies

up to 8mA when operating as an embedded OTG Host.

49C SCK0 I/O 3.15V µC signal SCK0/SPI1_CLK. This signal is connected to

the on-board SPI bootable EEPROM.

50C MISO0 I/O 3.15V µC signal MISO0/SPI1_DATIN. This signal is con-

nected to the on-board SPI bootable EEPROM and has

an internal 10k pull-up.

51C SSEL0 I/O 3.15V µC signal SSEL0/GPIO_05. This signal is connected to

the on-board SPI bootable EEPROM and has an internal 10k pull-up.

52C GND - - Ground

53C I2STX_CLK1 I/O 3.15V µC signal I2STX_CLK1/MAT3.0

54C I2STX_SDA1 I/O 3.15V µC signal I2STX_SDA1/MAT3.1

55C I2STX_WS1 I/O 3.15V µC signal I2STX_WS1/CAP3.0

56C ENET_RXD2 I 3.15V µC signal ENET_RXD2/GPI_00

57C GND - - Ground

58C ENET_CRS I 3.15V µC signal ENET_CRS/KEY_COL3

© PHYTEC America LLC 2009

14

Part I, Chapter 2: Pin Description

L-714e_1

Table 2-3. Pin Descriptions, phyCORE-Connector X2, Row C (Continued)

Pin # Signal I/O SL Description

59C ENET_MDIO I/O 3.15V µC signal ENET_MDIO/GPIO_03/KEY_ROW7

60C ENET_RX_ER I 3.15V µC signal ENET_RX_ER/KEY_COL2

61C ENET_TX_ER I/O 3.15V µC signal ENET_TX_ER/KEY_ROW0

62C GND - - Ground

63C ENET_TX_EN I/O 3.15V µC signal ENET_TX_EN/KEY_ROW3

64C ENET_RXD3 I 3.15V µC signal ENET_RXD3/GPI_02/CAP2.0

65C ENET_RXD1 I 3.15V µC signal ENET_RXD1/KEY_COL5

66C ENET_TXD3 I/O 3.15V µC signal ENET_TXD3/KEY_ROW2

67C GND - - Ground

68C ENET_TXD0 I/O 3.15V µC signal ENET_TXD0/KEY_ROW4

69C /SDIO_CD I VCC_SDIO SDIO controller card detect signal with internal 100k

pull-up.

70C SDIO_POW1 I VCC_SDIO SDIO controller power control signal 1 output

71C SDIO_CMD I/O VCC_SDIO SDIO controller command input/output

72C GND - - Ground

73C SDIO_D1 I/O VCC_SDIO SDIO controller data 1 input/output

74C SDIO_D2 I/O VCC_SDIO SDIO controller data 2 input/output

75C SDIO_D4 I/O VCC_SDIO SDIO controller data 4 input/output

76C SDIO_D7 I/O VCC_SDIO SDIO controller data 7 input/output

77C AGND - - Analog ground

78C TS_XOUT I/O 3.15V µC signal TS_XOUT

79C ADIN1 I 3.15V µC signal ADIN1

80C ADIN0 I 3.15V µC signal ADIN0

a. See the NXP SDIO101 datasheet for details.

b. See the NXP SDIO101 datasheet for details.

c. Typical -- See ADM3307 datasheet for details.

d. See LAN8700I datasheet for details.

Table 2-4. Pin Descriptions, phyCORE-Connector X2, Row D

Pin # Signal I/O SL Description

1D VCC I 3.15V 3.15V primary voltage supply input

2D VCC I 3.15V 3.15V primary voltage supply input

3D GND - - Ground

4D VCC_AD_EXT I 3.15V µC ADC power supply input

5D VCC_AD_EXT I 3.15V µC ADC power supply input

6D N/C - - Not connected

7D N/C - - Not connected

8D WDI I 3.15V Watchdog input. Connect this pin to an applicable sig-

© PHYTEC America LLC 2009

nal to periodically reset the watchdog timer.

15

Part I, Chapter 2: Pin Description

L-714e_1

Table 2-4. Pin Descriptions, phyCORE-Connector X2, Row D (Continued)

Pin # Signal I/O SL Description

9D GND - - Ground

10D /RESIN I

3.0V

a

or 3.15V

System reset input. Connect this pin to an open-drain

output and momentarily pull LOW to initiate a system

reset. Do not connect this pin to a push-pull output or

any other pull-up/pull-down circuitry.

11D N/C - - Not connected

12D N/C - - Not connected

13D N/C - - Not connected

14D GND - - Ground

15D N/C - - Not connected

16D U1_RX I 3.15V µC signal U1_RX/CAP1.0

17D U1_TX O 3.15V µC signal U1_TX

18D GPO_20 O 1.8V µC signal GPO_20

19D GND - - Ground

20D /RS232_EN I 3.15V UART 5/UART 1 RS-232 transceiver enable input. This

signal has an internal 100k pull-down.

21D RS232_SD I 3.15V UART 5/UART 1 RS-232 transceiver shut down input.

This signal has an internal 100k pull-down.

22D U1_RX_RS232 I

23D U1_TX_RS232 O

6.4V

6.4V

b

b

U1_RX converted to RS-232 levels

U1_TX converted to RS-232 levels

24D GND - - Ground

25D U3_DSR I/O 3.15V µC signal U3_DSR/U2_RX

26D U3_DTR O 3.15V µC signal U3_DTR/U2_TX

27D U3_RTS O 3.15V µC signal U3_RTS/U2_HRTS/GPO_23

28D U3_RI I 3.15V µC signal U3_RI/GPI_11

29D GND - - Ground

30D U6_IRRX I 3.15V µC signal U6_IRRX

31D I2C2_SDA I/O 1.8V µC signal I2C2_SDA. This signal has an internal 2.2k

pull-up.

32D I2C1_SDA I/O 3.15V µC signal I2C1_SDA. This signal has an internal 2.2k

pull-up.

33D /RTC_INT O 3.0V Off-chip Real Time Clock interrupt alarm open-drain

output. This pin has an optional 100k internal pull-up.[3]

34D GND - - Ground

35D ENET_TXN O

36D ENET_TXP O

37D ENET_CLKEN I 3.15V Ethernet clock enable. This pin has an internal 100k

© PHYTEC America LLC 2009

Note

Note

c

c

Ethernet negative differential transmit output

Ethernet positive differential transmit output

pull-up. Ground this pin to disable the ethernet clock.

Typically this is used in a low power mode.

16

Part I, Chapter 2: Pin Description

L-714e_1

Table 2-4. Pin Descriptions, phyCORE-Connector X2, Row D (Continued)

Pin # Signal I/O SL Description

38D GPIO_1 I/O 3.15V µC signal GPIO_01

39D GND - - Ground

40D GPI_7 I 3.15V µC signal GPI_07/PCAP3.0. This signal is used as the

SDIO controller interrupt input and has an internal 10k

pull-up.

41D GPO_1 O 1.8V µC signal GPO_01

42D GPO_4 O 3.15V µC signal GPO_04

43D GPO_11 O 3.15V µC signal GPO_11

44D GND - - Ground

45D GPO_17 O 3.15V µC signal GPO_17

46D USB_ID I

Note

d

USB OTG ID pin. Normally this pin is connected

directly to the ID pin on an OTG connector.

47D USB_D+ I/O

48D USB_D- I/O

Note

Note

d

d

USB positive differential input/output

USB negative differential input/output

49D GND - - Ground

50D MOSI0 I/O 3.15V µC signal MOSI0/SPI1_DATIO

51D GPI_4 I 3.15V µC signal GPI_04/SPI1_BUSY

52D ONSW O 1.2V µC signal ONSW

53D N/C - - Not connected

54D GND - - Ground

55D I2SRX_CLK1 I/O 3.15V µC signal I2SRX_CLK1/P0.0

56D I2SRX_SDA1 I 3.15V µC signal I2SRX_SDA1/HSTIM_CAP/GPI_06

57D I2SRX_WS1 I/O 3.15V µC signal I2SRX_WS1/P0.1

58D ENET_COL I 3.15V µC signal ENET_COL/KEY_COL7/GPI_09

59D GND - - Ground

60D ENET_MDC I/O 3.15V µC signal ENET_MDC/KEY_ROW6/GPIO_02

61D ENET_RX_DV I 3.15V µC signal ENET_RX_DV/SPI2_BUSY/KEY_COL6/

GPI_08

62D ENET_REF_CLKI 3.15V µC signal ENET_REF_CLK/ENET_RX_CLK/

KEY_COL1

63D ENET_TX_CLK I 3.15V µC signal ENET_TX_CLK/KEY_COL0

64D GND - - Ground

65D ENET_RXD0 I 3.15V µC signal ENET_RXD0/KEY_COL4

66D ENET_TXD2 I/O 3.15V µC signal ENET_TXD2/KEY_ROW1

67D ENET_TXD1 I/O 3.15V µC signal ENET_TXD1/KEY_ROW5

68D TST_CLK2 O 3.15V µC signal TST_CLK2

69D GND - - Ground

70D /SDIO_WP I VCC_SDIO SDIO controller write protect input. This pin has an

internal 100k pull-up.

© PHYTEC America LLC 2009

17

Part I, Chapter 2: Pin Description

Table 2-4. Pin Descriptions, phyCORE-Connector X2, Row D (Continued)

Pin # Signal I/O SL Description

71D SDIO_POW0 O VCC_SDIO SDIO controller power control signal 1 output

72D SDIO_CLK O VCC_SDIO SDIO controller clock output

73D SDIO_D0 I/O VCC_SDIO SDIO controller data 0 input/output

74D GND - - Ground

75D SDIO_D3 I/O VCC_SDIO SDIO controller data 3 input/output

76D SDIO_D5 I/O VCC_SDIO SDIO controller data 5 input/output

77D SDIO_D6 I/O VCC_SDIO SDIO controller data 6 input/output

78D TS_YOUT I/O - µC signal TS_YOUT

79D AGND - - Analog ground

80D ADIN2 I 3.15V µC signal ADIN2

a. 3.0V is the standard phyCORE-LPC3250 SOM configuration.

b. Typical -- see ADM3307 datasheet for details.

c. See the LAN8700I datasheet for details.

d. See the ISP1301 datasheet for details.

L-714e_1

© PHYTEC America LLC 2009

18

Part I, Chapter 3: Jumpers

Fig. 3-1. Jumper Locations (Controller Side)

L-714e_1

3 Jumpers

For configuration purposes, the phyCORE-LPC3250 has 24 solder jumpers, some of which have been

installed prior to delivery. Figure 3-1 and Figure 3-2 indicate the location of the solder jumpers on the

board. There are 11 solder jumpers located on the top side of the module (opposite side of connectors)

and 13 solder jumpers on the bottom side.

If manual jumper modification is required be sure to pay special attention to the "TYPE" column to ensure

you are using the correct type of jumper (0 Ohms, 10k Ohms, etc…). All jumpers are 0805 package with a

1/8W or better power rating.

Three and four position jumpers have pin 1 marked with a GREEN pad.

© PHYTEC America LLC 2009

19

Part I, Chapter 3: Jumpers

Fig. 3-2. Jumper Locations (Connector Side)

L-714e_1

Table 3-1 below provides a functional summary of the solder jumpers, their default positions, and possible

alternative positions and functions. A detailed description of each solder jumper can be found in the

applicable chapter listed in the table.

Table 3-1. Jumper Settings

J Type Setting Description Chapter

J1 0R 1+2

J2 0R 1+2

J3 0R 1+2

J4 0R 1+2

Data bus buffer D16...23 output enable controlled by processor signal BLS2.

2+3

Data bus buffer D16...23 output permanently enabled.

Data bus buffer D24...31 output enable controlled by processor signal BLS3.

2+3

Data bus buffer D24...31 output permanently enabled.

Data bus buffer D0...7 output enable controlled by processor signal

BLS0.

2+3

Data bus buffer D0...7 output permanently enabled.

Data bus buffer D8...15 output enable controlled by processor signal BLS1.

Data bus buffer D8...15 output permanently enabled.

2+3

13

13

13

13

© PHYTEC America LLC 2009

20

Part I, Chapter 3: Jumpers

L-714e_1

Table 3-1. Jumper Settings (Continued)

J Type Setting Description Chapter

J5 0R 1+2

2+3

2+4

Open

J6 0R 1+2

2+3

J7 10k Open

Closed

J8 10k Open

Closed

J9 10k Open

Closed

J16 0R Open

Closed

J17 0R Open

Closed

J19 0R 1+2

2+3

J21 0R 1+2

2+3

J22 0R Open

Closed

J23 0R Open

Closed

J24 0R Open

Closed

J25 0R Open

Closed

J26 0R Open

Closed

J27 0R Open

Closed

J28 0R Open

Closed

J29 0R Open

Closed

NAND Flash write protected during power-up, power-fail, and

power-down events by the controller /RESOUT signal.

NAND Flash permanently write protected.

NAND Flash write protection controlled via GPO_19.

NAND Flash permanently write enabled.

Activating /RESIN produces a system /RESET_SYS event.

Activating /RESIN produces a system /RESET_SYS and a /

RESET_BAT event.

Ethernet PHY operation MODE0 bit = 1.

Ethernet PHY operation MODE0 bit = 0.

Ethernet PHY operation MODE1 bit = 1.

Ethernet PHY operation MODE1 bit = 0.

Ethernet PHY operation MODE2 bit = 1.

Ethernet PHY operation MODE2 bit = 0.

µC signal SSEL0 disconnected from on-board SPI EEPROM /CS0

input.

µC signal SSEL0 connected to on-board SPI EEPROM /CS0

input.

Watchdog extended mode selected. Timeout period ~6s.

Watchdog normal mode selected. Timeout period ~12ms.

External watchdog reset forces a system wide reset and sleep

reset.

External watchdog reset forces a system wide reset.

External memory bus voltage set to 1.8V.

External memory bus voltage set to 3.15V.

Voltage regulator U22 disconnected from VCC_RTC.

Voltage regulator U22 supplies VCC_RTC power.

Voltage regulator U22 disconnected from VCC_SDRAM.

Voltage regulator U22 supplies VCC_SDRAM power.

Voltage regulator U23 disconnected from VCC_SDRAM.

Voltage regulator U23 supplies VCC_SDRAM power.

Voltage regulator U23 disconnected from VCC_1V8.

Voltage regulator U23 supplies VCC_1V8 power.

Voltage regulator U23 disconnected from VCC_RTC.

Voltage regulator U23 supplies VCC_RTC power.

Voltage regulator U23 disconnected from VCC_CORE.

Voltage regulator U23 supplies VCC_CORE power.

Voltage regulator U23 disconnected from VCC_1V2.

Voltage regulator U23 supplies VCC_1V2 power.

Voltage regulator U27 disconnected from VCC_CORE.

Voltage regulator U27 supplies VCC_CORE power.

9.2

N/A

10.2

10.2

10.2

9.5

7

7

13.1

4.5.3

4.5.3

4.5.1

4.5.1

4.5.1

4.5.1

4.5.1

4.5.2

© PHYTEC America LLC 2009

21

Part I, Chapter 3: Jumpers

Fig. 3-3. Default Jumper Settings (Controller Side)

L-714e_1

Table 3-1. Jumper Settings (Continued)

J Type Setting Description Chapter

J30 0R Open

Closed

J31 10k 1+2

2+3

J32 0R 1+2

2+3

µC signal LCD17/HIGHCORE disconnected from core voltage control.

µC signal LCD17/HIGHCORE controls core voltage setting

(0.9V or 1.2V).

SPI EEPROM write enabled.

SPI EEPROM write protected.

Off-chip RTC power is automatically selected between VCC

and VBAT based on VCC presence.

Off-chip RTC power is powered by VBAT input only.

4.5.2

9.5

6

© PHYTEC America LLC 2009

22

Part I, Chapter 3: Jumpers

Fig. 3-4. Default Jumper Settings (Connector Side)

L-714e_1

© PHYTEC America LLC 2009

23

Part I, Chapter 4: Power

L-714e_1

4 Power

The phyCORE-LPC3250 operates off of four separate power supply input domains. For systems that do

not required maximum flexibility it is possible to operate the phyCORE-LPC3250 off of a single power

supply voltage.

The following sections of this chapter discuss the primary power pins on the phyCORE-Connector X2 in

detail.

4.1 Primary System Power (VCC)

The phyCORE-LPC3250 operates off of a primary voltage supply with a nominal value of 3.15V. On-board

switching regulators generate the 1.8V, and 1.2V, and adjustable 0.9-1.2V voltage supplies required by the

LPC3250 MCU and on-board components from the primary 3.15V supplied to the SOM.

For proper operation the phyCORE-LPC3250 must be supplied with a voltage source of 3.15V ± 0.1V at

the VCC pins on the phyCORE-Connector X2. See Table 2-1 for VCC pin locations. See Chapter 14 for

current requirements.

Connect all +3.15V VCC input pins to your power supply and at least the matching number of GND pins

neighboring the +3.15V pins.

CAUTION:

As a general design rule we recommend connecting all GND pins neighboring signals which are being

used in the application circuitry. For maximum EMI performance all GND pins should be connected to a

solid ground plane.

4.2 Secondary Battery Power (VBAT)

For applications requiring a low power deep sleep mode a secondary battery sleep supply with a nominal

value of 3.0V is required. The battery supply powers the SDRAM and RTCs during a sleep condition,

allowing primary system power (VCC) to be removed.

For deep sleep operation the phyCORE-LPC3250 must be supplied with a secondary voltage source of

3.0V ± 0.1V at the VBAT pin on the phyCORE-Connector X2. See Table 2-1 for the VBAT pin location. See

Chapter 14 for current requirements.

Applications not requiring a sleep mode can connect the VBAT pin to the primary system power supply

(VCC = 3.15V).

4.3 Analog-to-Digital Converter Power (VCC_AD_EXT)

The LPC3250 Analog-to-Digital converter power domain pins are brought out to the phyCORE-Connector

X2 for an optional external filtered power supply. See Table 2-1 for the VCC_AD_EXT pin location. See the

NXP LPC3250 datasheet for permissible input voltage ranges (2.7V to 3.3V as of the printing of this

manual).

In general the VCC_AD_EXT pins will be connected to the primary VCC = 3.15V supply, requiring no

special circuitry. The phyCORE-LPC3250 Carrier Board connects the VCC_AD_EXT pins through a 1R/

4.7uF filter network from the primary VCC = 3.15V supply. Refer to the phyCORE-LPC3250 Carrier Board

schematics for details.

© PHYTEC America LLC 2009

24

Part I, Chapter 4: Power

L-714e_1

4.4 SDIO Controller Power (VCC_SDIO)

The on-board SDIO controller is capable of a configurable interface voltage to meet the demands of the

variety of SDIO devices with varying power requirements. In addition the SDIO controller is capable of

switching between a high power and low power mode on-the-fly to optimize dynamic power consumption.

The SDIO controller interface voltage is powered and set via the VCC_SDIO pins on the phyCOREConnector X2. The high/low power switching is controlled via the SDIO_POW0 and SDIO_POW1 pins on

the phyCORE-Connector X2. See the NXP SDIO101 datasheet for details on these power mode control

pins. See Table 2-1 for the locations of the applicable SDIO power and control pins.

For applications requiring an adjustable SDIO supply voltage the VCC_SDIO pins must be supplied with a

voltage of 2.25-3.6V

1

. See Chapter 14 for current requirements. See the phyCORE-LPC3250 Carrier

Board schematics for example adjustable supply circuitry. For SDIO applications which can operate off of

3.15V the VCC_SDIO pins can be connected directly to the VCC power supply and the SDIO_POW0/1

pins can be left unconnected.

4.5 On-board Voltage Regulators

The phyCORE-LPC3250 provides three on-board switching regulators to source the 1.2V, 1.8V, and

adjustable 0.9-1.2V voltages required by the processor and on-board components. Figure 4-1 presents a

graphical depiction of the powering scheme. The jumpers in blue are by default populated, while the

jumpers in white are unpopulated. By default U27 powers the VCC_CORE rail with an adjustable supply,

U22 powers the VCC_RTC and VCC_SDRAM rails, and U23 powers the VCC_1V2 and VCC_1V8 rails.

Notice that U22 generates 1.2V and 1.8V just as does U23. The reason for this is that U22 continues to

power the RTC and SDRAM subsystems via backup battery during a sleep mode. See Chapter 5 for

details.

To reduce system costs U27 and U22 can be removed. To supply the power lost by the removal of these

two regulators J26, J27, and J24 must be closed. Figure 4-1 depicts the standard default configuration, but

custom configurations can also be ordered. If your system does not require an adjustable core voltage to

periodically lower core power consumption while keeping the system powered then U27 can be removed

and J27 can be closed (note that the core is fixed at 1.2V in this case). If your system is not power

conscious and does not need to enter a sleep mode during moments of processor inactivity to conserve

power then U23 can be removed and J26 and J24 can be closed. This multi regulator + jumper approach

provide cost and system requirement flexibility.

The following sections go into detail about each switching regulator and any associated configuration

jumpers.

1. See the NXP SDIO101 datasheet for details.

© PHYTEC America LLC 2009

25

Part I, Chapter 4: Power

U22

VCC_SDRAM

1.2V

1.8V

U23

1.2V

1.8V

J26

J27

J28

J24

J25

J22

J23

VCC_RTC

VCC_CORE

VCC_1V2

VCC_1V8

U27 J290.9-1.2V

Fig. 4-1. phyCORE-LPC3250 On-board Powering Scheme

L-714e_1

4.5.1 Primary 1.2V and 1.8V Supplies (U23)

The dual output switching regulator located at U23 generates the 1.2V and 1.8V core and peripheral

supplies required by system components from the primary VCC = 3.15V board supply. Various jumpers

have been provided as current measurement access points on the outputs of both of these supplies. Table

4-1 provides a summary of the jumpers and their operation. See Chapter 4.5.4 for current measurement

techniques with a precision shunt resistor.

Table 4-1. U23 1.2V/1.8V Primary Voltage Regulator Jumper Settings

J Type Setting Description

J24 0R Open

J25 0R Open

J26 0R Open

J27 0R Open

J28 0R Open

Closed

Closed

Closed

Closed

Closed

Voltage regulator U23 disconnected from VCC_SDRAM.

Voltage regulator U23 supplies VCC_SDRAM power. Do not close this unless

U22 is unpopulated.

Voltage regulator U23 disconnected from VCC_1V8.

Voltage regulator U23 disconnected from VCC_1V8.

Voltage regulator U23 disconnected from VCC_RTC.

Voltage regulator U23 supplies VCC_RTC power. Do not close this unless U22

is unpopulated.