Philips XA-C3 Datasheet

Philips Semiconductors Advance information – Subject to change

XA-C316-bit microcontroller with on-chip CAN

DESCRIPTION

The XA-C3 device is a member of Philips’ 80C51 XA (eXtended

Architecture) family of high performance 16-bit single-chip

microcontrollers, and is intended for industrial control applications.

The XA-C3 device supports the full Controller Area Network (CAN)

2.0B. It supports both 11-bit and 29-bit identifiers (ID) at up to

1Mbit/s data rate. It is further optimized for DeviceNet applications.

The performance of the XA architecture supports the

comprehensive bit-oriented operations of the 80C51 while

incorporating support for multi-tasking operating systems and

high-level languages such as C. The speed of the XA architecture,

at 10 to 100 times that of the 80C51, gives designers an easy path

to truly high performance embedded control, while maintaining great

flexibility to adapt software to specific requirements.

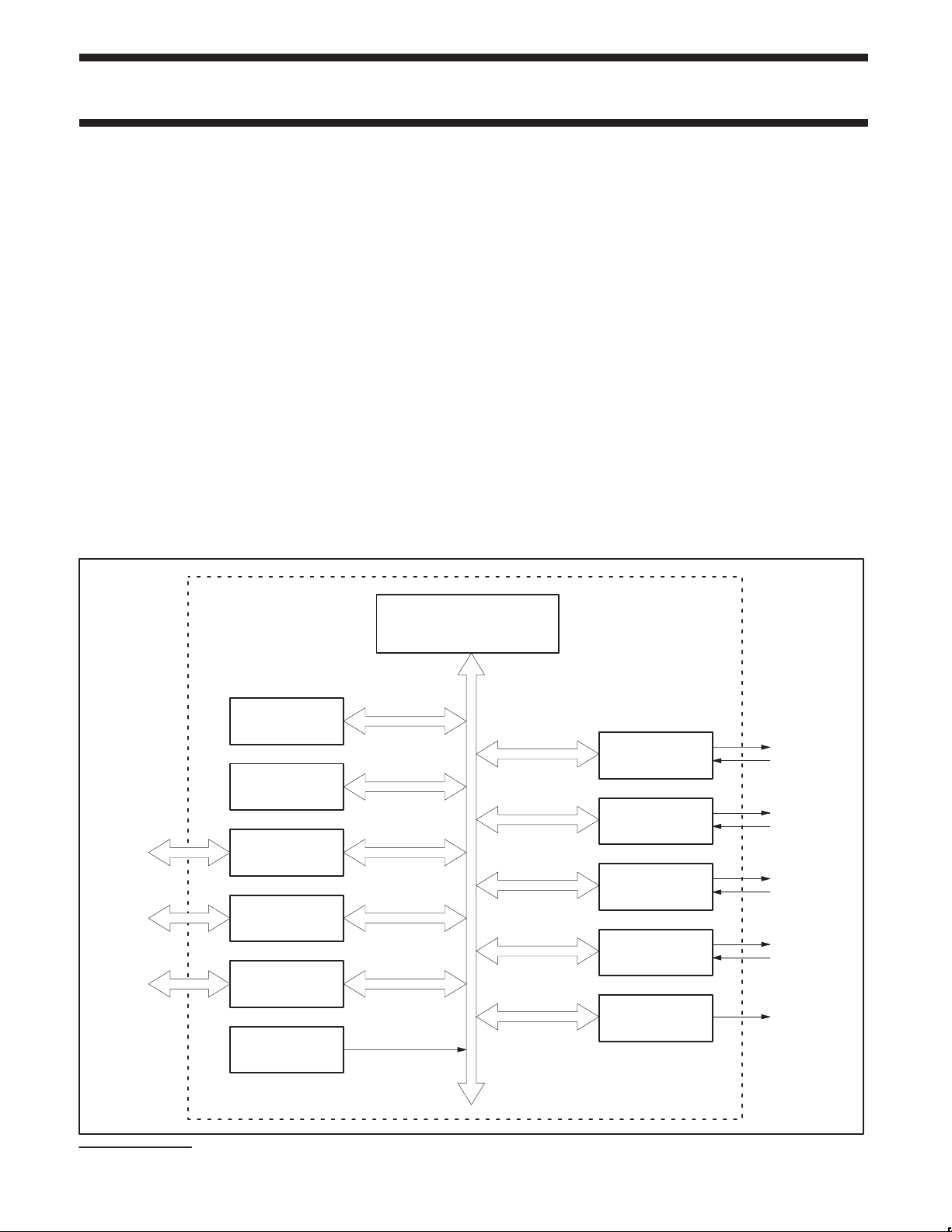

BLOCK DIAGRAM

XA CPU Core

Specific Features of the XA-C3

•2.7V to 5.5V operation

•32K bytes of on-chip EPROM/ROM program memory

•1024 bytes of on-chip data RAM

•CAN block supporting full CAN2.0B, with 11-/29-bit ID and up to

1Mbit/s

•Three standard counter/timers with enhanced features (equivalent

to 80C51 T0, T1, and T2) with outputs

•Watchdog timer with output

•1 UART

•Low voltage detect

•Three 8-bit I/O ports with 4 programmable output configurations

•EPROM/OTP versions can be programmed in circuit

•25MHz operating frequency at 4.5 – 5.5V V

operating conditions; 16MHz at 2.7V – 3.6V V

over commercial

CC

CC

•40-pin DIP, 44-pin PLCC, and 44-pin QFP packages

32K BYTES

ROM/EPROM

1024 BYTES

STATIC RAM

PORT 0

PORT 1

PORT 2

LOW VOLTAGE

DETECT

PERIPHERAL

BUS

UART

CAN 2.0B

TIMER 0 &

TIMER 1

TIMER 2

WATCHDOG

TIMER

SU00669

DeviceNet is a trademark of Open DeviceNet Vendor Association (OVDA).

1995 Jul 21

1

Loading...

Loading...