Philips TZA3004HL-C3 Datasheet

DATA SH EET

Objective specification

File under Integrated Circuits, IC19

1998 Feb 09

INTEGRATED CIRCUITS

TZA3004HL

SDH/SONET data and clock

recovery unit STM1/4 OC3/12

1998 Feb 09 2

Philips Semiconductors Objective specification

SDH/SONET data and clock recovery unit

STM1/4 OC3/12

TZA3004HL

FEATURES

• Data and clock recovery up to 622 Mbits/s (STM1/OC3

and STM4/OC12)

• Differential data input with 2.5 mV peak-to-peak typical

sensitivity

• Differential CML (Current-Mode Logic) data and clock

outputs with 50 Ω driving capability

• Adjustable CML output level

• Loop mode for system testing

• BER related LOS detection

• Few external components needed

• LQFP48 plastic package

• Power dissipation typical 370 mW

• Single supply voltage.

DESCRIPTION

The TZA3004HL is a data and clock recovery IC intended

for use in SDH (Synchronous Digital Hierarchy) and

SONET (Synchronous Optical Network) systems.

The circuit recovers data and extracts the clock signal from

an incoming bitstream up to 622 Mbits/s. It can be

configured for use in STM1/OC3 and STM4/OC12

systems.

APPLICATIONS

• Data and clock recovery in STM1/OC3 and STM4/OC12

transmission systems (up to 622 Mbits/s).

ORDERING INFORMATION

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

TZA3004HL LQFP48 plastic low profile quad flat package; 48 leads; body 7 × 7 × 1.4 mm SOT313-2

1998 Feb 09 3

Philips Semiconductors Objective specification

SDH/SONET data and clock recovery unit

STM1/4 OC3/12

TZA3004HL

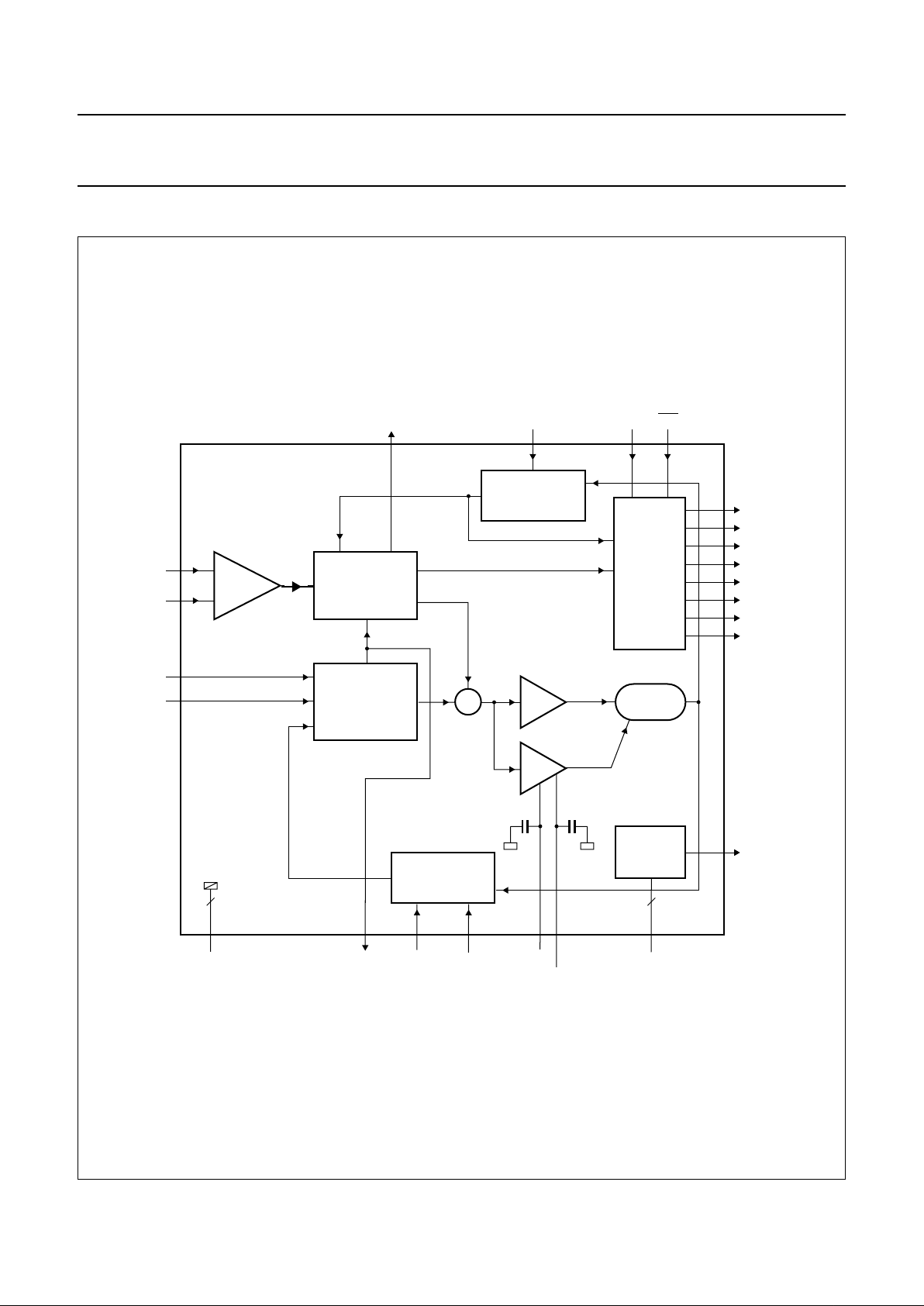

BLOCK DIAGRAM

Fig.1 Block diagram.

handbook, full pagewidth

MGK140

FREQUENCY

WINDOW

DETECTOR

(1000 ppm)

+

ALEXANDER

PHASE

DETECTOR

FREQUENCY

DIVIDER 1

4/16

FREQUENCY

DIVIDER 2

64/128

DATA

AND

CLOCK

OUTPUT

VCRO

proportional

path

integrating

path

POWER

CONTROL

1

2, 5, 8, 10, 11, 14, 17,

20, 23, 26, 29, 32, 35,

38, 41, 44, 47

9

36

33

30

1516

21

22

enable

48

42

45

46

7

37

39

12 24 25, 31

TZA3004HL

DCSQ

DIN

34

DINQ

SEL155

V

EE

DOUT

DOUTQ

COUT

COUTQ

DLOOP

DLOOPQ

CLOOP

CLOOPQ

43

LOS

PC

AREF

GND

3

4

6

REF19LOCK

CAPUPQ

CAPDOQREF39

CREF

CREFQ

ENL

130 pF130 pF

∫ dt

17 2

1998 Feb 09 4

Philips Semiconductors Objective specification

SDH/SONET data and clock recovery unit

STM1/4 OC3/12

TZA3004HL

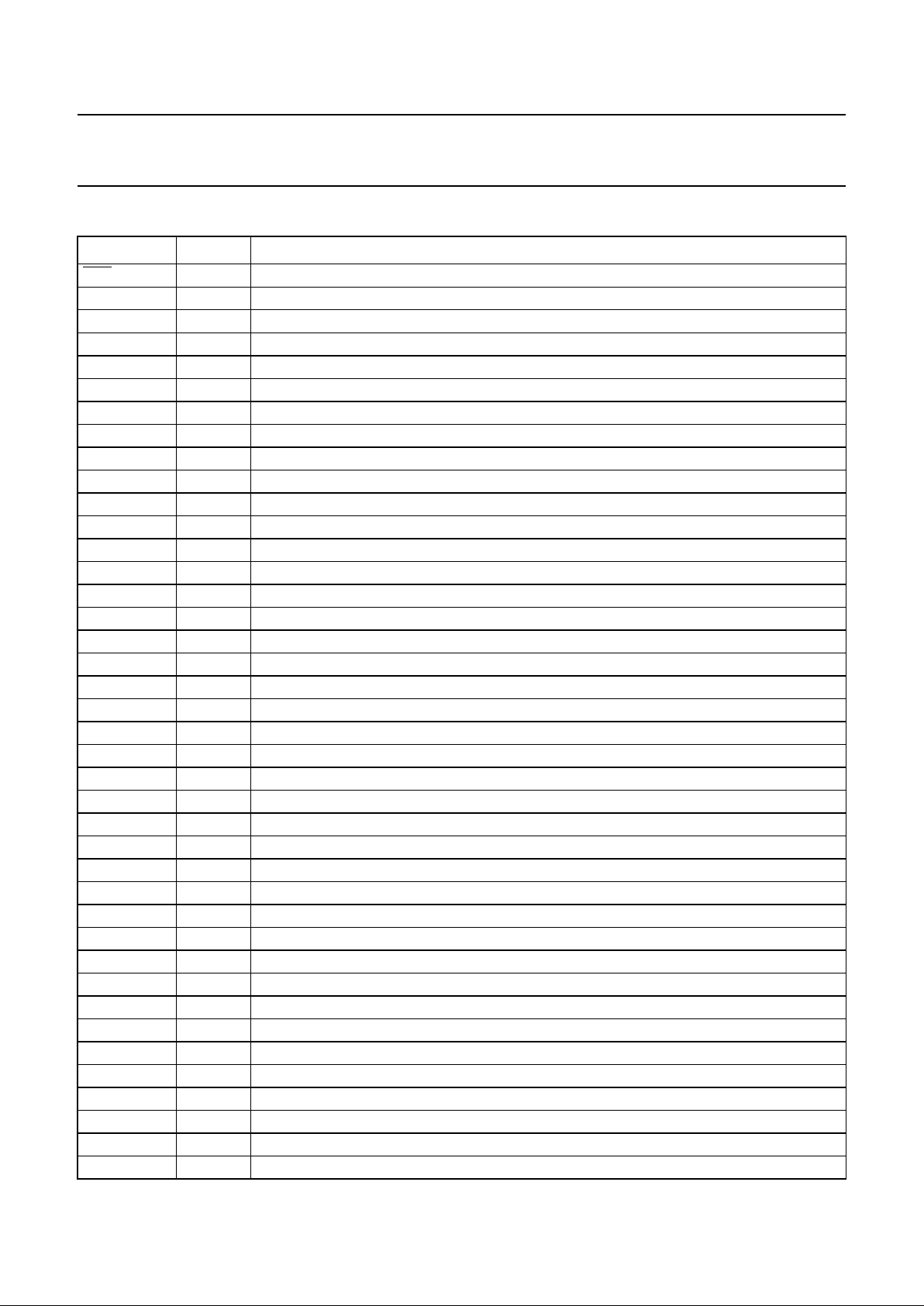

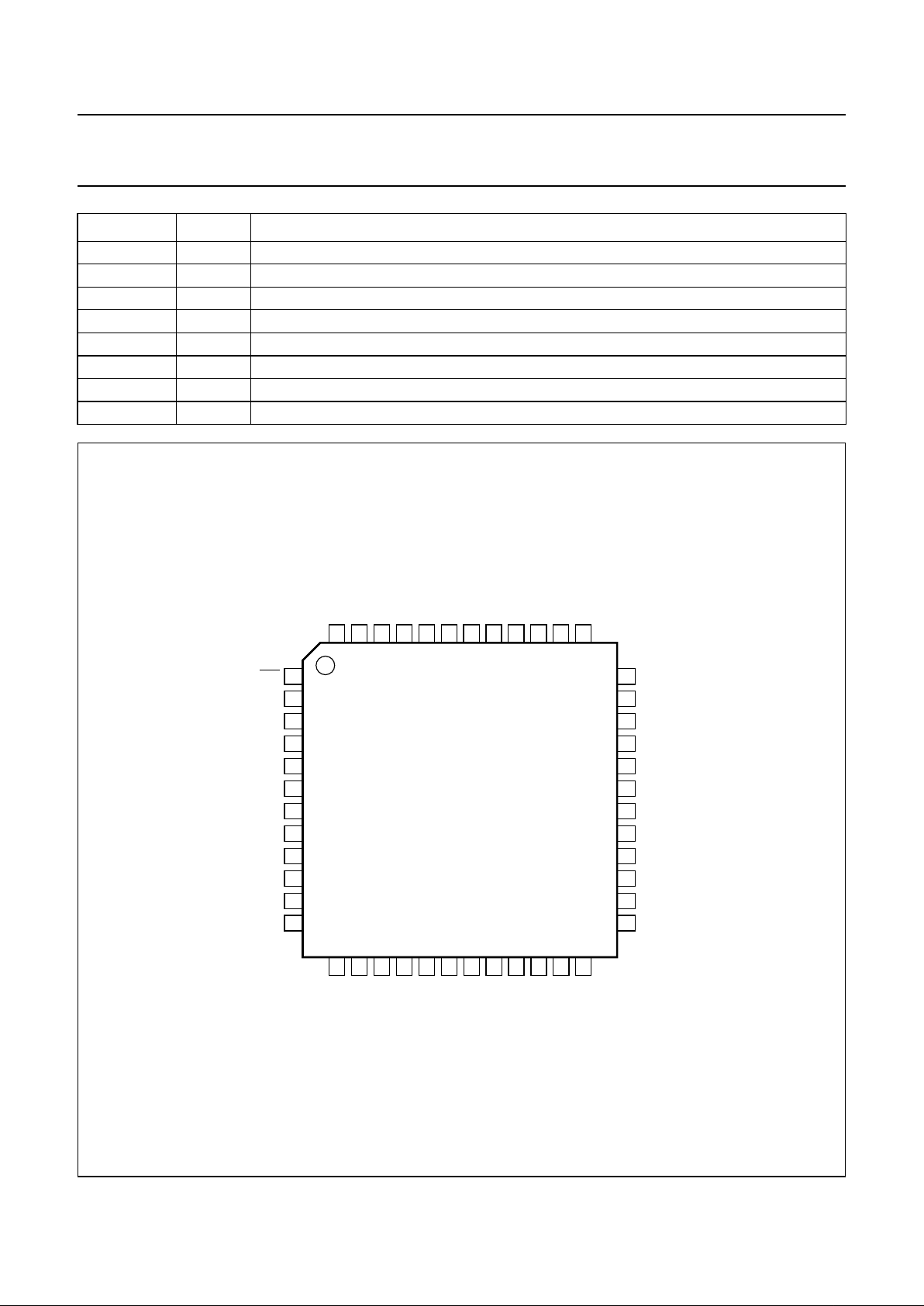

PINNING

SYMBOL PIN DESCRIPTION

ENL 1 loop mode enable input (active low)

GND 2 ground

CLOOP 3 clock output in loop mode (differential)

CLOOPQ 4 inverted clock output in loop mode (differential)

GND 5 ground

DLOOP 6 data output in loop mode (differential)

DLOOPQ 7 inverted data output in loop mode (differential)

GND 8 ground

REF19 9 reference frequency select input (see Table 2)

GND 10 ground

GND 11 ground

LOCK 12 phase lock detection output

i.c 13 internally connected (leave open)

GND 14 ground

CAPUPQ 15 external loop filter capacitor

CAPDOQ 16 external loop filter capacitor return

GND 17 ground

i.c. 18 internally connected (leave open)

i.c. 19 internally connected (leave open)

GND 20 ground

CREF 21 reference clock input (differential)

CREFQ 22 inverting reference clock input (differential)

GND 23 ground

REF39 24 reference frequency select input (see Table 2)

V

EE

25 negative supply voltage

GND 26 ground

V

EE

27 negative supply voltage

V

EE

28 negative supply voltage

GND 29 ground

SEL155 30 STM mode select input (see Table 1)

V

EE

31 negative supply voltage

GND 32 ground

DIN 33 data input (differential)

DINQ 34 inverting data input (differential)

GND 35 ground

i.c. 36 internally connected (leave open)

PC 37 negative power supply control signal output

GND 38 ground

LOS 39 loss-of-signal detection output

i.c. 40 internally connected (leave open)

1998 Feb 09 5

Philips Semiconductors Objective specification

SDH/SONET data and clock recovery unit

STM1/4 OC3/12

TZA3004HL

GND 41 ground

DOUT 42 data output in normal mode (differential)

DOUTQ 43 inverted data output in normal mode (differential)

GND 44 ground

COUT 45 clock output in normal mode (differential)

COUTQ 46 inverted clock output in normal mode (differential)

GND 47 ground

AREF 48 reference voltage input for controlling voltage swing on data and clock outputs

SYMBOL PIN DESCRIPTION

Fig.2 Pin configuration.

handbook, full pagewidth

1

2

3

4

5

6

7

8

9

10

11

36

35

34

33

32

31

30

29

28

27

26

13

14

15

16

17

18

19

20

21

22

23

48

47

46

45

44

43

42

41

40

39

38

12

24 37

25

TZA3004HL

MGK139

DCSQ

GND

DINQ

DIN

V

EE

SEL155

GND

n.c.

n.c.

GND

V

EE

GND

GND

COUTQ

COUT

GND

DOUTQ

DOUT

n.c.

LOS

GND

PC

AREF

GND

ENL

GND

CLOOP

CLOOPQ

GND

DLOOP

GND

REF19

GND

LOCK

DLOOPQ

GND

GND

CAPUPQ

CAPDOQ

GND

n.c.

n.c.

GND

CREFQ

GND

REF39

n.c.

CREF

i.c.

V

EE

V

EE

1998 Feb 09 6

Philips Semiconductors Objective specification

SDH/SONET data and clock recovery unit

STM1/4 OC3/12

TZA3004HL

FUNCTIONAL DESCRIPTION

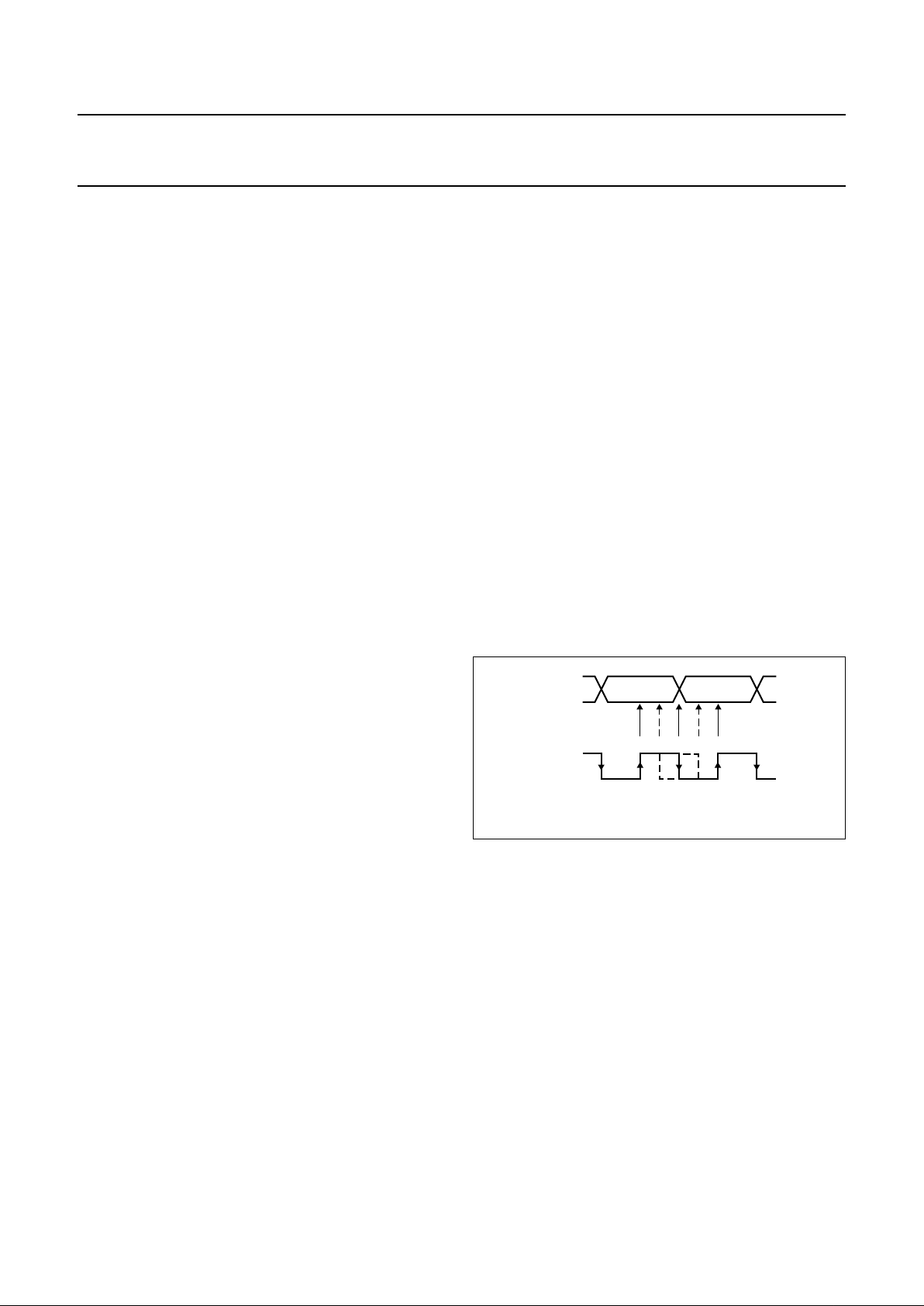

The TZA3004HL recovers data and clock signals from an

incoming high speed bitstream. The input signal on DIN,

DINQ is buffered and amplified by the input circuitry.

The signal is then fed to the Alexander phase detector

where the phase of the incoming data is compared with

that of the internal clock. If the signals are out of phase, the

phase detector generates (UP or DOWN) correction

pulses that shift the phase of the VCRO (Voltage

Controlled Ring Oscillator) output in discrete amounts, ∆ϕ,

until the clock and data signals are in phase.

The technique used is based on principles first proposed

by J.D.H. Alexander, hence the phase detector’s name.

The eye pattern of the incoming data is sampled at three

instants A, T and B (see Fig.3). When clock and data

signals are synchronized (locked), A is in the centre of the

data bit, T is in the vicinity of the next transition, and B is in

the centre of the bit following the transition. If the same

level is recorded at both A and B, a transition has not

occurred and no action is taken regardless of the value

at T. If A and B are different, however, a transition has

occurred and the phase detector uses the value at T to

determine whether the clock was too early or too late with

respect to the data transition. If A and T are the same, but

different from B, the clock was too early and needs to be

slowed down a little. The Alexander phase detector then

generates a DOWN pulse which stretches a single output

pulse from the ring oscillator by approximately 0.25% (or

4 ps in STM4 mode; 4 ps is 0.25% of the 1.608 ns bit

period). This forces the VCRO to run at a slightly lower

frequency for one bit period. The phase of the clock is thus

shifted fractionally with respect to the data.

If, on the other hand, B and T are the same but different

from A, the clock was too late and needs to be speeded up

for synchronization. The phase detector generates an UP

pulse forcing the VCRO to run at a slightly higher

frequency (+0.25%) for one bit period. The phase of the

clock is shifted with respect to the data (as above, but in

the opposite direction). Only the proportional path is active

while these phase adjustments are being made. Because

the instantaneous frequency of the VCRO can be changed

only in one of two discrete steps (±0.25%), this type of loop

is also known as a Bang/Bang PLL.

If not only the phase but also the frequency of the VCRO

is incorrect, a long train of UP or DOWN pulses will be

generated. This pulse train is integrated to generate a

control voltage that is used to shift the centre frequency of

the VCRO. Once the correct frequency has been

established, the phase will need to be adjusted for

synchronization. The proportional path adjusts the phase

of the clock signal, while the integrating path adjusts the

centre frequency.

The frequency window detector checks that the VCRO

frequency is within a 1000 ppm (parts per million) window

around the required frequency. It compares the output of

frequency divider 2 with the reference frequency at CREF,

CREFQ (19.44 MHz or 38.88 MHz as available; see

Table 2). If the VCRO frequency is found to be outside this

window, the frequency window detector disables the

Alexander phase detector and forces the VCRO output to

a frequency within the window. The phase detector then

starts acquiring lock again. Because of the loose coupling

(1000 ppm), the reference frequency doesn’t need to be

highly accurate or stable. Any crystal based oscillator that

generates a reasonably accurate frequency (e.g. 100ppm)

)will do.

Since sampling point A is always in the centre of the eye

pattern when the data and clock signals are in phase

(locked), the values recorded at this point are taken as the

retrieved data. The data and clock signals are available at

the CML output buffers, which are capable of driving a

50 Ω load.

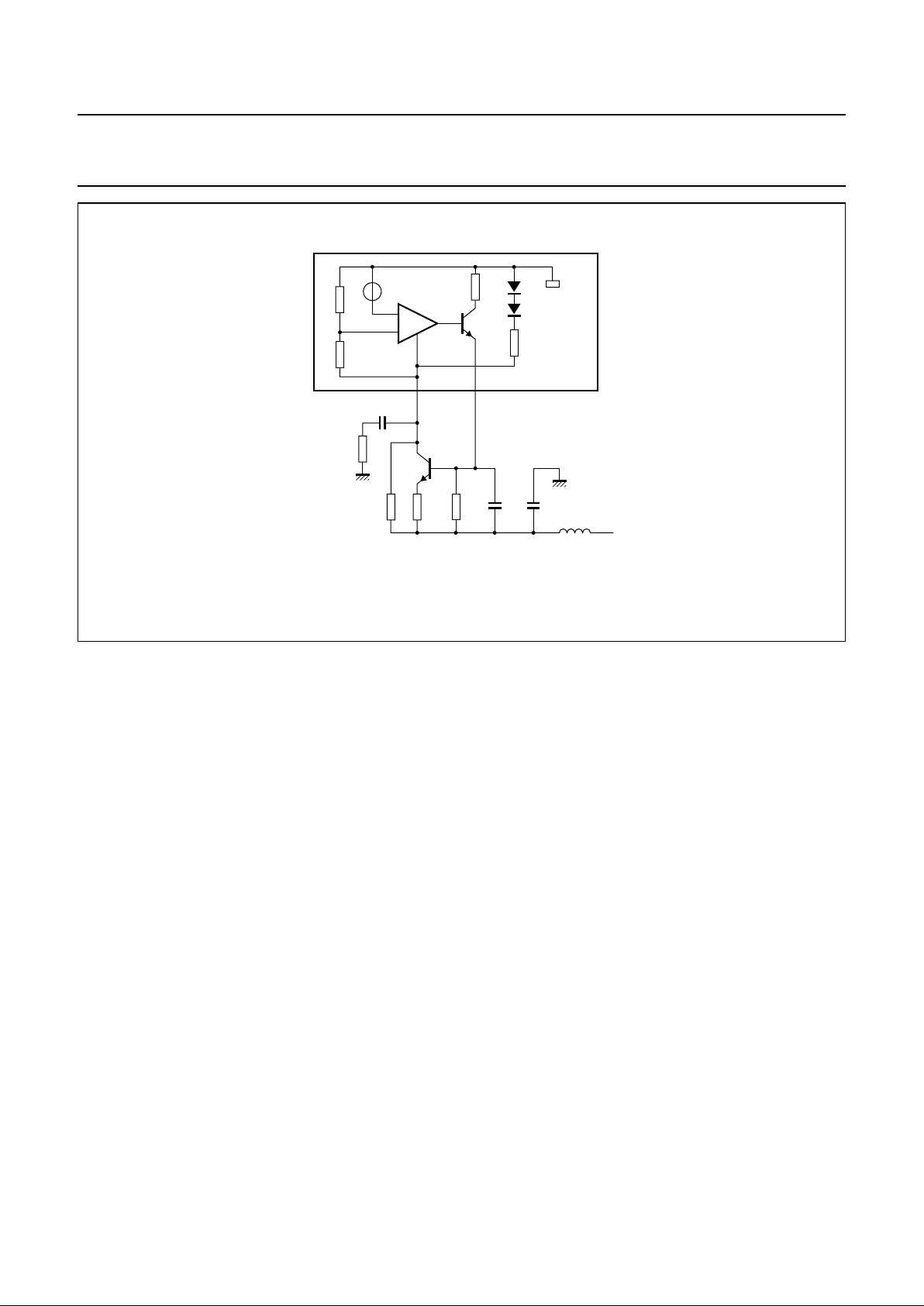

Power Control (PC)

The TZA3004HL contains an on-board voltage regulator.

An external power transistor is needed to deliver supply

current, I

EE

, to this circuit. The required external circuit is

straightforward, and can be built using a few components.

A suitable circuit is depicted in Fig.4. A different

configuration could be used, as long as the power supply

rejection ratio is greater than 60 dB for all frequencies.

The inductor is a (lossy) 1 µH RF-choke (EMI) with an

impedance greater than 50 Ω at frequencies higher than

2 MHz. Any transistor with a β > 100 and enough current

sink capability can be used.

The TZA3004HL can also be used with a -5V or -5.2V

supply voltage. The only adaption that has to be made to

the Power Control circuit is resistor R of 2Ω. This should

be 6.8Ω with a -5V supply and 8.2Ω with a -5.2V supply.

Fig.3 Data sampling.

handbook, halfpage

MGK143

DATADATA

CLOCK

ATB

1998 Feb 09 7

Philips Semiconductors Objective specification

SDH/SONET data and clock recovery unit

STM1/4 OC3/12

TZA3004HL

Fig.4 Schematic diagram of TZA3004HL power control loop.

handbook, full pagewidth

2 Ω

2 Ω

1 kΩ

1

kΩ

1 µF

1 µH

−4.5 V

β > 100

100 nF

3.3

nF

MGK141

BAND GAP

REFERENCE

POWER

CONTROL

V

EE

PC

Output amplitude reference (AREF)

The voltage swing at the CML compatible output stages

DOUT, DOUTQ; COUT, COUTQ; DLOOP, DLOOPQ and

CLOOP, CLOOPQ can be controlled by adjusting the

voltage at the AREF pin. An internal voltage divider of

500 Ω and16 kΩ between GND and VEE initially fixes this

level.

In most applications the outputs will be DC coupled to a

load, which can be as low as 50 Ω (±0.20%). The output

level regulation circuit will maintain a 200 mV

peak-to-peak single-ended swing across this load.

The voltage at AREF is half the single-ended peak-to-peak

value of the output signal (or −100 mV in this case).

No adjustments are necessary with DC coupling.

If the outputs are AC coupled, however, the voltage at

AREF is half the single-ended peak-to-peak value of the

output signal multiplied by a factor

where R

L

is the external load and Ro is the output

impedance of the TZA3004HL.

To maintain a 200 mV peak-to-peak single-ended swing

across a 50 Ω AC coupled load, the voltage at AREF must

be .

R

LRo

+

R

L

--------------------

100 mV– 50 Ω 100 Ω+()×

50 Ω

-------------------------------------------------------------------------

300 mV–=

This can be achieved by connecting a 7.3 kΩ resistor

between AREF and V

EE

.

The formulae for calculating the required voltage at AREF

and the external resistance needed between AREF and

V

EE

when the outputs are AC coupled are:

(1)

and:

(2)

where R1 = 500 Ω, R2 = 16 kΩ and V

EE

= −3.3 V. R

AREF

is connected between AREF and VEE.

V

AREF

RLRo+

R

L

--------------------

1

2

-- -

V

swing

×–=

R

AREF

R1

V

EE

V

AREF

---------------- -

1–

×

1

R1

R2

------- -

V

EE

V

AREF

---------------- -

1–

×

–

----------------------------------------------------------------

=

1998 Feb 09 8

Philips Semiconductors Objective specification

SDH/SONET data and clock recovery unit

STM1/4 OC3/12

TZA3004HL

Loop mode enable (ENL)

Loop mode is provided for system testing. Loop mode is

enabled by applying a voltage lower than 0.8 V (TTL LOW)

to the ENL pin. This selects loop mode outputs DLOOP,

DLOOPQ and CLOOP, CLOOPQ. If a voltage greater than

2.0 V (TTL HIGH) is applied to ENL, then DOUT, DOUTQ

and COUT, COUTQ are switched in while DLOOP,

DLOOPQ and CLOOP, CLOOPQ are disabled to minimize

power consumption. If ENL is connected to VEE(−3.3 V),

all outputs are enabled.

External capacitor for loop filter (CAPUPQ; CAPDOQ)

The loop filter is an integrator with a built in capacitance of

2 × 130 pF. An external 200 nF capacitance must be

connected between CAPUPQ and CAPDOQ to ensure

loop stability while the frequency window detector is

active.

Lock detection (LOCK)

The LOCK pin should be interpreted as an indication if the

reference clock (CREF) is present and if the acquisition aid

(frequency window detector) is working properly. The

LOCK pin is an open collector TTL output and should be

pulled up with a 10kΩ resistor to the positive supply. If the

VCO frequency is within a 1000 ppm window around the

desired frequency the LOCK pin will go HIGH. If no

reference clock is present, or the VCO is outside the 1000

ppm window, the LOCK pin will be LOW. The logic level of

LOCK does not indicate if the PLL is locked onto the

incoming data; this is indicated by the LOS signal.

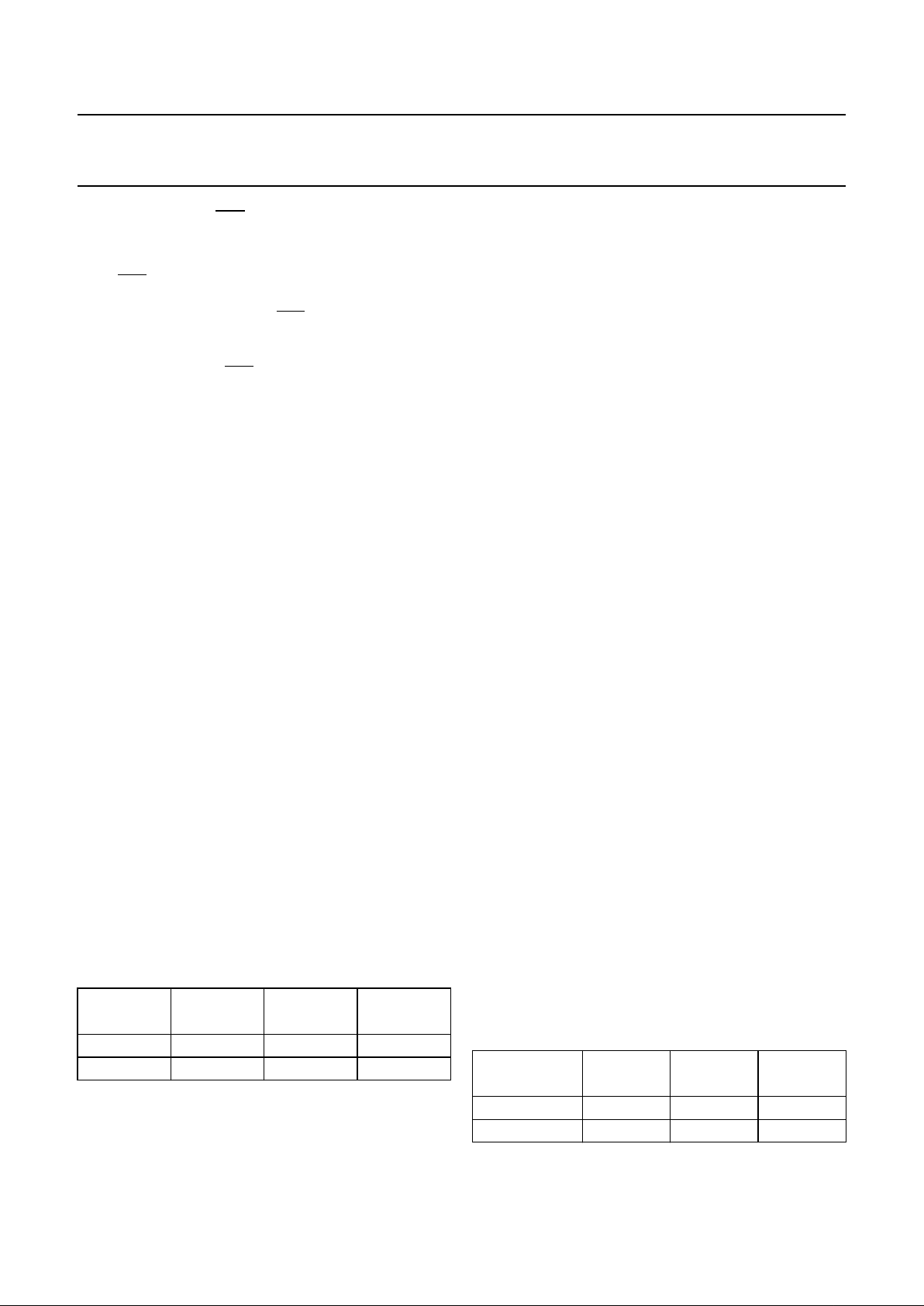

STM mode selection (SEL155)

SEL155 should be connected to V

EE

for STM1/OC3

(155.52 Mbits/s) operation. For STM4/OC12

(622.08 Mbits/s) systems, SEL155 should be connected to

GND. The connections to VEE and GND should have low

resistance and inductance. Short PCB tracks are

recommended.

Table 1 STM Mode Select

MODE

BIT RATE

Mbits/s

DIV # SEL155

STM1 155.52 16 V

EE

STM4 622.08 4 GND

Loss-of-signal detection (LOS)

The Loss of Signal (LOS) function is closely related to the

Alexander Phase Detector functionality. Refer to Fig.3 for

the meaning of A,B and T in this section.

In the functional description it is described that the phase

detector doesn’t take any action if the value at sample

points A and B is the same, because there hasn’t been any

transition. However, if the values at A and B are the same,

but different from T, this still means there hasn’t been any

transition, but somehow T got the wrong value. This is

probably due to noise or bad signal integrity, which will

lead to a Bit Error. Hence the occurrence of this particular

situation is an indication for Bit Errors. If too many of these

Bit Errors occur per time and the PLL is gradually losing

lock, the LOS alarm is asserted. The LOS assert level is

around a Bit Error Rate (BER) of 5⋅10

-2

and the de-assert

level is around BER of 1⋅10-3.

The LOS detection is BER related, but neither dependent

of datastream content, nor protocol. Therefore, a

SDH/SONET datastream is no prerequisite for a proper

LOS function. Since the LOS function of the TZA3004HL

is derived from digital signals, it is a good supplement to an

analog, amplitude based, LOS indication.

The LOS alarm is an open collector TTL compatible

output. A pull-up resistor should be connected to a positive

supply. LOS will be HIGH (TTL) if the data signal is absent

at DIN, DINQ or BER is > 5⋅10-2, otherwise it will be LOW

(BER < 1⋅10-3).

Reference frequency select (REF19, REF39)

A reference clock signal (either 19.44 MHz or 38.88 MHz,

whichever is available) must be connected to CREF and

CREFQ. Pins REF19 and REF39 are used to select the

appropriate output frequency at frequency divider 2. Since

the reference clock is only used as acquisition aid for the

PLL (Frequency Window Detector), the quality of the

reference clock is not important. There is no phase noise

specification imposed on the reference clock generator

and even frequency stability may be in the order of 100

ppm. In general most inexpensive crystal based oscillators

are suitable.

Table 2 Reference Frequency Select

FREQUENCY

MHz

DIV # REF19 REF39

38.88 64 V

EE

V

EE

19.44 128 GND V

EE

Loading...

Loading...