Philips TrimediaTM-1300 Datasheet

TriMedia TM-1300

Programmable Media Processor

Continuing a tradition of high-performance, low-cost

media processors, the TriMedia™ TM-1300 delivers up

to 66% more processing power1to multimedia applica-

tions at a lower unit cost. By combining a 166-MHz

CPU and a full complement of enhanced on-chip I/O

and coprocessing units,TM-1300 achieves up to 6.5 bil-

lion operations per second—ideal for applications

requiring real-time processing of video, audio, graphics,

and communications datastreams.

TM-1300 boosts performance through a faster clock

speed and a faster main memory interface than previ-

ous TriMedia processors. Datastream I/O is enhanced

with a new on-chip unit for handling audio output in

Sony/Philips digital format (SPDIF). Lower power con-

sumption and a smaller footprint contribute to making

the TM-1300 a more efficient and compact processing

solution for new multimedia designs.

TM-1300 is an ideal building block for applications requiring

simultaneous processing of several types of multimedia data-

streams. With ample computational power available to capture,

compress and decompress many video and audio data formats in

real time, TM-1300 is well suited for a broad range of video-

centric applications such as videoconferencing, video editing,

video-based security, surveillance, or industrial inspection systems,

and multifunctional devices such as digital TV sets and set-top

boxes. It also supports applications in a Java

™

virtual machine

environment.

With its comprehensive software development environment, the

TriMedia SDE, TM-1300 is comparable in ease of programmabil-

ity to general-purpose processors. The SDE enables multimedia

application development entirely in the C and C++ languages

improving time-to-market and lowering product development and

maintenance costs.

1

compared to TM-1000 processors

FEATURES

+

Processes audio, video, graphics and communications

datastreams on a single chip

+ Ideal for video-centric multimedia applications

+ Powerful, fine-grain parallel, 143- or 166-MHz VLIW CPU

achieving up to 6.5 BOPS

+ Versatile instruction set includes traditional microprocessor,

special multimedia SIMD, and IEEE floating-point operations

+ Comprehensive software development tools enable multi-

media application development entirely in the C/C++ programming languages

+ On-chip, independent, DMA-driven multimedia I/O and

coprocessing units offload the CPU

+ PCI/XIO host bus interface supports glueless interface to

PCI and eight-bit microcomputer peripherals, including

ROM/Flash, EEPROM, 68K, and x86 devices

+ 16- and 64-Mbit SDRAM support up to 143 MHz

+ On-chip DVD playback authentication/descrambling

+ TriMedia application libraries available from Philips and third-

party suppliers provide solutions for MPEG-2 decode, Dolby

Digital (AC-3)

®

decode, and more

TRIMEDIA TM-1300 ARCHITECTURE

On a single chip, the TM-1300 incorporates a powerful CPU and

peripherals to accelerate processing of audio, video, graphics, control,

and communications datastreams.

TriMedia TM-1300

System-on-a-chip

multimedia

engine

The TriMedia TM-1300 strikes a perfect balance between

cost and performance. A powerful C/C++-programmable

VLIW CPU coordinates on-chip activities. To reap the full

benefit of the CPU, independent, on-chip, bus-mastering

DMA peripheral units manage and format datastream I/O

and accelerate processing of multimedia algorithms. A

sophisticated memory hierarchy manages internal I/O and

streamlines access to external memory.The result—a single,

low-cost, programmable system-on-a-chip uniquely suited

for both standalone and hosted multimedia products.

PROGRAMMABLE VLIW CPU

A powerful DSP-like CPU delivers top performance through an ele-

gant implementation of a fine-grain parallel, very-long instruction

word (VLIW) architecture. Its five issue-slot instruction length enables

up to five simultaneous operations to be scheduled into a single VLIW

instruction. These operations can simultaneously target any five of the

CPU’s 27 pipelined functional units within one clock cycle. Most

common operations have their results available in one clock cycle;

more complex operations may have multicycle latencies.

Unique to the TriMedia VLIW implementation, parallelism is opti-

mized at compile time by an innovative compilation system. No spe-

cialized scheduling hardware is required to parallelize code during exe-

cution. Hardware saved by eliminating complex scheduling logic

reduces cost and allows the integration of multimedia-specific features

that enhance the power of the CPU.

The TM-1300 CPU implements a 32-bit linear address space and 128

fully general-purpose 32-bit registers. Registers are not separated into

banks enabling any operation to use any register for any operand.

High-powered, DSP-like, C/C++-callable special operations—In

addition to traditional microprocessor operations and a full comple-

ment of 32-bit, IEEE-compliant, floating point operations, the TM-

1300 instruction set includes special multimedia and DSP operations

(ops) to accelerate the performance of SIMD (single instruction, mul-

tiple data) computations common in multimedia applications. These

special ops combine multiple simple operations into a single VLIW

instruction that can implement up to 12 traditional microprocessor

operations in a single clock cycle. When incorporated into application

source code, special ops dramatically improve performance and

increase the efficiency of the TM-1300 parallel architecture.

Special multimedia ops are invoked with familiar function-call syntax

consistent with the C/C++ programming languages. They are auto-

matically scheduled to take full advantage of the TriMedia processor’s

highly parallel VLIW implementation. As with all other operations

generated by the TriMedia VLIW compilation system, the scheduler

takes care of register allocation, operation packing, and flow analysis.

ON-CHIP I/O AND COPROCESSING UNITS

Video input—The video input (VI) unit reads digital video datas-

treams from an off-chip source into main memory. It accepts signals

from any CCIR656-compliant device that outputs eight-bit parallel,

4:2:2 YUV time-multiplexed video data, such as a digital video cam-

era, digital video decoder, or devices connected through ECL-level

converters to the standard D1 parallel interface. After input, YUV

data is demultiplexed, subsampled as needed, and written to SDRAM.

The VI unit can also be programmed to perform on-the-fly 2X hori-

zontal resolution subsampling enabling high-resolution images (720

pixels/line) to be converted to 360 pixels/line without loading the

CPU. When low resolution video is desirable, subsampling during

data capture reduces initial storage and bus bandwidth requirements.

The VI unit can also receive raw data and unidirectional messages

from another TM-1300 video out port.

Video output—The video out (VO) unit outputs a digital YUV

datastream to off-chip video subsystems such as a digital video

encoder chip, digital video recorder, or other CCIR656-compatible

device. The output signal is generated by gathering bytes from the

separate Y, U, and V planes stored in SDRAM.

While generating the multiplexed stream, the VO unit can perform

programmed processing tasks, including horizontal 2X upscaling to

convert from CIF/SIF to CCIR 601 resolution. For simultaneous dis-

play of graphics and live video, the VO unit can perform 129-level

alpha blending to generate sophisticated graphics overlays of arbitrary

size and position within the output image. Chroma keying, genlock

frame synchronization, programmable YUV output clipping are also

supported. The VO unit can also be used to pass raw data and unidi-

rectional messages between TriMedia processors.

The VO unit can either supply or receive video clock and/or synchro-

nizing signals from the external interface. Clock and timing registers

can be precisely controlled through programmable registers. Program-

mable interrupts and dual buffers facilitate continuous data streaming

by allowing the CPU to set up a buffer while another is being emptied

by the VO unit.

Audio input and output—The audio input (AI) and audio output

(AO) units provide all signals needed to read and write digital audio

datastreams to/from most high-quality, low-cost serial audio oversam-

pling A/D and D/A converters and codecs. Both units connect to off-

chip stereo converters through flexible bit-serial interfaces.

The AI and AO units are highly programmable providing tremendous

flexibility in handling custom datastreams, adapting to custom proto-

cols, and upgrading to future audio standards. Driven by TM-1300,

the programmable audio sampling clock system supports a variety of

sample rates with fine-grain resolution enabling audio and video syn-

chronization in even the most complex multimedia applications.

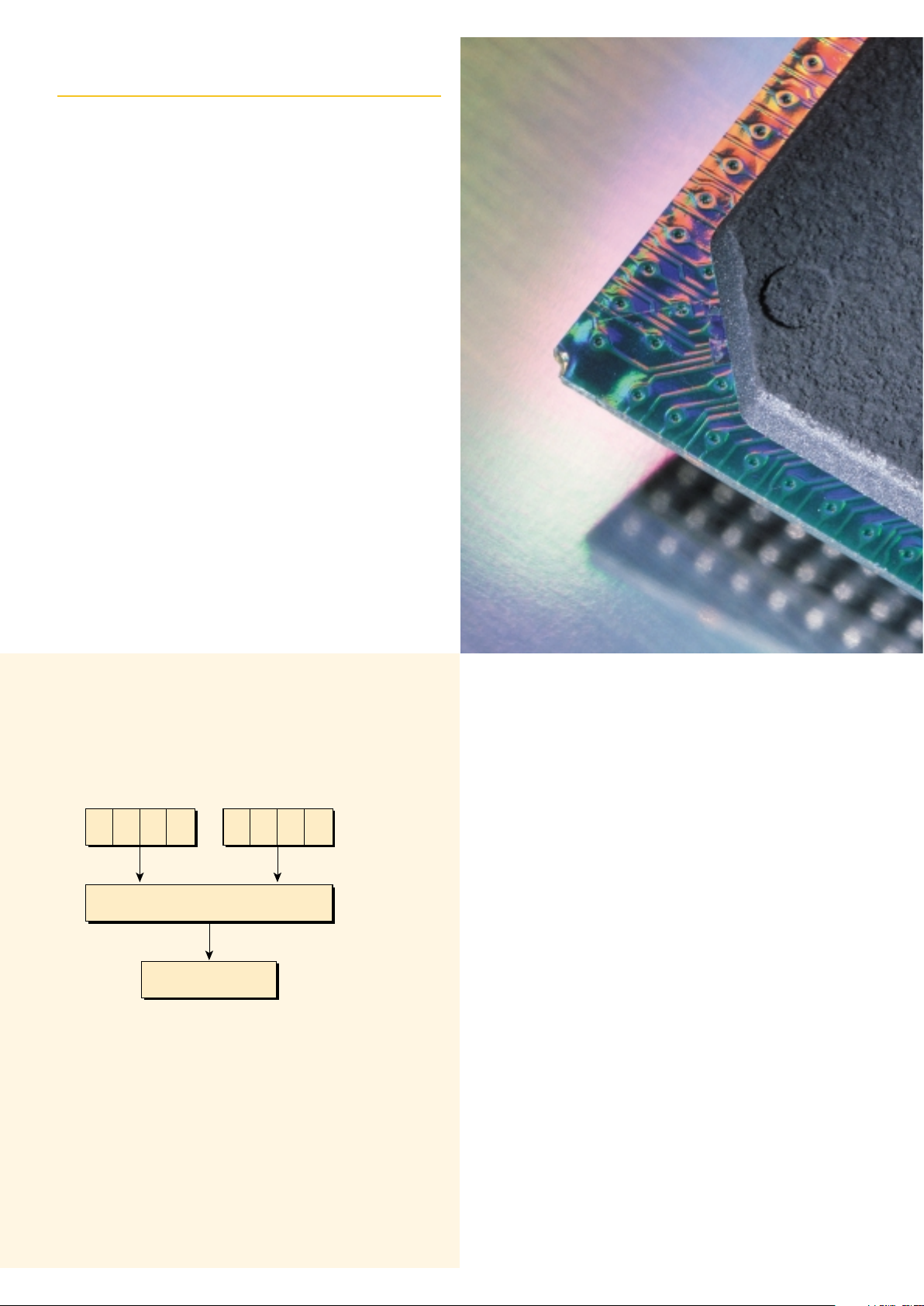

SPECIAL MULTIMEDIA OPERATIONS

The ume8uu operation, commonly used for motion estimation in

video compression, implements 11 simple operations in one

TriMedia special op.

RESULT

SOURCE REGISTER 1 SOURCE REGISTER 2

A B C D

|A-E| + |B-F| + |C-G| + |D-H|

E F G H

31 0

31 0

31 0

UME8UU: SUM OF ABSOLUTE VALUES

OF UNSIGNED 8-BIT DIFFERENCES

DSPALU

FUNCTIONAL

UNIT

DESTINATION

REGISTER

Loading...

Loading...