Philips TriMediaTM-1100 Datasheet

On a single chip, a TriMedia™TM-1100 delivers

real-time processing of audio, video, graphics,

and communications datastreams. With its low-

cost 133-MHz CPU and a full complement of

on-chip I/O and coprocessing peripheral units,

the TM-1100 media processor delivers up to

5.3 BOPS to new multimedia products. 100%

pin compatibility with the TM-1000 processor

ensures that developers can take immediate

advantage of up to 33% more processing power

in their existing TM-1000 designs.

Comparable in programmability to a general-

purpose processor, the TriMedia TM-1100

architecture enables development of multi-

media applications entirely in the C and C++

programming languages. Programmability

improves time-to-market, lowers development

costs, and extends product life through

software upgradability.

MULTIMEDIA APPLICATIONS

The TM-1100 is an ideal building block for any multimedia appli-

cation that processes multiple multimedia and communications

datastreams. It is well suited for creating a range of consumer and

professional products such as videophones, videoconferencing and

video editing systems, security systems, DVD encode/decode

devices, and digital television appliances.

SINGLE-CHIP MULTIMEDIA ENGINE

Powered by a low-cost, 133-MHz, C-programmable CPU, the

TriMedia TM-1100 strikes a perfect compromise between cost and

performance. To streamline data throughput, TM-1100 incorporates

independent on-chip DMA-driven peripheral units that manage

datastream I/O and formatting and accelerate processing of key

multimedia algorithms. To reap the full benefit of the CPU and pro-

cessing units, TM-1100’s sophisticated memory hierarchy manages

internal I/O and streamlines access to external memory. The result —

a single, low-cost programmable chip that powers standalone and

PC-hosted multimedia products.

FEATURES

+ Processes audio, video, graphics and communications

datastreams on a single chip

+ Powerful, fine-grain parallel, 133-MHz VLIW CPU with

versatile instruction set includes special multimedia and

DSP operations

+ Pin compatibility with TM-1000 delivers up to 33%

more performance to TriMedia TM-1000 designs

+ Multiple, independent, DMA-driven multimedia I/O and

coprocessing units format data and offload the CPU

+ Enhanced video out functionality includes 7-bit alpha

blending, full chroma keying, genlock capability, and

programmable YUV color clipping

+ PCI/XIO bus interface supports glueless interface to a

mix of PCI and 8-bit microcomputer peripheral chips,

such as ROM/Flash, EEPROM, 68K, and x86 devices

+ Robust software development tools enable multimedia

application development entirely in C/C++

+ DVD playback authentication/descrambling functions

for PC and standalone applications

+ 16- and 64-Mbit SDRAM support up to 133-MHz

Programmable Media Processor

TriMedia TM-1100

PROGRAMMABLE VLIW CPU

The TM-1100 delivers top performance through an elegant imple-

mentation of a very-long instruction word (VLIW) architecture.

Key to the TriMedia processor’s VLIW implementation, parallelism is

optimized at compile time by the TriMedia compilation system. No

specialized scheduling hardware is required to parallelize code during

execution. Hardware saved by eliminating complex scheduling logic

reduces cost and allows the integration of multimedia features that

enhance the power of the CPU in multimedia applications.

The TM-1100 processor’s powerful DSP-like, 32-bit CPU achieves

fine-grain parallelism by simultaneously targeting five of its 27

pipelined functional units within one clock cycle. Most common

operations have their results available in one clock cycle; more

complex operations have multicycle latencies.

Functional units can access 128 fully general-purpose, 32-bit registers

during execution. Since registers are not separated into banks, any

operation can use any register for any operand. Both big and little

endian byte ordering are supported.

The TriMedia TM-1100 CPU also provides special support for

instruction and data breakpoints, useful in debugging and program

development.

POWERFUL, DSP-LIKE, C-CALLABLE MULTIMEDIA OPS

In addition to traditional microprocessor operations and a full

complement of 32-bit, IEEE-compliant, floating point operations,

the TM-1100 instruction set includes multimedia and DSP operations

that accelerate the performance of multimedia applications. Such mul-

timedia operations can replace up to 11 traditional microprocessor

operations. When incorporated into application source code, they

dramatically improve performance and amplify the efficiency of the

TM-1100’s parallel architecture.

Multimedia operations are invoked with familiar function-call syntax

consistent with the C programming language. They are automatically

scheduled to take full advantage of the TriMedia processor’s highly

parallel VLIW implementation. As with all other operations generated

by the TriMedia VLIW compilation system, the scheduler takes care of

register allocation, operation packing, and flow analysis.

The TM-1100 processor enhances the multimedia operation set

available for the TM-1000 with 6 additional operations that improve

efficiency of MPEG-2 9-bit precise decoding, support video

de-interlacing (median filtering), and more.

MEMORY SYSTEM OVERVIEW

To reap the full benefit of the TM-1100 processor’s CPU and pro-

cessing units, its memory hierarchy must read and write data (and

instructions) fast enough to keep these units busy. Thus to meet the

A single-chip

multimedia

engine

Powered by a low-cost,

133-MHz, C-programmable CPU,

the TriMedia TM-1100 strikes a

perfect compromise between

cost and performance.

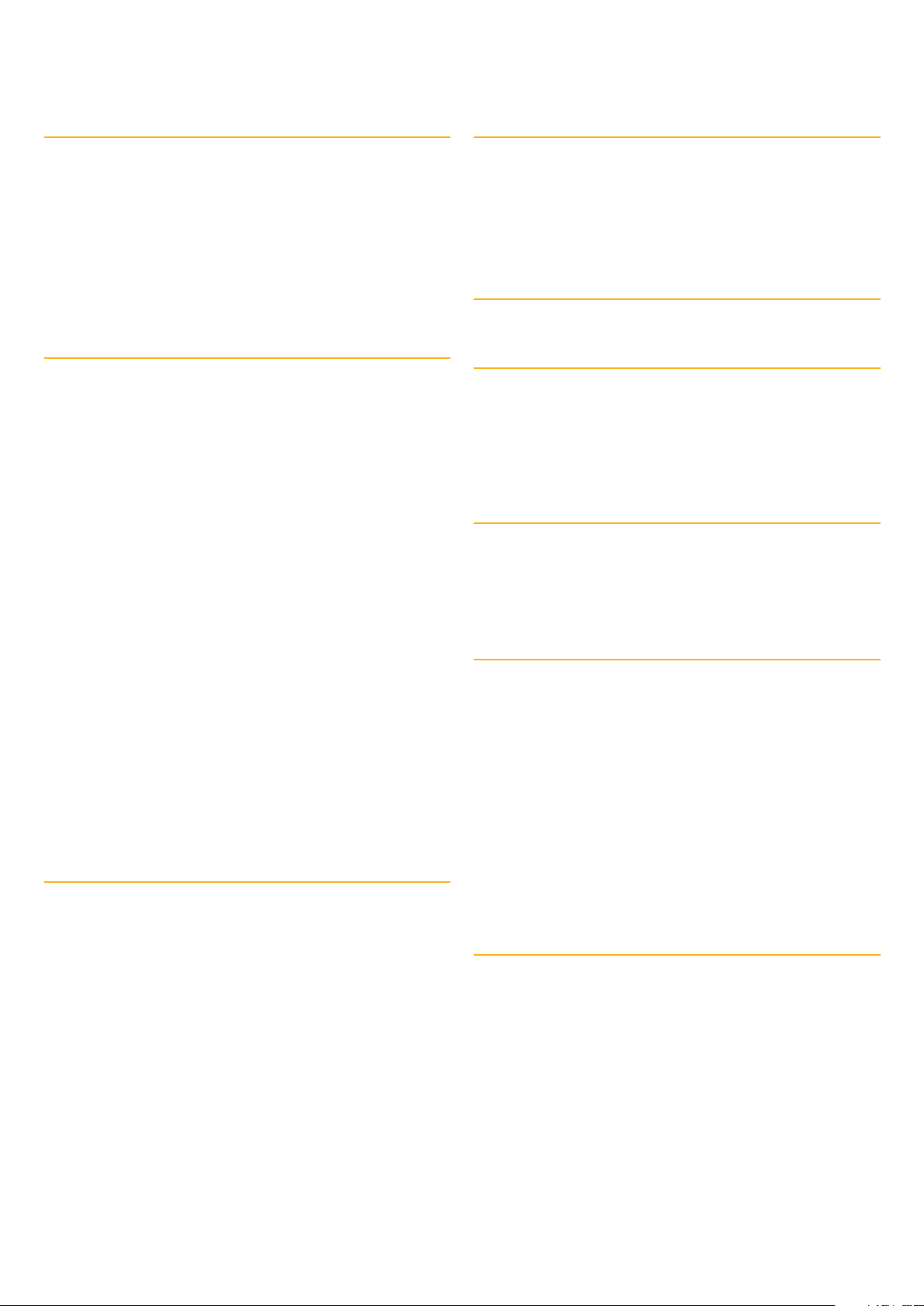

SDRAM

MAIN MEMORY

INTERFACE

I2C INTERFACE

AUDIO OUT

AUDIO IN

SYNCHRONOUS

SERIAL INTERFACE

TIMERS

ENHANCED VIDEO OUT

VLIW CPU

INSTR.

CACHE

DATA

CACHE

IMAGE

COPROCESSOR

PCI/XIO INTERFACE

VIDEO IN

VLD COPROCESSOR

TO

PCI/XIO

BUS

INTERNAL BUS (DATA HIGHWAY)

TM-1100 ARCHITECTURE

On a single chip, the TM-1100 incorporates a powerful CPU and

peripherals to accelerate processing of audio, video, graphics, and

communications data.

TM-1100 Specifications

PHYSICAL

Process C75: CMOS 0.35 micron; 5-layer metal

Packaging TE_QFP

Pins total 240

I/O pins 3.3 V with 5 V tolerance

Power supply 3.3 V +/- 5%

dissipation 6W (max)

consumption 1808 mA 5.97 W

management dynamic standby less than

990 mW

CENTRAL PROCESSING UNIT

Clock Speed 133 MHz

Instruction Length variable (2 to 23 bytes); compressed

Instruction Set arithmetic and logical ops, load/store ops.,

special multimedia and DSP ops.,

IEEE-compliant floating point ops.

Issue Slots 5

Functional Units 27, pipelined

integer and floating-point arithmetic

units, data-parallel DSP-like units

name quantity latency recovery

constant 5 1 1

integer ALU 5 1 1

memory load/store 2 3 1

shift 2 1 1

DSPALU 2 2 1

DSP multiply 2 3 1

branch 3 3 1

float ALU 2 3 1

integer/float mul 2 3 1

float compare 1 1 1

float sqrt./divide 1 17 16

Registers 128 (32-bit width)

Special Multimedia/ total 32 ops

DSP Operations

MEMORY SYSTEM

Speed 66/80/100/133 MHz

CPU/Memory programmable; 1:1, 5:4, 4:3, 3:2, and 2:1

Speed Ratios

Memory Size 512 KB to 64 MB (up to four ranks)

Supported Types 16-Mbit SDRAM (x4, x8, x16);

SGRAM (x32); 64-Mbit SDRAM (x32)

Width 32-bit bus

Max. Bandwidth 532 MB/sec (at 133 MHz)

Interface glueless up to 4 16-Mbit or 2 64-Mbit

chips at 133 MHz; more chips with slower

clock and/or external buffers

Signal Levels 3.3 V LVTTL

CACHES

Access data 8-, 16-, 32-bit word

instruction 64 bytes

Associativity 8-way set-associative with LRU replacement

Block Size 64 bytes

Size data 16 KB

instruction 32 KB

INTERNAL DATA HIGHWAY

Protocol 64-byte block-transfer

separate 32-bit data and 32-bit address buses

PCI INTERFACE

Speed 33 MHz

Bus Width 32-bit

Address Space 32 bits (4 GB)

Voltage drive and receive at 3.3V or 5V

Standard Compliance PCI Local Bus Specification 2.1

VIDEO IN

Supported Signals CCIR 601/656 8-bit video up to 19 Mpix/sec

raw 8-10-bit data (messages) up to 38 MB/sec

Image Sizes all sizes, subject to sample rate

Functions programmable on-the-fly 2X horizontal

resolution subsampling

ENHANCED VIDEO OUT

Image Sizes flexible, including CCIR601;

maximum 4K x 4K pixels (subject to

80 MB/sec data rate)

Input Formats YUV 4:2:2, YUV 4:2:0

Output Formats CCIR601/656 8-bit video, PAL or NTSC

Clock Rates programmable (4-80 MHz), typically 27

MB/sec (13.5 Mpixels/sec for NTSC, PAL)

Transfer Speeds 80 MB/sec in data-streaming and

message-passing modes; 40 Mpix/sec in

YUV 4:2:2 mode

Functions full 129-level alpha blending, genlock

mode, frame synchronization, chroma key,

programmable YUV color clipping

AUDIO IN / AUDIO OUT

Number of Channels 2 input; 8 output

Sample Size 8- or 16-bit samples per channel

Sample Rates 1 Hz to 100 KHz

programmable with 0.001 Hz resolution

Data Formats 8-bit mono and stereo; 16-bit mono and

stereo PC standard memory data format

External Interface 4 pins each: 1 programmable clock output,

3 flexible serial input (AI) or output (AO)

interface

Clock Source internal or external

Native Protocol I

2

S and other serial 3-wire protocols

Loading...

Loading...