Page 1

INTEGRATED CIRCUITS

DATA SH EET

TDA9605H

Audio processor with head amplifier

for VHS hi-fi

Product specification

File under Integrated Circuits, IC02

1999 Apr 14

Page 2

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 ORDERING INFORMATION

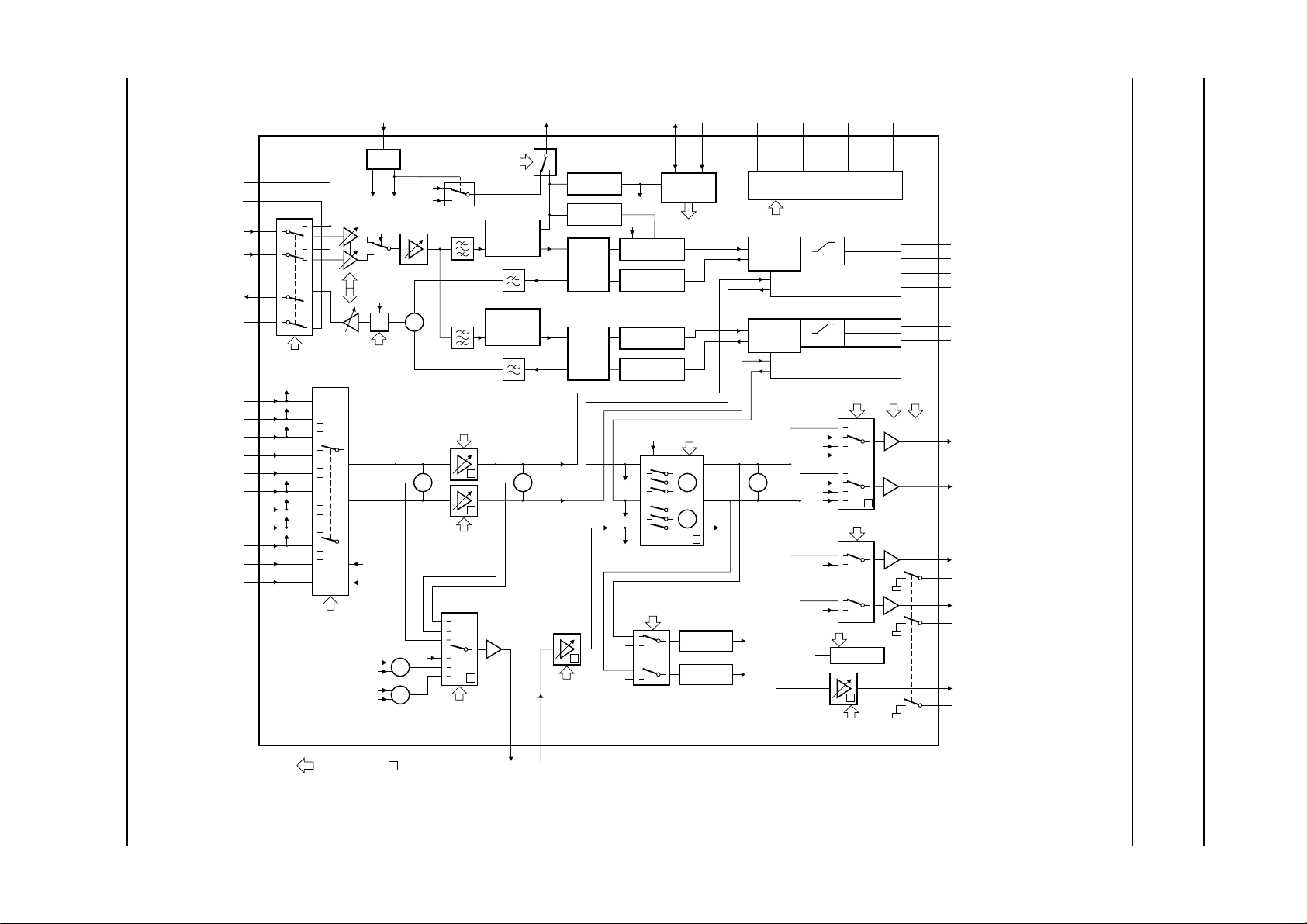

4 BLOCK DIAGRAM

5 PINNING

6 FUNCTIONAL DESCRIPTION

6.1 Record-mute mode or head identification

selection

6.2 Hi-fi audio output level

6.3 Reference current

6.4 Head amplifier

6.4.1 Playback mode

6.4.2 Record-mute mode

6.4.3 Record mode

6.4.4 Head amplifier power supply and ground

6.5 Automatic calibration

6.6 Power muting

6.7 Envelope output

6.8 RF converter output

6.9 Audio dubbing

6.9.1 Output mix

6.9.2 Input mix

7I

7.1 Addresses and data bytes

7.2 Valid transmissions to and from the TDA9605H

7.3 Overview of the TDA9605H I2C-bus control

7.4 Control byte at subaddress 00H

7.4.1 Audio FM mode

7.4.2 Playback mode

7.4.3 Record mode

7.4.4 System standard selection

7.4.5 Head amplifier playback amplification

7.4.6 Head amplifier record current

7.5 Select byte at subaddress 01H

7.5.1 Decoder output select

7.5.2 Head amplifier record current range select

7.5.3 Normal input level

7.6 Input byte at subaddress 02H

7.6.1 Input select

7.6.2 Normal select

7.7 Output byte at subaddress 03H

7.7.1 Line output amplification

7.7.2 Output select

7.7.3 Envelope output select

7.7.4 Line output select

7.7.5 Decoder output select

7.7.6 RF converter mute

2

C-BUS PROTOCOL

7.8 Volume bytes at subaddresses 04H, 05H

and 06H

7.8.1 Left and right volume control

7.9 Power byte at subaddress 07H

7.9.1 Calibration start

7.9.2 DC output voltage selection

7.9.3 Test mode

7.9.4 Power-on reset

7.9.5 Head amplifier disable

7.9.6 Power muting

7.9.7 Standby select

7.10 Read byte

7.10.1 Calibration ready

7.10.2 Auto-normal selection

7.10.3 Calibration error

7.10.4 Power-on reset

8 LIMITING VALUES

9 THERMAL CHARACTERISTICS

10 GENERAL CHARACTERISTICS

11 RECORD-MUTE MODE CHARACTERISTICS

12 RECORD MODE CHARACTERISTICS

13 PLAYBACK MODE CHARACTERISTICS

14 APPLICATION AND TEST INFORMATION

14.1 RM and HID control signals

14.2 Reference current resistor

14.3 Setting line output level

14.4 Test modes

15 INTERNAL CIRCUITRY

16 PACKAGE OUTLINE

17 SOLDERING

17.1 Introduction to soldering surface mount

packages

17.2 Reflow soldering

17.3 Wave soldering

17.4 Manual soldering

17.5 Suitability of surface mount IC packages for

wave and reflow soldering methods

18 DEFINITIONS

19 LIFE SUPPORT APPLICATIONS

20 PURCHASE OF PHILIPS I2C COMPONENTS

1999 Apr 14 2

Page 3

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

1 FEATURES

• All functions controlled via the serial 2-wire I2C-bus

• Integrated standby modes for low power consumption

• Audio FM head amplifier:

– Programmable recording current

– Programmable playback amplification

– Fast record-mute mode control input.

• Hi-fi signal processing:

– Adjustment free

– High performance

– Low distortion switching noise suppressor

– NTSC and PAL (SECAM) system.

• Linear audio input:

– Programmable (playback) level.

• 5 stereo inputs and additional mono Second Audio

Program (SAP) input

• 2 stereo outputs (line and decoder) with independent

output select function

• RF converter output with overload-protection AGC

• Integrated output power muting

• Audio level meter output

• Extensive input and output select function

• Full support of video recorder feature modes.

2 GENERAL DESCRIPTION

The TDA9605H is a single-chip device in a small package

that contains all the required functions, including the head

amplifier, to realize the audio FM hi-fi stereo system in a

VHS video recorder (see Fig.1). The device is adjustment

free by use of an integrated auto-calibration system.

Extensive signal select functions are offered to support

pay-TV decoding and video recorder feature modes.

The high performance and functionality of the TDA9605H

comprises world-wide system and application

requirements for NTSC, PAL, SECAM and multi-standard

video recorders from basic up to high-end models.

3 ORDERING INFORMATION

TYPE

NUMBER

TDA9605H QFP44 plastic quad flat package; 44 leads (lead length 1.3 mm);

1999 Apr 14 3

NAME DESCRIPTION VERSION

body 10 × 10 × 1.75 mm

PACKAGE

SOT307-2

Page 4

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

n

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Apr 14 4

V

CCH

GNDH

PBIN1

PBIN2

RECOUT

HMSW

SAP

TUNL

TUNR

CINL

CINR

EXT1L

EXT1R

EXT2L

EXT2R

AUXL

AUXR

40

39

37

35

36

38

playback. +

record-mute,

recording

1

2

3

4

5

6

7

8

9

10

11

SAP

TUL

TUR

E1L

E1R

E2L

E2R

HEAD AMPLIFIER

input select

I2C-bus

control

RMHID

41 44 42 43

DCL

HID

current

RM

M

HID

DCR

HF AGC

1.3 or 1.4 MHz

+

1.7 or 1.8 MHz

RM

playback head

amplification,

record head

carrier ratio select,

record-mute

FM (DE-)MODULATOR

volume left

M

M

volume right

M

normal select

TUL

TUR

E2L

E2R

N

dub

M

+

+

= mute

+

SAP

ENVOUT

envelope

output

select

+ playback

LEVEL

DETECTOR

HF LIMITER

HF LFP

LEVEL

DETECTOR

HF LIMITER

HF LFP

+ ++

I/O CONTROL

normal

input

level

21 22

LINOUT LININ

HI-FI

DETECTOR

DROPOUT

CANCELING

PLL

CCO

(1.3 or

1.4 MHz)

PLL

CCO

(1.7 or

1.8 MHz)

M

dbook, full pagewidth

SDA SCL

I2C-BUS

INTERFACE

AUTN

HID

NOISE

SUPPRESSION

AUDIO

CLIPPER

NOISE

SUPPRESSION

AUDIO

CLIPPER

output selectAUTN

L

R

+

N

envelope output

select + record

L

R

PEAK HOLD

PEAK HOLD

TDA9605H

V

CC

34 27 29 28

standby select

5th ORDER

AUDIO LPF

COMPRESSOR

5th ORDER

AUDIO LPF

COMPRESSOR

dub

M

DCL

DCR

GND

SUPPLY

NOISE REDUCTION

W + FM

EXPANDER

W + FM

EXPANDER

TUL

E1L

SAP

TUR

E1R

SAP

E2L

E2R

mute

V

CC

RFCAGC

V

ref

DETECTOR

RECTIFIER

CCA

DETECTOR

RECTIFIER

CCA

decoder

select

M

line select

AUTO-MUTE

M

RF converter

mute

12

I

ref

+1 dB 12 V

26

25

24

23

30

31

32

33

19

20

16

15

17

18

13

14

MGR834

DETL

DCL

EMPHL

DCFBL

DETR

DCR

EMPHR

DCFBR

DECL

DECR

LINEL

MUTEL

LINER

MUTER

RFCOUT

MUTEC

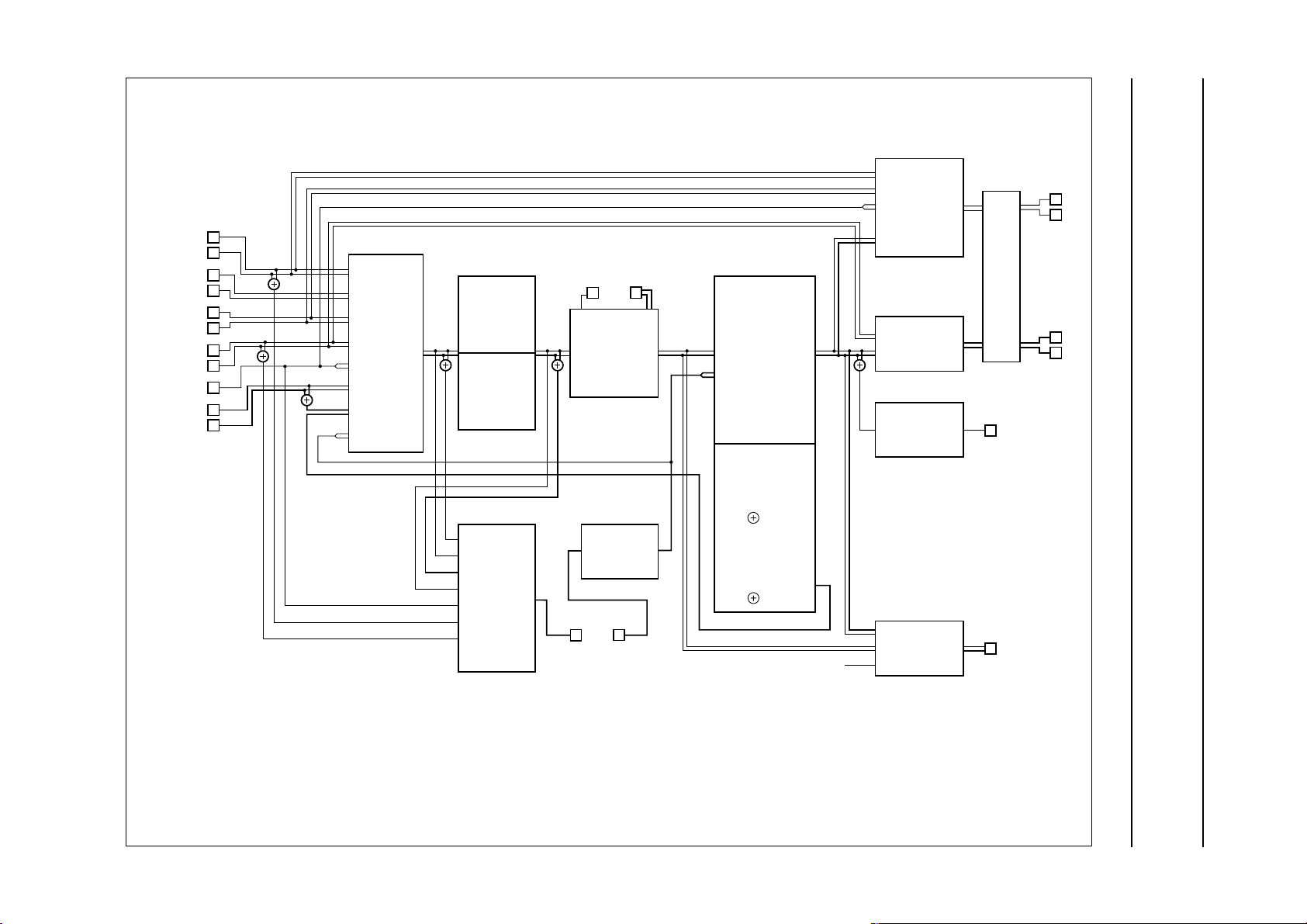

4 BLOCK DIAGRAM

Audio processor with head amplifier for VHS hi-fi TDA9605H

Philips Semiconductors Product specification

Fig.1 Block diagram.

Page 5

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

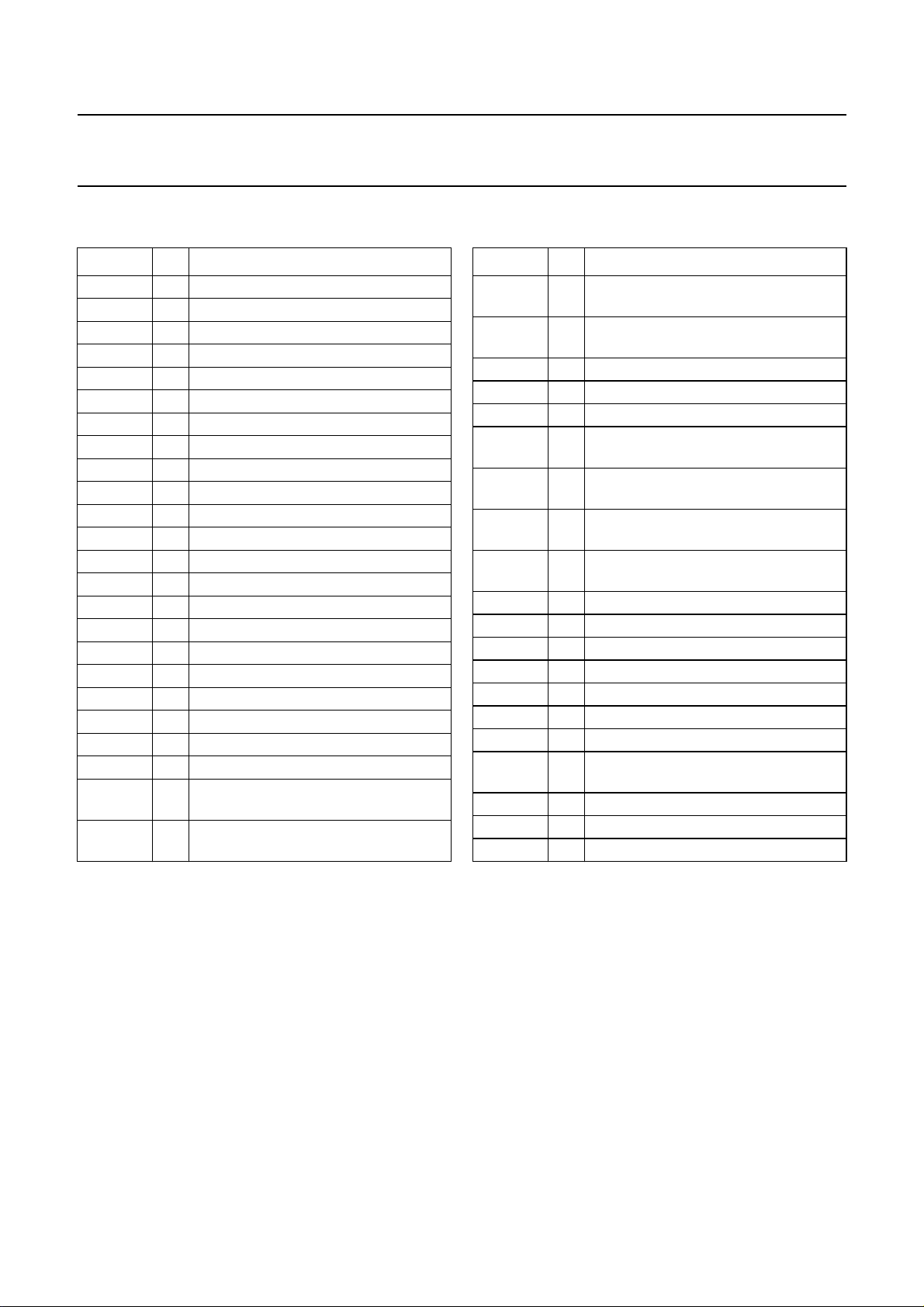

5 PINNING

SYMBOL PIN DESCRIPTION

SAP 1 tuner input mono

TUNL 2 tuner input left

TUNR 3 tuner input right

CINL 4 CINCH input left

CINR 5 CINCH input right

EXT1L 6 external 1 input left

EXT1R 7 external 1 input right

EXT2L 8 external 2 input left

EXT2R 9 external 2 input right

AUXL 10 auxiliary input left

AUXR 11 auxiliary input right

RFCAGC 12 RF converter AGC timing connection

RFCOUT 13 RF converter output

MUTEC 14 mute for RF converter output

MUTEL 15 mute for line output left

LINEL 16 line output left

LINER 17 line output right

MUTER 18 mute for line output right

DECL 19 decoder output left

DECR 20 decoder output right

LINOUT 21 linear audio output

LININ 22 linear audio input

DCFBL 23 DC feedback noise reduction

connection left

EMPHL 24 emphasis noise reduction connection

left

SYMBOL PIN DESCRIPTION

DCL 25 DC decoupling noise reduction

connection left

DETL 26 detector noise reduction connection

left

GND 27 ground

I

ref

V

ref

28 reference standard current connection

29 reference voltage connection

DETR 30 detector noise reduction connection

right

DCR 31 DC decoupling noise reduction

connection right

EMPHR 32 emphasis noise reduction connection

right

DCFBR 33 DC feedback noise reduction

connection right

V

CC

34 power supply

PBIN2 35 head 2 playback input

RECOUT 36 recording current output

PBIN1 37 head 1 playback input

HMSW 38 head amplifier mode switch connection

GNDH 39 ground of head amplifier

V

CCH

40 power supply of head amplifier

RMHID 41 record-mute mode or head

identification input

SDA 42 I2C-bus data input/output

SCL 43 I

2

C-bus clock input

ENVOUT 44 HF or AF envelope output

1999 Apr 14 5

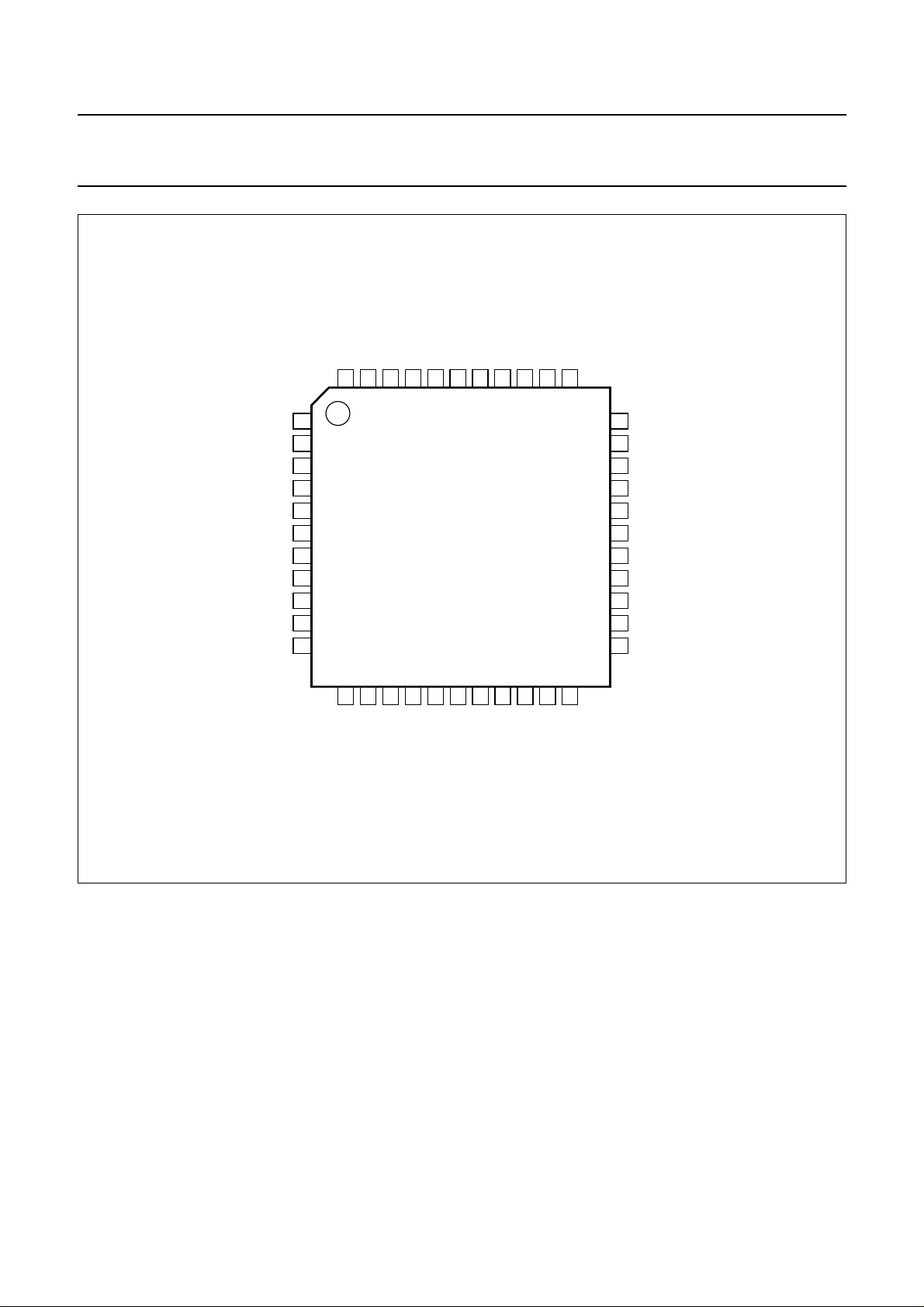

Page 6

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

handbook, full pagewidth

SAP

TUNL

TUNR

CINL

CINR

EXT1L

EXT1R

EXT2L

EXT2R

AUXL

AUXR

SDA

ENVOUT

SCL

44

43

42

1

2

3

4

5

6

7

8

9

10

11

12

13

14

MUTEC

RFCAGC

RFCOUT

CCH

RMHID

V

41

40

TDA9605H

15

16

LINEL

MUTEL

GNDH

39

17

LINER

PBIN1

HMSW

38

37

18

19

DECL

MUTER

RECOUT

36

20

DECR

CC

V

PBIN2

35

34

21

22

LININ

LINOUT

33

DCFBR

EMPHR

32

31

DCR

30

DETR

V

29

28

I

GND

27

DETL

26

DCL

25

24

EMPHL

DCFBL

23

MGR835

ref

ref

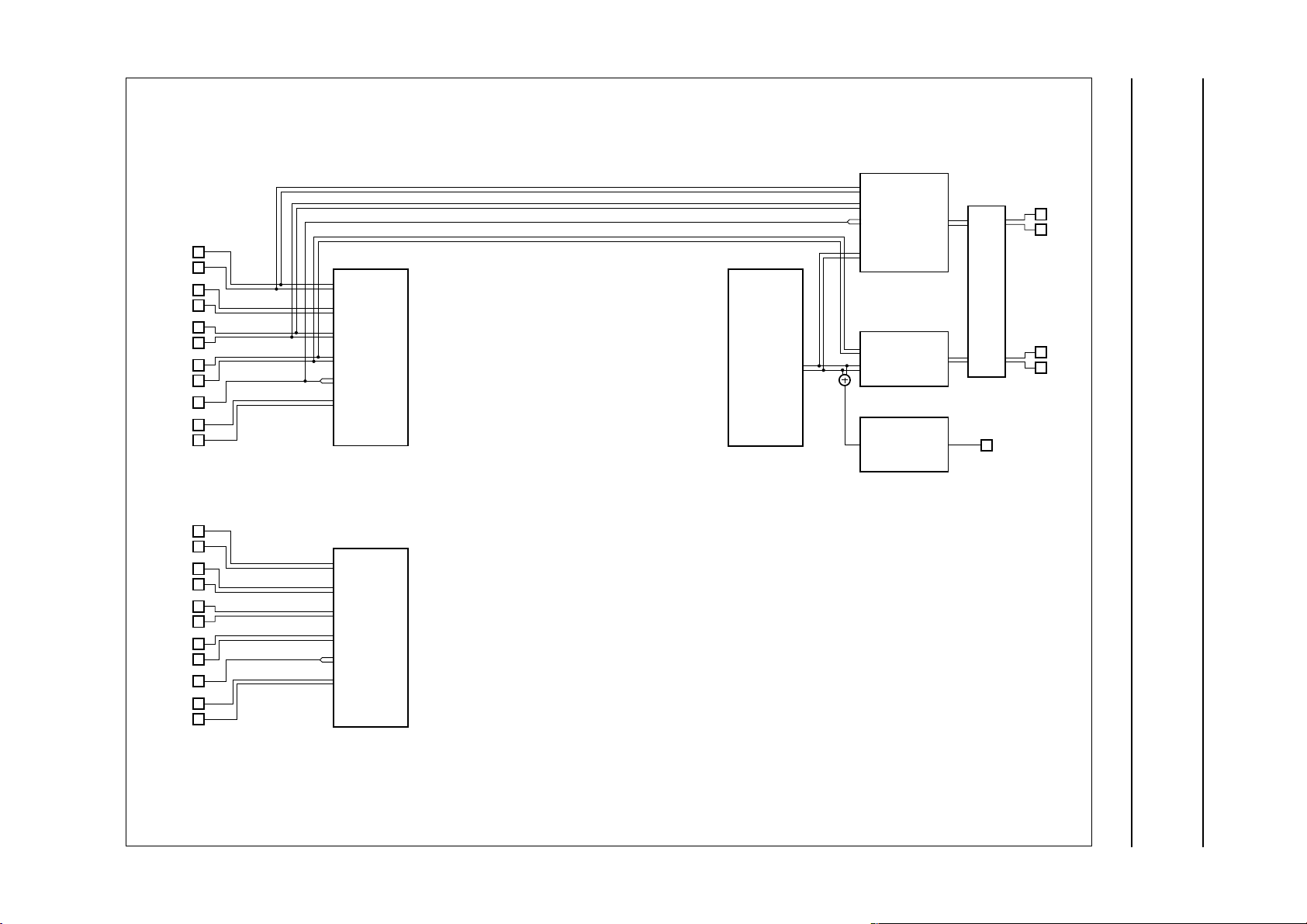

Fig.2 Pin configuration.

6 FUNCTIONAL DESCRIPTION

Input and output selections for the various modes are given in the following diagrams:

• Standard operating mode (see Fig.3)

• Dub-mix mode (see Fig.4)

• Standby mode: active or passive (see Fig.5).

1999 Apr 14 6

Page 7

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

o

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Apr 14 7

TUNL

TUNR

CINL

CINR

EXT1L

EXT1R

EXT2L

EXT2R

SAP

AUXL

AUXR

(1)

input select

TUNER

CINCH

EXT1

EXT2

SAP

AUX

DUB MIX

NORMAL

volume left

MUTE

(−47 to 0 dB;

0 to +15 dB)

MUTE

(−47 to 0 dB;

0 to +15 dB)

volume right

RECOUT

ok, full pagewidth

tape

PBIN1

PBIN2

HI-FI

AUDIO FM

PROCESSING

output select

MUTE

LEFT

RIGHT

STEREO

NORMAL

NORMAL LEFT

NORMAL RIGHT

NORMAL STEREO

decoder select

TUNER

EXT1

SAP

MUTE

OUTPUT SELECT

line select

EXT2

OUTPUT SELECT

RF converter AGC

0 dB AGC

MUTE

line output

amplification

0 dB

+1 dB

RFCOUT

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

DECL

DECR

LINEL

LINER

(1) For dub-mix mode signal selections see Fig.4.

normal input levelnormal select

INPUT SELECT

INPUT LEFT

VOLUME

VOLUME LEFT

SAP

TUNER

EXT2

MUTE

LINOUT

MUTE

(0 to +14 dB)

LININ

linear audio

processing

Fig.3 Input and output selections for standard operating mode.

envelope select

OUTPUT SELECT

STEREO

HF ENVELOPEHF envelope

MGR836

ENVOUT

Page 8

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

k

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Apr 14 8

, full pagewidth

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

TUNL

TUNR

CINL

CINR

EXT1L

EXT1R

EXT2L

EXT2R

SAP

AUXL

AUXR

input select

DUB MIX

volume aux output select

MUTE

(−47 to 0 dB;

0 to +15 dB)

MUTE

(−47 to 0 dB;

0 to +15 dB)

volume hi-fi

INPUT SELECT

INPUT LEFT

VOLUME

VOLUME LEFT

SAP

TUNER

EXT2

MUTE

RECOUT

PROCESSING

normal input levelnormal select

LINOUT

linear audio

processing

(record)

tape

PBIN1

PBIN2

HI-FI

AUDIO FM

(playback)

MUTE

(0 to +14 dB)

LININ

MUTE

LEFT

RIGHT

STEREO

NORMAL

NORMAL

NORMAL

NORMAL

MUTE

LEFT

RIGHT

LEFT RIGHT

MUTE

LEFT

RIGHT

LEFT RIGHT

decoder select

TUNER

EXT1

SAP

MUTE

OUTPUT SELECT

line select

EXT2

OUTPUT SELECT

RF converter AGC

0 dB AGC

MUTE

envelope select

OUTPUT SELECT

STEREO

HF ENVELOPEHF envelope

MGR837

line output

amplification

0 dB

+1 dB

RFCOUT

ENVOUT

DECL

DECR

LINEL

LINER

Dub-mix mode: IS2 =1, IS1 = 0 and IS0 = 1.

Input mixing of the hi-fi (playback) signal with the auxiliary, used for linear audio dubbing recording.

Selections generally used in combination with dub-mix mode are shown in heavy line type.

Fig.4 Input and output selections for dub-mix mode.

Page 9

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Apr 14 9

TUNL

TUNR

CINL

CINR

EXT1L

EXT1R

EXT2L

EXT2R

SAP

AUXL

AUXR

input select

MUTE

handbook, full pagewidth

output select

MUTE

decoder select

TUNER

EXT1

SAP

MUTE

OUTPUT SELECT

line select

EXT2

OUTPUT SELECT

RF converter AGC

MUTE

MGR838

line output

amplification

0 dB

+1 dB

a. Active standby mode (bit STBA = 1, bit STBP = 0); over 80% power reduction.

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

DECL

DECR

LINEL

LINER

RFCOUT

TUNL

TUNR

CINL

CINR

EXT1L

EXT1R

EXT2L

EXT2R

SAP

AUXL

AUXR

input select

MUTE

b. Passive standby mode (bit STBP = 1); over 90% power reduction.

Fig.5 Input and output selections for standby modes.

Page 10

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

6.1 Record-mute mode or head identification

selection

Pin RMHID allows input of two independent digital control

signals for selecting the record-mute or head identification

modes which are voltage coded. The RM control signal is

selected via a 10 kΩ resistor and the HID control signal is

selected via a 18 kΩ resistor. This set-up enables the two

signals within the TDA9605H to be separated. The RM

control signal is only in use during the record mode

(bit AFM = 1); during the playback mode (bit AFM = 0) the

RM signal is ignored. Pin RMHID should be connected to

ground when the RM control signal is not used.

The use of the RM control signal is optional since the same

function is available via the I

2

C-bus control in the

record-mute mode. However, accurate timing of recording

start and stop may sometimes be difficult to realize via the

I2C-bus control. In this event the RM control signal can be

used instead. There is also the possibility to use the

record-mute mode control line of the video head amplifier.

6.2 Hi-fi audio output level

When the application circuit is used in accordance with the

application diagram, the standard FM deviation of 50 kHz

equals a 1 kHz audio signal of −8 dBV line output level

(bit LOH = 0). A different standard audio level can be

selected by changing the external filter components of the

noise reduction on pins EMPHL and EMPHR

(see Section 14.3). The standard audio level changes

proportionally to the impedance of the external

de-emphasis filter.

6.3 Reference current

The external resistor connected to pin I

defines the

ref

internal reference currents and determines the

temperature stability of circuits adjusted by the

auto-calibration function.

6.4 Head amplifier

6.4.1 PLAYBACK MODE

The playback mode is selected by setting bit AFM = 0.

During the playback mode the input circuit on pins PBIN2

and PBIN1 is enabled (see Fig.6). Pin RECOUT is

disabled and pin HMSW shows a low impedance to

ground, so realizing an AC ground for the head circuit via

the external capacitor connected between these pins.

The head identification (HID) signal on pin RMHID selects

between the head signals on pins PBIN2 or PBIN1. Head

selection is defined as shown in Table 1.

The state of the RM control signal on pin RMHID is don’t

care in the playback mode.

2

I

C-bus control bits HAC2, HAC1 and HAC0 offer a wide

selection of playback amplification to fit different head and

head transformer specifications. The advised setting of the

playback amplification realizes a level of 24 mV (RMS) for

each carrier signal after the head amplifier to obtain a

17 dB overhead compared to the auto-normal level (hi-fi

detection). However, performance is not critical and a

different setting can be used if desired.

The carrier level can be measured using the HF envelope

output voltage on pin ENVOUT (bit EOS = 1). During

standard operating mode the HF envelope signal is

derived from the left channel carrier amplitude

(1.3 or 1.4 MHz carrier) but the special test 10 of the test

mode also enables the HF envelope output of the right

channel carrier amplitude (1.7 or 1.8 MHz carrier).

The advised carrier playback level of 24 mV (RMS) equals

an HF envelope voltage of 3.3 V.

The head amplifier output signal can be monitored directly

by using test 8 of the test mode. Pin ENVOUT functions as

the test output showing 6 dB attenuation compared to the

actual head amplifier output level (see Section 14.4).

Table 1 Selection of the head signal

HID

SIGNAL

LEVEL ON PIN RMHID

LOW lower than 0.6 V or

between 2.65 and 3.8 V

HIGH between 1.0 and 2.35 V

or higher than 4.3 V

6.4.2 R

ECORD-MUTE MODE

SELECTION OF

HEAD SIGNAL

pin PBIN2

(head 2)

pin PBIN1

(head 1)

The record-mute mode is selected by setting bit AFM = 1

and either setting bits DOC, SHH and DETH to logic 0 or

switching the RM control signal to HIGH-level.

During the record-mute mode no recording current is

present on pin RECOUT (see Fig.6). The head amplifier

status actually equals the playback mode, however, the

second amplifier stage is disabled to minimize power

consumption.

The RM control signal on pin RMHID enables fast

switching between the record and record-mute modes

(see Table 2). If the I2C-bus control is set to the record

mode, the use of record-mute mode control via pin RM

allows for accurate timing of recording start and stop,

independent of the I2C-bus control (see Section 6.1).

1999 Apr 14 10

Page 11

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

Table 2 Selection of recording modes

RM

SIGNAL

LEVEL ON

PIN RMHID

RECORD MODE

LOW lower than 2.35 V record or record-mute

mode as defined by

2

I

C-bus control

HIGH higher than 2.65 V record-mute mode

6.4.3 R

ECORD MODE

The record mode is selected by setting bit AFM = 1 and

setting bits DOC, SHH and DETH from logic 001 to 111

and switching the RM control signal to LOW-level.

During the record mode actual recording is activated and

the recording current is output on pin RECOUT

(see Fig.6). Pins PBIN2 and PBIN1 form a connection to

the 5 V head amplifier supply voltage (V

). Pin HMSW

CCH

is internally connected to pin RECOUT and the external

capacitor has no function in this mode.

The desired carrier mix ratio is set via I2C-bus control

bits DOC, SHH and DETH. A wide selection of recording

currents is available to fit different head and head

transformer specifications and are set via bits HAC2,

HAC1, HAC0 and range bit HRL. The setting of the carrier

mix ratio does not change the selected recording current.

The DC bias current on pin RECOUT is changed

proportional to the selected recording current for

optimizing the performance and minimizing the power

consumption for each recording current selected.

A Boucherot damping circuit is connected between

pin HMSW and ground to prevent head current resonance

peaking. A capacitor of 10 nF and a resistor of 470 Ω are

specified in Fig.14, but the component values are not

critical.

6.4.4 H

EAD AMPLIFIER POWER SUPPLY AND GROUND

The head amplifier is supplied via a separate 5 V supply

(pin V

) and ground (pin GNDH).

CCH

A capacitor of 100 nF should be placed close to the device

between pins V

and GNDH for proper decoupling of

CCH

the power supply.

The head amplifier ground (pin GNDH) should be

connected to the main ground (pin GND).

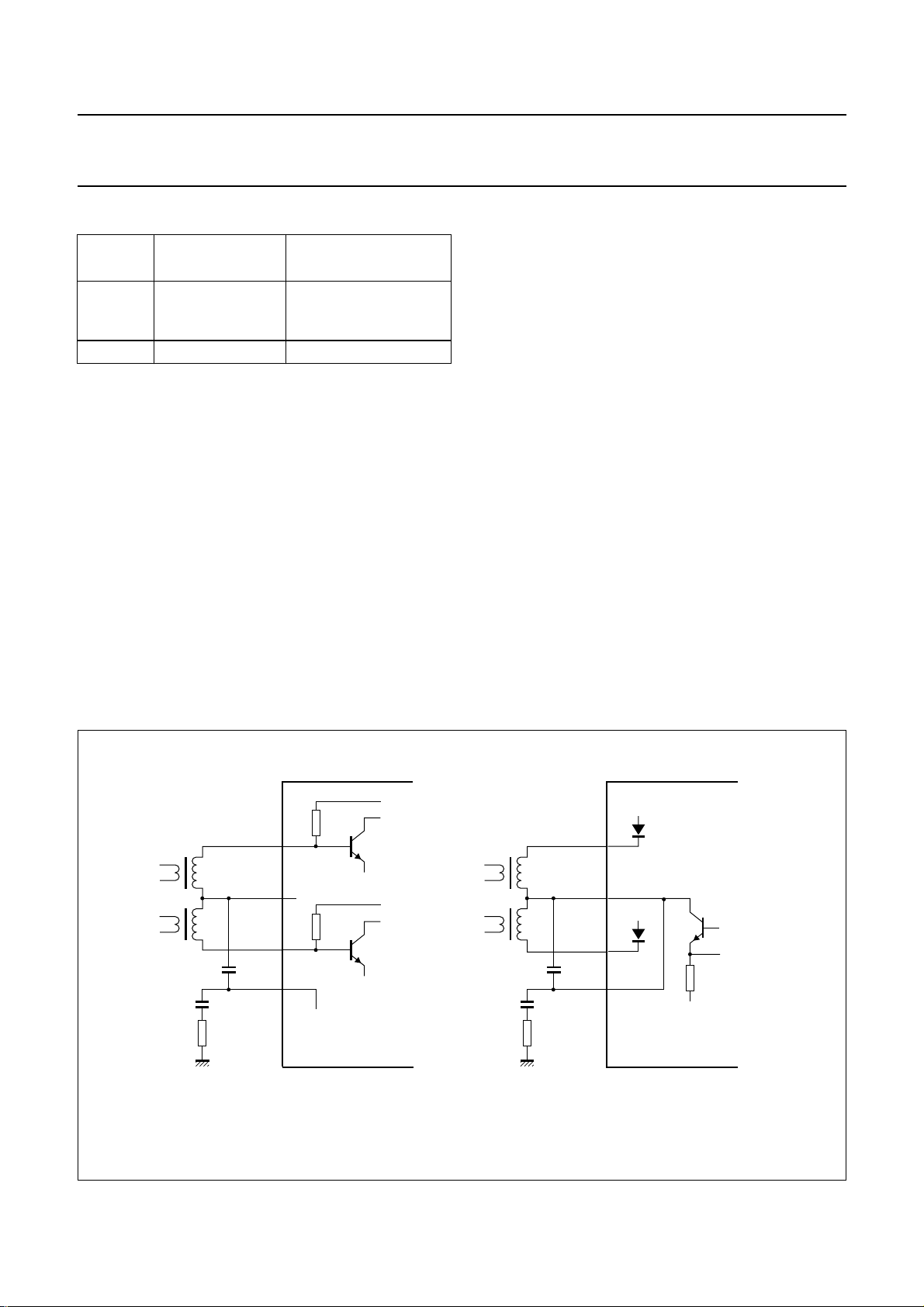

handbook, full pagewidth

35

36

37

38

35 kΩ

GNDH

35 kΩ

GNDH

GNDH

TDA9605H

PBIN2

AH2

RECOUT

AH1

PBIN1

HMSW

a. Playback mode and record-mute mode. b. Record mode.

Fig.6 Simplified circuit diagrams of the head amplifier modes.

1999 Apr 14 11

AH2

AH1

PBIN2

RECOUT

PBIN1

HMSW

35

36

37

38

V

V

CCH

CCH

5 Ω

GNDH

TDA9605H

MGR841

Page 12

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

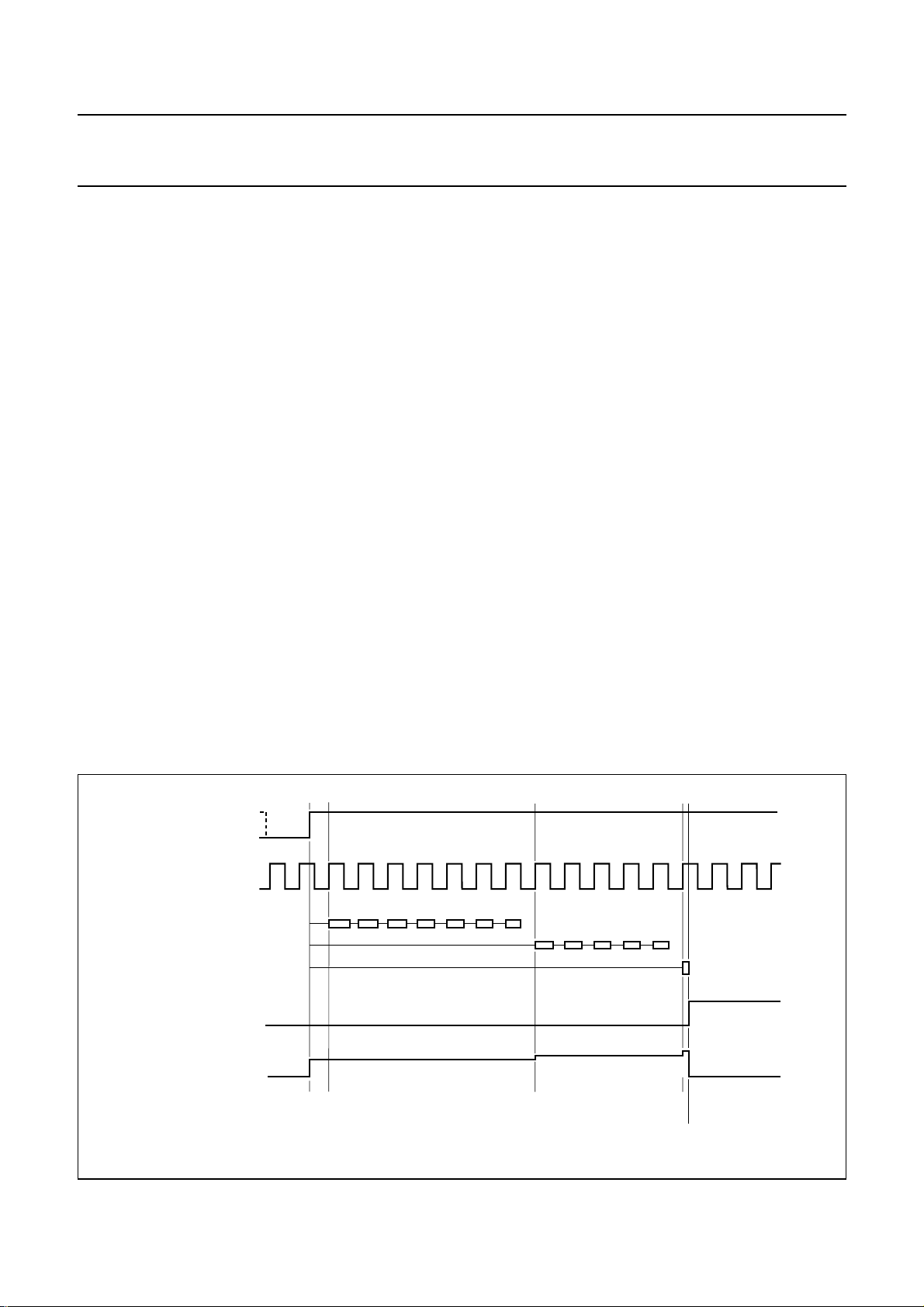

6.5 Automatic calibration

The integrated auto-calibration system is activated by

means of bit CALS of the power byte (see Fig.7).

The auto-calibration system ensures hi-fi processing is

well in accordance with the VHS hi-fi system standard by

an automated adjustment of carrier frequencies,

band-pass filters and noise reduction filters. Calibration is

only needed after start-up of the video recorder.

The calibration settings remain stable as long as the

supply voltage (VCC) is present.

Auto-calibration is only executed in the record-mute mode

or record mode and no standby mode or test mode should

be selected, i.e. auto-calibration requires the setting of

bit AFM = 1, bit STBP = 0, bit STBA = 0 and bit TEST = 0.

Auto-calibration is started after setting bit CALS = 1.

Calibration is performed fully automatically, using the HID

control signal as a time reference. Audio signals are not

disturbed during the calibration process.

Calibration of the oscillator frequencies is performed by

measuring the number of oscillator cycles within one

period when the HID control signal is at HIGH-level and

comparing this result with an internal value stored in the

Read Only Memory (ROM). Four different ROM values are

available for NTSC or PAL (SECAM) system calibration of

both the left and right channel carrier.

In case of NTSC a special routine is active for the

calibration of the right channel carrier which results in a

frequency difference between the left and right channel

carrier near to 401.2 kHz. This value effectively reduces

the crosstalk from hi-fi carriers to video colour signal as

present during Extended Play (EP) tape speed. NTSC

calibration uses a standard HID control signal of 29.97 Hz

(pulse width =16.683 ms) where PAL calibration uses a

standard HID control signal of 25 Hz (pulse

width = 20 ms). After auto-calibration the maximum

frequency error is ±5 kHz assuming a time error of

maximum of 5 µs when the HID control signal is at

HIGH-level. Jitter on the HID control signal should not

exceed 1 µs to realize EP optimization within ±2 kHz for

NTSC. In general, the crystal based HID control signal

available in the video recorder can be used without

modification.

When the calibration of the oscillators is completed the

band-pass filters are calibrated. The integrated weighting

and FM de-emphasis filters of the noise reduction are

calibrated at the same time.

The total auto-calibration time needed is maximum

17 cycles of the HID control signal. Completion of the

calibration is signalled by bit CALR =1 of the read byte.

The calibration can also be monitored by means of the

envelope output. For this purpose the voltage on

pin ENVOUT is forced to >2.5 V during the calibration.

The audio signal to the audio envelope function (level

meter) should be muted (i.e. output select = mute).

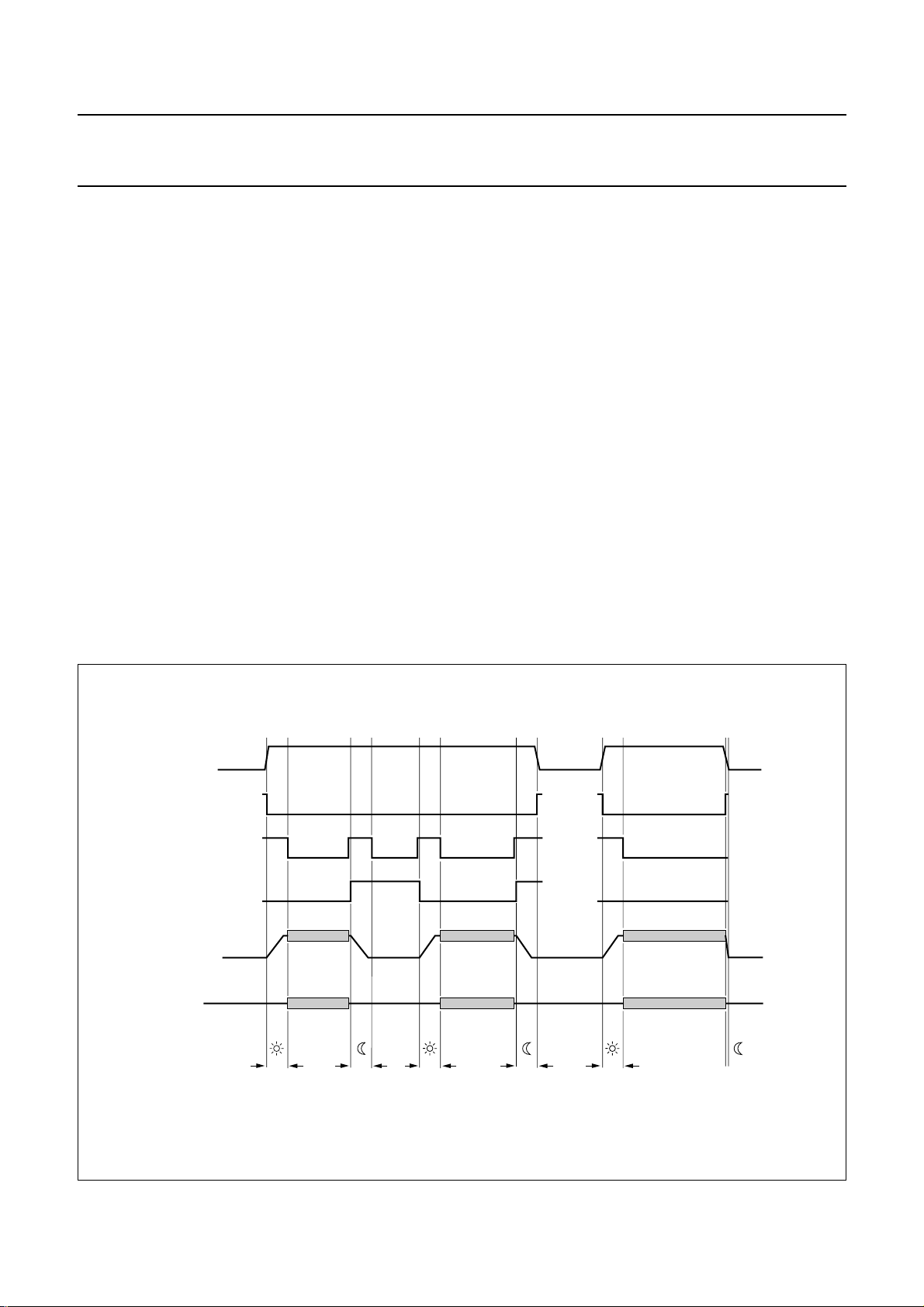

handbook, full pagewidth

2

I

C-bus write bit CALS

RMHD input

left channel oscillator

right channel oscillator

band-pass and

noise reduction filters

2

I

C-bus read bit CALR

ENVOUT output

logic 0

logic 1

Fig.7 Example of automatic calibration flow.

1999 Apr 14 12

logic 0

4 V3 V

5 V

logic 1

calibration

ready

MGR842

Page 13

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

Otherwise, the audio envelope output voltage may

become >2.5 V which makes it impossible to detect the

completion of the calibration on pin ENVOUT.

Calibration relies upon the frequency accuracy of the HID

control signal. The calibration result may be incorrect

when the HID control signal is disturbed during a critical

part of the calibration. An additional check is incorporated

to detect such a situation by reading bit CALE during

calibration. When bit CALE = 1, the calibration result is

detected to be unreliable due to external causes. A new

auto-calibration can be started by setting bit CALS = 0

followed by setting bit CALS = 1. Bit CALE always reads

logic 1 when bit CALS is logic 0.

The oscillators and band-pass filters can be switched

between NTSC and PAL system frequencies after a

calibration in NTSC or PAL mode without the need of

additional calibration. Switching between these system

modes is executed immediately and can be done in any

operating mode. The frequency accuracy of system

switching is 100 ±3 kHz for both carriers. To obtain the

best possible frequency accuracy in the record mode it is

good practice to recalibrate after system switching.

6.6 Power muting

Switching off and on of the power supply voltage or using

the built-in passive standby mode results in rising and

dropping of the output DC voltages and causes strong

disturbances on the output pins. The TDA9605H includes

three integrated mute switches to block such disturbances

so avoiding the need for an external mute circuit. Pop-free

line and RF converter output signals are realized by

connecting the integrated power mute switches behind the

line and RFC output capacitors.

Power muting is active when bit MUTE = 1 (see Fig.8).

Power muting is automatically activated when V

CC

is

switched on, because this situation is the Power-on reset

default state. The integrated mute switches on

pins MUTEC, MUTEL and MUTER are closed and form a

low-impedance path to ground. Furthermore, the

pins RFCOUT, LINEL and LINER are current limited to

−1 mA to avoid excessive supply currents and to achieve

good noise attenuation without the need for a series

resistor between the output and mute pins. Pins DECL and

DECR are also current limited for using the integrated

power mute switches or for assisting external muting.

handbook, full pagewidth

bit MUTE (I

bit STBP (I

RFCOUT

LINEL

LINER

output signal

with power mute

MUTEC

MUTEL

MUTER

(1) Power-on reset.

V

CC

auto-mute

(V

CC

2

2

C-bus)

< 7 V)

power off

(standby)

(

C-bus)

power

off

1)

(

t

mute

active

operation

t

mute

passive

standby

t

mute

active

operation

t

mute

Fig.8 Examples of power mute control and the auto-mute function.

1)

auto-mute

power

off

MGR843

t

mute

active

operation

1999 Apr 14 13

Page 14

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

During power muting the internal output signal is also

muted. After the output DC voltage has been established

power muting can be de-activated by setting bit MUTE = 0.

Now the mute switches are opened resulting in a

high-impedance path of 100 kΩ to ground. The output

current limiting is not active.

Power muting is also used in combination with the

integrated passive standby mode (bit STBP = 1). During

this mode the output circuits are switched off and the line,

decoder and RF converter output voltages decrease to 0 V

using a discharge current of 1 mA. Do not set power mute

mode and change the passive standby mode at the same

time. Power mute mode should be activated first, followed

by switching on or off of the passive standby mode to avoid

possible output glitches.

It should be noted that the time needed for stabilizing the

output DC voltage is proportional to the output capacitor

value. A safe mute time is 200 ms using a 10 µF capacitor

(t

=C×20000 s). Power muting consumes

mute

approximately 4 mA additional supply current, so to obtain

minimum power consumption the mute mode should be

de-activated after use. Very good performance is achieved

for power-up, power-down and passive standby mode

switching.

An auto-mute function is included which activates power

muting when the supply voltage drops below 7 V.

The performance of this auto-mute function depends upon

the power voltage drop rate. The voltage drop rate should

not exceed 1 V during 10 ms. The best performance

independent of voltage drop rate is realized by activating

the passive standby mode before switching off the power

supply voltage (by setting bit MUTE = 1 and bit STBP = 1).

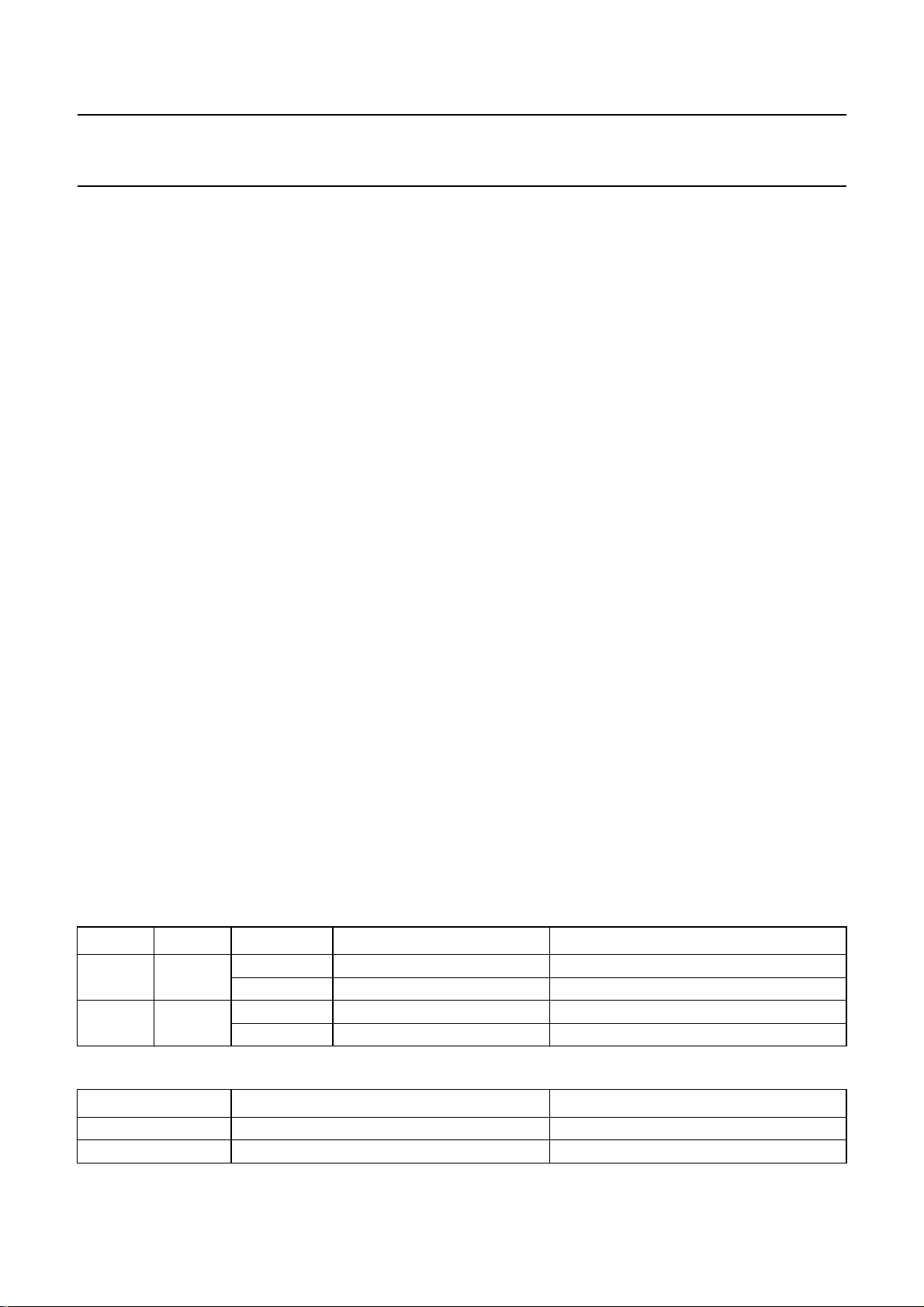

6.7 Envelope output

Pin ENVOUT is an analog output for stereo audio level

(e.g. level meter display) and for playback FM carrier level

(e.g. auto-tracking). The functional diagram is given in

Fig.9 and the timing diagram is shown in Fig.10. Only one

ADC input is needed on the microcontroller for reading all

the required information.

During the playback mode the selection between audio

level and carrier level information is realized by setting

2

I

C-bus control bit EOS (see Table 3). The AF envelope

output is defined by the signal selection made at the output

select.

During the record mode bit EOS offers the selection

between the audio level of the output select or the audio

level of the fixed hi-fi stereo signal. This is a helpful setting

when the microcontroller uses the audio level information

to adjust the hi-fi recording level (volume control).

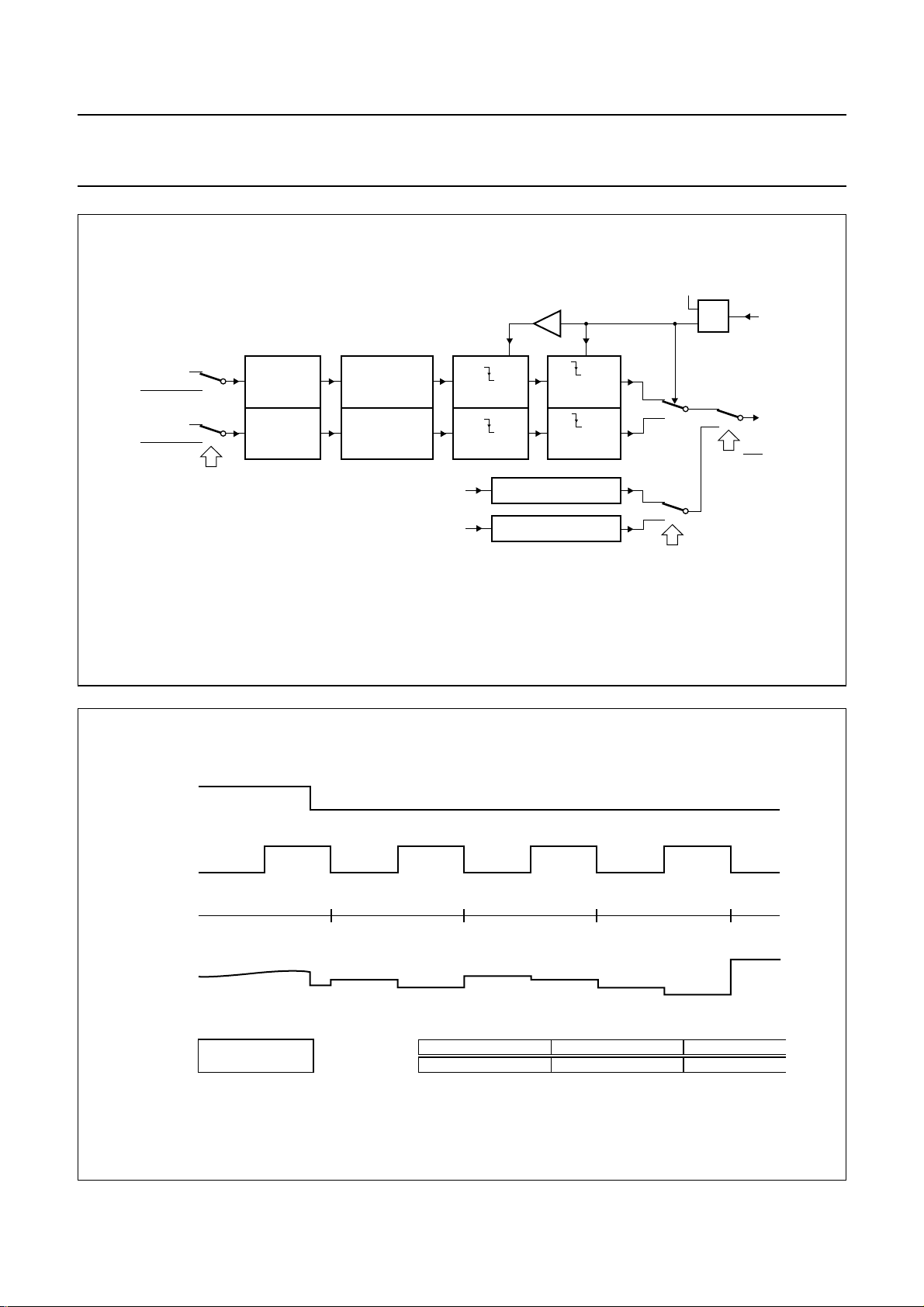

The HF envelope output signal is continuous and is

derived from the left channel carrier. The HF envelope

output exhibits a logarithmic characteristic (see Fig.11).

In a standard application circuit only the left channel carrier

level is required to support auto-tracking or manual

tracking. However, test 10 of the special test mode allows

for the right channel carrier level output instead for

measurement purposes (see Section 14.4).

The AF envelope output as a function of the output level is

given in Fig.12.

The AF envelope circuit uses time multiplexing for the left

and right channel audio level. A peak-hold function and

dynamic range compression (square root function) are

included for easy read out. The peak-hold function and the

left and right channel multiplexing are controlled by the

HID control signal on pin RMHID (see Table 4).

Table 3 Selection of the envelope output

MODE BIT AFM BIT EOS ENVELOPE OUTPUT FUNCTION

Playback

Record

Table 4 AF envelope output with channel multiplexing

HID SIGNAL LEVEL ON PIN RMHID AF ENVELOPE OUTPUT

LOW lower than 0.6 V or between 2.65 and 3.8 V left channel audio peak level

HIGH between 1.0 and 2.35 V or higher than 4.3 V right channel audio peak level

1999 Apr 14 14

0

1

0 AF envelope: via output select level meter display

1 HF envelope auto-tracking or manual tracking display

0 AF envelope: via output select level meter display

1 AF envelope: hi-fi stereo record volume control (and level display)

Page 15

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

handbook, full pagewidth

left channel audio:

output select

hi-fi

right channel audio:

output select

hi-fi

EOS • AFM

t

d

FULL-WAVE

RECTIFIER

FULL-WAVE

RECTIFIER

SQUARE ROOT

COMPRESSION

SQUARE ROOT

COMPRESSION

1.3 or 1.4 MHz carrier

1.7 or 1.8 MHz carrier

RESET

PEAK HOLD

RESET

PEAK HOLD

HF LEVEL DETECTOR

HF LEVEL DETECTOR

SAMPLE-

AND-HOLD

SAMPLE-

AND-HOLD

Fig.9 Functional diagram of the envelope output circuit.

SAMPLE

SAMPLE

AF

envelope

HF

envelope

test

10

RM

HID

EOS • AFM

RMHID

ENVOUT

MGR845

handbook, full pagewidth

I2C-bus

registers

HID signal

HID period

ENVOUT

level meter

display

EOS = 1 and

AFM = 0

0123

HF envelope

tracking level

indication

EOS = 0 or AFM = 1

peak right

in period −1

in period 0

peak right

in period 0

peak left

left (period 0)

right (period 0)

Fig.10 Timing diagram of the envelope output signal.

1999 Apr 14 15

peak left

in period 1

peak right

in period +1

peak left

in period 2

left (period 1)

right (period 1)

peak right

in period +2

right (period 2)

peak left

in period +3

left (period 2)

MGR844

Page 16

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

handbook, halfpage

5

ENVOUT

output

voltage

4

(V)

3

2

1

0

−1

10

1.3 MHz (NTSC) or 1.4 MHz (PAL) at internal node between head

amplifier and HF AGC.

11010

left channel carrier amplitude (RMS value) (mV)

MGR846

2103

Fig.11 HF envelope output (playback carrier level).

handbook, halfpage

RF

converter

output

(dBV)

−3

MGR848

MGR847

output

voltage

(V)

Bit LOH = 0.

5

4

3

2

1

0

−40 10−30 −20 −10 0

handbook, halfpage

ENVOUT

LINEL and LINER output level (dBV)

Fig.12 AF envelope output (audio peak level).

6.8 RF converter output

An AGC function is incorporated to avoid overmodulation

in the RF converter connected to pin RFCOUT. The AGC

limits the maximum signal level on the RF converter output

to −3 dBV (see Fig.13).

−3

line output (dBV)

Fig.13 AGC output of RF converter.

1999 Apr 14 16

The RF converter output can be muted by setting

bit RFCM = 1. When using this RF converter mute, the

AGC control is reset by discharging the capacitor

connected to pin RFACG.

Page 17

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

6.9 Audio dubbing

The TDA9605H includes unparalleled functionality

supporting the audio dubbing function of hi-fi video

recorders. Audio dubbing is a feature which enables the

recording of new sound material on the linear audio track

(i.e. normal sound) of an existing recording. The dub-mix

mode is selected by setting bit IS2 = 1, bit IS1 = 0 and

bit IS0 = 1. Audio dubbing can be used in two different

ways:

• Output mix

• Input mix.

6.9.1 O

UTPUT MIX

A new additional recording is made on the linear audio

track. In the playback mode, the new linear audio sound

and the original hi-fi sound are combined. In this way the

hi-fi stereo quality remains and the linear audio sound is

partly used (e.g. for commentary only). However, there is

no control over the original hi-fi sound.

Mixing of the hi-fi and normal sound signals in the playback

mode is supported by the output select function mix-left,

mix-right and mix-stereo (bits OSN, OSR and OSL) and

creates a new fixed output signal of1⁄2× hi-fi plus

1

⁄2× normal.

6.9.2 I

NPUT MIX

A new complete recording is made on the linear audio

track (see Fig.4). In the playback mode, only the linear

audio sound is used. In this way the hi-fi stereo quality is

lost, but total freedom in defining the new sound material

is an extra advantage. Furthermore, such recording is no

longer restricted to playback on hi-fi video recorders (with

an output mix option).

The circuit changes into a mixing desk when using the

dub-mix mode of the input select function in combination

with the volume setting of normal select. A new linear

audio recording can be created by mixing together the new

and the original sound.

Continuous user control over amplitude and ratio mix of

the auxiliary input signal (e.g. a microphone input) and the

original hi-fi playback sound is possible using the left and

right channel volume controls. This function is realized

inside the IC by connecting the auxiliary input signal pair

(pins AUXL and AUXR) to the left channel volume control

and the hi-fi output signal pair to the right channel volume

control.

The settings of the output select function are used to

arrange the hi-fi selection and the output signals in the

dub-mix mode. However, some of these settings are

overruled in the dub-mix mode. The normal signal is

available on the line outputs for monitoring the dub-mix

recording signals in the output select function modes

mix-left, mix-right and mix-stereo.

Mix-stereo of the output select function is generally used

for audio dubbing. In combination with the volume setting

of normal select, user control over amplitude and ratio is

offered for the auxiliary and the hi-fi signal as follows:

1

⁄4× aux left +1⁄4× aux right) × volume left plus

(

(1⁄4× hi-fi left +1⁄4× hi-fi right) × volume right.

The dub-mix mode is to be used in the (hi-fi) playback

mode. In the record mode, a signal loop from output to

input can be closed which may cause audio oscillation.

The auto-normal switching is not active during the dub-mix

mode. The hi-fi sound is muted when no hi-fi input signal

is detected; bit AUTN is not affected.

Table 5 Dub-mix mode

OUTPUT SELECT

MODE

DUB-MIX OUTPUT

SELECTION

LEFT CHANNEL RIGHT CHANNEL

DUB-MIX INPUT

mute mute aux stereo mute

hi-fi left hi-fi left aux stereo hi-fi left

hi-fi right hi-fi right aux stereo hi-fi right

hi-fi stereo hi-fi stereo aux stereo hi-fi stereo

normal normal aux stereo mute

mix-left normal aux stereo hi-fi left

mix-right normal aux stereo hi-fi right

mix-stereo normal aux stereo hi-fi stereo

1999 Apr 14 17

Page 18

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7I2C-BUS PROTOCOL

7.1 Addresses and data bytes

2

Full control of the TDA9605H is accomplished via the 2-wire I

accordance with the I2C-bus fast-mode specification.

Seven data byte registers are available for programming the device (write mode) and one data byte register is available

for reading data from the device (read mode). The registers are addressable via eight subaddresses. Automatic

subaddress incrementing enables writing of successive data bytes in one transmission.

During power-up, the data byte registers and auto-calibration registers are reset to a default state by the use of a

Power-On Reset (POR) circuit. The reset signal is derived from an internally generated voltage supplied by VCC.

Table 6 Addresses and POR state bits

NAME ADDRESS BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

Write mode

Slave byte B8H 10111000

Subaddress byte 00H to 07H;

000000or10or10or1

note 1

Control byte subaddress 00H AFM DOC SHH DETH NTSC HAC2 HAC1 HAC0

POR state 10001000

Select byte subaddress 01H DOS1 DOS0 s5 HRL NIL3 NIL2 NIL1 NIL0

POR state 0 0 0

Input byte subaddress 02H i7 IS2 IS1 IS0 NS2 NS1 NS0 i0

POR state 0

(2)

0001110

Output byte subaddress 03H LOH OSN OSR OSL EOS LOS DOS RFCM

POR state 00000001

Left volume byte subaddress 04H l7 VLS VL5 VL4 VL3 VL2 VL1 VL0

POR state 0

(2)

1000000

Right volume byte subaddress 05H r7 VRS VR5 VR4 VR3 VR2 VR1 VR0

POR state 0

(2)

1000000

Volume byte subaddress 06H simultaneous loading of the subaddress 04H and subaddress 05H registers

Power byte subaddress 07H CALS VCCS TEST PORR HPD MUTE STBP STBA

POR state 00000100

C-bus. Bus speeds up to 400 kbits/s can be used in

(2)

00000

(2)

Read mode

Slave address byte B9H 10111001

Read byte B9H CALR AUTN CALE POR 0

(3)

(3)

0

(3)

0

(3)

0

Notes

1. Continuous writing to a single data byte register is possible when subaddresses F0H to F7H (1111 0xxx) are used

instead of 00H to 07H (0000 0xxx). In that case automatic subaddress incrementing is disabled.

2. It is advised to keep the not-used write bits equal to the POR state to accommodate future compatibility.

3. You cannot rely upon the state of the not-used read bits because their state may change during development.

1999 Apr 14 18

Page 19

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.2 Valid transmissions to and from the TDA9605H

Table 7 Examples of valid transmissions

FUNCTION DATA TRANSFER SEQUENCE

Write START, B8H, 00H, data for 00, STOP

Write with auto-increment START, B8H, 00H, data for 00, data for 01, data for 02, STOP

Write with auto-increment ‘wrap-around’ START, B8H, 07H, data for 07, data for 00, data for 01, STOP

Write without auto-increment START, BBH, F6H, data for 06, data for 06, data for 06, STOP

Read START, B9H, data from IC, STOP

Read (continued) START, B9H, data from IC, data from IC, data from IC, STOP

7.3 Overview of the TDA9605H I

Table 8 Condensed overview

FUNCTION MODES CONTROL BITS

Audio FM mode playback and record AFM

Playback dropout cancelling on and off DOC

Playback head switch noise cancel time 6 µs and 8 µs SHH

Playback hi-fi carrier detection time slow and fast DETH

Record-mute and carrier ratio select record-mute, 3, 4.5, 6, 8, 9.5, 11

System standard NTSC and PAL NTSC

Playback head amplifier amplification 48, 51, 54, 57, 60, 63, 66 and 69 dB HAC2, HAC1 and HAC0

Record head amplifier current 12.5, 15, 17.5, 21, 25, 30, 35, 42, 50, 60,

Normal input level 0 to 14 dB and mute NIL3, NIL2, NIL1 and NIL0

Input select tuner, CINCH, ext1, ext2, SAP, dub-mix,

Normal select input select, volume, input-left,

Line output amplification 0 dB and +1 dB LOH

Output select mute, left, right, stereo, normal, mix-left,

Envelope select output select, stereo and HF envelope EOS and AFM

Line select output select and ext2 LOS

Decoder select output select, tuner, ext1, SAP and mute DOS, DOS1 and DOS0

RF converter mute 0 dB AGC and mute RFCM

Volume left −47 to 0 dB, mute and 0 to 15 dB VLS and VL5 to VL0

Volume right −47 to 0 dB, mute and 0 to 15 dB VRS and VR5 to VR0

Auto-calibration off and start calibration CALS

Supply voltage select 9 V and 12 V VCCS

Test standard operating mode and test mode TEST, HRL, NIL3, NIL2, NIL1

2

C-bus control

and 12.5 dB mix ratio

71 and 84 mA (p-p)

normal and aux

volume-left, SAP, tuner, ext2 and mute

mix-right and mix-stereo

DOC, SHH and DETH

HAC2, HAC1, HAC0 and HRL

IS2, IS1 and IS0

NS2, NS1 and NS0

OSN, OSR and OSL

and NIL0

1999 Apr 14 19

Page 20

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

FUNCTION MODES CONTROL BITS

Playback head amplifier disable standard operating mode and playback

disabled

Power output muting power mute MUTE

Operating mode standard operating mode, active standby

and passive standby

7.4 Control byte at subaddress 00H

The control byte is used to set the parameters of hi-fi processing and head amplifier control.

HPD

STBP and STBA

7.4.1 A

Bit AFM controls the main mode of the hi-fi processing and head amplifier. The function of other bits of the control byte

and bit EOS of the output byte depends on the state of bit AFM.

Table 9 Audio FM mode selection (bit AFM)

AFM MODE DESCRIPTION

0 playback hi-fi processing in playback mode and head amplifier in playback mode

1 record hi-fi processing in record mode and head amplifier is in record mode or record-mute mode

7.4.2 PLAYBACK MODE

When during the playback mode no FM carrier is detected from tape, the normal audio signal on pin LININ is

automatically selected by the output select function.

For this auto-normal mode:

• The timing of the hi-fi carrier detection can be selected via bit DETH which defines the auto-normal release time:

– Fast mode: hi-fi detection delay is 1 to 2 HID control signal periods (for NTSC: 33 to 66 ms; for PAL: 40 to 80 ms)

– Slow mode: hi-fi detection delay is 7 to 8 HID control signal periods (for NTSC: 233 to 267 ms;

• The state of hi-fi detection and auto-normal can be monitored by I2C-bus control bit AUTN of the read byte.

• In case automatic selection of the normal audio signal is not required the normal input level control can be set to mute

(bits NIL3 to NIL0 of the select byte).

UDIO FM MODE

for PAL: 280 to 320 ms).

Table 10 Dropout cancelling (bit DOC), sample-and-hold high-state (bit SHH) and detector time hi-fi (bit DETH) in the

playback mode; note 1

AFM DOC SHH DETH MODE DESCRIPTION

0 0 X X playback and DOC off dropout cancelling disabled

0 1 X X playback and DOC on dropout cancelling active

0 X 0 X playback and sample-and-hold time = 6 µs head switch noise cancel time set to 6 µs

0 X 1 X playback and sample-and-hold time = 8 µs head switch noise cancel time set to 8 µs

0 X X 0 playback and hi-fi detect = fast fast mode hi-fi detector timing

0 X X 1 playback and hi-fi detect = slow slow mode hi-fi detector timing

Note

1. X = don’t care.

1999 Apr 14 20

Page 21

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.4.3 RECORD MODE

During the record-mute mode, the recording output current on pin RECOUT is muted and the head amplifier is partly

disabled. The record mode, set by I2C-bus control, can also be changed to the record-mute mode by an external control

signal on pin RMHID. Sometimes the record-mute mode is named loop-through mode or EE mode.

Table 11 Dropout cancelling (bit DOC), sample-and-hold high-state (bit SHH) and detector time hi-fi (bit DETH) in the

record mode

AFM DOC SHH DETH MODE DESCRIPTION

1000record-mute record-mute and no recording output current; note 1

1001record and 3 dB mix recording with 3 dB output carrier ratio (1 : 1.4)

1010record and 4.5 dB mix recording with 4.5 dB output carrier ratio (1 : 1.7)

1011record and 6 dB mix recording with 6 dB output carrier ratio (1 : 2)

1100record and 8 dB mix recording with 8 dB output carrier ratio (1 : 2.5)

1101record and 9.5 dB mix recording with 9.5 dB standard output carrier ratio (1 : 3)

1110record and 11 dB mix recording with 11 dB output carrier ratio (1 : 3.5)

1111record and 12.5 dB mix recording with 12.5 dB output carrier ratio (1 : 4.2)

Note

1. Power-on reset state.

7.4.4 S

Bit NTSC selects between the NTSC and PAL (SECAM) system carrier frequencies for the CCO modulators or PLL

demodulators and the band-pass filters. FM carrier frequencies of 1.3 and 1.7 MHz are used for the NTSC system where

1.4 and 1.8 MHz are used for the PAL system. Different code settings for the auto-calibration circuit assure proper

calibration using the standard HID control signal frequency of 29.97 Hz for NTSC mode and 25 Hz for PAL mode. After

auto-calibration is completed bit NTSC enables instant switching between the NTSC and PAL system.

Table 12 System standard selection (bit NTSC)

Note

1. Power-on reset state.

YSTEM STANDARD SELECTION

NTSC MODE DESCRIPTION

0 PAL hi-fi circuit in PAL mode

1 NTSC hi-fi circuit in NTSC mode; note 1

1999 Apr 14 21

Page 22

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.4.5 HEAD AMPLIFIER PLAYBACK AMPLIFICATION

Eight settings of playback amplification can be selected for the head amplifier. The amplification values are valid for the

head signals from pins PBIN1 or PBIN2 to the internal node between the head amplifier and HF AGC circuit. The setting

of the playback amplification results in a selection of the hi-fi detection level (auto-normal function). The hi-fi detection

level indicated is the RMS value of the left channel carrier signal on pins PBIN1 and PBIN2.

The signal at the internal node can be monitored for testing purposes via pin ENVOUT using test 8 of the test mode.

It should be noted that the output level of test 8 shows 6 dB attenuation compared to the internal node level.

Table 13 Head amplifier control (bits HAC2, HAC1 and HAC0) in the playback mode

AFM HAC2 HAC1 HAC0 MODE DESCRIPTION

0 0 0 0 48 dB hi-fi detection level equals 13 µV (RMS) from head

0 0 0 1 51 dB hi-fi detection level equals 9.4 µV (RMS) from head

0 0 1 0 54 dB hi-fi detection level equals 6.7 µV (RMS) from head

0 0 1 1 57 dB hi-fi detection level equals 4.7 µV (RMS) from head

0 1 0 0 60 dB hi-fi detection level equals 3.3 µV (RMS) from head

0 1 0 1 63 dB hi-fi detection level equals 2.4 µV (RMS) from head

0 1 1 0 66 dB hi-fi detection level equals 1.7 µV (RMS) from head

0 1 1 1 69 dB hi-fi detection level equals 1.2 µV (RMS) from head

7.4.6 H

A total of twelve settings of the recording current can be selected for the head amplifier record output pin RECOUT.

Bit HRL of the select byte selects between high and low current settings. The recording current is defined as the

peak-to-peak value of the current of the record output signal which includes both the left and right carrier signal.

The selected recording current is independent of the selected record mix ratio setting, but recording is disabled during

the record-mute mode as defined by the bits DOC, SHH and DETH or the control signal on pin RMHID.

Table 14 Head amplifier control (bits HAC2, HAC1 and HAC0) and head record current low (bit HRL) in the record

AFM HAC2 HAC1 HAC0 HRL MODE DESCRIPTION

EAD AMPLIFIER RECORD CURRENT

mode

1000025mA(p-p) high recording current is 25 mA (p-p)

1001030mA(p-p) high recording current is 30 mA (p-p)

1010035mA(p-p) high recording current is 35 mA (p-p)

1011042mA(p-p) high recording current is 42 mA (p-p)

1100050mA(p-p) high recording current is 50 mA (p-p)

1101060mA(p-p) high recording current is 60 mA (p-p)

1110071mA(p-p) high recording current is 71 mA (p-p)

1111084mA(p-p) high recording current is 84 mA (p-p)

1000112.5 mA (p-p) low recording current is 12.5 mA (p-p)

1001115mA(p-p) low recording current is 15 mA (p-p)

1010117.5 mA (p-p) low recording current is 17.5 mA (p-p)

10111 21mA(p-p) low recording current is 21 mA (p-p)

1999 Apr 14 22

Page 23

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.5 Select byte at subaddress 01H

The select byte is used for decoder output select, record current range select and linear audio volume control.

7.5.1 D

By setting bit DOS = 0 of the output byte, the decoder output signal on pins DECL and DECR is defined by the output

select function. However, by setting bit DOS = 1 the decoder select function enables several independent signal

selections controlled via bits DOS1 and DOS0. Via the decoder select function the input signals on pins TUNL

and TUNR, pins EXT1L and EXT1R and pin SAP can be selected. The mute mode can also be selected.

The indicated decoder select function modes are also available during the active standby mode by setting bit STBA = 1.

Table 15 Decoder output select (bits DOS1 and DOS0)

DOS1 DOS0 MODE DESCRIPTION

Note

1. Power-on reset state.

7.5.2 H

The default selection of eight recording currents set by bits HAC2, HAC1 and HAC0 of the control byte is extended with

four additional low level recording currents by setting bit HRL = 1.

Table 16 Head amplifier record low current (bit HRL)

ECODER OUTPUT SELECT

0 0 tuner selection of input signal on pins TUNL and TUNR; note 1

0 1 ext1 selection of input signal on pins EXT1L and EXT1R

1 0 SAP selection of input signal on pin SAP

1 1 mute muting the input signal

EAD AMPLIFIER RECORD CURRENT RANGE SELECT

HRL MODE DESCRIPTION

0 high current selection of 8 medium and high-level recording currents; note 1

1 low current selection of 4 low-level recording currents

Note

1. Power-on reset state.

1999 Apr 14 23

Page 24

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.5.3 NORMAL INPUT LEVEL

Fifteen settings of amplification and mute can be selected for the linear audio input signal on pin LININ. The normal input

level control can replace the manual adjustment of the playback level at the linear audio circuit.

All selections using the normal linear audio signal include the normal input level control.

Table 17 Normal input level (bits NIL3 to NIL0)

NIL3 NIL2 NIL1 NIL0 MODE DESCRIPTION

0 0 0 0 0 dB amplification of linear audio of 0 dB; note 1

0 0 0 1 1 dB amplification of linear audio of 1 dB

::::: :

1 1 0 1 13 dB amplification of linear audio of 13 dB

1 1 1 0 14 dB amplification of linear audio of 14 dB

1 1 1 1 mute linear audio signal muted

Note

1. Power-on reset state.

7.6 Input byte at subaddress 02H

The input byte is used for input selection of the hi-fi and linear audio.

7.6.1 I

The input select function defines the input signal which is forwarded to the volume control function of hi-fi processing and

usually via the normal select function to the external linear audio circuit on pin LINOUT.

Table 18 Input select (bits IS2, IS1 and IS0)

Notes

1. Power-on reset state.

2. The dub-mix mode is a special selection which supports audio dubbing. This video recorder feature enables the

NPUT SELECT

IS2 IS1 IS0 MODE DESCRIPTION

0 0 0 tuner tuner input signal on pins TUNL and TUNR; note 1

0 0 1 CINCH CINCH input signal on pins CINL and CINR

0 1 0 ext1 TV input signal on pins EXT1L and EXT1R

0 1 1 ext2 decoder input signal on pins EXT2L and EXT2R

1 0 0 SAP mono input signal on pin SAP

1 0 1 dub-mix input signal on pins AUXL and AUXR (for left channel)

and from hi-fi output signal (for right channel); note 2

1 1 0 normal from linear audio circuit (from pin LININ)

1 1 1 aux input on pins AUXL and AUXR (e.g. camcorder input)

recording of the sound signal of the linear audio only (see Section 6.9).

1999 Apr 14 24

Page 25

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.6.2 NORMAL SELECT

The normal select function defines which of the input signals is forwarded to pin LINOUT for the connection to an external

linear audio circuit.

Table 19 Normal select (bits NS2, NS1 and NS0)

NS2 NS1 NS0 MODE DESCRIPTION

0 0 0 input select left plus right channel signal selected by input select

0 0 1 volume left plus right channel signal including hi-fi volume control

selected by input select

0 1 0 input-left left channel only (language 1) selected by input select

0 1 1 volume-left left channel only (language 1) including hi-fi volume control

selected by input select

1 0 0 SAP mono input signal from pin SAP

1 0 1 tuner tuner input signal from pins TUNL and TUNR

1 1 0 ext2 external input signals from pins EXT2L and EXT2R

1 1 1 mute mute of the input signals; note 1

Note

1. Power-on reset state.

7.7 Output byte at subaddress 03H

The output byte is used for selecting and controlling the output.

7.7.1 L

An additional 1 dB amplification for the line and decoder outputs on pins LINEL, LINER, DECL and DECR can be

selected by the line output high function.

Table 20 Line output high (bit LOH)

Note

1. Power-on reset state.

7.7.2 O

The auto-normal function is activated when no hi-fi signal is found on tape in the playback mode. Except for the mute

mode, all output select function modes will be overruled and changed to normal. Control of normal input level should be

set to mute for muting the hi-fi sound. The state of the auto-normal function can be monitored by reading bit AUTN of the

read byte.

INE OUTPUT AMPLIFICATION

LOH MODE DESCRIPTION

0 0 dB no line output amplification; note 1

1 1 dB 1 dB line output amplification

UTPUT SELECT

1999 Apr 14 25

Page 26

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

Table 21 Output select normal, right and left (bits OSN, OSR and OSL)

OSN OSR OSL MODE DESCRIPTION

0 0 0 mute mute; no selection; note 1

0 0 1 left left hi-fi channel selected (language1)

0 1 0 right right hi-fi channel selected (language 2)

0 1 1 stereo hi-fi stereo selected

1 0 0 normal normal signal selected (linear audio from pin LININ)

1

1 0 1 mix-left mix of hi-fi left with normal (

1 1 0 mix-right mix of hi-fi right with normal (

1 1 1 mix-stereo mix of hi-fi stereo with normal (

Note

1. Power-on reset state.

In case the dub-mix mode is selected via the input select function, the performance of mix-left, mix-right and mix-stereo

modes is changed to support audio dubbing input mixing. The hi-fi channel is available for the input select function and

normal sound is available at the output for monitoring the linear audio recording. The auto-normal state is ignored during

the dub-mix mode and the hi-fi playback signal is muted instead.

⁄2× left +1⁄2× normal)

1

⁄2× right +1⁄2× normal)

1

⁄2× stereo +1⁄2× normal)

Table 22 Dub-mix mode (bits OSN, OSR and OSL)

OSN OSR OSL MODE OUTPUT IN DUB-MIX MODE INPUT IN DUB-MIX MODE

0 0 0 mute mute mute

0 0 1 left left channel left channel

0 1 0 right right channel right channel

1

0 1 1 stereo stereo signal

⁄2× left +1⁄2× right

1 0 0 normal normal signal mute

1 0 1 mix-left normal signal left channel

1 1 0 mix-right normal signal right channel

1 1 1 mix-stereo normal signal

7.7.3 E

NVELOPE OUTPUT SELECT

1

⁄2× left +1⁄2× right

The output signal on pin ENVOUT is selected via the envelope select function.

In the playback mode the HF envelope displays the amplitude of the left channel carrier. Display of the right channel

carrier amplitude for special measurement purposes can be selected via test 10 in the test mode.

Table 23 Envelope output select (bit EOS)

AFM EOS MODE DESCRIPTION

(1)

X

0 output select audio peak envelope of selected signal via output select function; note 2

0 1 HF envelope HF envelope of the left channel carrier in the playback mode

1 1 stereo envelope audio peak envelope of the hi-fi stereo signal in the record mode

Notes

1. X = don’t care.

2. Power-on reset state.

1999 Apr 14 26

Page 27

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.7.4 LINE OUTPUT SELECT

An independent selection of the input signals from

pins EXT2L and EXT2R to the line outputs on pins LINEL

and LINER is offered by the line select function.

In the active standby mode (bit STBA = 1) the output

select signal is muted. However, the line select function of

the ext2 input signal is still operating.

In combination with the decoder select function a complete

pay-TV decoder switching feature is offered via the

SCART connector.

Table 24 Line output select (bit LOS)

LOS MODE DESCRIPTION

0 output

select

1 ext2 line output signal is from input

Note

1. Power-on reset state.

7.7.5 D

The output signals on pins DECL and DECR can be

selected by the decoder select function. By setting

bit DOS = 0, the output signals are selected by the output

select function. By setting bit DOS = 1, an independent

selection between the input signals on pins TUNL

and TUNR, pins EXT1L and EXT1R, pin SAP or mute is

possible. These signals are selected by the decoder select

function (bits DOS1 and DOS2).

ECODER OUTPUT SELECT

line output signal is set by output

select; note 1

signal on pins EXT2L and EXT2R

7.7.6 RF CONVERTER MUTE

The RF converter output signal on pin RFCOUT can be

muted by setting bit RFCM = 1. In this mute mode, the

AGC capacitor on pin RFCAGC is discharged and the

AGC control is reset.

Table 26 RF converter mute (bit RFCM)

RFCM MODE DESCRIPTION

0 AGC RF converter output signal is set by

the output select function:

AGC active

1 mute RF converter output signal is muted

and AGC control is reset; note 1

Note

1. Power-on reset state.

7.8 Volume bytes at subaddresses 04H, 05H and 06H

The volume bytes are used to set left and right channel

volume control.

7.8.1 Left and right volume control

Left channel volume control can be set by using

subaddress 04H. Right channel volume control can be set

by using subaddress 05H. Left and right channel volume

control can be set simultaneous by using subaddress 06H.

In the active standby mode (bit STBA = 1) the output

select signal is muted. However, the decoder select

function is still operating.

In combination with the line select function a complete

pay-TV decoder switching feature is offered via the

SCART connector.

Table 25 Decoder output select (bit DOS)

DOS MODE DESCRIPTION

0 output

select

1 decoder

select

Note

1. Power-on reset state.

1999 Apr 14 27

decoder output signal is set by the

output select function; note 1

decoder output signal is set by the

decoder select function

Page 28

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

Table 27 Volume left sign (bit VLS), volume left (bits VL5 to VL0), volume right sign (bit VRS) and volume right

(bits VR5 to VR0); note 1

VLS VL5 VL4 VL3 VL2 VL1 VL0

MODE DESCRIPTION

VRS VR5 VR4 VR3 VR2 VR1 VR0

00000000dB volume 0 dB

0000001−1 dB volume −1dB

0000010−2 dB volume −2dB

:::::::: :

0101110−46 dB volume −46 dB

0101111−47 dB volume −47 dB

011XXXXmute mute

1XX00000dB volume 0 dB; note 2

1XX00011dB volume 1 dB

1XX00102dB volume 2 dB

:::::::: :

1XX111014dB volume 14 dB

1XX111115dB volume 15 dB

Notes

1. X = don’t care.

2. Power-on reset state.

7.9 Power byte at subaddress 07H

The power byte is used for power-up settings and the

standby control mode.

The combination of bit CALR = 1 and bit CALE = 0

indicates a successful calibration. Bit CALS should remain

at logic 1 after the calibration to keep a reliable state of

bit CALR and bit CALE.

7.9.1 C

ALIBRATION START

Automatic frequency calibration by setting the hi-fi modem,

the band-pass filter and the noise reduction is performed

after a change of bit CALS from logic 0 to logic 1. The use

of auto-calibration is only needed after power-up

(Power-on reset) of the supply voltage (see Section 6.5).

Table 28 Calibration start (bit CALS)

CALS MODE DESCRIPTION

0 no calibration note 1

1 start

calibration

start of the automatic calibration

cycle

Note

1. Power-on reset state.

The output signal on pin ENVOUT or bit CALR (calibration

ready) and bit CALE (calibration error) of the read byte can

be monitored to check for completion of the calibration.

1999 Apr 14 28

7.9.2 DC

OUTPUT VOLTAGE SELECTION

The DC output level on pins LINEL, LINER, DECL

and DECR can be changed by setting bit VCCS to

maximize the output power when using a supply voltage

of 12 V.

The use of power muting (bit MUTE = 1) ensures

disturbance free switching of the line output signal when

setting bit VCCS after power-up.

Table 29 V

supply voltage select (bit VCCS)

CC

VCCS MODE DESCRIPTION

0 9 V line and decoder output DC voltage

is 4.5 V; note 1

1 12 V line and decoder output DC voltage

is 6 V

Note

1. Power-on reset state.

Page 29

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.9.3 TEST MODE

Several special tests can be selected for test, evaluation

and measurement purposes. The selection of these tests

is made by setting bit HRL and bits NIL3 to NIL0.

See Section 14.4 for an overview of the test modes.

Table 30 Test mode (bit TEST)

TEST MODE DESCRIPTION

0 operating

mode

1 test mode test mode for special

Note

1. Power-on reset state.

7.9.4 P

Setting bit PORR = 1 ensures a reset of bit POR of the

read byte to logic 0. In this way, a reading of logic 1 for

bit POR always indicates the occurrence of an actual

I2C-bus register Power-on reset and can not be caused

accidentally by other I2C-bus control bits. Bit PORR has no

control function but it is an unused bit, dedicated by name

to change the I2C-bus register content from the Power-on

reset state.

Bit POR of the read byte is a logic AND function for

checking all I2C-bus register bits. Bit POR will read logic 1

when the I2C-bus register content equals the Power-on

reset default state and also when this state is set via the

I2C-bus control. Since a setting of bit PORR = 1 differs

from the Power-on reset default state, it forces a reset of

bit POR to logic 0 independent of other bit settings.

OWER-ON RESET

standard operating; note 1

measurements

7.9.5 HEAD AMPLIFIER DISABLE

Bit HPD offers a special setting intended for use with some

of the built-in test modes and for support of particular

applications that do not require use of the integrated head

amplifier. By setting bit HPD = 1 the head amplifier

playback circuit is disabled. This mode enables direct input

signal to the HF AGC circuit via pin HMSW (AC coupled

via a 10 nF capacitor).

Table 32 Head amplifier playback disable (bit HPD)

HPD MODE DESCRIPTION

0 operating

mode

1 head

amplifier

disable

Note

1. Power-on reset state.

7.9.6 P

The power mute function controls the mute switches on the

line and RF converter outputs. The power mute mode is

automatically activated via the Power-on reset function

during power-up of the supply voltage. During

power-down, the mute switches are activated

automatically by means of the auto-mute circuit which is

independent of the setting of bit MUTE. When setting

bit MUTE = 1 the output current on pins RFCOUT, LINEL,

LINER, DECL and DECR is limited to −1 mA for controlled

power-up response and the selected output signal is

muted (see Section 6.6).

OWER MUTING

standard operating mode; note 1

head amplifier disabled in playback

mode (for test or special

application)

Table 31 Resetting of bit POR (bit PORR)

PORR MODE DESCRIPTION

0 no reset note 1

1 bit POR

reset

Note

1. Power-on reset state.

1999 Apr 14 29

reset of bit POR (read byte)

Table 33 Power mute (bit MUTE)

MUTE MODE DESCRIPTION

0 no mute power muting released: mute

switches are open

1 mute power muting activated: mute

switches are closed; note 1

Note

1. Power-on reset state.

Page 30

Philips Semiconductors Product specification

Audio processor with head amplifier for VHS hi-fi TDA9605H

7.9.7 STANDBY SELECT

The TDA9605H is switched in the low-power active

standby mode by setting bit STBA = 1. Most circuits are

switched inactive for reducing power consumption.

However, the RF converter, line and decoder outputs

remain active in this mode and the direct audio selections

offered via the line select function and the decoder select

function remain available. The selected output signal is

muted during the active standby mode.

The TDA9605H is switched in the minimum power passive

standby mode by setting bit STBP = 1. All circuits are

switched inactive to obtain minimum power consumption

except for the power mute circuit, the I

input reference buffer (i.e. the DC voltage on pins 1 to 11

remains active). When bit STBP = 1 a discharge current of

1 mA is active on pins RFCOUT, LINEL, LINER, DECL

and DECR.

Power muting ensures disturbance-free switching of the

line and RF converter outputs to and from the passive

standby mode. In the passive standby mode power muting

can be de-activated again to achieve minimum power

consumption. The calibration and I2C-bus registers are not

affected in the active standby or passive standby mode.

2

C-bus and the line

7.10.1 CALIBRATION READY

The completion of calibration is signalled by changing

bit CALR from logic 0 to logic 1. Bit CALR remains logic 0

if for some reason a calibration can not be completed (i.e.

no HID control signal available or the hi-fi processing is in

the playback mode). Bit CALR will also return to logic 0 if

calibration is lost due to a Power-on reset situation.

Additional information about the calibration result is

available via bit CALE. Calibration is found correct if

bit CALR = 1 and bit CALE = 0.

Pin ENVOUT can also be used to monitor calibration

(see Section 6.5).

Table 35 Calibration ready (bit CALR)

CALR DESCRIPTION

0 not calibrated; note 1

1 auto-calibration completed

Note

1. Power-on reset state.

7.10.2 A

UTO-NORMAL SELECTION

Table 34 Standby passive (bit STBP) and standby active

(bit STBA); note 1

STBP STBA MODE DESCRIPTION

0 0 operating standard operating mode:

full function; note 2

0 1 active

standby

1 X passive

standby

Notes

1. X = don’t care.

2. Power-on reset state.