Philips tda3566 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

TDA3566

PAL/NTSC decoder

Preliminary specification

File under Integrated Circuits, IC02

May 1989

Philips Semiconductors Preliminary specification

PAL/NTSC decoder TDA3566

GENERAL DESCRIPTION

The TDA3566 is a monolithic integrated decoder for the PAL and/or NTSC colour television standards. It combines all

functions required for the identification and demodulation of PAL/NTSC signals. Furthermore it contains a luminance

amplifier, an RGB-matrix and amplifier. These amplifiers supply output signals up to 4 V peak-to-peak (picture

information) enabling direct drive of the discrete output stages. The circuit also contains separate inputs for data

insertion, analogue as well as digital, which can be used for text display systems (e.g. Teletext/broadcast antiope),

channel number display, etc.

Features

• A black-current stabilizer which controls the black-currents of the three electron-guns to a level low enough to omit the

black-level adjustment

• Contrast control of inserted RGB signals

• No black-level disturbance when non-synchronized external RGB signals are available on the inputs

• NTSC capability with hue control

QUICK REFERENCE DATA

Supply voltage (pin 1) V

Supply current (pin 1) I

P=V1-27

= I

P

1

typ. 12 V

typ. 80 mA

Luminance amplifier (pin 8)

Input voltage (peak-to-peak value) V

8-27(p-p)

typ. 450 mV

Contrast control range typ. 20 dB

Chrominance amplifier (pin 4)

Input voltage range (peak-to-peak value) V

4-27(p-p)

40 to 1100 mV

Saturation control range min. 50 dB

RGB matrix and amplifiers

Output voltage at nominal luminance and contrast

(peak-to-peak value) V

13, 15, 17-27(p-p)

typ. 4 V

Data insertion

Input signals (peak-to-peak value) V

12, 14, 16-27(p-p)

typ. 1 V

Data blanking (pin 9)

Input voltage for data insertion V

9-27

min. 0,9 V

Sandcastle input (pin 7)

Blanking input voltage V

Burst gating and clamping input voltage V

7-27

7-27

typ. 1,5 V

typ. 7 V

PACKAGE OUTLINE

28-lead DIL; plastic, with internal heat spreader (SOT117); SOT117-1, 1996 November 21.

May 1989 2

Philips Semiconductors Preliminary specification

PAL/NTSC decoder TDA3566

May 1989 3

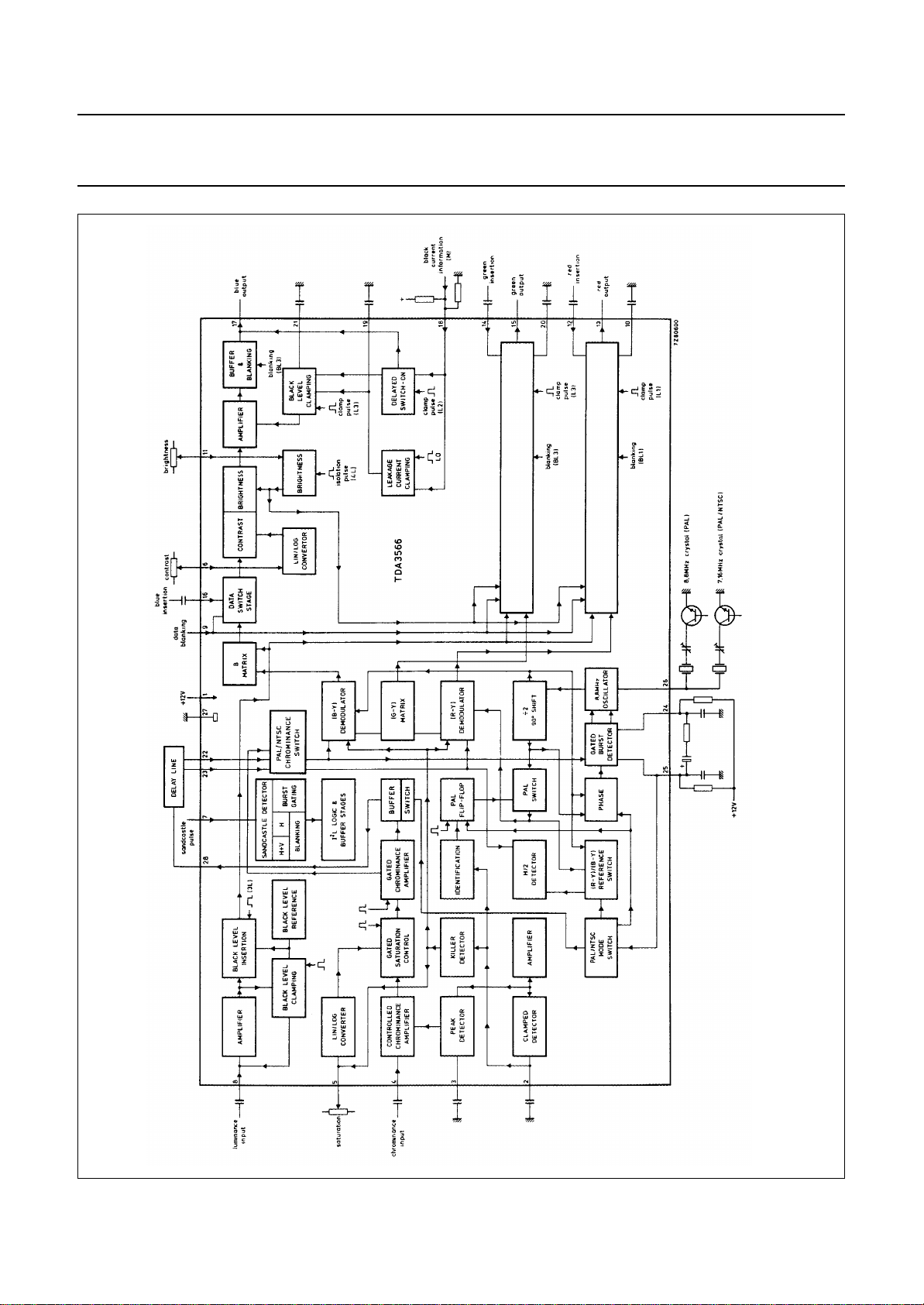

Fig.1 Block diagram; for explanation of pulse mnemonics see Fig.6.

Philips Semiconductors Preliminary specification

PAL/NTSC decoder TDA3566

FUNCTIONAL DESCRIPTION

The TDA3566 is a further development of the TDA3562A. It has the same pinning and almost the same application.

The differences between the TDA3562A and the TDA3566 are as follows:

• The NTSC-application has largely been simplified. In the case of NTSC the chroma signal is now internally coupled to

the demodulators, ACC and phase detectors. The chroma output signal (pin 28) is suppressed in this case. It follows

that the external switches and filters which are needed for the TDA3562A are not needed for the TDA3566.

Furthermore there is no difference between the amplitude of the colour output signals in the PAL or NTSC mode. The

PAL/NTSC-switch and the hue control of the TDA3566 and the TDA3562A are identical.

• The switch-on and the switch-off behaviour of the TDA3566 has been improved. This has been obtained by

suppressing the output signals during the switch-on and switch-off periods.

• The clamp capacitors connected to the pins 10, 20 and 21 can be reduced to 100 nF for the TDA3566. The clamp

capacitors also receive a pre-bias voltage to avoid coloured background during switch-on.

• The crystal oscillator circuit has been changed to prevent parasitic oscillations on the third overtone of the crystal. This

has the consequence that optimal tuning capacitance must be reduced to 10 pF.

Luminance amplifier

The luminance amplifier is voltage driven and requires an input signal of 450 mV peak-to-peak (positive video). The

luminance delay line must be connected between the i.f. amplifier and the decoder. The input signal is a.c. coupled to

the input (pin 8). After amplification, the black level at the output of the preamplifier is clamped to a fixed d.c. level by the

black level clamping circuit. During three line periods after vertical blanking, the luminance signal is blanked out and the

black level reference voltage is inserted by a switching circuit. This black level reference voltage is controlled via pin 11

(brightness). At the same time the RGB signals are clamped. Noise and residual signals have no influence during

clamping thus simple internal clamping circuitry is used.

Chrominance amplifiers

The chrominance amplifier has an asymmetrical input. The input signal must be a.c. coupled (pin 4) and have a minimum

amplitude of 40 mV peak-to-peak. The gain control stage has a control range in excess of 30 dB, the maximum input

signal must not exceed 1,1 V peak-to-peak, otherwise clipping of the input signal will occur. From the gain control stage

the chrominance signal is fed to the saturation control stage. Saturation is linear controlled via pin 5. The control voltage

range is 2 to 4 V, the input impedance is high and the saturation control range is in excess of 50 dB. The burst signal is

not affected by saturation control. The signal is then fed to a gated amplifier which has a 12 dB higher gain during the

chrominance signal. As a result the signal at the output (pin 28) has a burst to chrominance ratio which is 6 dB lower than

that of the input signal when the saturation control is set at −6 dB. The chrominance output signal is fed to the delay line

and, after matrixing, is applied to the demodulator input pins (pins 22 and 23). These signals are fed to the burst phase

detector. In the case of NTSC the chroma signal is internally coupled to the demodulators, ACC and phase detector.

Oscillator and identification circuit

The burst phase detector is gated with the narrow part of the sandcastle pulse (pin 7). In the detector the (R-Y) and (B-Y)

signals are added to provide the composite burst signal again. This composite signal is compared with the oscillator

signal divided-by-2 ((R-Y) reference signal). The control voltage is available at pins 24 and 25, and is also applied to the

8,8 MHz oscillator. The 4,4 MHz signal is obtained via the divide-by-2 circuit, which generates both the (B-Y) and (R-Y)

reference signals and provides a 90° phase shift between them.

The flip-flop is driven by pulses obtained from the sandcastle detector. For the identification of the phase at PAL mode,

the (R-Y) reference signal coming from the PAL switch, is compared to the vertical signal (R-Y) of the PAL delay line.

This is carried out in the H/2 detector, which is gated during burst. When the phase is incorrect, the flip-flop gets a reset

from the identification circuit. When the phase is correct, the output voltage of the H/2 detector is directly related to the

burst amplitude so that this voltage can be used for the a.c.c. To avoid ‘blooming-up’ of the picture under weak input

signal conditions the a.c.c. voltage is generated by peak detection of the H/2 detector output signal.

May 1989 4

Philips Semiconductors Preliminary specification

PAL/NTSC decoder TDA3566

The killer and identification circuits get their information from a gated output signal of the H/2 detector. Killing is obtained

via the saturation control stage and the demodulators to obtain good suppression. The time constant of the saturation

control (pin 5) provides a delayed switch-on after killing.

Adjustment of the oscillator is achieved by variation of the burst phase detector load resistance between pins 24 and 25

(see Fig.7). With this application the trimmer capacitor in series with the 8,8 MHz crystal (pin 26) can be replaced by a

fixed value capacitor to compensate for unbalance of the phase detector.

Demodulator

The (R-Y) and (B-Y) demodulators are driven by the colour difference signals from the delay-line matrix circuit and the

reference signals from the 8,8 MHz divider circuit. The (R-Y) reference signal is fed via the PAL-switch. The output

signals are fed to the R and B matrix circuits and to the (G-Y) matrix to provide the (G-Y) signal which is applied to the

G-matrix. The demodulation circuits are killed and blanked by by-passing the input signals.

NTSC mode

The NTSC mode is switched on when the voltage at the burst phase detector outputs (pins 24 and 25) is adjusted below

9 V. To ensure reliable application the phase detector load resistors are external. When the TDA3566 is used only for

PAL these two 33 kΩ resistors must be connected to +12 V (see Fig.7). For PAL/NTSC application the value of each

resistor must be reduced to 10 kΩ and connected to the slider of a potentiometer (see Fig.8). The switching transistor

brings the voltage at pins 24 and 25 below 9 V which switches the circuit to the NTSC mode. The position of the PAL

flip-flop ensures that the correct phase of the (R-Y) reference signal is supplied to the (R-Y) demodulator. The drive to

the H/2 detector is now provided by the (B-Y) reference signal. (In the PAL mode it is driven by the (R-Y) reference

signal.)

Hue control is realized by changing the phase of the reference drive to the burst phase detector. This is achieved by

varying the voltage at pins 24 and 25 between 7,5 V and 8,5 V, nominal position 8,0 V. The hue control characteristic is

shown in Fig.5.

RGB matrix and amplifiers

The three matrix and amplifier circuits are identical and only one circuit will be described. The luminance and the colour

difference signals are added in the matrix circuit to obtain the colour signal, which is then fed to the contrast control stage.

The contrast control voltage is supplied to pin 6 (high-input impedance). The control range is + 3 db to−17 dB nominal.

The relationship between the control voltage and the gain is linear (see Fig.2).

During the 3-line period after blanking a pulse is inserted at the output of the contrast control stage. The amplitude of this

pulse is varied by a control voltage at pin 11. This applies a variable offset to the normal black level, thus providing

brightness control. The brightness control range is 1 V to 3 V.

While this offset level is present, the ‘black-current’ input impedance (pin 18) is high and the internal clamp circuit is

activated. The clamp circuit then compares the reference voltage at pin 19 with the voltage developed across the external

resistor network R

stored in capacitors connected from pins 10, 20 and 21 to ground which controls the black level at the output. The

reference voltage is composed by the resistor divider network and the leakage current of the picture tube into this

bleeder. During vertical blanking, this voltage is stored in the capacitor connected to pin 19, which ensures that the

leakage current of the CRT does not influence the black current measurement.

The RGB output signals can never exceed a level of 10 V. When the signal tends to exceed this level the output signal

is clipped. The black level at the outputs (pins 13, 15 and 17) will be about 3 V. This level depends on the spread of the

guns of the picture tube. If a beam current stabilizer is not used it is possible to stabilize the black levels at the outputs,

which in this application must be connected to the black current measuring input (pin 18) via a resistor network.

and RB (pin 18) which is provided by picture tube beam current. The output of the comparator is

A

May 1989 5

Philips Semiconductors Preliminary specification

PAL/NTSC decoder TDA3566

Data insertion

Each colour amplifier has a separate input for data insertion. A 1 V peak-to-peak input signal provides a 4 V peak-to-peak

output signal. To avoid the ‘black-level’ of the inserted signal differing from the black level of the normal video signal, the

data is clamped to the black level of the luminance signal. Therefore a.c. coupling is required for the data inputs.

To avoid a disturbance of the blanking level due to the clamping circuit, the source impedance of the driver circuit must

not exceed 150 Ω.

The data insertion circuit is activated by the data blanking input (pin 9). When the voltage at this pin exceeds a level of

0,9 V, the RGB matrix circuits are switched off and the data amplifiers are switched on. To avoid coloured edges, the

data blanking switching time is short.

The amplitude of the data output signals is controlled by the contrast control at pin 6. The black level is equal to the video

black level and can be varied between 2 and 4 V (nominal condition) by the brightness control voltage at pin 11.

Non-synchronized data signals do not disturb the black level of the internal signals.

Blanking of RGB and data signals

Both the RGB and data signals can be blanked via the sandcastle input (pin 7). A slicing level of 1,5 V is used for this

blanking function, so that the wide part of the sandcastle pulse is separated from the remainder of the pulse. During

blanking a level of + 1 V is available at the output.

To prevent parasitic oscillations on the third overtone of the crystal the optimal tuning capacitance should be 10 pF.

RATINGS

Limiting values in accordance with Absolute Maximum System (IEC 134)

Supply voltage (pin 1) V

Total power dissipation P

Storage temperature range T

Operating ambient temperature range T

THERMAL RESISTANCE

From junction to ambient (in free air) R

= V

P

tot

stg

amb

th j-a

1-27

max. 13,2 V

max. 1,7 W

−25 to + 150 °C

−25 to + 70 °C

= 40 K/W

May 1989 6

Loading...

Loading...