Page 1

DVD-Video Player DVD Module SD-5.31SL

Contents Page

1 Technical Specifications 2

2 Safety Instructions, Warnings, and Notes 5

3 Directions for Use (not available) 6

4 Mechanical Instructions 7

5 Test Instructions Mono Board SD5.31SL 11

Diagnostic Software Description 20

6 Block Diagram and Testpoint Overview

Block Diagram 31

TTestpoint Overview Bare Board 32

7 Electrical Diagrams & Pwb’s Diagr. PWB

DVD Analog Front-end (Diagram M1) 33 41-46

Spindle/Servo Motor Driver (Diagram M2) 34 41-46

DVD Front-end Processor (Diagram M3) 35 41-46

DVD Back-end Processor (Diagram M4) 36 41-46

Back-end Memory (Diagram M5) 37 41-46

Audio (Diagram M6) 38 41-46

Services and Debug (Diagram M7) 39 41-46

Video and Power (Diagram M8) 40 41-46

8 Alignments (not available) 47

9 Circuit Description 47

List of Abbreviations 55

IC Data Sheets 56

10 Spare Part List 61

11 Revision List 64

©

Copyright 2003 Philips Consumer Electronics B.V. Eindhoven, The Netherlands.

All rights reserved. No part of this publication may be reproduced, stored in a

retrieval system or transmitted, in any form or by any means, electronic,

mechanical, photocopying, or otherwise without the prior permission of Philips.

Published by PF0365 Service Singapore Printed in the Netherlands Subject to modification EN 3122 785 13710

Page 2

EN 2 SD-5.31SL1.

Technical Specifications

1. Technical Specifications

1.1 Interfaces and Pin Assignments

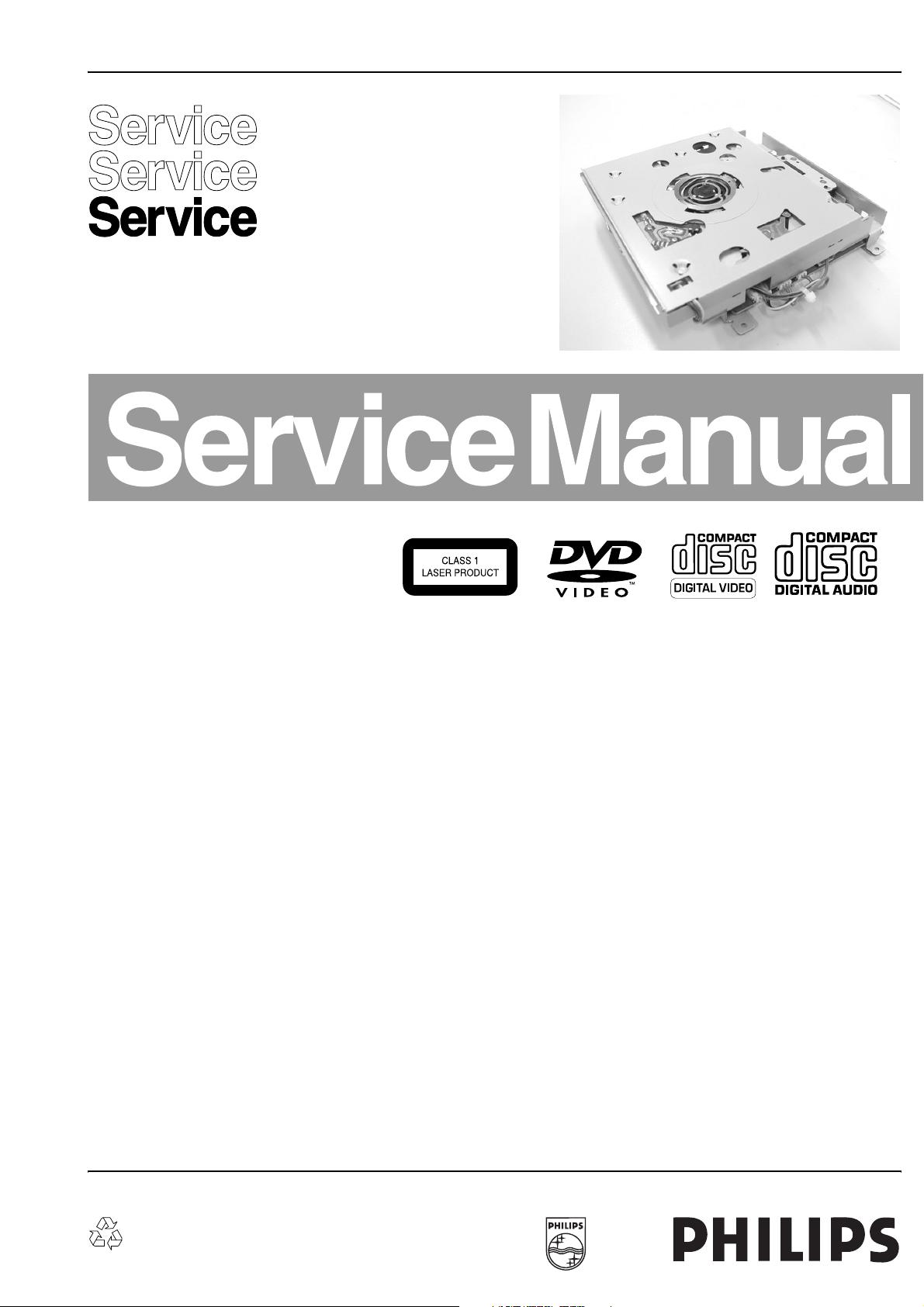

The interfaces or connectors are placed on both PCB layers of

top and bottom as shown in figure "Interfaces placement on

PCB layer".

Basic AV Advance AVExt I2S Digital Video

30 30 124

1

1702

7

1

1402

7

DIAGS

JTAG

15

Screw mounting

1600 18001701

point

Loader conn

124124

Figure 1-1 Interfaces placement on PCB layer

1

OPU

Monoboard

Top view

1300 1301

E-Link/Atapi-2E-Link/Atapi-1

Screw mounting

1

1400

Screw mounting

point

point

CL 36532043_016.eps

Motor

Spindle

210503

151

1100

1.2.2 Interface Basic AV at Location 1600

1. GND

2. DVD_SC

3. GND_SC

4. DVD_L

5. GND_L

6. DVD_R/ PCMDATA3(CELf)

7. GND_R

8. DVD_LFE

9. GND_LFE

10. DVD_LS / PCMDATA2(LsRs)

11. GND_LS

12. DVD_C

13. GND_C

14. DVD_RS/ PCMDATA1(LR)

15. GND_RS

16. SENSE_3V3

17. GND

18. MIC_IN (KOK)

19. GND

20. VIDEO_SEL

21. GND

22. I2CSCL_M

23. I2CSDA_M

24. GND

25. PCMDATA0(LtRt)

26. GND

27. DIG_IN_1

28. I2C INT

29. DAC_RST

30. GND

1.2 Connections

1.2.1 Interface ADVANCE AV at Location 1800:

1. I2CSCL_M / I2CSCL_S

2. I2CSDA_M / I2CSDA_S

3. SCART1 / I2C INT/ GND

4. SCART0 / SLOT_IN_DET

5. B_REF (Video ground)

6. B_U

7. G_REF (Video ground)

8. G_Y

9. R_REF (Video ground)

10. R_V

11. Y_REF (Video ground)

12. Y

13. C_REF (Video ground)

14. C

15. CVBS-REF (Video ground)

16. CVBS

17. +3V3

18. +3V3

19. +5V

20. +12V_Stby

21. +12V

22. MUTE / SPDIF

23. GND

24. PCMSCLK

25. PCMDATA0 / Lt

26. GND_LRT (Audio ground)

27. PCMCLK / Rt

28. PCMLRCLK

29. GND

30. SPDIF / MUTE

1.2.3 Service connector at Location 1702:

1 TXD_SER TXD service UART

2 SERVICE Service or normal mode select

3 RXD_SER RXD service UART

4 RTS_SER Not used

5 GNDB Ground

6 CTS_SER Not used

7 +5V 5V supply

1.3 Signal Specifications

This section defines the specifications of the signals at the

module interface.

1.3.1 Voltage level

TTLTransistor-transistor logic (5V logic)

Caution: Exceeding the absolute maximum rating will cause

damage to the module.

Absolute maximum rating:

IN =-0.5V to 5.5V

VOUT = -0.5V to 5.5V

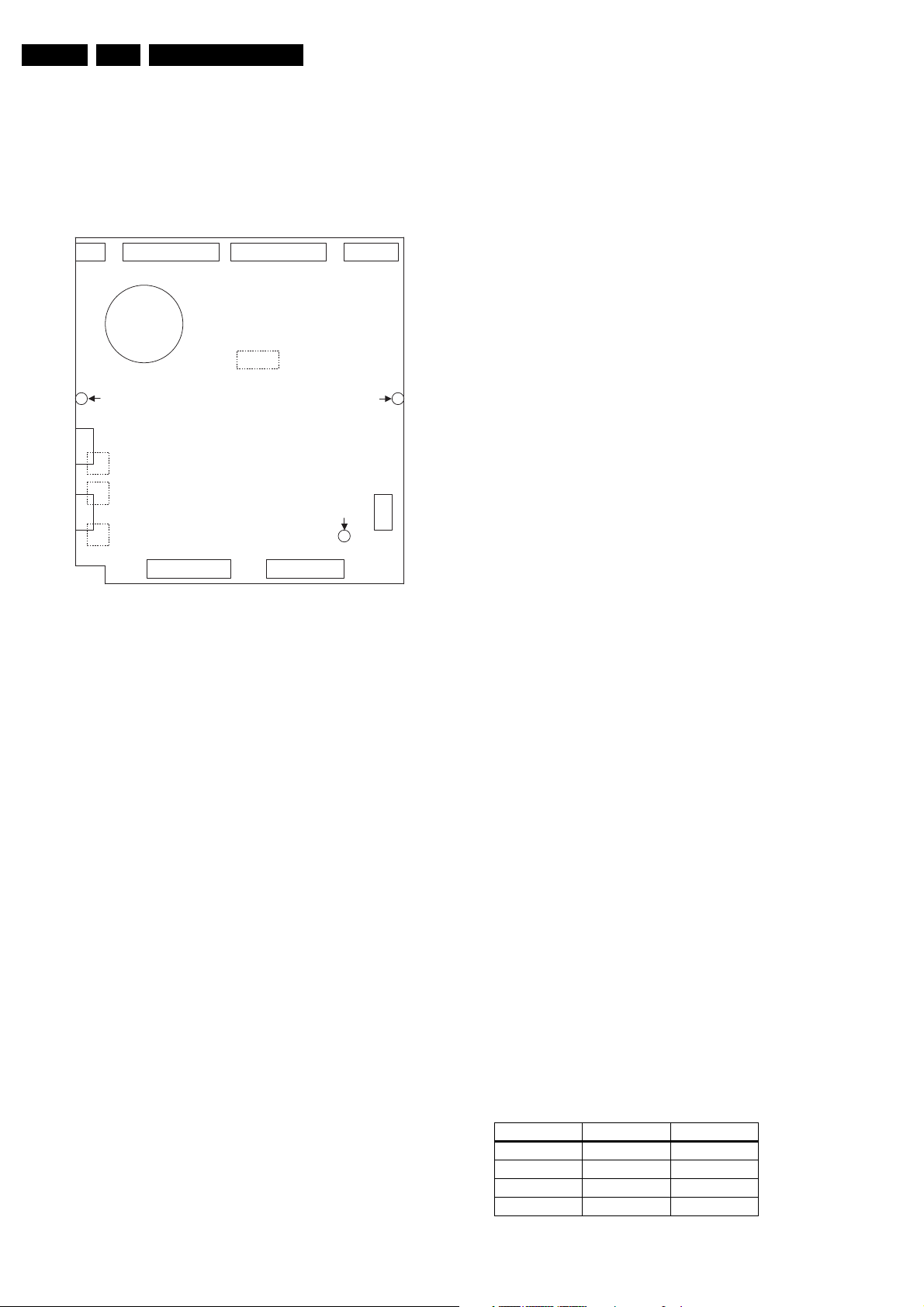

Table 1-1

Parameter Min Max

VIH (V) 2.0 VIL (V) - 0.8

VOH (V) 2.4 VOL (V) - 0.4

LVTTLLow voltage transistor-transistor logic (3.3V logic)

Page 3

Technical Specifications

EN 3SD-5.31SL 1.

Caution: Exceeding the absolute maximum rating will cause

damage to the module.

Absolute maximum rating:

VIN = -0.5V to 3.8V

VOUT =-0.5V to 3.8V

Maximum current drive: 4mA

Table 1-2

Parameter Min Max

VIH (V) 2.0 VIL (V) - 0.8

VOH (V) 2.4 VOL (V) - 0.4

I2C

• Inter-IC

• All I2C signals at the module's connectors are 5V levels.

I2S

• Inter-IC sound

• All I2S signals at the module's connectors are at LVTTL

levels.

RS232_COMP

• RS232 compatible specifications

• VIN approximately 3V threshold, 6kohm input resistance

• VOUT = 0 to 5V, 1kohm output resistance

H/L

• 5V logic states

• H = +5V ± 0.5V

•L = 0V ± 0.5V

h/l

• 3.3V logic states

•h = +3.3V ± 0.3V

•l = 0V ± 0.3V

1.3.2 SPDIF out

Function : Digital audio output

Signal : SPDIFOUT

Type : Output according to

IEC60958 or

IEC61937, 1Vp-p,

unbalanced.

1.3.3 Audio PCM (I2S format)

Function : Digital audio

Signal : DA_XCK, DA_BCK,

DA_LRCK,

DA_DATA0,

DA_DATA1,

DA_DATA2,

DA_DATA3

Type : I2S output (33ohm

output resistors, in

series)

1.3.4 Analog Audio

Function : Analog audio, 2-ch

Signal : LT, RT

Type : Analog output with on-

bd. 10k load

1.3.5 Audio mute

Function : Audio mute control for

final analog stage

Signal : MUTE

Type : LVTTL output

Table 1-3

Function MUTE

Mute off LOW

Mute on HIGH

1.3.6 Analog video

Function : Analog video

Signal : CVBS_VID, C_VID,

Y_VID, R_VID (V),

G_VID (Y), B_VID (U)

Type : Output (75ohm output

resistors, in series)

1.3.7 Slow blanking SCART

Function : Slow blanking SCART

(0/6/12)

Signal : SCART0, SCART1

Type : LVTTL output

Table 1-4

Function SCART0 SCART1

TV display HIGH HIGH

TV display LOW HIGH

16:9 aspect ratio HIGH LOW

4:3 aspect ratio LOW LOW

Note: SCART0 & SCART1 are legacy features. They were

used to generate 0/6/12 signal on an ext. A/V bd. However,

most TV/Audio sets have their own Scart control ic & hence

these 2 pins have alternate functions via optional jumpers.

SCART1 shares with I2C_INT & GND; SCART0 pin shares

with SLOT_IN_DETECT.

1.3.8 Slave I2C

Function : Slave I2C bus

(Hardware)

Signal : S_I2C_CL;

S_I2C_DA

Type : I2C

Note: I2C lines are pulled to +5V.

1.3.9 Master I2C

Function : Master I2C bus

(Software)

Signal : M_I2C_CL;

M_I2C_DA

Type : I2C

Note: I2C lines are pulled to +5V.

Page 4

EN 4 SD-5.31SL1.

Technical Specifications

1.3.10 27MHz clock

Function : Output a 27MHz clock

signal

Signal : VCLK

Type : LVTTL output

(100ohm output

resistor, in series)

Note: This VCLK pin has dual functionality. It provides 27 Mhz

when Digital video output is used & as

This VCLK pin has dual functionality. It provides 27 Mhz when

Digital video output is used & as an input for PCM_CLK when

ext. I2S is used. Option jumpers are provided.

Exercise caution when connecting to this line; excessive

loading can cause noise and increase jitter levels & degrade

the quality of SPDIF and I2S signals.

1.3.11 Service bus

Function : Service and

diagnostic bus

Signal : TXD_SER,

RXD_SER

Type : RS232_COMP

(TXD_SER output,

RXD_SER input)

1.3.12 Service activation

Function : To activate service/

diagnostic mode

Signal : SERVICE

Type : LVTTL input

Table 1-5

: Watermark detect and

decode for DVDaudio

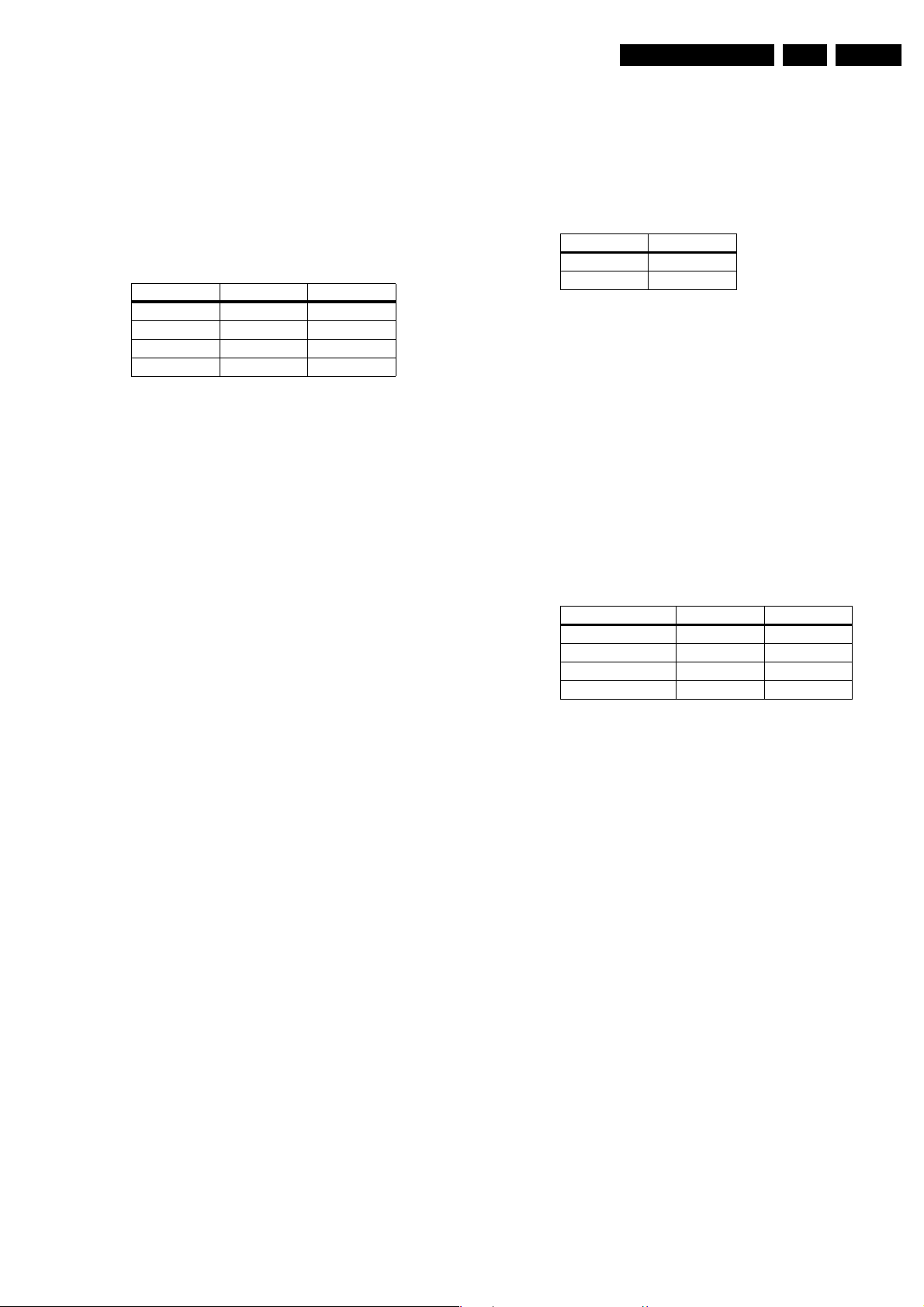

1.4.1 Analog video performance

The video output standard follows the source material. The

OSD can be switched between PAL and NTSC.

The module has 6 analog video outputs in 4 format: CVBS, Y/

C, and RGB (YUV). However, depending on the module

configuration, not all output can be available at the same time.

Table 1-6

Signal name Video format

CVBS_VID CVBS

Y_VID, C_VID Y/C

R_VID (V) / G_VID (Y) / B_VID (U) RGB (YUV)

1.4.2 Option Jumpers:

J1, J2 & J3 hard select the required video output on Connector

1800. Alternatively, pre-determined Software setting, via slash

option, is also possible. DAC's that are not in used should be

turned off.

Note: RGB and YUV component video signals shared the

same lines. Therefore, the module is not able to output both

RGB and YUV at the same time.

Superimposed DC level : 1.2V

Output impedance : 75ohm

Signal-to-noise ratio : better than 65dB

Video bandwidth : 8MHz (± 3dB) /

16MHz (± 3dB) for

progressive scan

Function SERVICE

Service mode LOW (or pulled to ground)

Normal mode HIGH (or unconnected)

Note: This line is pulled to HIGH via 10kohm resistor. A module

reset is required to activate service mode.

1.4 Audio Format (I2S)

Function : Digital audio

Signal : DA_XCK, DA_BCK,

DA_LRCK,

DA_DATA0,

DA_DATA1, DA_A

Additional 2 channels : downmixed stereo/

LtRt - optional

Sampling rate : MPEG-1, MPEG-2,

Dolby Digital, DTS

and DVD-Audio up to

192 kHz

Decoding : MPEG-1 and -2,

Layers I, II, and III

(MP3); MPEG-2 5.1;

: Dolby Digital Class A;

MLP; DTS; Dolby Pro

Logic; HDCD

Copy protection : CPPM for

prerecorded media

(DVD-audio)

: CPRM for recordable

media (DVD-audio)

Copy protection : CSS

: Macrovision Version

7.1.L.1 for NTSC/PAL

interlaced video

outputs

: Macrovision AGC

1.03 for 480P

progressive scan

video output

Page 5

Safety Instructions, Warnings, and Notes

2. Safety Instructions, Warnings, and Notes

EN 5SD-5.31SL 2.

2.1 Safety Instructions

2.1.1 General Safety

Safety regulations require that during a repair:

• Connect the unit to the mains via an isolation transformer.

• Replace safety components, indicated by the symbol ,

only by components identical to the original ones. Any

other component substitution (other than original type) may

increase risk of fire or electrical shock hazard.

Safety regulations require that after a repair, you must return

the unit in its original condition. Pay, in particular, attention to

the following points:

• Route the wires/cables correctly, and fix them with the

mounted cable clamps.

• Check the insulation of the mains lead for external

damage.

• Check the electrical DC resistance between the mains plug

and the secondary side:

1. Unplug the mains cord, and connect a wire between

the two pins of the mains plug.

2. Set the mains switch to the 'on' position (keep the

mains cord unplugged!).

3. Measure the resistance value between the mains plug

and the front panel, controls, and chassis bottom.

4. Repair or correct unit when the resistance

measurement is less than 1 MΩ.

5. Verify this, before you return the unit to the customer/

user (ref. UL-standard no. 1492).

6. Switch the unit ‘off’, and remove the wire between the

two pins of the mains plug.

2.1.2 Laser Safety

This unit employs a laser. Only qualified service personnel may

remove the cover, or attempt to service this device (due to

possible eye injury).

2.2 Warnings

2.2.1 General

• All ICs and many other semiconductors are susceptible to

electrostatic discharges (ESD, ). Careless handling

during repair can reduce life drastically. Make sure that,

during repair, you are at the same potential as the mass of

the set by a wristband with resistance. Keep components

and tools at this same potential. Available ESD protection

equipment:

– Complete kit ESD3 (small tablemat, wristband,

connection box, extension cable and earth cable) 4822

310 10671.

– Wristband tester 4822 344 13999.

• Be careful during measurements in the live voltage section.

The primary side of the power supply (pos. 1005), including

the heatsink, carries live mains voltage when you connect

the player to the mains (even when the player is 'off'!). It is

possible to touch copper tracks and/or components in this

unshielded primary area, when you service the player.

Service personnel must take precautions to prevent

touching this area or components in this area. A 'lightning

stroke' and a stripe-marked printing on the printed wiring

board, indicate the primary side of the power supply.

• Never replace modules, or components, while the unit is

‘on’.

2.2.2 Laser

• The use of optical instruments with this product, will

increase eye hazard.

• Only qualified service personnel may remove the cover or

attempt to service this device, due to possible eye injury.

• Repair handling should take place as much as possible

with a disc loaded inside the player.

• Text below is placed inside the unit, on the laser cover

shield:

Laser Device Unit

Type : Semiconductor laser

GaAlAs

Wavelength : 650 nm (DVD)

: 780 nm (VCD/CD)

Output Power : 20 mW (DVD+RW

writing)

: 0.8 mW (DVD

reading)

: 0.3 mW (VCD/CD

reading)

Beam divergence : 60 degree

Figure 2-1

Note: Use of controls or adjustments or performance of

procedure other than those specified herein, may result in

hazardous radiation exposure. Avoid direct exposure to beam.

CAUTION VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID EXPOSURE TO BEAM

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING VED ÅBNING UNDGÅ UDSÆTTELSE FOR STRÅLING

ADVARSEL SYNLIG OG USYNLIG LASERSTRÅLING NÅR DEKSEL ÅPNES UNNGÅ EKSPONERING FOR STRÅLEN

VARNING SYNLIG OCH OSYNLIG LASERSTRÅLNING NÄR DENNA DEL ÄR ÖPPNAD BETRAKTA EJ STRÅLEN

VARO! AVATTAESSA OLET ALTTIINA NÄKYVÄLLE JA NÄKYMÄTTÖMÄLLE LASER SÄTEILYLLE. ÄLÄ KATSO SÄTEESEEN

VORSICHT SICHTBARE UND UNSICHTBARE LASERSTRAHLUNG WENN ABDECKUNG GEÖFFNET NICHT DEM STRAHL AUSSETSEN

DANGER VISIBLE AND INVISIBLE LASER RADIATION WHEN OPEN AVOID DIRECT EXPOSURE TO BEAM

ATTENTION RAYONNE MENT LASER VISIBLE ET INVISIBLE EN CAS D'OUVERTURE EXPOSITION DANGEREUSE AU FAISCEAU

!

Figure 2-2

2.2.3 Notes

Dolby

Manufactered under licence from Dolby Laboratories. “Dolby”,

“Pro Logic” and the double-D symbol are trademarks of Dolby

Laboratories. Confidential Unpublished Works. ©1992-1997

Dolby Laboratories, Inc. All rights reserved.

Figure 2-3

Trusurround

TRUSURROUND, SRS and symbol (fig 2-4) are trademarks of

SRS Labs, Inc. TRUSURROUND technology is manufactured

under licence frm SRS labs, Inc.

Figure 2-4

Page 6

EN 6 SD-5.31SL3.

3. Directions for Use

There is no DFU available

Directions for Use

Page 7

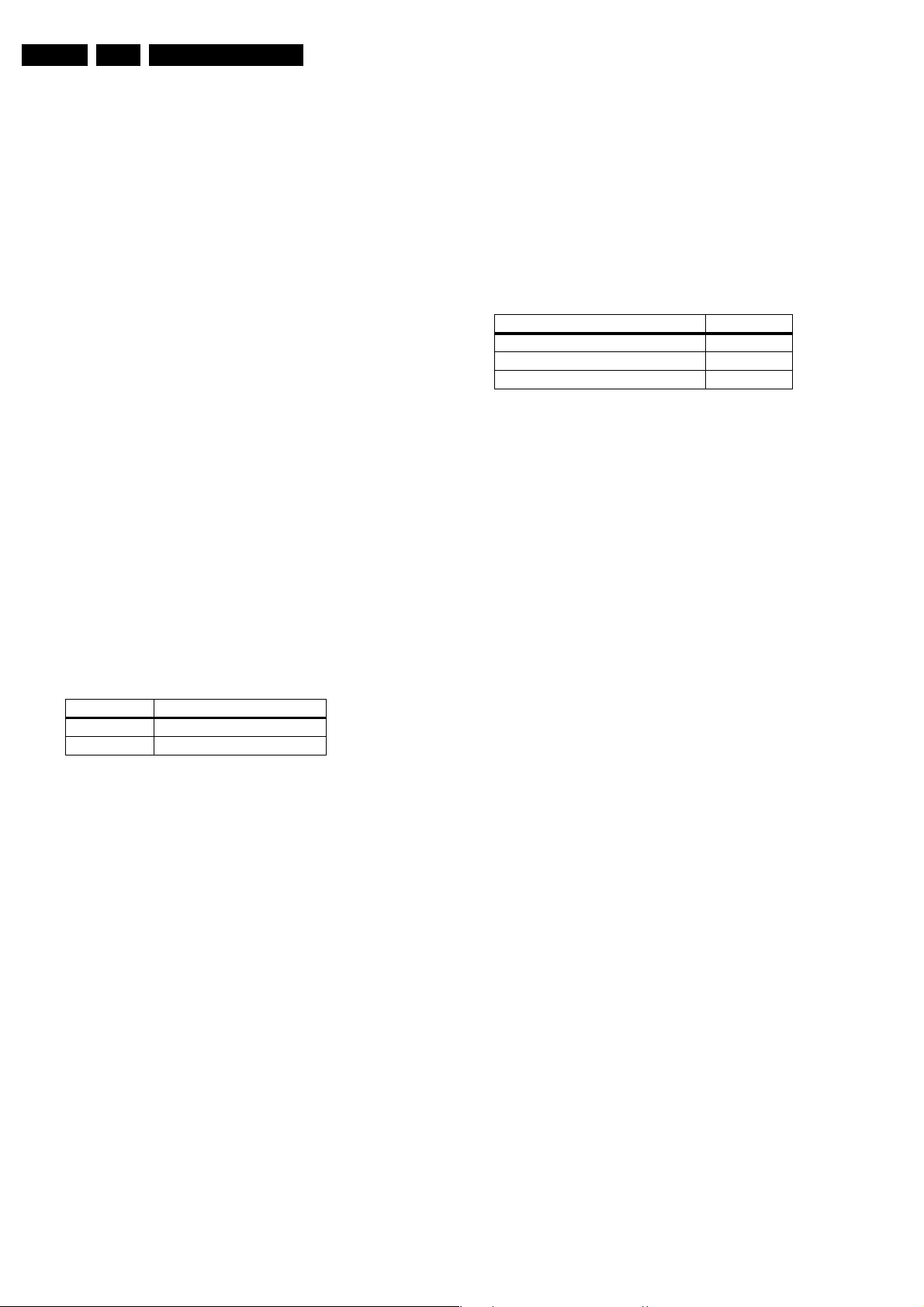

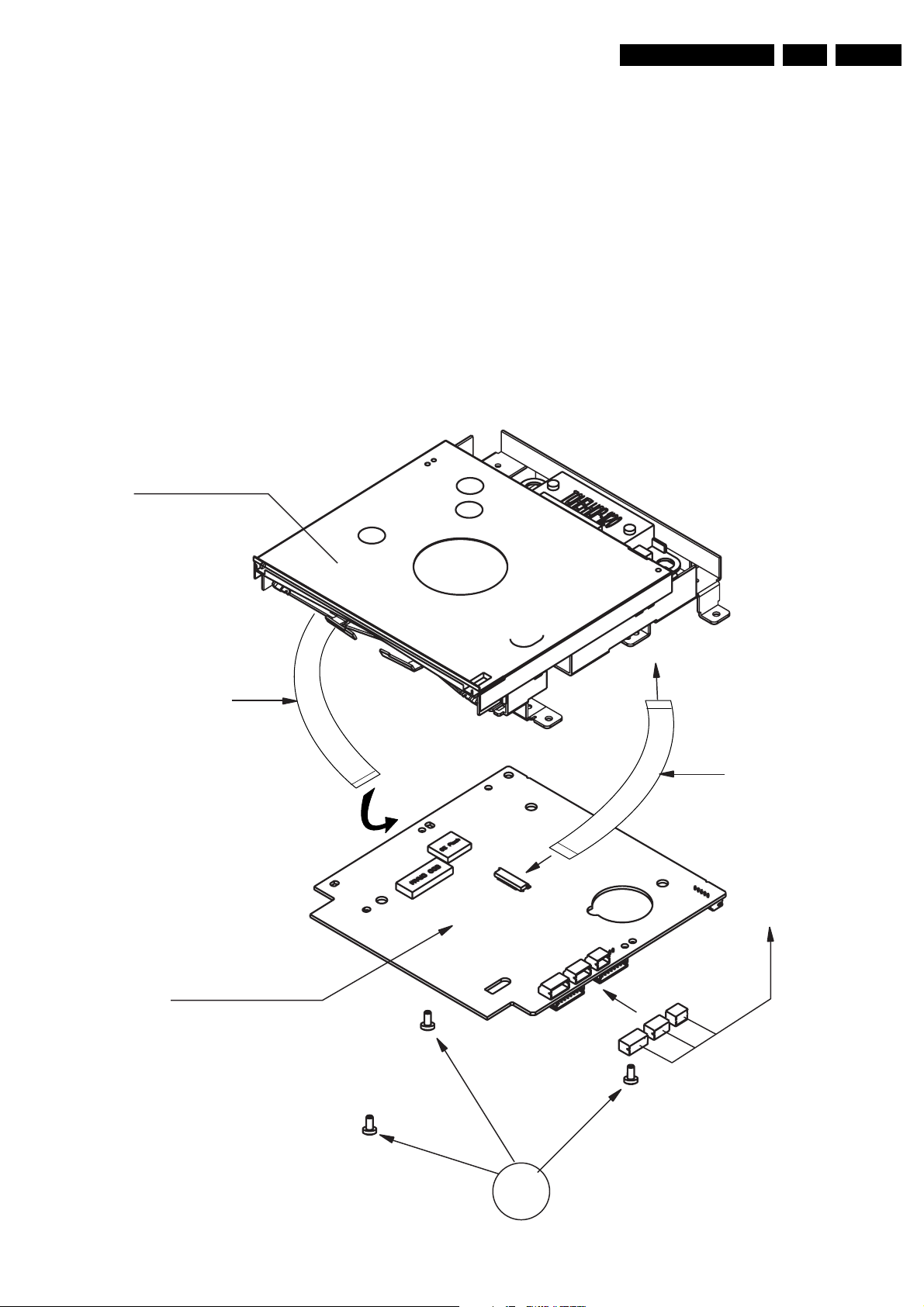

4. Mechanical Instructions

4.1 Dismantling Instruction

Dismantling Instruction

1. Unplug 3 conn [C] from Monoboard [D].

2. Unlock conn 1100 on Monoboard [D] and gentlely unplug Flex [B].

3. Remove 3 screws [F].

4. Separate Monoboard [D] gentlely from loader [E] and beware of the Flex [A].

5. Unlock conn 1001 on the Monoboard [D] and gentlely unplug Flex [A].

Slot-in Loader [E]

Mechanical Instructions

EN 7SD-5.31SL 4.

Flex [B]

Monoboard [D]

To Loader OPU

Flex [A]

from Loader

Conn [C]

Figure 4-1

F

CL 36532043_021.eps

220503

Page 8

EN 8 SD-5.31SL4.

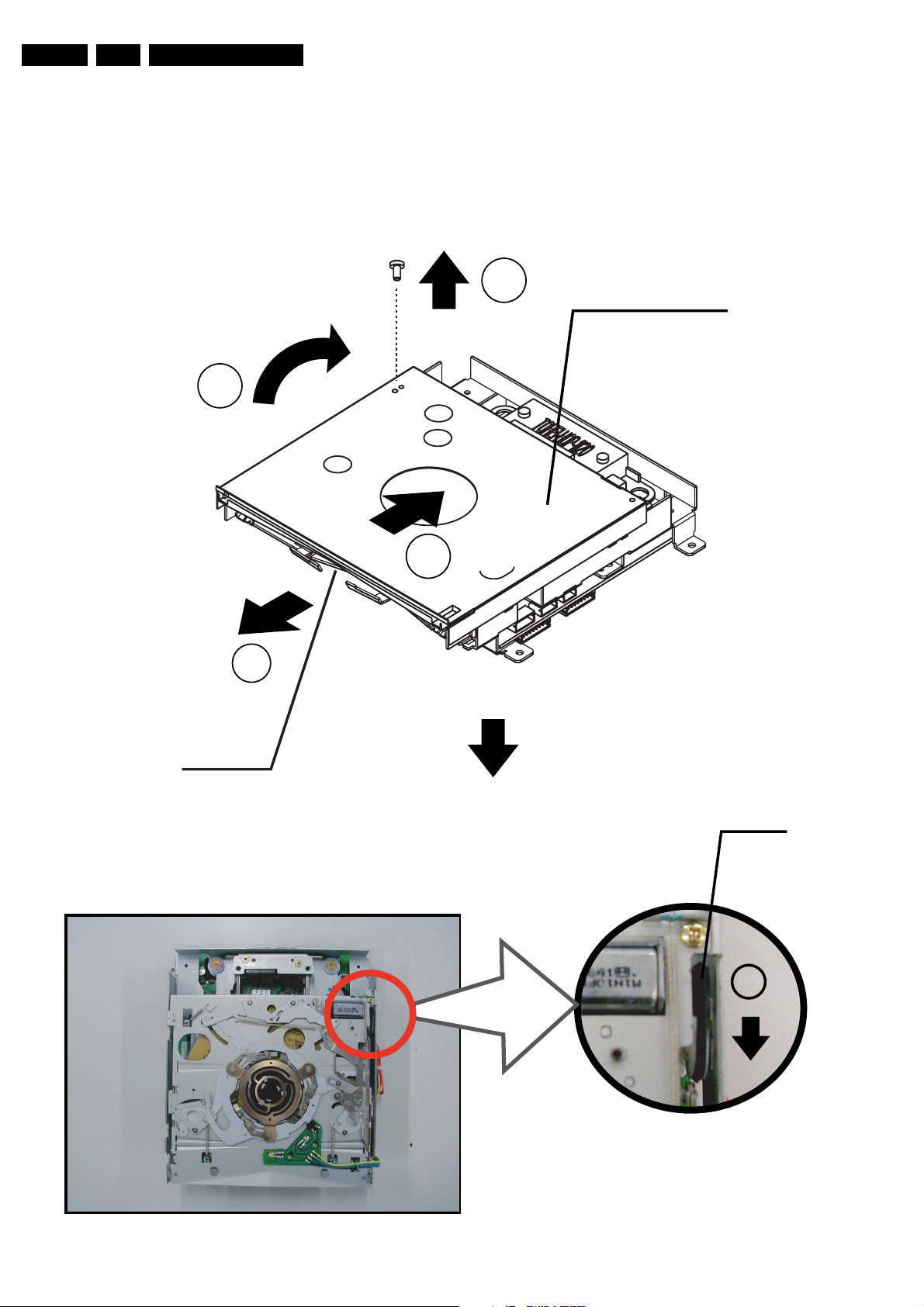

4.1.1 Manually Eject the Disc

See Figure 4-2 eject the disc manually.

1. Remove screw,

2. Slide top cover backward,

3. Flip top cover and remove it,

4. Turn the belt in the anti-clockwise direction with your thumb

till the disc is ejected,

5. Gently pull the disc out.

Mechanical Instructions

3

5

2

1

Top Cover

Slot

Belt

4

CL 36532043_022.eps

020603

Figure 4-2 Manually eject the disk

Page 9

Mechanical Instructions

solder joint

EN 9SD-5.31SL 4.

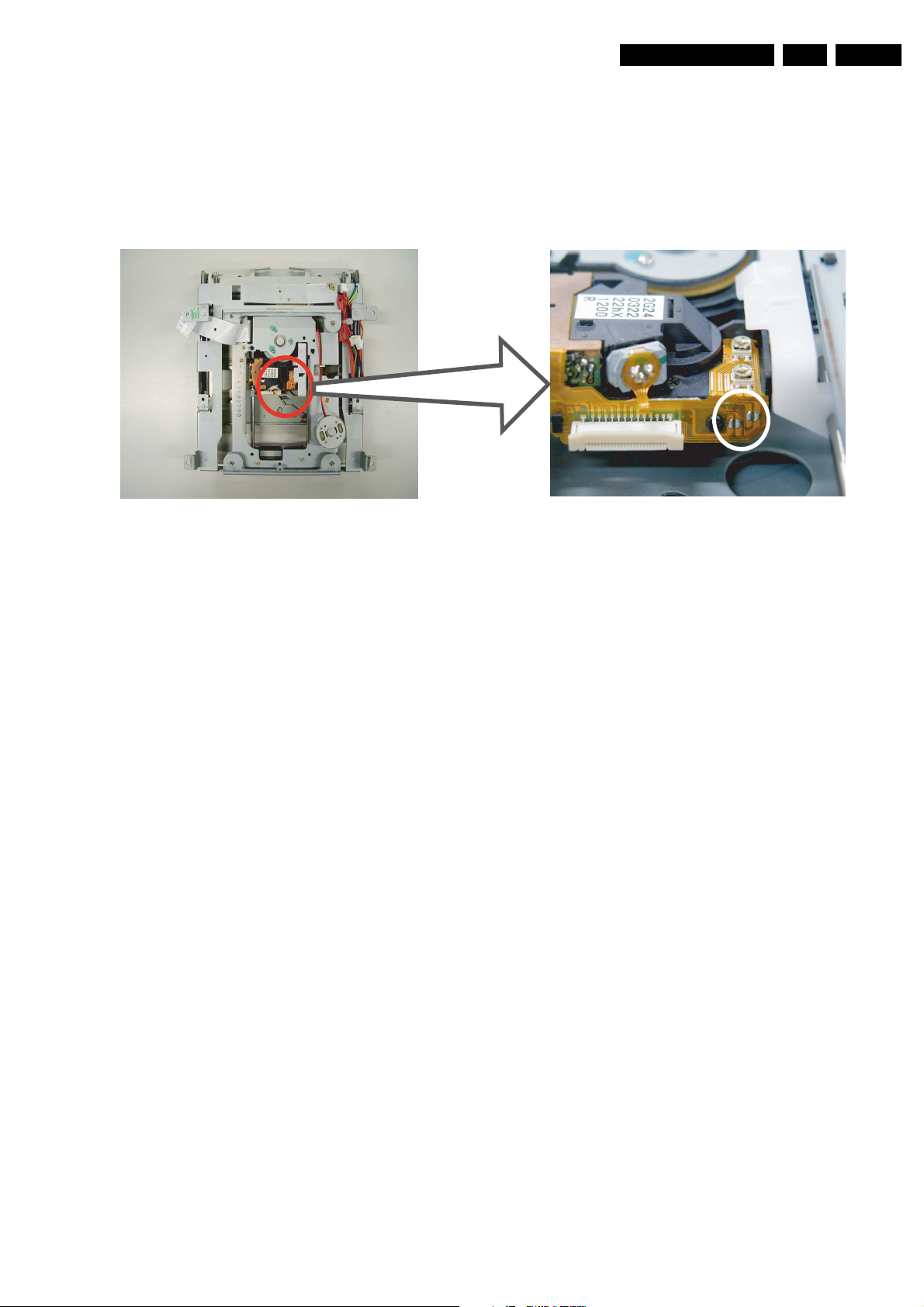

4.2 Service Hints

4.2.1 Repair tips

DVD Module SD5.31SL

The DVD module is an integrated unit of TOHEI SLOT-IN

loader and Monoboard.

TOHEI SLOT-IN Loader

The loader is a non-repairable unit and in case of failure, it has

to be replaced with a new loader.

When replacing with a new Slot-in loader, two solder joints

have to be removed after connecting the OPU flex foil to the

Monoboard. The solder joints which short circuits the laser

diodes to ground are for protection against ESD. Refer to

Figure "ESD solder joint" for location of solder points.

CL 36532043_018.eps

020603

Monoboard

The Monoboard has to be repaired down to components level.

Repair handling of the Monoboard requires a workshop with

sophisticated de-soldering tools.

4.2.2 Change of Slash number setting

The software setting can be change according to the following

procedure:

1. Press PLAY< 159>

2. Enter the 8-digit code <2><2><2><0><0><5><0><0> on

the remote control.

3. Press PLAY.

4. The change should effect immediately with information

indicated on TV screen.

4.2.3 Software upgrade via Download disc

Both the application and servo software can be flashed into the

DVD player by means

of a CD-ROM disc. The CD-ROM disc has to be made with a

CD writer SW.

Application software

1. Insert the Upgrade disc into the player.

2. The upgrading operation will start automatically.

3. Once the upgrading process finishes, the player will

automatically eject the disc.

4. Remove the Upgrade disc.

5. The player will be restarted automatically and display on

TV screen will show

Figure 4-3 ESD solder joint

recommended to write only this file into the disc &

write it in DAO ie. Disc At Once mode.

2. Upgrading procedure

3. Power-on the module.

4. Insert the Upgrading disc. Make sure that this is the first

disc that the module sees, otherwise the module will treat

it as a general cd-rom disc & not perform the upgrade.

5. The upgrading process takes about 10 secs. & when it

finishes, the disc will be ejected.

6. Power sequence the module for the new code to take

effect.

Servo software

1. First, make the CD-R/CD-RW:-

• Disc format

– The disc format must be CD-ROM Mode 1 and

ISO9660 format.

• Writing mode

– The volume name (Label) of the disc must be

"ALI_CODE" & the file name of the upgrading

firmware must be "PS57.BIN". You must put the

file as the first item in the disc.Highly

Page 10

EN 10 SD-5.31SL4.

4.2.4 Verify setting

To check that the setting has change successfully.

1. Press button on the remote control while disc tray is open.

2. The texts will appear on the TV screen. That is how it looks

like.

– Copyright©

– Philips 2002-03

– SD5.31-34

– 30May2003

– 15:42

– 22200500

– A1133

– C3091

– 100305R3424

In the texts, the following numbers refer to:

• SD5.31-34 ==> refer to Application software version

• 30May2003 ==> refer to date software was upgraded

• 15:42 ==> refer to time software was upgraded

• 22200500 ==> refer to Slash version

• 100305R3424 ==> refer to servo software version

4.2.5 Test disc

The following test discs are recommended for use to test the

playability of the player.

• DVD disc: MPTD CVP 02.18- 12nc 7104 099 91691

• Audio disc (CDDA): Subchassis 8a Test disc- 12nc 7104

099 28362

Mechanical Instructions

4.2.6 Ejecting Disc

When ejecting disc is not possible using remote control

• Short circuit test land [F220] to ground when power

supplies are still present with assumption the front end is

not faulty.

• When above is not possible, ejecting of the disc has to be

done manually. Refer to instruction "Manually Ejecting of

disc".

4.2.7 ComPair

For assistance with the repair process of the Monoboard,

electronic fault finding guidance has been developed. This

program is called ComPair. This ComPair program is available

on CDROM. The version of the CDROM for repair of the

monoboard is V1.3 or higher and can be ordered with

codenumber 4822 727 21637. The procedure for registration is

explained in the help file of the program and in the CDROM

booklet. The cable to connect the Monoboard with a PC can be

ordered with codenumber: 3122 785 90017. All the hardware

and software requirements of the systems, necessary for

working with ComPair, are described on the CDROM

Page 11

Test Instructions Mono Board SD5.31SL

PM3380B

5. Test Instructions Mono Board SD5.31SL

5.1 General

EN 11SD-5.31SL 5.

• Impedance of measuring-equipment should be > 1MΩ.

• Most tests have to be done by software commands.

Together with the software command you will find a Ref.#

nbr. This is the number of the diagnostic nulceus used for

this test. More detailed information can be find in the

chapter “Diagnostic Nuclei”.

• Levels: Most measurements are digital measurements.

The signal levels specification in this document are defined

in the chapter Technical Specifications.

• All the waveforms measurement carried out in these test

instruction will be base on the testpoint indicated in the

Monoboard schematic diagram in the service manual.

5.2 General Start-up Measurements

5.2.1 Supply Check:

Table 5-1 Supply check

No Testland Signal Name

1 F810 +3V3 3.15V 3.30V 3.50V

2 F811 +5V 4.75V 5.00V 5.25V

3 F813 +12V 10.0V 12.0V 13.2V

The monoboard operates in power-off and power-on mode

only. There is no standby mode. In power-off mode, the

monoboard does not respond to any communication or signals.

Reset is via an internal reset circuit, which are tied to the +3V3

supply. To ensure proper power recycling, the following timing

should be observed:

+12V

+12VSTBY

+3.3V

+5V

Internal

Reset

Modes:-

+12V

0V

+12V

0V

+3.3V

0V

+5V

0V

3ms min

High

Low

Power-off

50ms min

Reset mode Operational mode

DC Voltage (V)

Min Typ Max

CL 36532043_044.eps

Standby mode

270503

ch1

ch2

T

1

2

CH1 1.00V=

CH2 1.00V= MTB 500ms 4.96dv ch1+

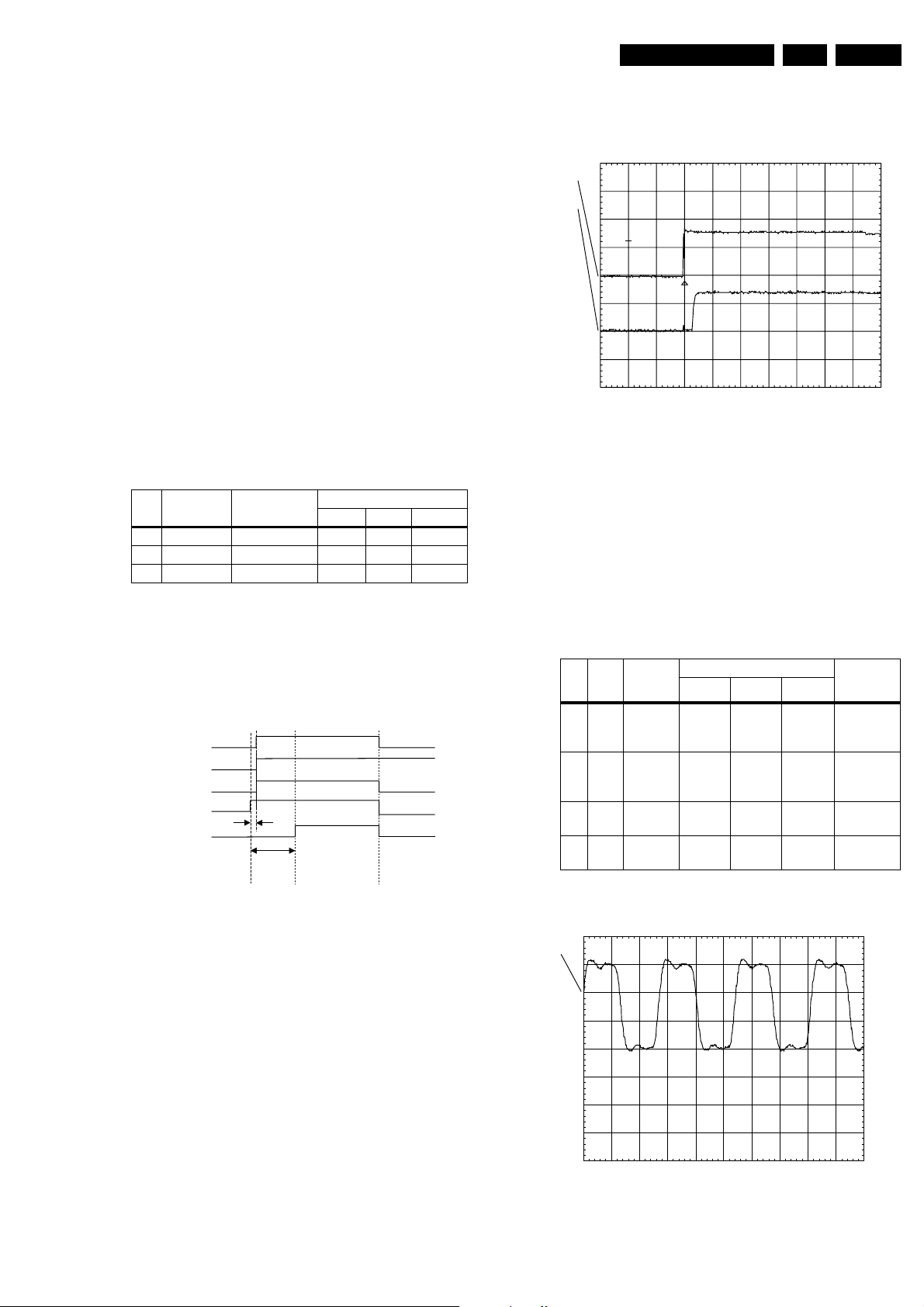

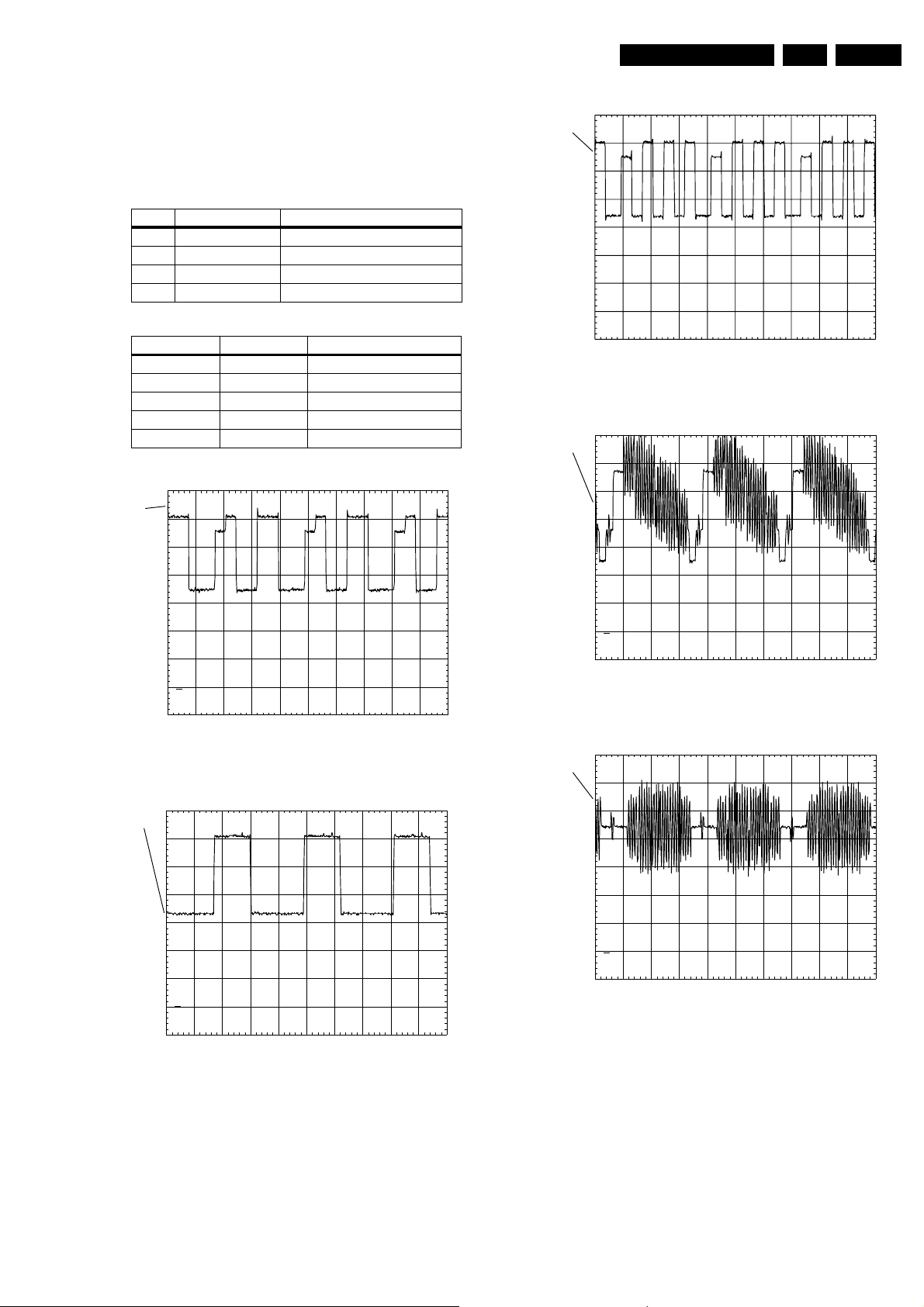

Figure 5-2 Reset

NB: The SYS_RST rising edge,CH2, should be at least

100msec after the +3V3ST (refer to CH1 Figure Reset).

If the reset input does not go high then check the reset circuit

around IC7500.

5.2.3 Clock Check

To check the correct functioning of the ZIVA, we first have to

check the presence of all clocks.

Table 5-2 Clock check

Test

No

land

Signal

name

Frequency (MHz)

Min Typ Max

1 F401 XTAL 13.4993 13.5000 13.5007

2 F209 ALI_CLK 33.6994 33.8688 34.0382

3 F421 DA_XCK 18.063 18.432 18.801

4 F502 SD_CLK 119.070 121.500 123.930

CL 36532043_067.eps

030603

Descrip-

tion

Back-end

clock

(± 50ppm)

Front-end

clock

(± 0.5%)

Audio

clock

SDRAM

clock

5.2.2 Reset Check:

Figure 5-1 Timing chart

All tests that require the diagnostic software should be

performed in power-on mode only.

To ensure a proper start-up of the monoboard, the back-end

reset signal SYS_RST is required at the ZIVA-5 input (testpoint

F501) after power-on.

To check the reset timing, measure the SYS_RST (testpoint

F501) and the +3V3ST supply (testpoint F503), reset circuit

trigger signal.

PM3380B

ch1 ch1 freq 18.5Mhz

1

CH1 1.00V= MTB 20.0ns ch1+

Figure 5-3 DA_XCK

CL 36532043_057.eps

030603

Page 12

EN 12 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

PM3380B

ch1 ch1 freq 13.5MHz

1

CH1 1.00V= MTB 50.0ns ch1+

Figure 5-4 XTAL

PM3380B

ch1 ch1 freq 123MHz

1

CL 36532043_083.eps

030603

Table 5-3 PC connection

Connector pin Signal

1702-1 TXT_SER (service port/UART transmit)

1702-2 SERVICE (service/normal mode select)

1702-3 RXD_SER (service port/UART receive)

1702-4 Not in use

1702-5 GND

1702-6 Not in use

1702-7 +5V_SER

Now start the terminal program. Make sure that the service-pin

(pin 1702-2) of the µP is pulled low.

The terminal program of your PC should now display: “DVDv6

Diagnostic software version ...”. This message already means

that the µP is running. This is also an indication that the first

basic nucleus (nucleus number 1) has been executed during

diagnostic start-up. The other commands can be carried out by

selecting the “command input” and simply type the reference

nbr. to do the test or select the “Menu - driven” test.

To be sure that the µP is able to run the diagnostic software,

serial port will be checked during start-up.

Table 5-4 Serial port check

Ref. # Reference Name Remark

(1) BasicSpAcc Serial port Access test/

initialisation

CH1 1.00V= MTB 5.00ns ch1+

Figure 5-5 SD_CLOCK

PM3380B

ch1: freq= 33.8MHz

ch1

CH1 2.00 V= MTB50.0ns ch1+

Figure 5-6 ALI_CLOCK

5.3 µP Environment:

5.3.1 General:

CL 36532043_072.eps

030603

CL 36532043_070.eps

050603

With this test, the serial communication is checked in both

directions.

5.3.2 Memory Check:

The Flash can be check for failure with the PapChksFl

command.

Table 5-5 Memory check

Ref. # Command Name Remark

6 PapChksFl Checksum FLASH

The PapChksFI calculate and verify checksum of the FLASH.

This includes the entire binary ROM image checksum.

5.4 General I/O Port & Peripherals Check

5.4.1 I2C Bus/NVRAM Check

To access the NVRAM, the I2C bus is used. So by writing and

reading to the NVRAM the chip and the bus is checked. With

next commands a certain byte is written to the NVRAM. The

original information will always be written back into the

NVRAM.

Table 5-6 I2C/NVRAM check command

Ref. # Command Name Remark

11 PapI2cNvram I2C NVRAM access

All the tests are carried out by diagnostic software. To start the

diagnostic software, connect a PC to the serial bus of the ZIVA.

Use connector 1702 for this connection.

The complete NVRAM can also be checked on failures by

writing to all addresses and reading back. This test takes a long

time (110 sec).

Page 13

Test Instructions Mono Board SD5.31SL

PM3380B

EN 13SD-5.31SL 5.

Table 5-7 NVRAM Write/Read check command

Ref. # Command Name Remark

15 PapNvramWrR NVRAM Write Read

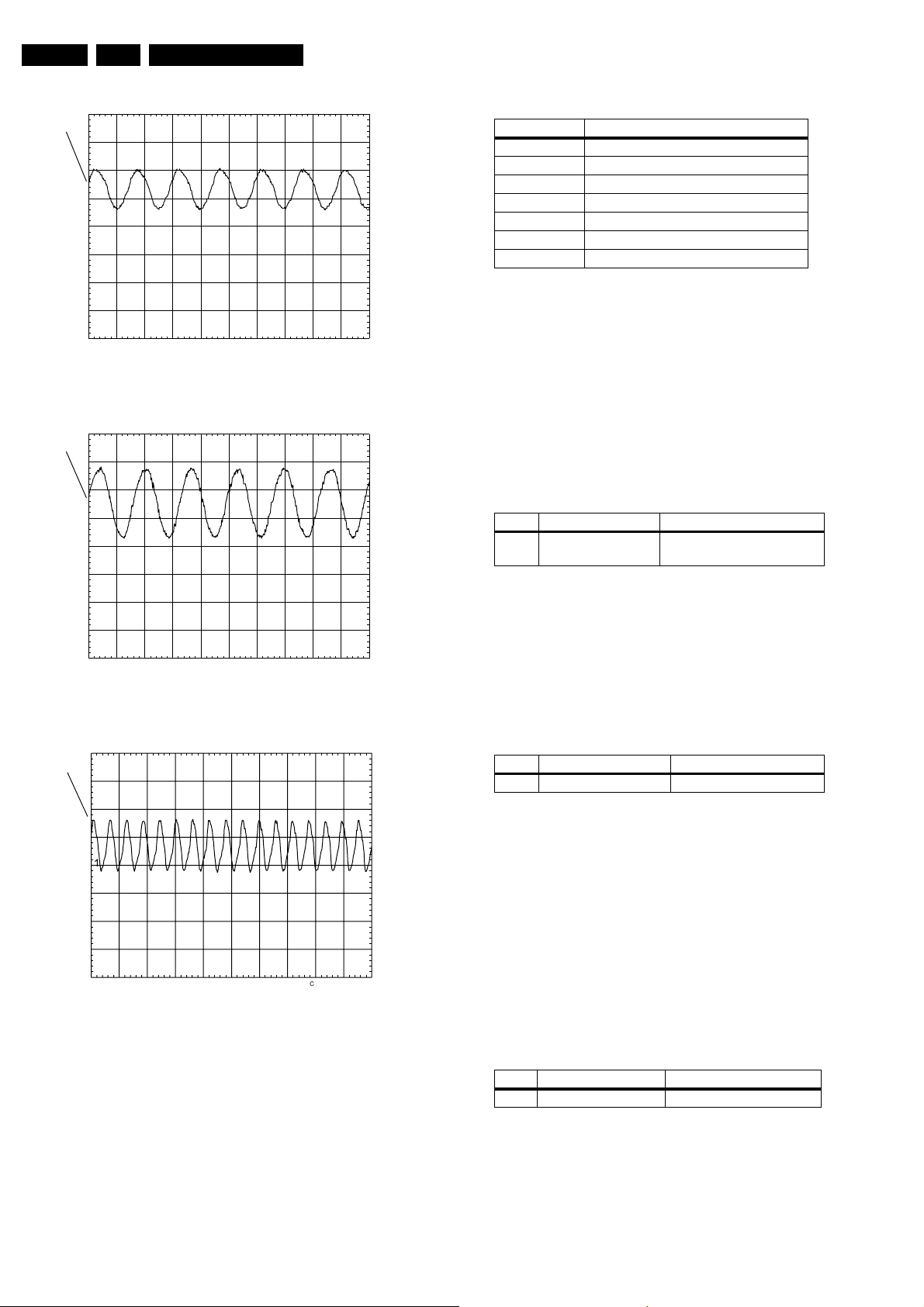

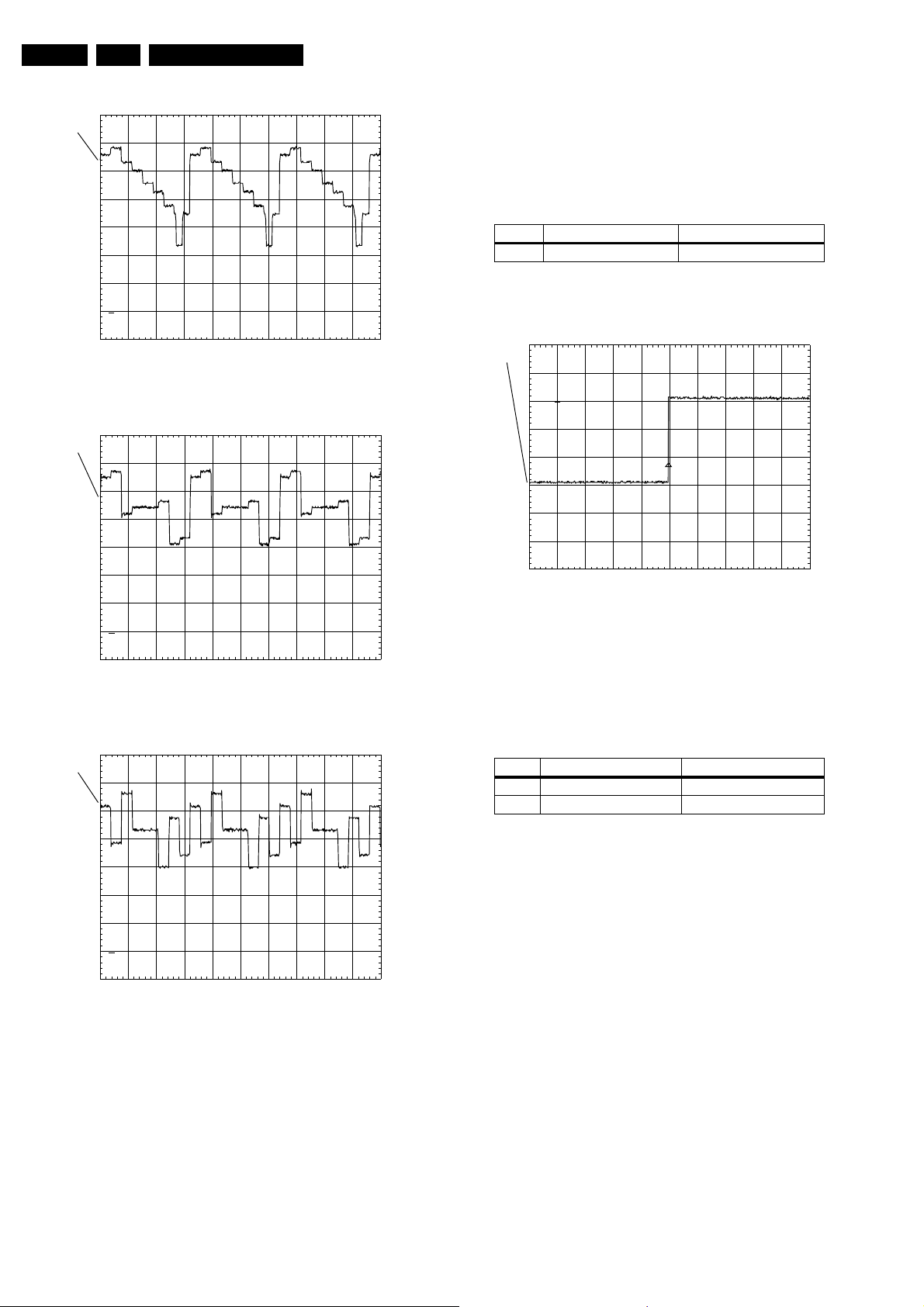

5.4.2 Audio Clock Check

The internally generated Audio clock can be set to either 44.1

kHz (CD_DA), 48 kHz (DVD) or 96 kHZ (DVD). To check the

different mode, use the following commands and measure the

waveform as correct operation cannot be detected by the

Diagnostic Software.

Table 5-8 Audio clock check

Command

Ref #

Name Remark

8a PapSgsAclk

Cdda

Internal PLL

CLK in CD-DA

Test

point Frequency

F421 16.934 MHz

mode (Fig 5-4)

8b PapSgsAclk

Dvd

Internal PLL

CLK in DVD

F421 18.432 MHz

mode (Fig 5-5)

8c PapSgsAclk

Dvd96

Internal PLL

CLK in DVD

F421 36.864 MHz

mode (Fig 5-6)

± 0.02%

± 0.02%

± 0.02%

PM3380B

ch1 ch1 freq 36.9MHz

1

CH1 1.00V= MTB 20.0ns ch1+

Figure 5-9 Internal PLL CLK in DVD96kHz mode

5.4.3 Audio Mute Check

Switch on the Mute circuit by sending next command:

Table 5-9 Audio mute ON check command

Ref. # Command Name Remark

19a AudioMuteOn AudioMuteOn

CL 36532043_060.eps

030603

ch1 ch1 freq 18.5Mhz

1

CH1 1.00V= MTB 20.0ns ch1+

Figure 5-7 Internal PLL CLK in CDDA mode

PM3380B

ch1 ch1 freq 18.4MHz

1

CL 36532043_057.eps

030603

Check the Mute output again at testpoint F603: 3V3 ± 10%

Switch off the Mute circuit by sending next command

Table 5-10 Audio mute OFF check command

Ref. # Command Name Remark

19a AudioMuteOff AudioMuteOff

Check the Mute output at testpoint F603: 0V ± 0.3V

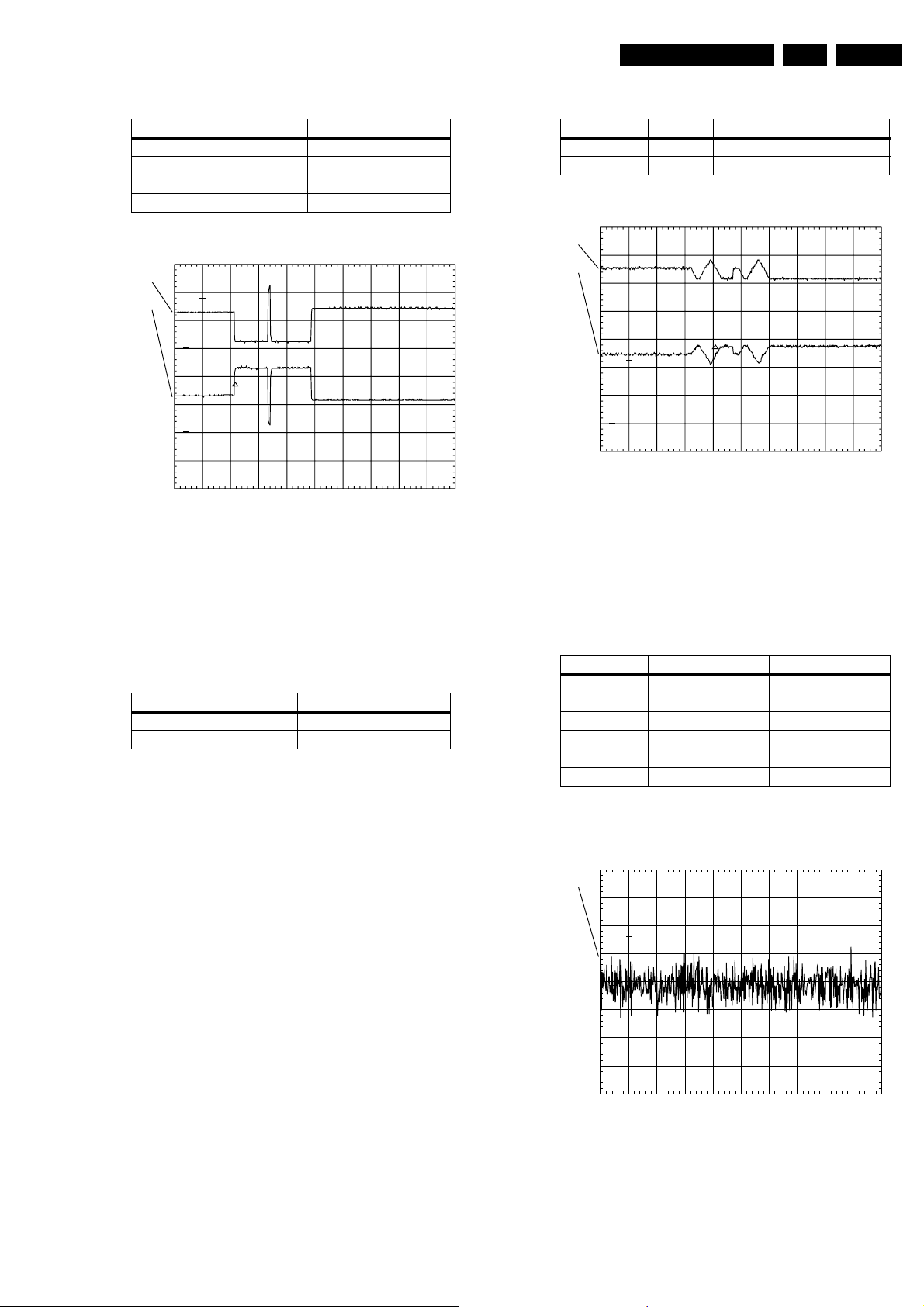

5.4.4 Audio I2S Check

To check the audio output from the internal audio DAC on the

Monoboard, execute the following commands and observe the

I2S audio outputs for both sine and pink noise.

Table 5-11 Audio I2S check commands

Command

Ref. #

21a AudioSineOn Audio Sine

Name Remark Audio outputs

Audio Sine signal On

signal Off

Sine, 1kHz on stereo

Press stop button

20a AudioPinkNoi

seOn

Audio

Pinknoise

Pink Noise on 6

channels

On

20b AudioPinkNoi

seOff

Audio

Pinknoise

Off

CH1 1.0 V= MTB 20.0ns ch1+

CL 36532043_059.eps

Figure 5-8 Internal PLL CLK in DVD48kHz mode

030603

The audio signal (sine or pink noise) will also be present on the

digital ouput (SPDif). This can be checked by connecting an

amplifier with digital input.

Check the I2S output.

Page 14

EN 14 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

Table 5-12 NameTestpointWaveform

Name Testpoint Description

DA_XCK F421 Audio clock

DA_BCK F822 Audio bit clock

DA_DATA0 pin 27/IC7800 Audio data

DA_LRCK F825 Audio word

SPDIF F821 Audio digital out

PM3380B

ch1 ch1 freq 18.5Mhz

1

CH1 1.00V= MTB 20.0ns ch1+

CL 36532043_057.eps

030603

PM3380B

ch1 ch1 freq 48.1kHz

1

CH1 1.00V= MTB 10.0us ch1+

Figure 5-13 DA_LRCK

PM3380B

ch1

T

CL 36532043_056eps

030603

Figure 5-10 DA_XCK

PM3380B

ch1

CH1: freq 2.31Mhz

1

CH1 1.00V = MTB 200ns ch1+

Figure 5-11 DA_BCK

PM3380B

ch1

ch1 freq 255kHz

CL 36532043_054.eps

030603

1

CH1 2.00V= MTB 200ns ch1+

STOP

CL 36532043_079.eps

030603

Figure 5-14 SPDIF

To switch the audio signal OFF, press the STOP button on the

front.

Without A/V board, the switching levels are as follows:

– DA_DATA1,DA_DATA2 and DA_DATA3 switch between

low and high for pink noise. For sine, this is low.

– DA_DATA0, DA_LRCK, DA_XLK and DA_BCK switches

between low and high for both pink noise and sine.

– SPDIF switches between LOW and HIGH

1

STOP

CH1 1.00V= MTB 2.00us ch1+

Figure 5-12 DA_DATA0

CL 36532043_055.eps

030603

Page 15

Test Instructions Mono Board SD5.31SL

EN 15SD-5.31SL 5.

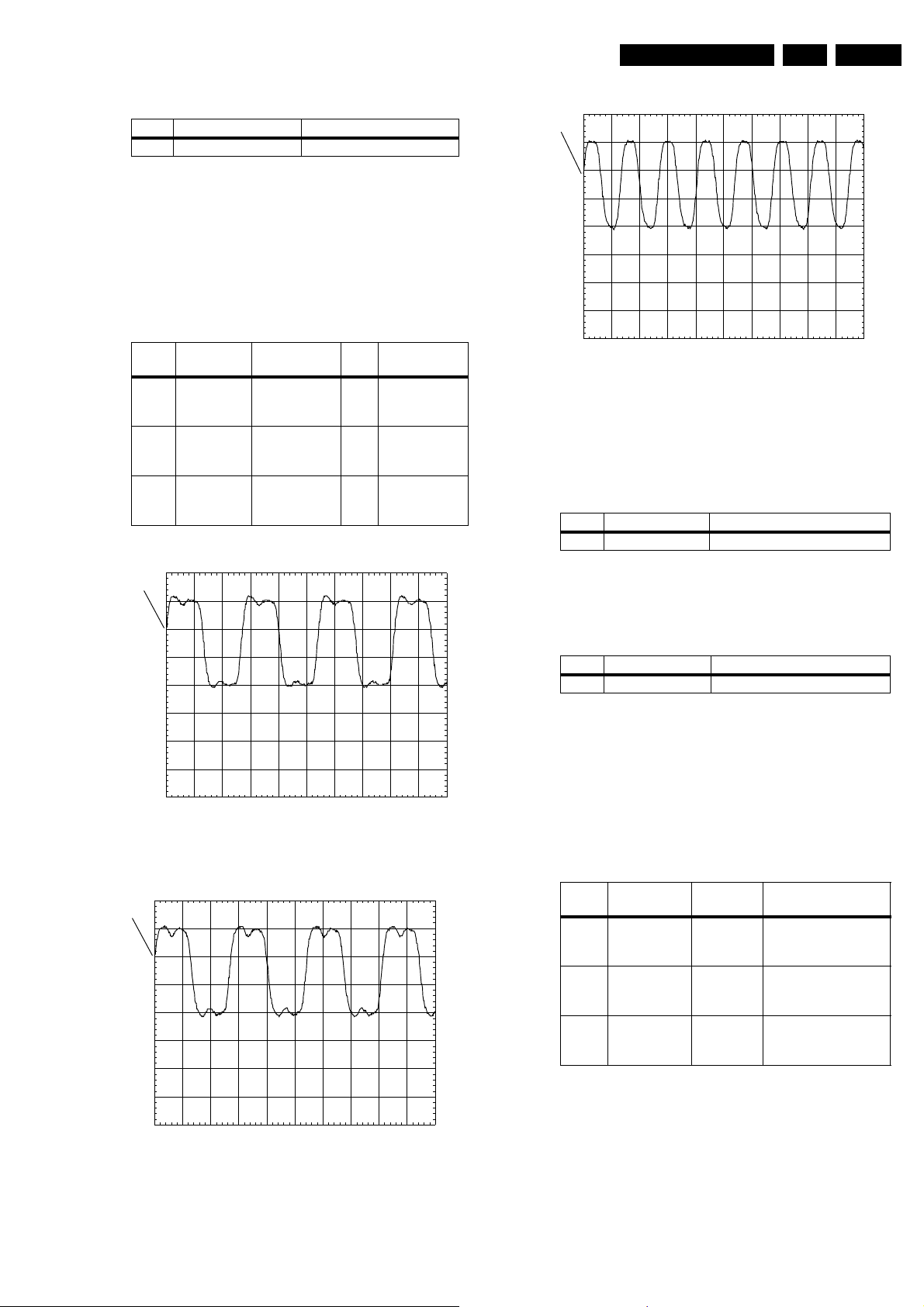

5.5 VIDEO

5.5.1 Video Output Check

Measure the DC voltages at all video-outputs at conn 1800

while the video signal is turned off: 1V ± 10%

Generate a color-bar via next software commands:

Ref. # Command Name Remark

23a VideoColDencOn Colourbar DENC ON

61a VideoColOutRGB Set Video out to RGB

61b VideoColOutYUV Set Video out to YUV

23b VideoColDencOff Colourbar DENC/MPEG OFF

Check video output at the next testpoints:

Name Testpoint Waveform

R_V F817 Refer to Figure R_V

G_Y F816 Refer to Figure G_Y

B_U F815 Refer to Figure B_U

C F819 Refer to Figure C_VIDEO

CVBS F820 Refer to Figure CVBS_VID

PM3380B

ch1

PM3380B

ch1

1-

CH1 500mV= MTB 20.0us ch1+

Figure 5-17 B_U with video out at RGB

PM3380B

ch1

CL 36532043_050.eps

030603

1

CH1 500nV= MTB 20.0us ch1+

Figure 5-15 R_V with video out at RGB

PM3380B

ch1

1

CH1 500mV= MTB 20.0us ch1+

STOP

Figure 5-16 G_Y with video out at RGB

CL 36532043_069.eps

030603

CL 36532043_062.eps

030603

1

CH1 500mV= MTB 20.0us ch1+

Figure 5-18 CVBS_VID

PM3380B

ch1

1

CH1 500mV= MTB 20.0us ch1+

Figure 5-19 C VIDEO

CL 36532043_053.eps

030603

CL 36532043_052.eps

030603

Page 16

EN 16 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

PM3380B

ch1

1

CH1 500mV= MTB 20.0us ch1+

Figure 5-20 G_Y with video out at YUV

PM3380B

ch1

CL 36532043_063.eps

030603

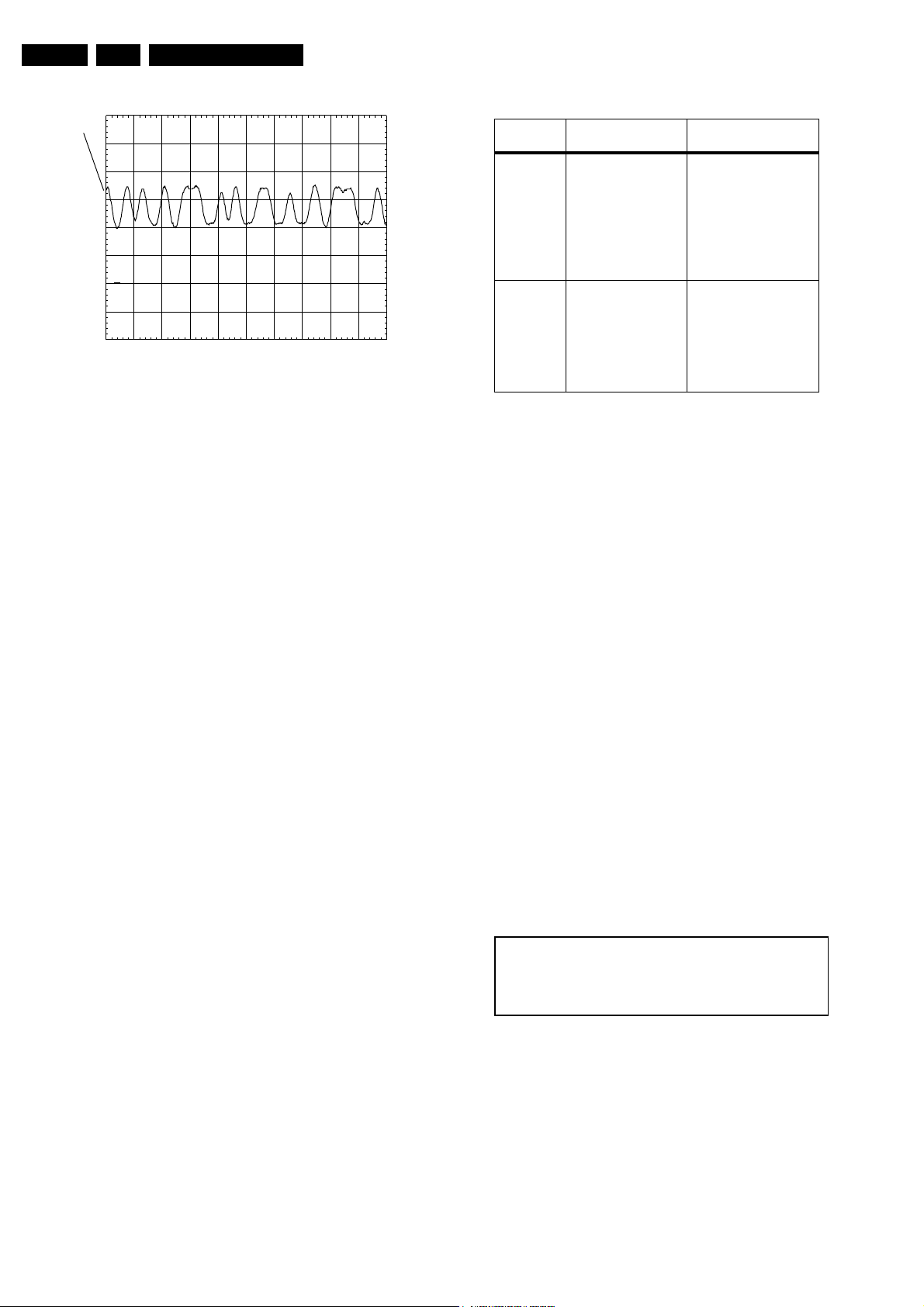

5.6 Servo

5.6.1 General Start-up Measurements:

Reset the Basic Engine part

Table 5-13 Reset basic engine command

Ref. # Command Name Remark

44 BeReset Reset the Basic Engine

Check the Servo Reset (IDERST) waveform at pin 50 / IC7200

goes from high to low after executing BeReset commands.

PM3380B

ch1

T

1

1

CH1 500mV= MTB 20.0us ch1+

Figure 5-21 R_V with video out at YUV

PM3380B

ch1

1

CH1 500mV= MTB 20.0us ch1+

CL 36532043_071.eps

030603

CL 36532043_051.eps

030603

CH1 1.00V= MTB 10.0us 4.96dv ch1+

Figure 5-23 IDERST

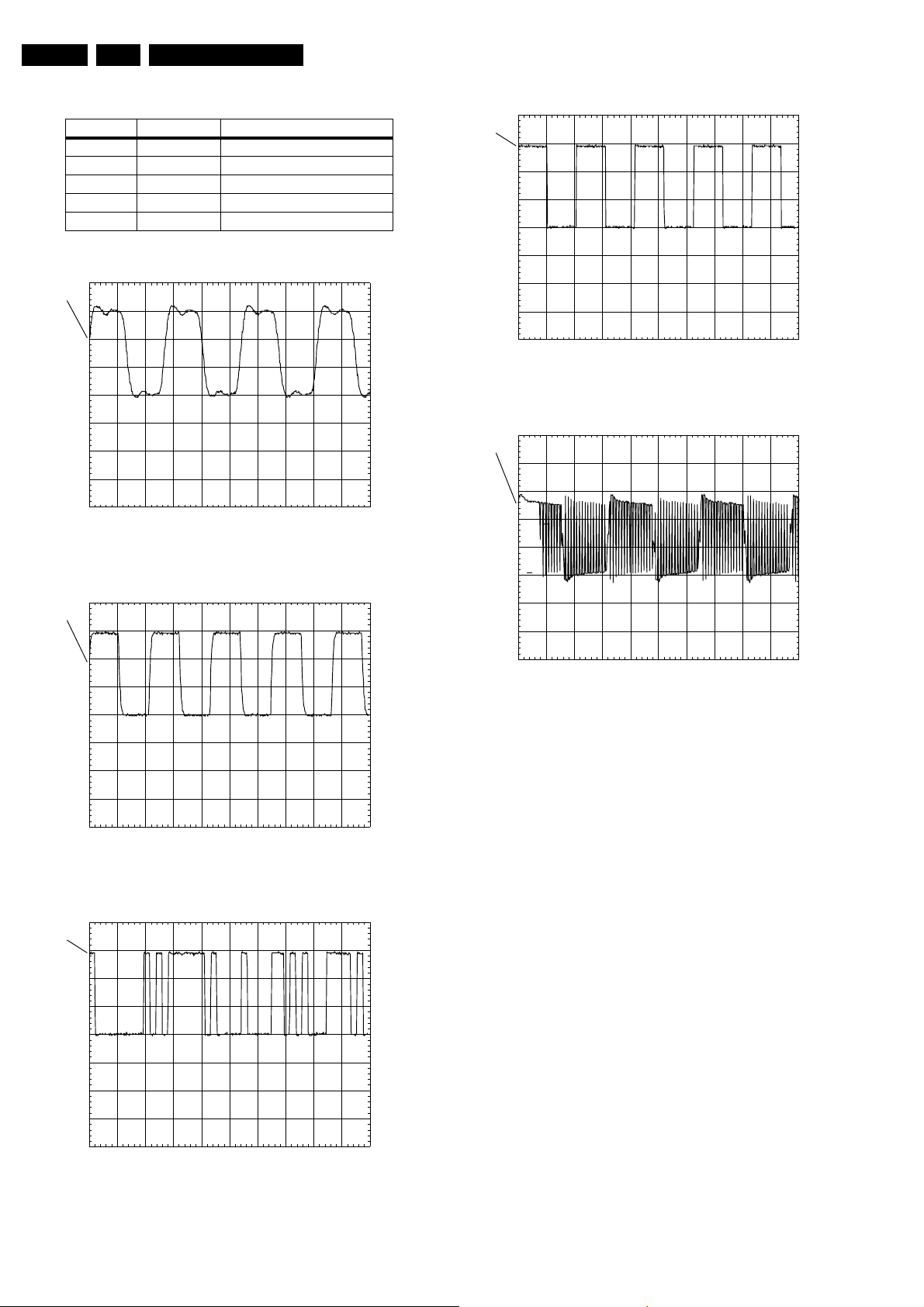

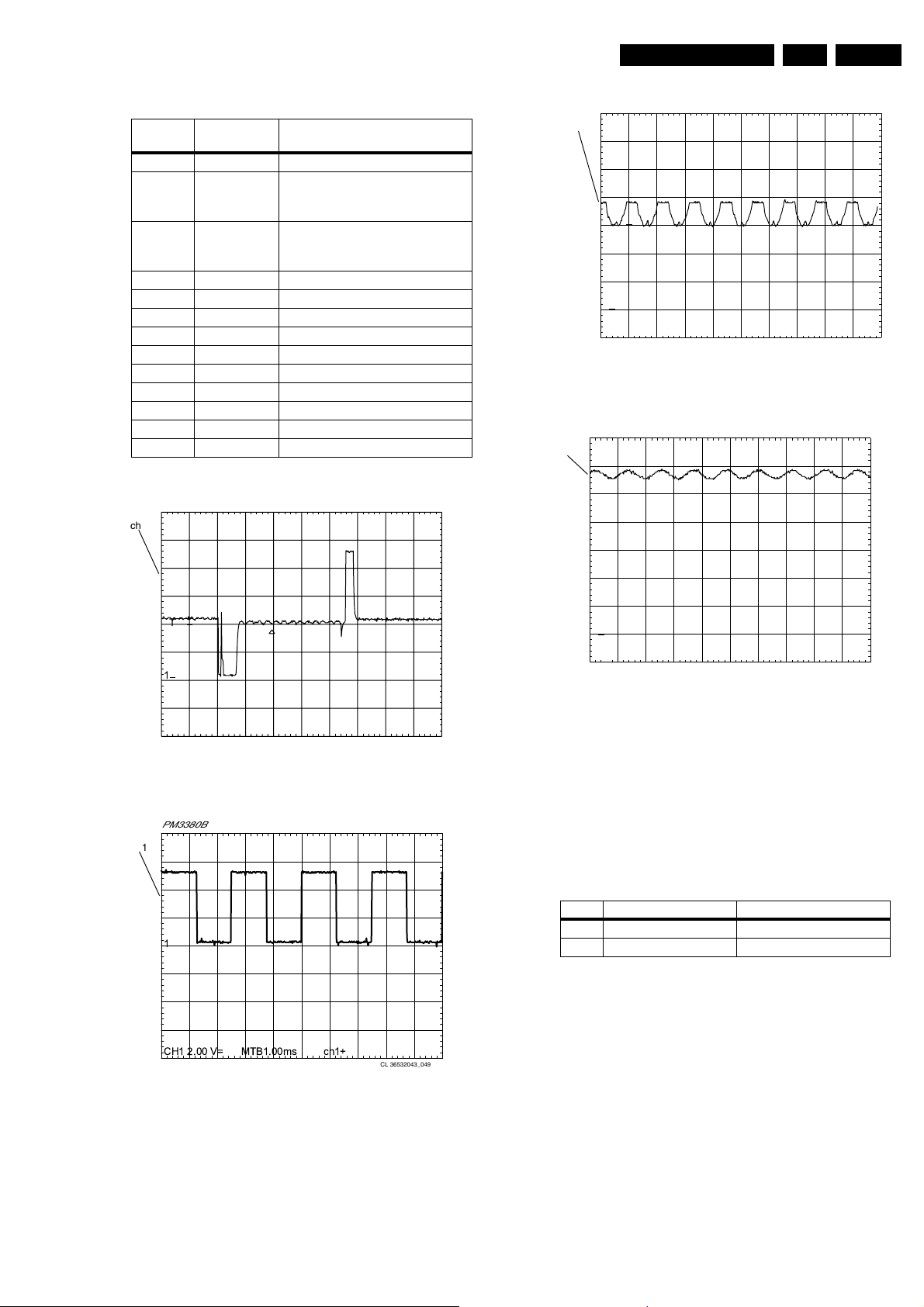

5.6.2 Spindle Motor check:

The tracking control circuit is checked using the following

commands:

Table 5-14 Spindle check commands

Ref. # Command Name Remark

39a BeDiscmotorOn Discmotor on

39b BeDiscmotorOff Discmotor off

Check the following signals with the discmotor switched ON

with the loader connected and with DVD Disc inserted.

CL 36532043_065.eps

030603

Figure 5-22 B_U with video out at YUV

Page 17

Test Instructions Mono Board SD5.31SL

EN 17SD-5.31SL 5.

Table 5-15 Disc motor switching

Signal

Name Testpoint Frequency

SMOTOR Pin22/IC7101 Output voltage control

SSPDON Pin23/IC7101 Power save

Motor ON - high

Motor OFF - low

VH Pin15/IC7101 HALL Bias

Motor ON - LOW

Motor OFF - HIGH

SFGIN Pin 24/IC7101 Tacho signal output

DA1 F113 Output

DA2 F114 Output

DA3 F115 Output

H1+ F112 H1+ HALL input (positive signal)

H1- F111 H1- HALL input (negative signal)

H2+ F110 H2+ HALL input (negative signal)

H2- F109 H2- HALL input (negative signal)

H3+ F108 H3+ HALL input (negative signal)

H3- F107 H3- HALL input (negative signal)

PM3380B

ch1

PM3380B

ch1

T

1

CH1 2.00V= MTB 5.00mus ch1+

STOP

Figure 5-26 DA1-DA2-DA3

PM3380B

ch1

CL 36532043_058.eps

030603

6

CH1 1.00 V= MTB2.00 s- 3.94dv ch1+

CL 36532043_048.eps

Figure 5-24 SMotor (Random during jump track)

PM3380B

ch1

1

CH1 2.00 V= MTB1.00ms ch1+

CL 36532043_049.eps

Figure 5-25 SFGIN

030603

050603

1

CH1 500mV= MTB 5.00ms ch1+

Figure 5-27 HALL input signal

When measurement is completed, switch the discmotor OFF

before executing next command

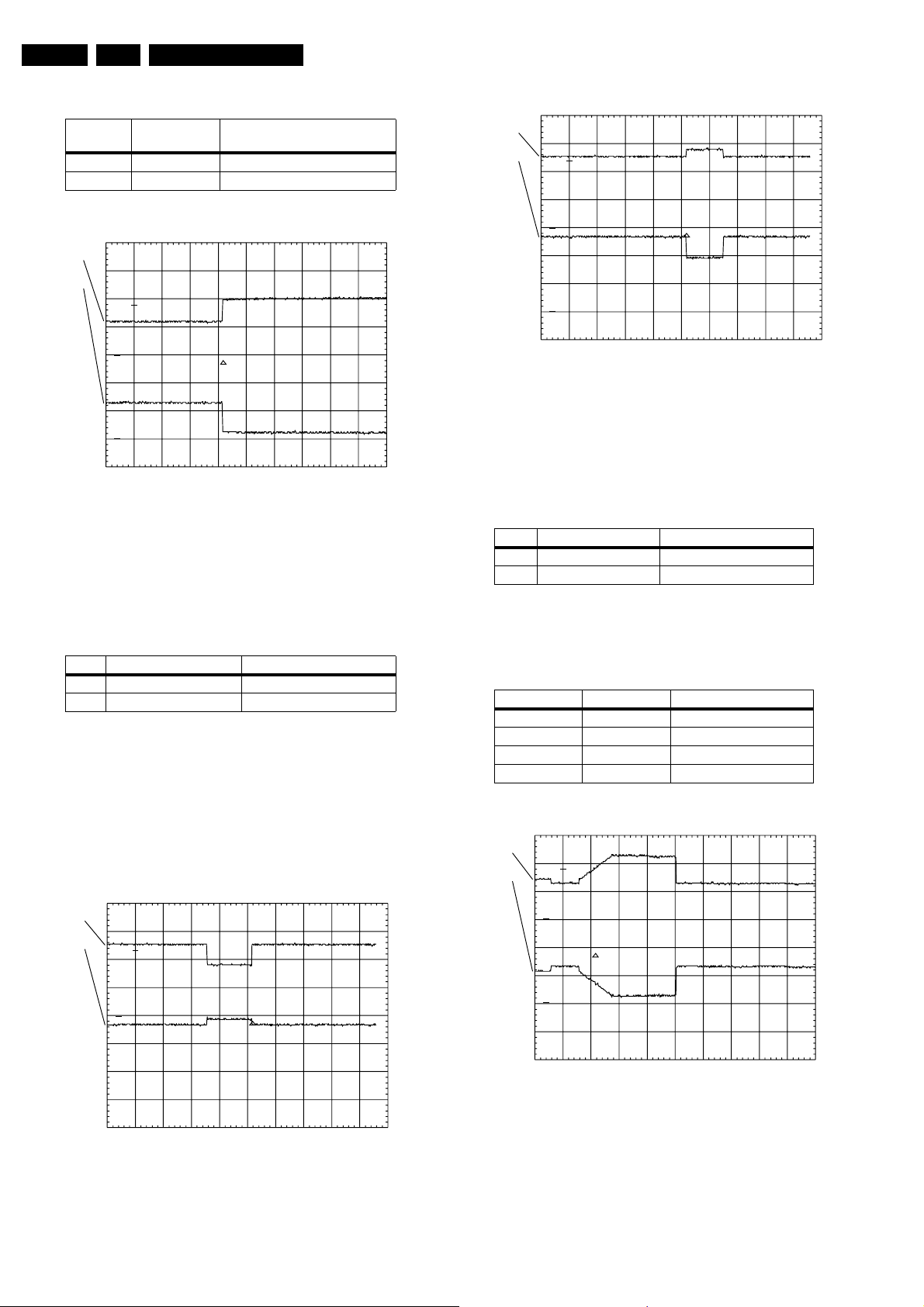

5.6.3 Tracking check

The tracking control circuit is checked using the following

commands:

Table 5-16 Tracking

Ref. # Command Name Remark

40a BeRadialOn Radial control on

40b BeRadialOff Radial control off

Visual check on the radial ,when Radial control ON, if the

radial movement is visible.

Once the check is completed,switch the Radial control OFF

before executing next command

To check the waveform of TRACK- and TRACK+,

connect a 10W / 0.25W resistor between TRACK- and

TRACK+ to serve as dummy load without connecting the

loader.

CL 36532043_064.eps

030603

Page 18

EN 18 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

Table 5-17 Trackingl

Signal

Name Testpoint Description

Track - F003 Negative drive to tracking coil

Track + F004 Positive drive to tracking coil

PM3380B

ch1

ch2

T

1

2

CH1 2.00V=

CH1 2.00V= MTB 1.00s 4.18dv ch1+

Figure 5-28 TRACK ON Command

5.6.4 Sledge check

The Sledge control circuit is checked using the following

commands to move the sledge:

Table 5-18 Sledge check commands

CL 36532043_080.eps

030603

PM3380B

ch1

ch2

T

1

CH1 2.00V=

CH2 2.00V= MTB 500ms 5.82dv ch1+

Figure 5-30 SLED Outwards command

5.6.5 Tray Check:

The tray control circuit is checked using the following

command:

Table 5-19 Tray command

Ref. # Command Name Remark

43a BeTrayIn Tray in

43b BeTrayOut Tray out

Measure the DC voltages and waveforms when executing

the tray closed command.

CL 36532043_078.eps

030603

Ref. # Command Name Remark

41a BeSledgeIn Sledge inwards

41b BeSledgeOut Sledge outwards

Visual check on the sledge,when Sledge control ON, if the

sledge movement is visible.

Once the check is completed,switch the Sledge control OFF

before executing next command

To check the waveform of SLEDGE- and SLEDGE+,

connect a 10W / 0.25W resistor between SLEDGE- and

SLEDGE+ to serve as dummy load without connecting the

loader.

PM3380B

ch1

ch2

T

1

CH1 2.00V=

CH2 2.00V= MTB 500ms 5.82dv ch1+

CL 36532043_077.eps

030603

Figure 5-29 SLED Inwards comand

Table 5-20 Tray in

Signal Name Testpoint Value (Tray closed)

LOAD + F116 2V5 +/- 0V2

LOAD - F117 2V5 +/- 0V2

INSW F119 0V +/- 0V2

OUTSW F121 3V +/- 0V2

PM3380B

ch1

T

ch2

1

2

CH1 2.00V=

CH1 2.00V= MTB 500ms 2.24dv ch1+

CL 36532043_081.eps

030603

Figure 5-31 Tray in command

Measure the DC voltages and waveforms when executing the

tray opening command.

Page 19

Test Instructions Mono Board SD5.31SL

EN 19SD-5.31SL 5.

Table 5-21 Tray out

Signal Name Testpoint Value (Tray closed)

LOAD + F116 2V8 ± 0V2

LOAD - F117 2V2 ± 0V2

INSW F119 3V ± 0V2

OUTSW F121 0V ± 0V2

PM3380B

ch1

T

ch2

1

2

CH1 2.00V=

CH1 2.00V= MTB 500ms 2.24dv ch1+

CL 36532043_082.eps

Figure 5-32 Tray out command

030603

Table 5-23 Focus motor switching

Signal Name Testpoint Description

FOCUS - F005 Negative drive to focus coil

FOCUS + F006 Positive drive to focus coil

PM3380B

ch2

ch1

2

T

1

CH1 1.00V=

CH2 1.00V= MTB 500ms 4.08dv ch1+

Figure 5-33 Focus ON Command

5.6.7 Hf Path

CL 36532043_061.eps

030603

5.6.6 Focus check

Test need a DVD disc in the DVD player to operate properly.

The focus control circuit is checked using the following

commands:

Table 5-22 Focus check commands

Ref. # Command Name Remark

38a BeFocusOn Focus on

38b BefocusOff Focus off

Visual check on the laser,when Focus control ON, if the

laserlight is visible.

Once the check is completed,switch the focus control OFF

before executing next command.

To check the waveform of FOCUS- and FOCUS+,

connect a 10W / 0.25W resistor between FOCUS- and

FOCUS+ to serve as dummy load without connecting the

loader.

Play DVD Test Disc.

Measure outputs of diodes A, B, C, D, E, F.

Table 5-24

Signal Name Testpoint Value

A F016 2.5V +/-0.2%

B F015 2.5V +/-0.2%

C F014 2.5V +/-0.2%

D F017 2.5V +/-0.2%

E F019 2.5V +/-0.2%

F F018 2.5V +/-0.2%

At outputs of diodes A, B, C, D the following waveform can be

measured: Refer to Figure Output of diodes A, B, C, D

PM3380B

ch1

T

1

CH1 50.0mV= MTB 20.0us ch1+

CL 36532043_066.eps

030603

Figure 5-34 Output of diodes A,B,C,D

Check the HF output, RFO, at testland F219 and observe the

waveform, refer to Figure RFO.

Page 20

EN 20 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

PM3380B

ch1

1

CH1 1.00V= MTB 250ns ch1+

Figure 5-35 RFO

5.7 Diagnostic Software Description

5.7.1 Introduction

Purpose

This document describes all interfaces from the outside world

to the diagnostic software, what is needed to use these

interfaces and how to access them.

Scope

This document has been realised within the framework of the

DVD video player.

5.7.2 Definitions and Abbreviations

Definitions

Control PC Automatic test equipment, part of the

production control system in the

factory, to control the execution of

Diagnostic Nuclei in the DVD player.

Diagnostic Nucleus Part of the Diagnostic Software. Each

nucleus contains an atomic and

software independent diagnostic test,

testing a functional part of the DVD

player hardware on component level.

Script Part of the Diagnostic Software. Each

script contains a sequence of

Diagnostic Nuclei to be executed.

Service PC PC used by a service- or repair-person

to communicate with the Diagnostic

Software in the DVD player.

CL 36532043_068.eps

030603

Table 5-25 Interface overview

Logical

Interface Description

Menu

Interface

Menu-driven

activation of

individual nuclei,

used for Level 2/

Second Line

diagnostic mode.

Physical interface

components

- Service PC running a

terminal emulation

program, connected

to the RS232 port of

the DVD player.

- Test pin grounded

Users are service or

repair people

Command

Line

Interface

Used during Level 1

diagnostic mode.

Used to send

commands from the

Control PC into the

DVD hardware.

- Control PC, running a

control program (e.g.

Hyperterminal),

connected to RS232

port of the DVD

player.

- Test pin grounded

• In the next chapters the logical user interfaces are

described in more detail including the exact use of the

physical interface components.

5.9 Description of Interfaces

5.9.1 Menu Interface

The menu interface is part of the Level 2 / Second Line

diagnostic mode. Via the menu interface it is possible to control

the execution of the Diagnostic Nuclei.

Set-up Physical Interface Components

Hardware required:

• Service PC

• one free COM port on the Service PC

• special cable to connect DVD player to Service PC

The service PC must have a terminal emulation program (e.g.

OS2 WarpTerminal or Procomm /Windows Hyperterminal)

installed and must have a free COM port (e.g. COM1). Activate

the terminal emulation program and check that the port settings

for the free COM port are: 19200 bps, 8 data bits, no parity, 1

stop bit and no flow control. The free COM port must be

connected via a special cable to the RS232 port of the DVD

player. This special cable will also connect the test pin, which

is available on the connector, to ground (i.e. activate test pin).

Activation

Switch the player on and the following text will appear on the

screen of the terminal (program):

Abbreviations

FDS Full Diagnostic Software

5.8 Overview of Interfaces

The table below shows an overview of the user interfaces of the

Diagnostic Software. The table is based on logical interface,

interfaces as seen from user perspective. A logical interface

can use one or more physical interface components. The DVD

has only a single RS232 port, implying that all interfaces using

this port are mutually exclusive.

DVDv6 Diagnostic Software version 7.03 S

(M)enu, or (C)ommand [M]:@ m <enter>

Press ENTER to go to Main Menu

CC: >

CL 36532043_023.eps

020603

Figure 5-36

• The first line indicates that the Diagnostic software has

been activated and contains the version number of the

diagnostic; this is also an indication that the first basic

nucleus (nucleus number 1) has been executed

succesfully.

• The term "DVDv6" implies that the DSW is running in the

ZiVA5 platform (6th generation).Interpretation of the DSW

version is done as follows:

Page 21

Test Instructions Mono Board SD5.31SL

EN 21SD-5.31SL 5.

(X) Major revision number, always fixed to 7

(YY) Minor revision number, a two-digit number incremented for

every release of a DSW variant.

version X.YY Z

(Z) DSW variant ID letter, identifies the module/player where this

DSW was targeted to run:

A – SD5.11, I2C Master module-based players

B – SD5.2, I2C Master module, used in DVD760 players

C – SD5.2, I2C Master module, used in high-end SACD2003 players

D – SD5.12, I2C Slave module, used in MTV combi applications

S – SD5.31, I2C Slave module, used in MTV combi applications

CL 36532043_024.eps

220503

• The second line is the prompt asking the user to choose the

interface format. Enter ‘M’ to select Menu mode and the

main menu will appear.For the layout of the menus,

see chapter ‘Layout of Menu and Submenu’.

To switch between interfaces, the DVD player needs to be

switched off and on again.

Note: For player that has no Mechanical power switch, it can

be turned on by connecting the power-cable.

Usage

To select, type the number of the chosen menu-item at the

prompt. Each entry must be terminated with a ‘RETURN’.

Invalid selections will cause an error message by the Menu

Handler

Example:

Select > 99

Invalid menu choice, number out of range ER @

Press RETURN to continue @

CL 16532163_038.eps

230102

Result and output of an activated (and terminated) nucleus will

be sent back to the service terminal.

Example:

Select > 3

1301 OK @

Press RETURN to continue @

CL 36532043_025.eps

220503

After the user presses a key, the current menu is rebuilt on

screen.

Pressing “RETURN” at the prompt without any further input at

the terminal will always rebuild the main menu.

DVDv6 Diagnostic Software version 7.03 S

(M)enu, OR (C)ommand [M]:@ C <enter>

DD: >

CL 36532043_026.eps

220503

The first line indicates that the Diagnostic software has been

activated and contains the version number; this is also an

indication that the first basic nucleus (nucleus number 1) has

been executed succesfully. The second line lets the user

choose the interface format. Enter ‘C’ to select Command

Mode and the next three lines are the succesful result of the

two subsequent basic tests (nuclei 2, 4 and the detection of the

display type used by the panel respectively). If not all these

messages appear on the terminal screen, then the related

nucleus found an error. The last line is the prompt ("DD>"). The

diagnostic software is now ready to receive commands.

Note: For player that has no Mechanical power switch, it can

be turned on by connecting the power-cable.

Usage

The commands that can be given are the reference IDs of the

test nuclei. A command must be terminated with a <RETURN>

character from the control PC. When typing commands, the

backspace key can be used to make corrections.

In case of typing errors in the command, an error message is

returned.

Example:

DD: > CompSdarmWrR? (Nuclei name cannot be accepted)

0001 Unknown command ER @

DD: >

CL 16532163_041.eps

230102

If the command (the nucleus ID) is recognised, the nucleus is

executed. Result and output of an activated (and terminated)

nucleus will be sent back to the control PC according to the

standard layout.

Example for a command without error:

DD: > 13 <ENTER> (Execute PapAtapiEcho nuclei)

1300 OK @

DD: >

CL 36532043_027.eps

220503

Termination

The menu interface can be terminated by switching off the AC

power from the DVD player/ module.

5.9.2 Command Line Interface

The command line interface is part of level 1 diagnostic mode.

Via a command line interface the execution of Diagnostic

Nuclei can be controlled.

Set-up Physical Interface Components

Hardware required:

• Control PC

• one free COM port on the Control PC

• special cable to connect DVD player to the Control PC

The control PC must use the following port settings for the used

COM port: 19200 bps, 8 data bits, no parity, 1 stop bit and no

flow control. The control PC is connected with a special cable

to the RS232 port of the DVD player. Via the same connection

the test pin will be connected to ground.

Activation

After power on the next text will sent to the control PC

Example for a command with error:

DD: > 13 <ENTER>

1304 No response from ATAPI drive ER @

DD: >

CL 36532043_028.eps

220503

Termination

The command line interface is terminated by switching off the

AC power from the DVD player/ module.

5.10 Layout of Menu and Submenu

5.10.1 Layout Of Menus And Submenus For The Service Terminal

NOTE: a symbol “--” in the menu layouts indicates that that

specific menu choice will invoke the display of a submenu. This

symbol will also be used in the implementation of the menus

(i.e. the “--” will also appear in the user interface).

Page 22

EN 22 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

Menus

MAIN MENU

1 Audio...

2 Video...

3 Front Panel...

4 Basic Engine...

5 Processor Peripherals...

6 Error Log...

7 Miscellaneous...

First Level Submenus

MAIN > AUDIO MENU

1 Mute...

2 Pink Noise...

3 Sine Wave...

4 Digital Ports...

MAIN > VIDEO MENU

1 Colourbar...

2 Digital Port...

MAIN > FRONT PANEL MENU

1 No items available

MAIN > BASIC ENGINE MENU

1 Reset [44]

2 Version [37]

3 ATAPI...

4 Loader Mechanism...

5 Special Diagnostics...

MAIN > PROCESSOR PERIPHERALS MENU

1 Clock...

2 Flash...

3 NVRAM...

4 Processor info [5]

5 Slave IIC Loopback Test [90]

MAIN > ERROR LOG MENU

1 Read Last Errors [31]

2 Read Error Bits [32]

3 Reset Error Log [33]

MAIN > MISCELLANEOUS MENU

1 Statistics Info...

2 Read DVD Application version [46]

5 Set Video Out To RGB [61a]

6 Set Video Out To YUV [61b]

MAIN > VIDEO > DIGITAL PORT MENU

1 Video Port Out 0xAA [17a]

2 Video Port Out 0x55 [17b]

MAIN > BASIC ENGINE > ATAPI MENU

1 ATAPI Echo [13]

MAIN > BASIC ENGINE > MECHANISM MENU

1 Disc Motor...

2 Laser...

3 Tray...

4 Focus...

5 Radial...

6 Sledge...

7 Grooves...

MAIN > BASIC ENGINE > SPECIAL DIAGNOSTICS MENU

1 Read FlashID [70]

2 ROM Checksum [71]

3 Scratch Detector Test [72]

MAIN > PROCESSOR PERIPHERALS > PCM CLOCK MENU

1 PCM_CLK In CDDA Mode (11.3MHz) [8a]

2 PCM_CLK In DVD Mode (12.3MHz) [8b]

3 PCM_CLK In DVD96kHz Mode (24.6MHz) [8c]

MAIN > PROCESSOR PERIPHERALS > FLASH MENU

1 Verify FLASH Checksum [6]

2 Show FLASH Checksum [62]

3 FLASH Write Acces [10]

MAIN > PROCESSOR PERIPHERALS > NVRAM MENU

1 I2C NVRAM Acces [11]

2 NVRAM Config [34]

3 NVRAM Reset [35]

4 NVRAM Modify [36]

5 NVRAM Read/Wr Test [15]

MAIN > MISCELLANEOUS > STATISTICS INFO MENU

1 Total Nr Of Times Tray Open [47a]

2 Total Time Power On [47b]

3 Total Play-Time CDDA & VCD [47c]

4 Total Play-Time DVD [47d]

Third Level Submenus

Second Level Submenus

MAIN > AUDIO > MUTE MENU

1 Mute On [19a]

2 Mute Off [19b]

MAIN > AUDIO > PINK NOISE MENU

1 Pink Noise On [20a]

2 Pink Noise / Beep Tone Off [20b]

3 Beep Tone On [20c]

MAIN > AUDIO > SINE WAVE MENU

1 Audio Sine On [21a]

2 Audio Burst On [21b]

MAIN > AUDIO > DIGITAL PORTS MENU

1 No test available

MAIN > VIDEO > COLOURBAR MENU

1 Colourbar DENC On (PAL) [23a]

2 Colourbar DENC On (NTSC) [23c]

3 Colourbar DENC/MPEG Off [23b]

4 ProgressiveScan MPEG On [24a]

MAIN > BASIC ENGINE > MECHANISM > DISC MOTOR MENU

1 Disc Motor On [39a]

2 Disc Motor Off [39b]

MAIN > BASIC ENGINE > MECHANISM > LASER MENU

1 CD Laser On [58a]

2 CD Laser Off [58b]

3 DVD Laser On [58c]

4 DVD Laser Off [58d]

MAIN > BASIC ENGINE > MECHANISM > TRAY MENU

1 Tray Open [43b]

2 Tray Close [43a]

MAIN > BASIC ENGINE > MECHANISM > FOCUS MENU

1 Focus On [38a] (load DVD first)

2 Focus Off [38b]

MAIN > BASIC ENGINE > MECHANISM > RADIAL MENU

1 Radial Control On [40a] (load DVD first)

2 Radial Control Off [40b]

Page 23

Test Instructions Mono Board SD5.31SL

MAIN > BASIC ENGINE > MECHANISM > SLEDGE MENU

1 Sledge Inwards [41a]

2 Sledge Outwards [41b]

MAIN > BASIC ENGINE > MECHANISM > GROOVES (Uses DVD) MENU

1 Jump To Inside Grooves [42a]

2 Jump To Middle Grooves [42b]

3 Jump To Outside Grooves [42c]

1. 0001 Unknown command ER @

2. 3100 OK @

3. 0901 Data line X is not connected to the DRAM ER @

4. Device ID: 0x01

Manufac ID: 0xC2

7000 OK @

5.11 Diagnostic Nuclei

EN 23SD-5.31SL 5.

CL 16532163_045.eps

230102

Screen Layout With Menus

When menus are used, no specific screen layout can be given:

menu information will not be in a special format, except for the

layout as mentioned in the previous paragraphs.

A typical menu session can look as follows:

DVDv6 Diagnostic Software version 7.03 S

(M)enu, or (C)ommand [M]:@ <enter>

Press ENTER to go to main menu

CC: > <enter>

MAIN MENU

1. Audio ...

2. Video ...

3. Front Panel ...

4. Basic Engine ...

5. Processor Peripherals ...

6. Error Log ...

7. Miscellaneous ...

Select > 4 <enter>

MAIN > BASIC ENGINE MENU

1. Reset [44]

2. Version [37]

3. S2B

4. Loader Mechanism ...

5. Special Diagnostics ...

Press Enter to go to Main Menu

Select > 5 <enter>

MAIN > BASIC ENGINE > SPECIAL DIAGNOSTIC MENU

1. Read flashID [70]

2. ROM checksum [71]

3. Scratsh detector test [72]

Press Enter to go to Main Menu

CL 36532043_029.eps

020603

Each nucleus contains an atomic and independent diagnostic

test, testing a functional part of the DVD player hardware on

component level. Each Nucleus returns a result message to its

caller. Some tests (e.g. generating a colour bar) can only return

an "OK" result. Internal communication will be done via a

uniform interface between the diagnostic Engine, Scripts and

the Diagnostic Nuclei.

The diagnostic Engine can only operate if a certain (minimal)

set of hardware is functioning properly. To test this set of

hardware, a set of basic diagnostic nuclei is embedded in the

DVD player. Each basic diagnostic nucleus will only test that

part of the hardware which is required for execution of the

diagnostic Engine, e.g. a RAM test will only test that part of

RAM that is used by the diagnostic engine. After the Diagnostic

Engine is operational it is possible to do a full RAM diagnostic.

All basic diagnostic nuclei start with prefix 'Basic'.

In the overview each Diagnostic Nucleus consists of a

reference number, a reference name and remarks. Reference

number and name are coupled and one of them is enough for

unique identification.

Figure 5-37

Depending on the height of the screen, the text will start

scrolling off the top of the screen.

Layout Of Results Diagnostic Nuclei On Control/service Pc

Results returned from a Diagnostic Nucleus to the control/

service PC will have a maximum length of 300 characters and

are terminated by a CR character (included in the string length)

The result has the following layout

< number >< string > [OK l ER] @< CR >

The use of the "@" enables the Asterix system on the Control

PC to parse the output string of each nucleus into a database.

< number > is a 4-digit decimal number padded with leading

zeros if its value is less than 4 digits. The first two digits identify

the generating nucleus (or goup of nuclei), the latter two digits

indicate the error number.

< string > is a text string containing information about the result

of the Diagnostic Nucleus.

< number > and < string > are defined in [SDD_DN] in the

output sections of each Nucleus.

Examples:

Page 24

EN 24 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

Table 5-26 Basic diagnostic nuclei

Ref. # Reference Name Remark

1 BasicSpAcc Serial port Access test/

initialization

5 CompProcInfo Display processor specific

Table 5-27 Processor and peripherals

Ref. # Reference Name Remark

6 PapChksFl Calculate and Verify

7a PapUclkAclkCdda External uClock A_CLK in

7b PapUclkAclkDvd External uClock A_CLK in

7c PapUclkAclkDvd96 External uClock A_CLK in

8a PapSgsAclkCdda Internal PLL CLK in CD-DA

8b PapSgsAclkDvd Internal PLL CLK in DVD

8c PapSgsAclkDvd96 Internal PLL CLK in DVD

10 PapFlashWrAcc Tests Backend flash Write

11 PapI2cNvram I2C NVRAM access

12 PapI2cDisp I2C/Sio Bus-Display PWB

13 PapUdeEcho/

PapATAPIEcho

14 PapUdePass Enter UDE Pass-through

15 PapNvramWrR NVRAM Write Read

62 PapChksSum Show checksums stored in

info (LOR register,

Chip Revision)

Checksum FLASH

CD-DA mode (SD5.2only)

DVD mode (SD5.2 only)

DVD (96kHz)

mode (SD5.2 only)

mode

mode

mode

Access function

communication check

UDE Echo(SD5.2) / ATAPI

echo (SD5.12/SD5.31)

(SD5.2 only)

flash

19a AudioMuteOn Audio Mute On

67b DAC_ClockExternal Uses external clock for

68a DAC_AudioPreMuteOn Enable Audio Pre-mute

68b DAC_AudioPreMuteOff Disable Audio Pre-mute

69a DAC_CenterOn Enable Center on pin

69b DAC_CenterOff Disable Center on pin

79 DAC_Reset Resets DAC

80a DAC_ModeCDDA Sets DAC to CDDA

80b DAC_ModeDVD48 Sets DAC to DVD mode

80c DAC_ModeDVD96 Sets DAC to DVD mode

80d DAC_ModeDSD Sets DAC to DSD mode

81a DAC_LowPowerStandbyOnEnable Low Power

81b DAC_LowPowerStandby

Off

82a DAC_UpsamplingFreq192kSets Upsampling fre-

82b DAC_UpsamplingFreq96kSets Upsampling fre-

82c DAC_UpsamplingOn Enable upsampling

82d DAC_UpsamplingOff Disable upsampling

DAC (384fs)

pin

pin

mode

(48kHz)

(96kHz)

Standby

Disable Low Power

Standby

quency to 192kHz

quency to 96kHz

Table 5-28 Audio

Ref. # Reference Name Remark

19a AudioMuteOn Audio Mute On

19b AudioMuteOff Audio Mute Off

20a AudioPinkNoiseOn Audio Pinknoise On

20b AudioPinkNoiseOff Aud io Pinknoise (or beep

tone) Off

20c AudioBeepToneOn Audio Beep Tone On

21a AudioSineOn Audio Sine signal On/Off

21b AudioSineBurst Audio Sine signal Burst

Table 5-29 Audio DAC related (SD5.2 only)

19a AudioMuteOn Audio Mute On

65 DAC_I2C Resets DAC and check

66a DAC_I2CEnable Enable I2C communica-

66b DAC_I2CDisable Disable I2C communica-

67a DAC_ClockInternal Uses internal clock from

I2C communication with

DAC

tion to AV board

tion to AV board

monoboard for DAC

(256fs)

Page 25

Test Instructions Mono Board SD5.31SL

EN 25SD-5.31SL 5.

Table 5-30 Video

Ref. # Reference Name Remark

17a VidPortOutAA Output the value 0XAA at

the Digital Video Interface

Port (SD5.2 only)

17b VidPortOut55 Output the value 0X55 at the

Digital Video Interface Port

(SD5.2 only)

23a VideoColDencOnPAL Colourbar (PAL) DENC On

23b VideoColDencOff Colourbar DENC / Digital

Video Off

23c VideoColDencOnNTSCColourbar (NTSC) DENC

On

24a VideoProgMPEGon Progressive - DigitalVideo

Colour Bar ON

(SD5.2 only)

24b VideoYuvMPEGon Enhanced YUV-

DigitalVideo Colour Bar

25a VideoScartLo Scart Low (SD5.2 only)

25b VideoScartMi Scart Medium (SD5.2 only)

25c VideoScartHi Scart High (SD5.2 only)

54 VideoScartSwComm Scart Switch communication

(SD5.2 only)

55a VideoScartSwDvd Scart Switch Dvd

(SD5.2 only)

55b VideoScartSwPass Scart Switch Pass-through

(SD5.2 only)

57a VideoScartPinLo PIO-pins used for Scart-

switching

57b VideoScartPinMi PIO-pins used for Scart-

switching

57c VideoScartPinHi PIO-pins used for Scart-

switching

61a VideoColOutRGB Enable Video Output to

RGB

61b VideoColOutYUV Enable Video Output to

YUV

Ref. # Reference Name Remark

46 MiscApplVer Read version of

application software

47a MiscTrayOpenNr Read the number of

times the tray opened

47b MiscPowerOnTime Read the total time the

player's power has been

on

47c MiscPlayTimeCddaVcd Read the Playtime of

CDDA and VCD discs

47d MiscPlayTimeDvd Read the Playtime of

DVD discs

Table 5-31 Display (slave processor) (SD5.2 only)

Ref. # Reference Name Remark

26 DispVer Version number

27 DispKeyb Keyboard

28 DispRc Remote Control

29 DispLed LEDs

30a DispDisplay VFT Display test

30b DispLCDisplay LCD Display test

30c DispLCDBkLight LCD Backlight test

60 DispP50 P50 loopback test

Table 5-32 Log (Error logging in Nvram)

Ref. # Reference Name Remark

31 LogReadErr Read last Errors

32 LogReadBits Read errors Bits

33 LogReset Reset

Table 5-33 Miscellaneous

Ref. # Reference Name Remark

34 MiscReadConfig Read Configuration area

35 MiscNvramReset NVRAM Reset

36 MiscNvramMod Modify NVRAM contents

from NVRAM

Page 26

EN 26 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

Table 5-34 Basic engine

Ref. # Reference Name Remark

37 BeVer Version number

38a BeFocusOn Focus On

38b BeFocusOff Focus Off

39a BeDiscmotorOn Discmotor On

39b BeDiscmotorOff Discmotor Off

40a BeRadialOn Radial control On

40b BeRadialOff Radial control Off

41a BeSledgeIn Sledge Inwards

41b BeSledgeOut Sledge Outwards

42a BeGroovesIn jump Grooves to Inside

42b BeGroovesMid jump Grooves to Middle

42c BeGroovesOut jump Grooves to Outside

43a BeTrayIn Tray In

43b BeTrayOut Tray Out

44 BeReset Reset Basic Engine

58a LaserCdOn CD Laser on

58b LaserCdOff CD Laser off

58c LaserDvdOn DVD Laser on

58d LaserDvdOff DVD Laser off

70 BedReadFlashID Read flash memory manufac-

turer and device ID

71 BedCalcRomChk-

sum

72 BedScratchTest Test scratch detection circuit

Table 5-35 Furore IC (SD5.2 only)

Ref. # Reference Name Remark

62 Furore_SdramWrR Furore SDRAM Write Read

63 Furore_SdramWrR

Fast

64 Furore_Id Furore version ID check

83 Furore_Reset Furore reset

84a Furore_High Sets Furore output pins

84b Furore_Low Sets Furore output pins

Table 5-36 Karaoke (not available)

Ref. # Reference Name Remark

48a KaraokeModeOff Switch Karaoke mode off

48b KaraokeModeOn Switch Karaoke mode on

49 KaraokeMicInput Check path from the

50a KaraokeKeyOn Set Karaoke Key to the

50b KaraokeKeyOff Set Karaoke Key to flat octave

51a KaraokeEchoOn Set Echo Control fuction on

51b KaraokeEchoOff Set Echo Control function off

Calculate ROM checksum

test

Furore SDRAM interconnec-

tion test

DSD_PCM0-9 to high

DSD_PCM0-9 to low

microphone input to audio

output

maximum level (1200 cent)

(0 cent)

5.12 Nuclei Error Codes

In the following tables the error description of the error codes

will be described.

5.12.1 Audio Nuclei

Error

code

1800 Audio Deemp On OK

1820 Audio Deemp Off OK

1880 Audio Deemp Tri OK

1900 Audio mute On OK

1920 Audio mute Off OK

1940 Audio Front LR mute On OK

1960 Audio Front LR mute Off OK

2000 Audio Pinknosie On OK

2001 Audio Pinknoise On DAC fail

2020 Audio Pinknoise Off OK

2040 Audio Beep tone On OK

2041 Audio Beep tone On DAC fail

2100 Audio Sine On OK

2101 Audio Sine On DAC fail

2120 Audio Sine Burst OK

2121 Audio Sine Burst DAC fail

6600 DAC I2C OK

6601 DAC I2C Bus busy

6602 DAC I2C expander

6603 DAC I2C DAC 4362

6620 DAC I2C enable OK

6640 DAC I2C disable OK

6700 DAC Clk internal OK

6701 DAC Clk internal I2C bus busy

6702 DAC Clk internal I2C failed

6720 DAC Clk external OK

6721 DAC Clk external I2Cbus busy

6722 DAC Clk external I2C failed

6800 DAC Audio pre-mute On OK

6801 DAC Audio pre-mute On I2C bus busy

6802 DAC Audio pre-mute On I2C failed

6820 DAC Audio pre-mute Off OK

6821 DAC Audio pre-mute Off I2C bus busy

6822 DAC Audio pre-mute Off I2C failed

6900 DAC Center On OK

6901 DAC Center On I2C bus busy

6902 DAC Center On I2C failed

6920 DAC Center Off OK

6921 DAC Center Off I2C bus busy

6922 DAC Center Off I2C failed

7900 DAC Reset OK

7901 DAC Reset I2C bus busy

7902 DAC Reset I2C expander

8000 DAC Mode CDDA OK

8001 DAC Mode CDDA I2C bus busy

8002 DAC Mode CDDA I2C failed

8020 DAC Mode DVD48 OK

8021 DAC Mode DVD48 I2C bus busy

8022 DAC Mode DVD48 I2C failed

8040 DAC Mode DVD96 OK

8041 DAC Mode DVD96 I2C bus busy

8042 DAC Mode DVD96 I2C failed

8060 DAC Mode DSD OK

8061 DAC Mode DSD I2C bus busy

8062 DAC Mode DSD I2C failed

8100 DAC Low Power Standby On OK

8101 DAC Low Power Standby On I2C bus busy

8102 DAC Low Power Standby On I2C failed

Error text

Page 27

Test Instructions Mono Board SD5.31SL

EN 27SD-5.31SL 5.

Error

code

8120 DAC Low Power Standby Off OK

8121 DAC Low Power Standby Off I2C bus busy

8122 DAC Low Power Standby Off I2C failed

8200 DAC Upsample 192k OK

8201 DAC Upsample 192k I2C bus busy

8202 DAC Upsample 192k I2C failed

8220 DAC Upsample 96k OK

8221 DAC Upsample 96k I2C bus busy

8222 DAC Upsample 96k I2C failed

8240 DAC UpSample On OK

8241 DAC UpSample On bus busy

8242 DAC UpSample On I2C failed

8260 DAC UpSample Off OK

8261 DAC UpSample Off bus busy

8262 DAC UpSample Off I2C failed

5.12.2 Basic Engine Nuclei

Error

code Error text

3900 Test successful

3901 “Parity error from Basic Engine to Serial”

3902 “Unexpected response from Basic Engine”

3903 “Communication time-out error”

3904 “Basic Engine returned error number 0xXX”

3921 “Parity error from Basic Engine to Serial”

3922 “Unexpected response from Basic Engine”

3923 “Communication time-out error”

3924 “Basic Engine returned error number 0xXX”

3800 Test successful

3801 “Parity error from Basic Engine to Serial”

3802 “Unexpected response from Basic Engine”

3803 “Communication time-out error”

3804 “Basic Engine returned error number 0xXX”

3805 “Focus loop could not be closed”

3820 Test successful

3821 “Parity error from Basic Engine to Serial”

3822 “Unexpected response from Basic Engine”

3823 “Communication time-out error”

3824 “Basic Engine returned error number 0xXX”

4200 Test successful

4201 “Parity error from Basic Engine to Serial”

4202 “Unexpected response from Basic Engine”

4203 “Communication time-out error”

4204 “Basic Engine returned error number 0xXX”

4205 “Sledge could not be moved to home

4206 “Focus loop could not be closed”

4207 “Motor not on speed within time-out”

4208 “Radial loop could not be closed”

4209 “PLL could not lock in accessing or tracking

4210 “Subcode or sector information could not be

4211 “Requested subcode item could not be

4212 “TOC could not be read in time”

4213 “Seek could not be performed”

4220 Test successful

Error text

position”

state”

read”

found”

Error

code Error text

4221 “Parity error from Basic Engine to Serial”

4222 “Unexpected response from Basic Engine”

4223 “Communication time-out error”

4224 “Basic Engine returned error number 0xXX”

4225 “Sledge could not be moved to home

position”

4226 “Focus loop could not be closed”

4227 “Motor not on speed within time-out”

4228 “Radial loop could not be closed”

4229 “PLL could not lock in accessing or tracking

state”

4230 “Subcode or sector information could not be

read”

4231 “Requested subcode item could not be

found”

4232 “TOC could not be read in time”

4233 “Seek could not be performed”

4240 Test successful

4241 “Parity error from Basic Engine to Serial”

4242 “Unexpected response from Basic Engine”

4243 “Communication time-out error”

4244 “Basic Engine returned error number 0xXX”

4245 “Sledge could not be moved to home

position”

4246 “Focus loop could not be closed”

4247 “Motor not on speed within time-out”

4248 “Radial loop could not be closed”

4249 “PLL could not lock in accessing or tracking

state”

4250 “Subcode or sector information could not be

read”

4251 “Requested subcode item could not be

found”

4252 “TOC could not be read in time”

4253 “Seek could not be performed”

4000 Test successful

4001 “Parity error from Basic Engine to Serial”

4002 “Unexpected response from Basic Engine”

4003 “Communication time-out error”

4004 “Basic Engine returned error number 0xXX”

4005 “Radial loop could not be closed”

4020 Test successful

4021 “Parity error from Basic Engine to Serial”

4022 “Unexpected response from Basic Engine”

4023 “Communication time-out error”

4024 “Basic Engine returned error number 0xXX”

4400 Test successful

4401 Test successful

4100 Test successful

4101 “Parity error from Basic Engine to Serial”

4102 “Unexpected response from Basic Engine”

4103 “Communication time-out error”

4104 “Basic Engine returned error number XX”

4120 Test successful

4121 “Parity error from Basic Engine to Serial”

4122 “Unexpected response from Basic Engine”

4123 “Communication time-out error”

4124 “Basic Engine returned error number XX”

Page 28

EN 28 SD-5.31SL5.

Test Instructions Mono Board SD5.31SL

Error

code Error text

4300 Test successful

4301 “Parity error from Basic Engine to Serial”

4302 “Unexpected response from Basic Engine”

4303 “Communication time-out error”

4304 “Basic Engine returned error number 0xXX”

4320 Test successful

4321 “Parity error from Basic Engine to Serial”

4322 “Unexpected response from Basic Engine”

4323 “Communication time-out error”

4324 “Basic Engine returned error number 0xXX”

3700 “Version: X.Y.Z”

3701 “Parity error from Basic Engine to Serial”

3702 “Unexpected response from Basic Engine”

3703 “Communication time-out error”

3704 “Basic Engine returned error number 0xXX”

5800 Test successful

5820 Test successful

5840 Test successful

5860 Test successful

5801 "Unexpected response from Basic Engine"

7000 "Manuf. ID: <XX>" "Device ID: <YY>"

7001 "Comm Test Failed"

7002 "Load Cmd Failed"

7003 "Load Dat Failed"

7004 "Run Cmd Failed"

7100 "ROM Checksum: XXXX"

7101 "Comm Test Failed"

7102 "Load Cmd Failed"

7103 "Load Dat Failed"

7104 "Run Cmd Failed"

7201 "Comm Test Failed"

7200 "Test successful"

7202 "Load Cmd Failed"

7203 "Load Dat Failed"

7204 "Run Cmd Failed"

7205 "Scratch circuit not OK"

5.12.3 Display PWB Nuclei

Error

code Error text

3000 “Test successful”

3001 “Disp not responding”

3002 “Disp key no response”

3003 “One or more patterns not correct”

3004 “Disp type invalid”

3020 “Test successful”

3021 “Disp not responding”

3022 “Disp key no response”

3023 “One or more patterns not correct”

3040 “Test successful”

3041 “Disp not responding”

3042 “Disp key no response”

3043 “One or more patterns not correct”

2700 “Model name in wich the test is running”

2701 “Disp key no response”

2702 “Disp not responding”

Error

code Error text

2707 “Stop key not pressed”

2708 “Pause key not pressed”

2709 “Play key not pressed”

2710 “Open/close key not pressed”

2713 “Previous key not pressed”

2714 “Next key not pressed”

2715 “More than one key not pressed”

2716 " Audio key not pressed"

2900 “Test successful”

2901 “Slave not responding”

2902 “Slave keyboard not responding”

2903 “Standby led not working”

2800 “Test successful”

2801 “Slave display controller not responding”

2802 “Slave keyboard not responding”

2803 “No key press received from remote control”

2600 “The ROM version of the slave processor =

0xXX, and the internal ID = 0xYY”

2601 “I2c bus busy”

2602 “I2c bus not working“

6000 P50 test

6001 “No readback on P50”

6002 “Disp not responding “

6003 “P50 readback error”

5.12.4 Processor & Peripherals Nuclei

Error

code Error text

700 Test successful

720 Test successful

740 Test successful

600 "All checksums are correct"

601 “Following checksum is faulty: BootCode1

Checksum is 0xY2 and is not correct (must be

0xZ2)”

601 “This test is not available when stand-alone

compiled”

6200 "Checksums = 0xA1, 0xB1, 0xC1, 0xD1"

6201 “This test is not available when stand-alone

compiled”

1000 Test successful

1001 Test successful

1020 Test successful

1021 Test successful

1100 Test successful

1104 “NVRAM reply time-out”

1200 Test successful

1202 “Slave bus not working”

1203 “Slave controller not responding”

1204 “Slave response is not correct”

5900 Test successful

Page 29

Test Instructions Mono Board SD5.31SL

EN 29SD-5.31SL 5.

Error

code Error text

5901 “I2c bus busy”

5902 “I2c bus not working“

5904 “DTS chip response not correct”

1300 Test successful

1301 “Parity error from basic engine to serial”

1302 “Parity error from serial to basic engine”

1303 “No communication between serial and basic

engine”

1304 “Communication time-out error”

1600 Test successful

1601 “The DVD SDRAM is faulty”

5.12.5 Log Nuclei

Error

code Error text

3100 "Show error log"

3101 "Error log is invalid"