Philips SCC2698BC1A84 Datasheet

INTEGRATED CIRCUITS

SCC2698B

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

Product specification

Supersedes data of 1995 May 01

IC19 Data Handbook

1998 Sep 04

Philips Semiconductors Product specification

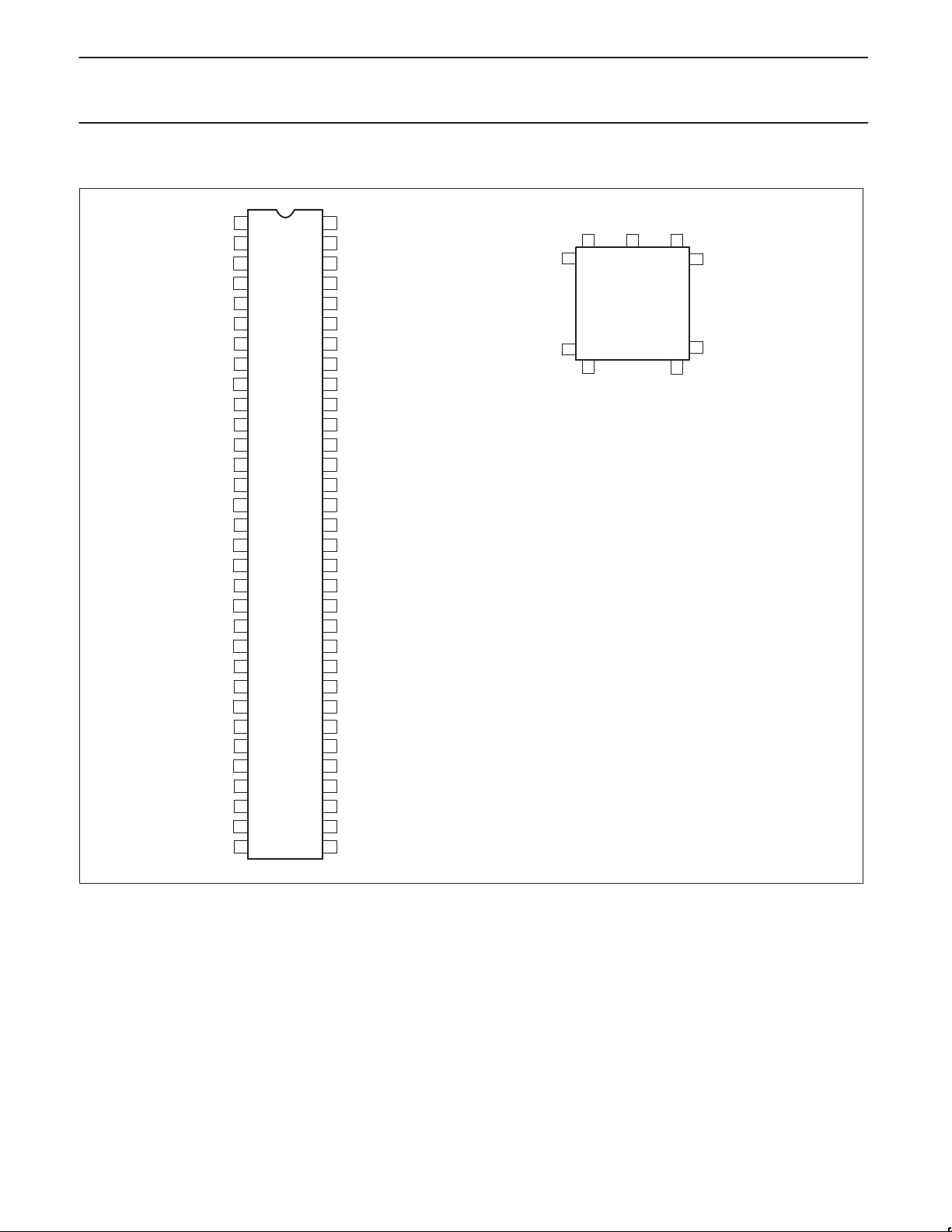

PACKAGES

DWG #

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

DESCRIPTION

The SCC2698B Enhanced Octal Universal Asynchronous

Receiver/Transmitter (Octal UART) is a single chip MOS-LSI

communications device that provides eight full-duplex asynchronous

receiver/transmitter channels in a single package. It is fabricated

with CMOS technology which combines the benefits of high density

and low power consumption.

The operating speed of each receiver and transmitter can be

selected independently as one of eighteen fixed baud rates, a 16X

clock derived from a programmable counter/timer, or an external 1X

or 16X clock. The baud rate generator and counter/timer can

operate directly from a crystal or from external clock inputs. The

ability to independently program the operating speed of the receiver

and transmitter make the Octal UART particularly attractive for

dual-speed channel applications such as clustered terminal

systems.

The receiver is quadruple buffered to minimize the potential of

receiver overrun or to reduce interrupt overhead in interrupt driven

systems. In addition, a handshaking capability is provided to disable

a remote UART transmitter when the receiver buffer is full.

The UART provides a power-down mode in which the oscillator is

frozen but the register contents are stored. This results in reduced

power consumption on the order of several magnitudes. The Octal

UART is fully TTL compatible and operates from a single +5V power

supply.

The SCC2698B is an upwardly compatible version of the 2698A

Octal UART. In PLCC packaging, it is enhanced by the addition of

receiver ready or FIFO full status outputs, and transmitter empty

status outputs for each channel on 16 multipurpose I/O pins. The

multipurpose I/O pins of the SCC2698B were inputs only on the

SCC2698A.

SCC2698B

FEATURES

• Eight full-duplex independent asynchronous receiver/

transmitters

• Quadruple buffered receiver data register

• Programmable data format:

– 5 to 8 data bits plus parity

– Odd, even, no parity or force parity

– 1, 1.5 or 2 stop bits programmable in 1/16-bit incre-

ments

• Baud rate for the receiver and transmitter selectable from:

– 18 fixed rates: 50 to 38.4K baud

Non-standard rates to 1 15.2K baud

– User-defined rates from the programmable counter/tim-

er associated with each of four blocks

– External 1x or 16x clock

• Parity, framing, and overrun error detection

• False start bit detection

• Line break detection and generation

• Programmable channel mode

– Normal (full-duplex), automatic echo, local loop back,

remote loopback

• Four multi-function programmable 16-bit counter/timers

• Four interrupt outputs with eight maskable interrupting

conditions for each output

• Receiver ready/FIFO full and transmitter ready status

available on 16 multi-function pins in PLCC package

• On-chip crystal oscillator

• TTL compatible

• Single +5V power supply with low power mode

• Eight multi-purpose output pins

• Sixteen multi-purpose I/O pins

• Sixteen multi-purpose Input pins with pull-up resistors

ORDERING INFORMATION

COMMERCIAL INDUSTRIAL

VCC = +5V +5%, TA = 0°C to +70°C VCC = +5V +5%, TA = –40°C to +85°C

84-Pin Plastic Leaded Chip Carrier (PLCC) SCC2698BC1A84 SCC2698BE1A84 SOT189-3

NOTE: Pin Grid Array (PGA) package version is available from Philips Components Military Division.

DD

1

PARAMETER RATING UNIT

to GND

2

3

3

2

Note 4

–0.5 to +7.0 V

–0.5 to V

+0.5 V

CC

o

C

o

C

ABSOLUTE MAXIMUM RATINGS

SYMBOL

T

A

T

STG

V

CC

V

S

P

D

NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any other condition above those indicated in the operation section of this specification is not

implied.

2. For operating at elevated temperatures, the device must be derated based on +150°C maximum junction temperature.

3. This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static

charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

4. Parameters are valid over specified temperature range. See ordering information table for applicable temperature range and operating

supply range.

1998 Sep 04 853-1 127 19974

Operating ambient temperature range

Storage temperature range –65 to +150

Voltage from V

Voltage from any pin to ground

Power dissipation 1 W

Philips Semiconductors Product specification

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

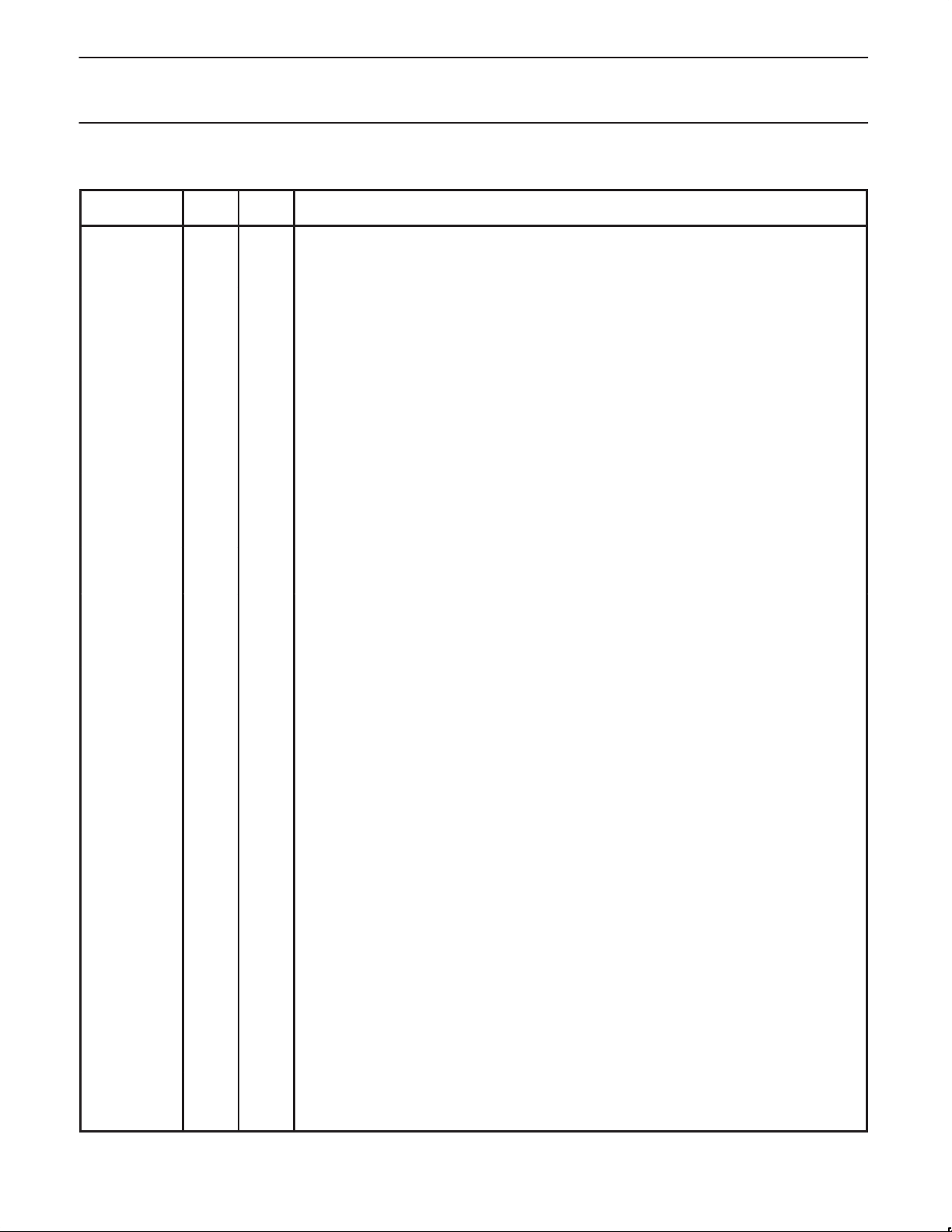

PIN CONFIGURATIONS

RxDa

V

CC

X2

X1/CLK

D0

D1

D2

NC

D3

NC

D4

NC

D5

RESET

D6

D7

CEN

WRN

GND

RDN

A0

A1

A2

A3

A4

A5

MP10a

MP10b

INTRAN

INTRBN

MP10c

MP10d

TxDb

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

45

45

44

43

42

41

40

39

38

37

36

35

34

33

TxDa

RxDc

TxDc

RxDe

MP10h

MP10g

RxDg

TxDe

TxDg

MPOa

MPOc

MPOe

MPOg

GND

MP10f

MP10e

RxDh

RxDf

RxDd

RxDb

TxDh

MPOh

Test input

MPOf

TxDf

MPOd

TxDd

INTRDN

INTRCN

V

CC

MPOb

SCC2698B

11

1

75

12

PLCC

32

33

Pin Function Pin Function Pin Function

1

TxDa

2

MPP2g

3

RxDa

4

MPP2h

5

V

CC

X2

6

X1/CLK

7

D0

8

D1

9

D2

10

D3

11

D4

12

D5

13

MPI1a

14

RESET

15

D6

16

D7

17

CEN

18

WRN

19

GND

20

MPI1b

21

RDN

22

A0

23

MPP1a

24

A1

25

MPP1b

26

A2

27

MPP2a

28

29

A3

30

MPP2b

31

A4

32

A5

33

MPI0a

34

MPI0b

35

INTRAN

36

INTRBN

37

MPI0c

38

MPI1c

39

MPI0d

40

MPI1d

41

TxDb

42

MPP1c

43

MPOb

44

MPP1d

45

V

CC

INTRCN

46

INTRDN

47

MPP2c

48

TxDd

49

MPP2d

50

MPOd

51

TxDf

52

MPOf

53

MPOh

54

TxDh

55

RxDb

56

74

54

53

57

RxDd

58

RxDf

59

RxDh

60

MPI1e

61

MPI0e

62

MPI1f

63

MPI0f

64

MPP1e

65

GND

66

MPP1f

67

MPOg

68

MPP2e

69

MPOe

70

MPP2f

71

MPOc

72

MPOa

73

TxDg

74

TxDe

75

RxDg

76

MPI0g

77

MPI0h

78

MPI1g

79

RxDe

80

MPIh

81

TxDc

82

MPP1g

83

RxDc

84

MPP1h

SD00184

1998 Sep 04

Figure 1. Pin Configurations

3

Philips Semiconductors Product specification

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

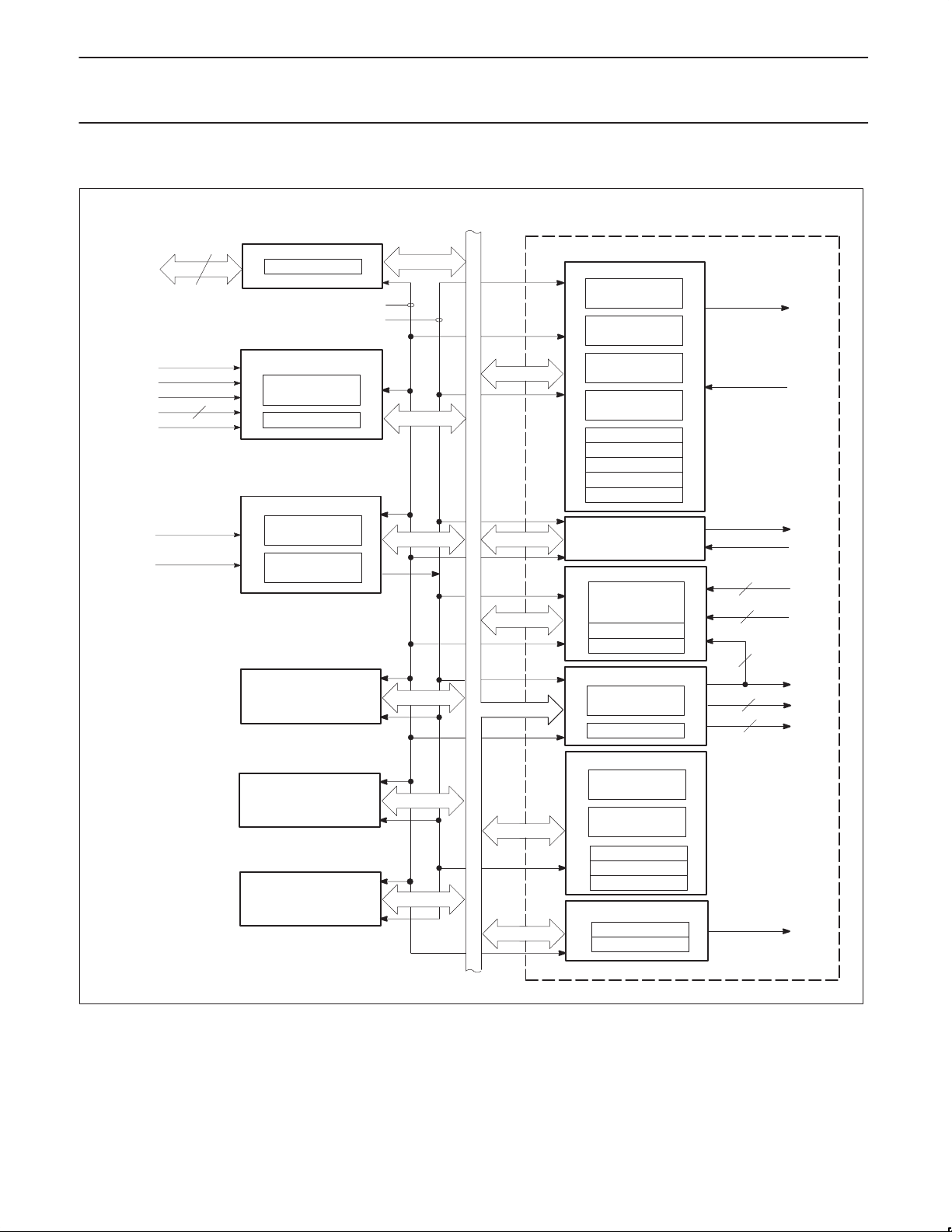

BLOCK DIAGRAM

D0–D7

RDN

WRN

CEN

A0–A5

RESET

X1/CLK

8

6

X2

BUS BUFFER

TIMING

CONTROL

OPERATION CONTROL

ADDRESS

DECODE

R/W CONTROL

TIMING

CRYSTAL

OSCILLATOR

POWER-ON

LOGIC

BLOCK B

(SAME AS A)

INTERNAL DATA

BUS

CHANNEL A

TRANSMIT HOLD

REGISTER

TRANSMIT SHIFT

REGISTER

RECEIVE HOLD

REGISTER (3)

RECEIVE SHIFT

REGISTER

MR1, 2

CR

SR

CSR Rx

CSR Tx

CHANNEL B

(AS ABOVE)

INPUT PORT

CHANGE-OF-

STATE

DETECTORS (4)

IPCR

ACR

OUTPUT PORT

FUNCTION SELECT

LOGIC

OPCR

SCC2698B

BLOCK A

TxDA

RxDA

TxDb

RxDb

4

MPI0

4

MPIb

4

MPP1

4

MPP2

2

MPO

1998 Sep 04

BLOCK C

(SAME AS A)

BLOCK D

(SAME AS A)

Figure 2. Block Diagram

4

TIMING

CLOCK

SELECTORS

COUNTER/

TIMER

ACR

CTUR

CTLR

INTERRUPT CONTROL

IMR

ISR

INTRAN

SD00185

Philips Semiconductors Product specification

MNEMONIC

PIN

TYPE

NAME AND FUNCTION

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

PIN DESCRIPTION

PIN

NO.

D0–D7 8–13,

CEN 18 I Chip Enable: Active-Low input. When Low, data transfers between the CPU and the Octal UART are

WRN 19 I Write Strobe: Active-Low input. A Low on this pin while CEN is Low causes the contents of the data

RDN 22 I Read Strobe: Active-Low input. A Low on this pin while CEN is Low causes the contents of the

A0–A5 23, 25,

RESET 15 I Reset: Master reset. A High on this pin clears the status register (SR), clears the interrupt mask

INTRAN–

INTRDN

X1/CLK 7 I Crystal 1: Crystal or external clock input. When using the crystal oscillator, this pin serves as the

X2 6 I Crystal 2: Connection for other side of crystal. If an external source is used instead of a crystal, this

RxDa–RxDh 3, 56,

TxDa–TxDh 1, 41,

MPOa–MPOh 72, 43,

MPI0a–MPI0h 33, 34,

16, 17

27, 29,

31, 32

35, 36,

46, 47

83, 57,

79, 58,

75, 59

81, 49,

74, 52,

73, 55

71, 51,

69, 53,

67, 54

37, 39,

61, 63,

76, 77

I/O Data Bus: Active–High 8-bit bidirectional 3-State data bus. Bit 0 is the LSB and bit 7 is the MSB. All

data, command, and status transfers between the CPU and the Octal UART take place over this bus.

The direction of the transfer is controlled by the WRN and RDN inputs when the CEN input is low.

When the CEN input is High, the data bus is in the 3-State condition.

enabled on D0–D7 as controlled by the WRN, RDN and A0–A5 inputs. When CEN is High, the Octal

UART is effectively isolated from the data bus and D0–D7 are placed in the 3-State condition.

bus to be transferred to the register selected by A0–A5. The transfer occurs on the trailing (rising)

edge of the signal.

register selected by A0–A5 to be placed on the data bus. The read cycle begins on the leading

(falling) edge of RDN.

I Address Inputs: Active-High address inputs to select the Octal UART registers for read/write

operations.

register (IMR), clears the interrupt status register (ISR), clears the output port configuration register

(OPCR), places the receiver and transmitter in the inactive state causing the TxD output to go to the

marking (High) state, and stops the counter/timer. Clears power-down mode and interrupts. Clears

Test Modes, sets MR pointer to MR1.

O Interrupt Request: This active-Low open drain output is asserted on occurrence of one or more of

eight maskable interrupting conditions. The CPU can read the interrupt status register to determine

the interrupting condition(s).

connection for one side of the crystal. If a crystal is not used, an external clock is supplied at this

input. An external clock (or crystal) is required even if the internal baud rate generator is not utilized.

This clock is used to drive the internal baud rate generator, as an optional input to the timer/counter,

and to provide other clocking signals required by the chip.

connection should be left open (see Figure 7).

I Receiver Serial Data Input: The least significant bit is received first. If external receiver clock is

specified, this input is sampled on the rising edge of the clock. If internal clock is used, the RxD input

is sampled on the rising edge of the RxC1x signal as seen on the MPO pin.

O Transmitter Serial Data Output: The least significant bit is transmitted first. This output is held in the

marking (High) condition when the transmitter is idle or disabled and when the Octal UART is

operating in local loopback mode. If external transmitter is specified, the data is shifted on the falling

edge of the transmitter clock. If internal clock is used, the TxD output changes on the falling edge of

the TxC1x signal as seen on the MPO pin.

O Multi-Purpose Output: Each of the four DUARTS has two MPO pins (one per UART). One of the

following eight functions can be selected for this output pin by programming the OPCR (output port

configuration register). Note that reset conditions MPO pins to RTSN.

RTSN – Request to send active-Low output. This output is asserted and negated via the command

register. By appropriate programming of the mode registers, (MR1[7])=1 R TSN can be programmed to

be automatically reset after the character in the transmitter is completely shifted or when the receiver

FIFO and shift register are full. RTSN is an internal signal which normally represents the condition of

the receiver FIFO not full, i.e., the receiver can request more data to be sent. However, it can also be

controlled by the transmitter empty and the commands 8h and 9h written to the CR (command

register).

C/TO – The counter/timer output.

TxC1X – The 1X clock for the transmitter.

TxC16X – The 16X clock for the transmitter.

RxC1X – The 1X clock for the receiver.

RxC16X – The 16X clock for the receiver.

TxRDY – Transmitter holding register empty signal.

RxRDY/FFULL – Receiver FIFO not empty/full signal.

I Multi-Purpose Input 0: This pin (one in each UART) is programmable. Its state can always be read

through the IPCR bit 0, or the IPR bit 0.

CTSN: By programming MR2[4] to a 1, this input controls the clear-to-send function for the

transmitter. It is active low. This pin is provided with a change-of-state detector.

SCC2698B

1998 Sep 04

5

Philips Semiconductors Product specification

MNEMONIC

PIN

TYPE

NAME AND FUNCTION

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

PIN DESCRIPTION (Continued)

PIN

NO.

MPI1a–MPI1h 14, 21,

MPP1a–MPP1h 24, 26,

MPP2a–MPP2h 28, 30,

Test Input – I T est Input: This pin is used as an input for test purposes at the factory while in test mode. This pin

V

CC

GND 20, 65 I Ground

38, 40,

60, 62,

78, 80

42, 44,

64, 66,

82, 84

48, 50,

68, 70,

2, 4

5, 45 I Power Supply: +5V supply input.

I Multi-Purpose Input 1: This pin (one for each unit) is programmable. Its state can always be

determined by reading the IPCR bit 1 or IPR bit 1.

C/TCLK – This input will serve as the external clock for the counter/timer when ACR[5] is set to 0.

This occurs only for channels a, c, e, and g since there is one counter/timer for each DUART block.

This pin is provided with a change-of-state detector.

I/O Multi-Purpose Pin 1: This pin (one for each UART) is programmed to be an input or an output

according to the state of OPCR[7]. (0 = input, 1 = output). The state of the multi-purpose pin can

always be determined by reading the IPR. When programmed as an input, it will be the transmitter

clock (TxCLK). It will be 1x or 16x according to the clock select registers (CSR[3.0]). When

programmed as an output, it will be the status register TxRDY bit. These pins have a small pull-up

device.

I/O Multi-Purpose Pin 2: This pin (one for each UART) is programmed to be an input or an output

according to the state of OPCR[7]. (0 = input, 1 = output). The state of the multi-purpose pin can

always be determined by reading the IPR. When programmed as an input, it will be the receiver clock

(RxCLK). It will be 1x or 16x according to the clock select registers (CSR[7:4). When programmed as

an output, it will be the ISR status register RxRDY/FIFO full bit. These pins have a small pull-up

device.

can be treated as ‘N/C’ by the user. It can be tied high, or left open.

SCC2698B

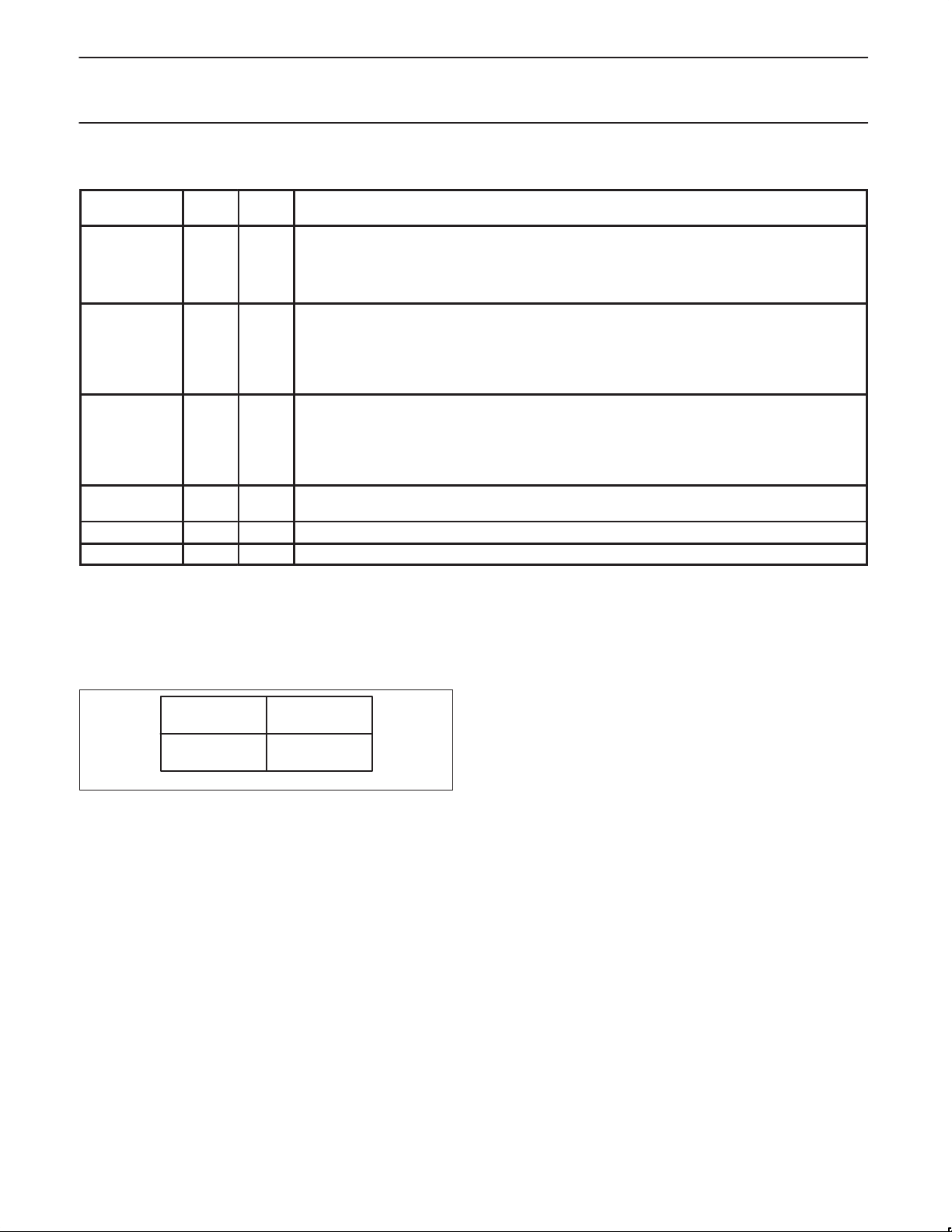

BLOCK DIAGRAM

As shown in the block diagram, the Octal UART consists of: data

bus buffer, interrupt control, operation control, timing, and eight

receiver and transmitter channels. The eight channels are divided

into four different blocks, each block independent of each other (see

Figure 3).

BLOCK A

CHANNELS a, b

BLOCK B

CHANNELS c, d

Figure 3. Channel Architecture

BLOCK C

CHANNELS e, f

BLOCK D

CHANNELS g, h

SD00186

Channel Blocks

There are four blocks (Figure 3), each containing two sets of

receiver/transmitters. In the following discussion, the description

applies to Block A which contains channels a and b. However, the

same information applies to all channel blocks.

Data Bus Buffer

The data bus buffer provides the interface between the external and

internal data buses. It is controlled by the operation control block to

allow read and write operations to take place between the controlling

CPU and the Octal UART.

Interrupt Control

A single interrupt output per block (INTRN) is provided which is

asserted on occurrence of any of the following internal events:

–Transmit holding register ready for each channel

–Receive holding register ready or FIFO full for each channel

–Change in break received status for each channel

–Counter reached terminal count

–Change in MPI input

Associated with the interrupt system are the interrupt mask register

(IMR) and the interrupt status register (ISR). The IMR can be

programmed to select only certain conditions, of the above, to cause

INTRN to be asserted. The ISR can be read by the CPU to

determine all currently active interrupting conditions. However, the

bits of the ISR are not masked by the IMR. The transmitter ready

status and the receiver ready or FIFO full status can be provided on

MPP1a, MPP1b, MPP2a, and MPP2b by setting OPCR[7]. these

outputs are not masked by IMR.

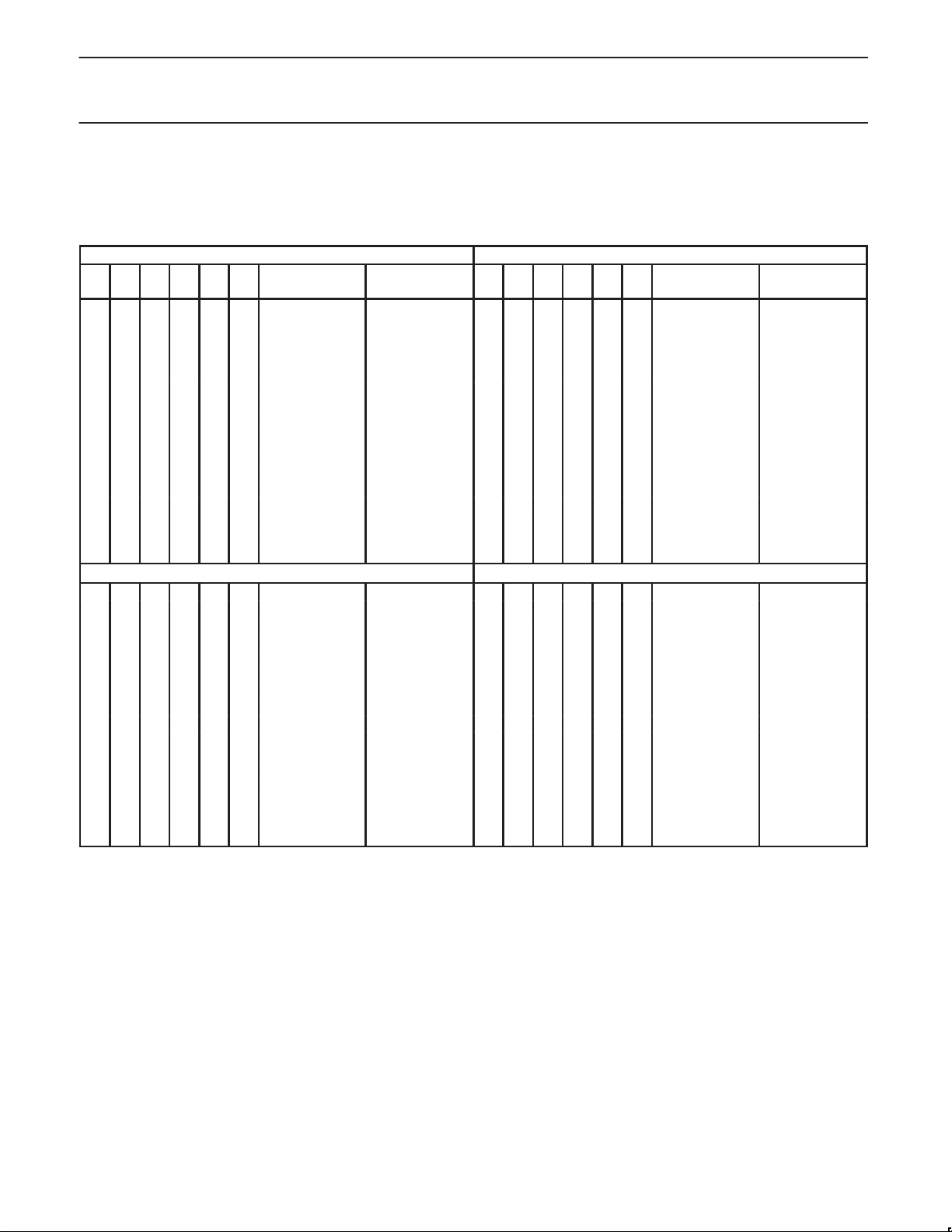

Operation Control

The operation control logic receives operation commands from the

CPU and generates appropriate signals to internal sections to

control device operation. It contains address decoding and read and

write circuits to permit communications with the microprocessor via

the data bus buffer. The functions performed by the CPU read and

write operations are shown in Table 1.

Mode registers 1 and 2 are accessed via an auxiliary pointer. The

pointer is set to MR1 by RESET or by issuing a reset pointer

command via the command register . Any read or write of the mode

register while the pointer is at MR1 switches the pointer to MR2. The

pointer then remains at MR2 so that subsequent accesses are to

MR2, unless the pointer is reset to MR1 as already described.

Timing Circuits

The timing block consists of a crystal oscillator, a baud rate

generator, a programmable 16-bit counter/timer for each block, and

two clock selectors.

Crystal Clock

The crystal oscillator operates directly from a 3.6864MHz crystal

connected across the X1/ CLK and X2 inputs with a minimum of

external components. If an external clock of the appropriate

frequency is available, it may be connected to X1/CLK. If an external

clock is used instead of a crystal, X1 must be driven and X2 left

1998 Sep 04

6

Philips Semiconductors Product specification

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

floating as shown in Figure 7. The clock serves as the basic timing

reference for the baud rate generator (BRG), the counter/timer, and

other internal circuits. A clock frequency, within the limits specified in

Table 1. Register Addressing

Units A and B Units E and F

A5 A4 A3 A2 A1 A0 READ (RDN=0)

WRITE

(WRN=0)

0 0 0 0 0 0 MR1a, MR2a MR1a, MR2a 1 0 0 0 0 0 MR1e, MR2e MR1e, MR2e

0 0 0 0 0 1 SRa CSRa 1 0 0 0 0 1 SRe CSRe

0 0 0 0 1 0 BRG Test

2

CRa 1 0 0 0 1 0 Reserved

0 0 0 0 1 1 RHRa THRa 1 0 0 0 1 1 RHRe THRe

0 0 0 1 0 0 IPCRA ACRA 1 0 0 1 0 0 IPCRC ACRC

0 0 0 1 0 1 ISRA IMRA 1 0 0 1 0 1 ISRC IMRC

0 0 0 1 1 0 CTUA CTURA 1 0 0 1 1 0 CTUC CTURC

0 0 0 1 1 1 CTLA CTLRA 1 0 0 1 1 1 CTLC CTLRC

0 0 1 0 0 0 MR1b, MR2b MR1b, MR2b 1 0 1 0 0 0 MR1f, MR2f MR1f, MR2f

0 0 1 0 0 1 SRb CSRb 1 0 1 0 0 1 SRf CSRf

0 0 1 0 1 0 1X/16X Test

2

CRb 1 0 1 0 1 0 Reserved

0 0 1 0 1 1 RHRb THRb 1 0 1 0 1 1 RHRf THRf

0 0 1 1 0 0 Reserved

1

Reserved

1

0 0 1 1 0 1 Input port A OPCRA 1 0 1 1 0 1 Input port C OPCRC

0 0 1 1 1 0 Start C/T A Reserved

0 0 1 1 1 1 Stop C/T A Reserved

1

1

Units C and D Units G and H

0 1 0 0 0 0 MR1c, MR2c MR1c, MR2c 1 1 0 0 0 0 MR1g, MR2g MR1g, MR2g

0 1 0 0 0 1 SRc CSRc 1 1 0 0 0 1 SRg CSRg

0 1 0 0 1 0 Reserved

1

CRc 1 1 0 0 1 0 Reserved

0 1 0 0 1 1 RHRc THRc 1 1 0 0 1 1 RHRg THRg

0 1 0 1 0 0 IPCRB ACRB 1 1 0 1 0 0 IPCRD ACRD

0 1 0 1 0 1 ISRB IMRB 1 1 0 1 0 1 ISRD IMRD

0 1 0 1 1 0 CTUB CTURB 1 1 0 1 1 0 CTUD CTURD

0 1 0 1 1 1 CTLB CTLRB 1 1 0 1 1 1 CTLD CTLRD

0 1 1 0 0 0 MR1d, MR2d MR1d, MR2d 1 1 1 0 0 0 MR1h, MR2h MR1h, MR2h

0 1 1 0 0 1 SRd CSRd 1 1 1 0 0 1 SRh CSRh

0 1 1 0 1 0 Reserved

1

CRd 1 1 1 0 1 0 Reserved

0 1 1 0 1 1 RHRd THRd 1 1 1 0 1 1 RHRh THRh

0 1 1 1 0 0 Reserved

1

Reserved

1

0 1 1 1 0 1 Input port B OPCRB 1 1 1 1 0 1 Input port D OPCRD

0 1 1 1 1 0 Start C/T B Reserved

0 1 1 1 1 1 Stop C/T B Reserved

1

1

NOTE:

1. Reserved registers should never be read during normal operation since they are reserved for internal diagnostics.

ACR = Auxiliary control register SR = Status Register

CR = Command register THR = Tx holding register

CSR = Clock select register RHR = Rx holding register

CTL = Counter/timer lower IPCR = Input port change register

CTLR = Counter/timer lower register ISR = Interrupt status register

CTU = Counter/timer upper IMR = Interrupt mask register

CTUR = Counter/timer upper register OPCR= Output port configuration register

MR = Mode register

2. See T able 5 for BRG Test frequencies in this data sheet, and

and SCC2698B”

Philips Semiconductors ICs for Data Communications, IC-19, 1994.

“Extended baud rates for SCN2681, SCN68681, SCC2691, SCC2692, SCC68681

BRG

The baud rate generator operates from the oscillator or external

clock input and is capable of generating 18 commonly used data

communications baud rates ranging from 50 to 38.4K baud. Thirteen

of these are available simultaneously for use by the receiver and

transmitter. Eight are fixed, and one of two sets of five can be

selected by programming ACR[7]. The clock outputs from the BRG

are at 16X the actual baud rate. The counter/timer can be used as a

the electrical specifications, must be supplied even if the internal

BRG is not used.

A5 A4 A3 A2 A1 A0 READ (RDN=0)

1 0 1 1 0 0 Reserved

1 0 1 1 1 0 Start C/T C Reserved

1 0 1 1 1 1 Stop C/T C Reserved

1 1 1 1 0 0 Reserved

1 1 1 1 1 0 Start C/T D Reserved

1 1 1 1 1 1 Stop C/T D Reserved

timer to produce a 16X clock for any other baud rate by counting

down the crystal clock or an external clock. The clock selectors

allow the independent selection, by the receiver and transmitter, of

any of these baud rates or an external timing signal.

Counter/Timer (C/T)

There are four C/Ts in the Octal UART, one for each block. The C/T

operation is programmed by ACR[6:4]. One of eight timing sources

SCC2698B

WRITE

(WRN=0)

1

1

1

1

1

1

CRe

CRf

Reserved

CRg

CRh

Reserved

1

1

1

1

1

1

1998 Sep 04

7

Philips Semiconductors Product specification

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

can be used as the input to the C/T. The output of the C/T is

available to the clock selectors and can also be programmed by

OPCR[2:0] for channel a and OPCR[6:4] for channel b, to be output

on the MPOa or MPOb pin, respectively.

A register read address is reserved to issue a start counter/timer

command and a second register read address is reserved to issue a

stop counter/timer command for each timer. For example, to issue a

stop counter command for the counter-timer in block B, a read of

address ‘1F’ must be performed. See Table 1 for register addressing.

In the timer mode, the C/T generates a square wave whose period

is twice the number of clock periods loaded into the C/T upper and

lower registers. The counter ready bit in the ISR is set once each

cycle of the square wave. If the value in CTUR or CTLR is changed,

the current half-period will not be affected, but subsequent

half-periods will be affected. In this mode the C/T runs continuously

and does not recognize the stop C/T command (the command only

resets the counter ready bit in the ISR). Receipt of a start C/T

command causes the counter to terminate the current timing cycle

and to begin a new cycle using the values in CTUR and CTLR.

In the counter mode, the C/T counts down the number of pulses

loaded into CTUR and CTLR. Counting begins upon receipt of a

start counter command. Upon reaching terminal count, the counter

ready bit in the ISR is set. The counter continues counting past the

terminal count until stopped by the CPU. If MPO is programmed to

be the output of the C/T, the output remains High until terminal count

is reached, at which time it goes Low. The output returns to the High

state and the counter ready bit is cleared when the counter is

stopped by a stop counter command. The CPU may change the

values of CTUR and CTLR at any time, but the new count becomes

effective only on the next start counter command following a stop

counter command. If new values have not been loaded, the previous

count values are preserved and used for the next count cycle.

In the counter mode, the current value of the upper and lower eight

bits of the counter may be read by the CPU. It is recommended that

the counter be stopped when reading to prevent potential problems

which may occur if a carry from the lower eight bits to the upper eight

bits occurs between the times that both halves of the counter are read.

However, a subsequent start counter command causes the counter to

begin a new count cycle using the values in CTUR and CTLR.

Receiver and Transmitter

The Octal UART has eight full-duplex asynchronous

receiver/transmitters. The operating frequency for the receiver and

transmitter can be selected independently from the baud rate

generator, the counter/timer, or from an external input.

Registers associated with the communications channel are the

mode registers (MR1 and MR2), the clock select register (CSR), the

command register (CR), the status register (SR), the transmit

holding register (THR), and the receive holding register (RHR).

Transmitter

The transmitter accepts parallel data from the CPU and converts it

to a serial bit stream on the TxD output pin. It automatically sends a

start bit followed by the programmed number of data bits, an

optional parity bit, and the programmed number of stop bits. The

least significant bit is sent first. Following the transmission of the

stop bits, if a new character is not available in the THR, the TxD

output remains high and the TxEMT bit in the SR will be set to 1.

Transmission resumes and the TxEMT bit is cleared when the CPU

loads a new character in the THR. In the 16X clock mode, this also

re-synchronizes the internal 1X transmitter clock so that

transmission of the new character begins with minimum delay.

SCC2698B

The transmitter can be forced to send a break (continuous Low

condition) by issuing a start break command via the CR. The break is

terminated by a stop break command. If the transmitter is disabled, it

continues operating until the characters currently being transmitted and

the character in the THR, if any, are completely sent out. Characters

cannot be loaded in the THR while the transmitter is disabled.

Receiver

The receiver accepts serial data on the RxD pin, converts the serial

input to parallel format, checks for start bit, stop bit, parity bit (if any),

or break condition, and presents the assembled character to the

CPU. The receiver looks for a High-to-Low (mark-to-space)

transition of the start bit on the RxD input pin. If a transition is

detected, the state of the RxD pin is sampled again each 16X clock

for 7-1/2 clocks (16X clock mode) or at the next rising edge of the bit

time clock (1X clock mode).

If RxD is sampled High, the start bit is invalid and the search for a

valid start bit begins again. If RxD is still Low, a valid start bit is

assumed and the receiver samples the input. This continues at one

bit time intervals, at the theoretical center of the bit, until the proper

number of data bits and the parity bit (if any) have been assembled,

and one stop bit has been detected. The data is then transferred to

the RHR and the RxRDY bit in the SR is set to a one. If the

character length is less than eight bits, the most significant unused

bits in the RHR are set to zero.

After the stop bit is detected, the receiver will immediately look for

the next start bit. However, if a non-zero character was received

without a stop bit (i.e. framing error) and RxD remains low for

one-half of the bit period after the stop bit was sampled, then the

receiver operates as if a new start bit transition had been detected at

that point (one-half bit time after the stop bit was sampled). The

parity error, framing error and overrun error (if any) are strobed into

the SR at the received character boundary, before the RxRDY

status bit is set.

If a break condition is detected (RxD is low for the entire character

including the stop bit), only one character consisting of all zeros will

be loaded in the FIFO and the received break bit in the SR is set to

1. The RxD input must return to high for two (2) clock edges of the

X1 crystal clock for the receiver to recognize the end of the break

condition and begin the search for a start bit. This will usually

require a high time of one X1 clock period or 3 X1 edges since

the clock of the controller is not synchronous to the X1 clock.

TIMEOUT MODE

The timeout mode uses the received data stream to control the

counter. Each time a received character is transferred from the shift

register to the RHR, the counter is restarted. If a new character is

not received before the counter reaches zero count, the counter

ready bit is set, and an interrupt can be generated. This mode can

be used to indicate when data has been left in the Rx FIFO for more

than the programmed time limit. Otherwise, if the receiver has been

programmed to interrupt the CPU when the receive FIFO is full, and

the message ends before the FIFO is full, the CPU may not know

when there is data left in the FIFO, The CTU and CTL value would

be programmed for just over one character time, so that the CPU

would be interrupted as soon as it has stopped receiving continuous

data. This mode can also be used to indicate when the serial line

has been marking for longer than the programmed time limit. In this

case, the CPU has read all of the characters from the FIFO, but the

last character received has started the count. If there is no new data

during the programmed time interval, the counter ready bit will get

set, and an interrupt can be generated.

1998 Sep 04

8

Philips Semiconductors Product specification

Enhanced octal universal asynchronous

receiver/transmitter (Octal UART)

This mode is enabled by writing the appropriate command to the

command register. Writing an ‘Ax’ to CRA or CRB will invoke the

timeout mode for that channel. Writing a ‘Cx’ to CRA or CRB will

disable the timeout mode. The timeout mode should only be used by

one channel at once, since it uses the C/T. CTU and CTL must be

loaded with a value greater than the normal receive character

period. The timeout mode disables the regular STAR T/STOP

counter commands and puts the C/T into counter mode under the

control of the received data stream. Each time a received character

is transferred from the shift register to the RHR, the C/T is stopped

after one C/T clock, reloaded with the value in CTU and CTL and

then restarted on the next C/T clock. If the C/T is allowed to end the

count before a new character has been received, the counter ready

bit, ISR[3], will be set. If IMR[3] is set, this will generate an interrupt.

Since receiving a character restarts the C/T, the receipt of a

character after the C/T has timed out will clear the counter ready bit,

ISR[3], and the interrupt. Invoking the ‘Set Timeout Mode On’

command, CRx=‘Ax’, will also clear the counter ready bit and stop

the counter until the next character is received.

This mode is cleared by “Disable Time-out Mode” command (C0) to

the command register.

Time Out Mode Caution

When operating in the special time out mode, it is possible to

generate what appears to be a “false interrupt”, i.e., an interrupt

without a cause. This may result when a time-out interrupt occurs

and then, BEFORE the interrupt is serviced, another character is

received, i.e., the data stream has started again. (The interrupt

latency is longer than the pause in the data strea.) In this case,

when a new character has been receiver, the counter/timer will be

restarted by the receiver, thereby withdrawing its interrupt. If, at this

time, the interrupt service begins for the previously seen interrupt, a

read of the ISR will show the “Counter Ready” bit not set. If nothing

else is interrupting, this read of the ISR will return a x’00 character.

RECEIVER FIFO

The RHR consists of a first-in-first-out (FIFO) with a capacity of

three characters. Data is loaded from the receive shift register into

the top-most empty position of the FIFO. The RxRDY bit in the

status register (SR) is set whenever one or more characters are

available to be read, and a FFULL status bit is set if all three stack

positions are filled with data. Either of these bits can be selected to

cause an interrupt. A read of the RHR, outputs the data at the top of

the FIFO. After the read cycle, the data FIFO and its associated

status bits are ‘popped’ thus emptying a FIFO position for new data.

Receiver Status Bits

In addition to the data word, three status bits (parity error, framing

error, and received break) are appended to each data character in

the FIFO. Status can be provided in two ways, as programmed by

the error mode control bit in the mode register. In the ‘character’

mode, status is provided on a character-by-character basis: the

status applies only to the character at the top of the FIFO. In the

‘block’ mode, the status provided in the SR for these three bits is the

logical OR of the status for all characters coming to the top of the

FIFO since the last reset error command was issued. In either

mode, reading the SR does not affect the FIFO. The FIFO is

‘popped’ only when the RHR is read. Therefore, the SR should be

read prior to reading the corresponding data character.

If the FIFO is full when a new character is received, that character is

held in the receive shift register until a FIFO position is available. If

an additional character is received while this state exists, the

SCC2698B

contents of the FIFO are not affected: the character previously in the

shift register is lost and the overrun error status bit, SR[4], will be set

upon receipt of the start bit of the new (overrunning) character.

The receiver can control the deactivation of RTS. If programmed to

operate in this mode, the RTSN output will be negated when a valid

start bit was received and the FIFO is full. When a FIFO position

becomes available, the RTSN output will be re-asserted

automatically. This feature can be used to prevent an overrun, in

the receiver, by connecting the RTSN output to the CTSN input of

the transmitting device.

Receiver Reset and Disable

Receiver disable stops the receiver immediately – data being

assembled if the receiver shift register is lost. Data and status in the

FIFO is preserved and may be read. A re-enable of the receiver

after a disable will cause the receiver to begin assembling

characters at the next start bit detected. A receiver reset will discard

the present shift register data, reset the receiver ready bit (RxRDY),

clear the status of the byte at the top of the FIFO and re-align the

FIFO read/write pointers. This has the appearance of “clearing or

flushing” the receiver FIFO. In fact, the FIFO is NEVER cleared!

The data in the FIFO remains valid until overwritten by another

received character. Because of this, erroneous reading or extra

reads of the receiver FIFO will miss-align the FIFO pointers and

result in the reading of previously read data. A receiver reset will

re-align the pointers.

WAKE-UP MODE

In addition to the normal transmitter and receiver operation

described above, the Octal UART incorporates a special mode

which provides automatic wake-up of the receiver through address

frame recognition for multiprocessor communications. This mode is

selected by programming bits MR1[4:3] to ‘11’.

In this mode of operation, a ‘master’ station transmits an address

character followed by data characters for the addressed ‘slave’

station. The slave stations, whose receivers are normally disabled,

examine the received data stream and ‘wake-up’ the CPU [by

setting RxRDY) only upon receipt of an address character. The CPU

compares the received address to its station address and enables

the receiver if it wishes to receive the subsequent data characters.

Upon receipt of another address character, the CPU may disable the

receiver to initiate the process again.

A transmitted character consists of a start bit, the programmed

number of data bits, an address/data (A/D) bit, and the programmed

number of stop bits. The polarity of the transmitted A/D bit is

selected by the CPU by programming bit MR1[2]; MR1[2] = 0

transmits a zero in the A/D bit position which identifies the

corresponding data bits as data; MR1[2] = 1 transmits a one in the

A/D bit position which identifies the corresponding data bits as an

address. The CPU should program the mode register prior to

loading the corresponding data bits in the THR.

While in this mode, the receiver continuously looks at the received

data stream, whether it is enabled or disabled. If disabled, it sets the

RxRDY status bit and loads the character in the RHR FIFO if the

received A/D bit is a one, but discards the received character if the

received A/D bit is a zero. If enabled, all received characters are

then transferred to the CPU via the RHR. In either case, the data

bits are loaded in the data FIFO while the A/D bit is loaded in the

status FIFO position normally used for parity error (SR[5]). Framing

error, overrun error, and break detect operate normally whether or

not the receiver is enabled.

1998 Sep 04

9

Loading...

Loading...