INTEGRATED CIRCUITS

SCC2691

Universal asynchronous

receiver/transmitter (UART)

Product specification

Supersedes data of 1995 May 01

IC19 Data Handbook

1998 Sep 04

Philips Semiconductors Product specification

SCC2691Universal asynchronous receiver/transmitter (UART)

DESCRIPTION

The Philips Semiconductors SCC2691 Universal Asynchronous

Receiver/Transmitter (UART) is a single-chip CMOS-LSI

communications device that provides a full-duplex asynchronous

receiver/transmitter. It is fabricated with Philips Semiconductors

CMOS technology which combines the benefits of high density and

low power consumption.

The operating speed of the receiver and transmitter can be selected

independently as one of 18 fixed baud rates, a 16X clock derived

from a programmable counter/timer, or an external 1X or 16X clock.

The baud rate generator and counter/timer can operate directly from

a crystal or from external clock inputs. The ability to independently

program the operating speed of the receiver and transmitter make

the UART particularly attractive for dual-speed channel applications

such as clustered terminal systems.

The receiver is quadruple buffered to minimize the potential of

receiver overrun or to reduce interrupt overhead in interrupt driven

systems. In addition, a handshaking capability is provided to disable

a remote UART transmitter when the receiver buffer is full.

The UART provides a power-down mode in which the oscillator is

frozen but the register contents are stored. This results in reduced

power consumption on the order of several magnitudes.

The UART is fully TTL compatible and operates from a single +5V

power supply.

FEA TURES

•Full-duplex asynchronous receiver/transmitter

•Quadruple buffered receiver data register

•Programmable data format:

– 5 to 8 data bits plus parity

– Odd, even, no parity or force parity

– 1, 1.5 or 2 stop bits programmable in 1/16-bit increments

•16-bit programmable Counter/Timer

•Baud rate for the receiver and transmitter selectable from:

– 22 fixed rates: 50 to 115.2K baud

– Non-standard rates to 115.2kb

– Non-standard user-defined rate derived from programmable

timer/ counter

– External 1X or 16X clock

•Parity, framing, and overrun detection

•False start bit detection

•Line break detection and generation

•Programmable channel mode

– Normal (full-duplex)

– Automatic echo

– Local loopback

– Remote Loopback

•Multi-function programmable 16-bit counter/timer

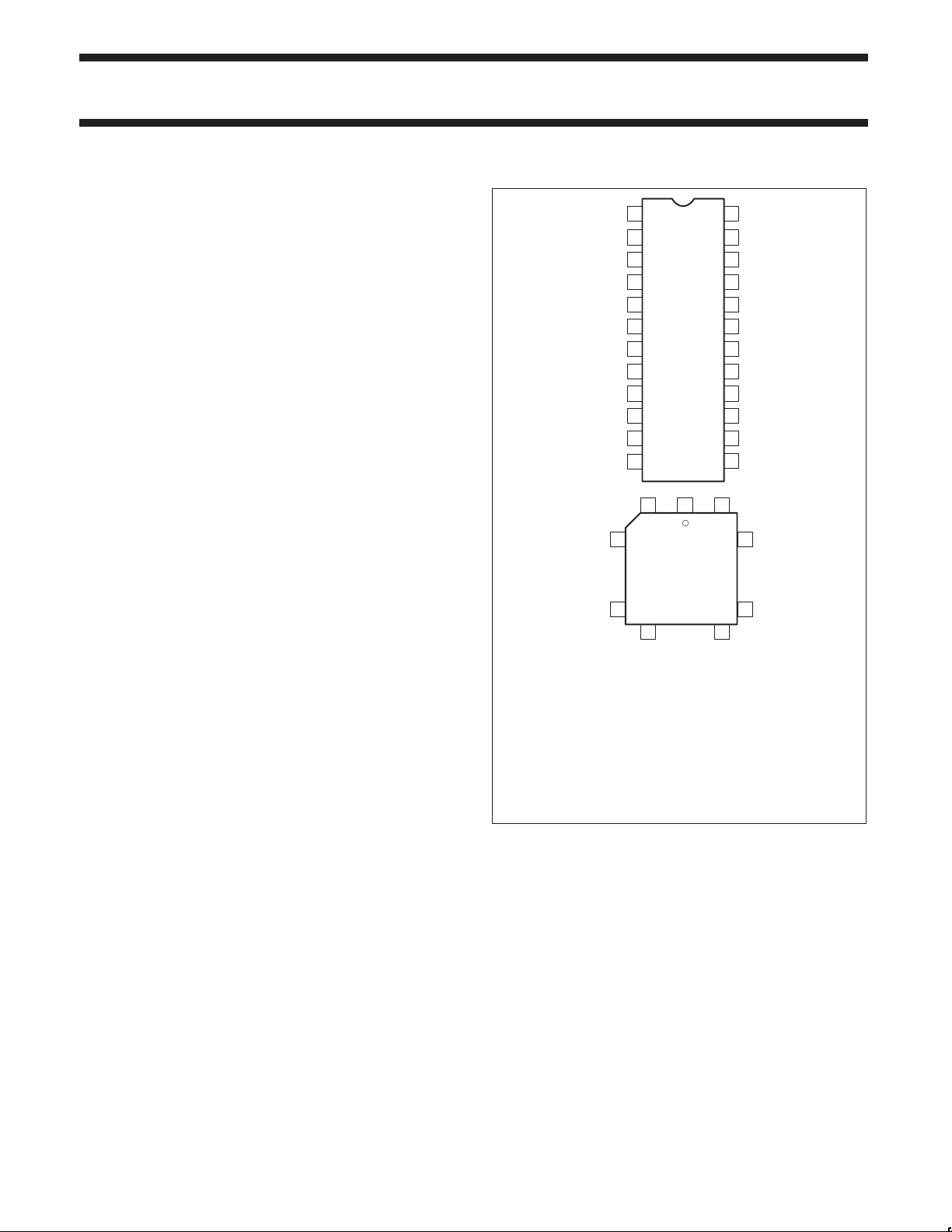

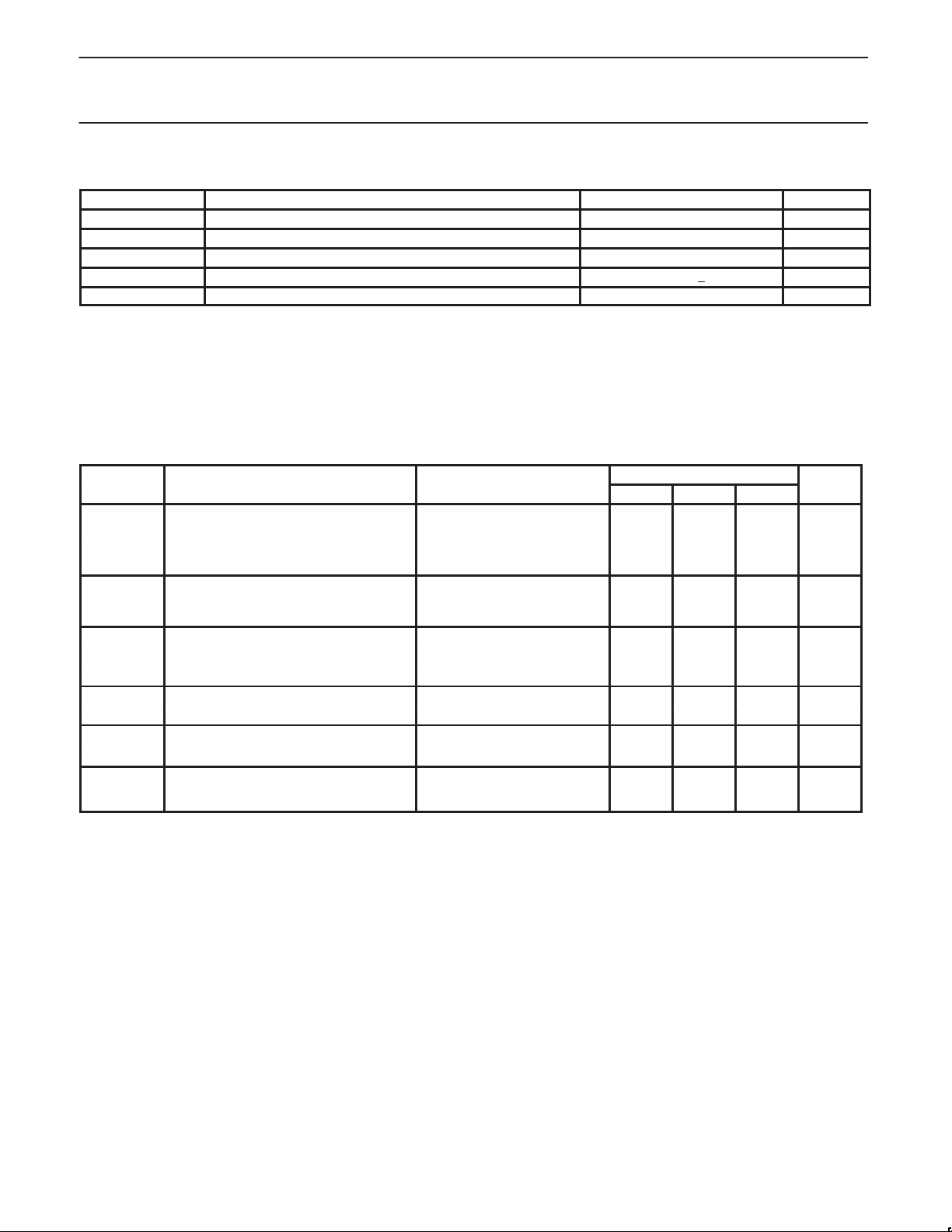

PIN CONFIGURATIONS

1

RDN

2

RxD

3

TxD

4

MPO

5

MPI

N24

6

A2

A1

A0

X1/CLK

X2

RESET

GND

5

11

Pin Symbol Pin Symbol

1

2

3

4

5

6

7

8

9

10

11

12

13

14

AND

D24

7

PACKAGES

8

9

10

11

12

4126

A28

PACKAGE

V

CC

RDN

RxD

TxD

MPO

MPI

NC

NC

A2

A1

A0

X1/CLK

X2

RESET

Figure 1. Pin Configurations

24

V

CC

23

WRN

22

D0

21

D1

20

D2

19

D3

18

D4

17

D5

16

D6

D7

15

14

CEN

13

INTRN

25

19

1812

15

GND

16

INTRN

17

CEN

18

D7

19

D6

20

D5

21

D4

22

D3

23

NC

24

D2

25

D1

26

NC

27

D0

28

WRN

SD00122

•Single interrupt output with seven maskable interrupting

conditions

•On-chip crystal oscillator

•Low power mode

•TTL compatible

•Single +5V power supply

•Commercial (0°C to +70°C) and industrial (-40°C to +85°C)

temperature versions available

•SOL, PLCC and 300 mil wide DIP packages available

1998 Sep 04 853–1078 19971

2

Philips Semiconductors Product specification

SCC2691Universal asynchronous receiver/transmitter (UART)

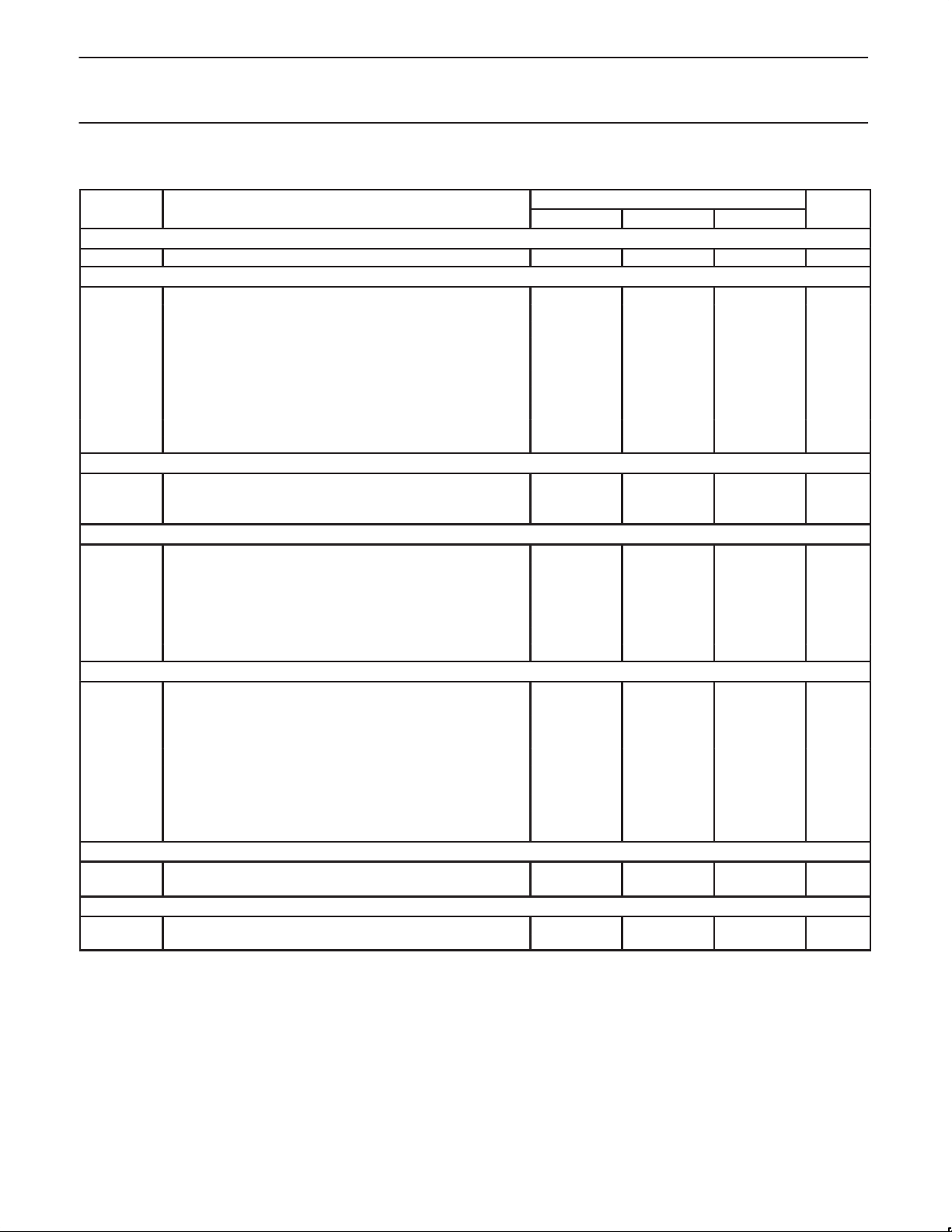

ORDERING INFORMATION

COMMERCIAL INDUSTRIAL

PACKAGES

VCC = +5V +10%,

TA = 0°C to +70°C

VCC = +5V +10%,

TA = –40°C to +85°C

24-Pin Plastic Dual In-Line Package (DIP) SCC2691AC1N24 SCC2691AE1N24 SOT222–1

28-Pin Plastic Leaded Chip Carrier (PLCC) Package SCC2691AC1A28 SCC2691AE1A28 SOT261-3

24-Pin Plastic Small Outline Large (SOL) Package SCC2691AC1D24 SOT137-1

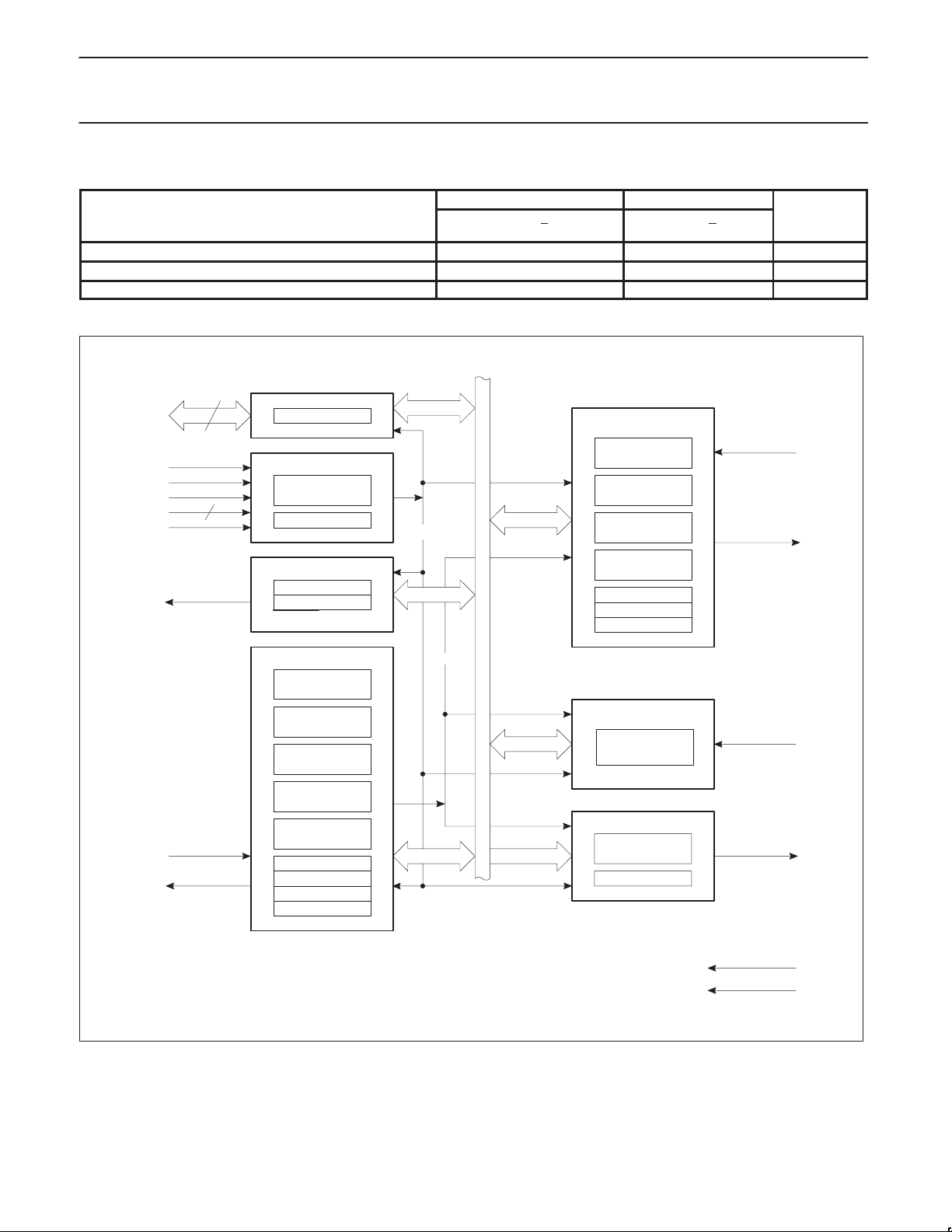

BLOCK DIAGRAM

INTERNAL DATA

BUS

8

D0–D7

RDN

WRN

CEN

A0–A2

RESET

INTRN

3

BUS BUFFER

OPERATION CONTROL

ADDRESS

DECODE

R/W CONTROL

INTERRUPT CONTROL

IMR

ISR

CONTROL

CHANNEL A

TRANSMIT

HOLDING REG

TRANSMIT

SHIFT REGISTER

RECEIVE

HOLDING REG (3)

RECEIVE

SHIFT REGISTER

MR1, 2

CR

SR

DWG #

TxD

RxD

X1/CLK

TIMING

BAUD RATE

GENERATOR

CLOCK

SELECTORS

COUNTER/

TIMER

CRYSTAL

OSCILLATOR

POWER DOWN

LOGIC

CSR

X2

ACR

CTUR

CTLR

TIMING

INPUT PIN

CHANGE OF

STATE

DETECTOR

OUTPUT PIN

FUNCTION

SELECT LOGIC

ACR

MPI

MPO

V

CC

GND

SD00123

Figure 2. Block Diagram

1998 Sep 04

3

Philips Semiconductors Product specification

MNEMONIC

TYPE

NAME AND FUNCTION

SCC2691Universal asynchronous receiver/transmitter (UART)

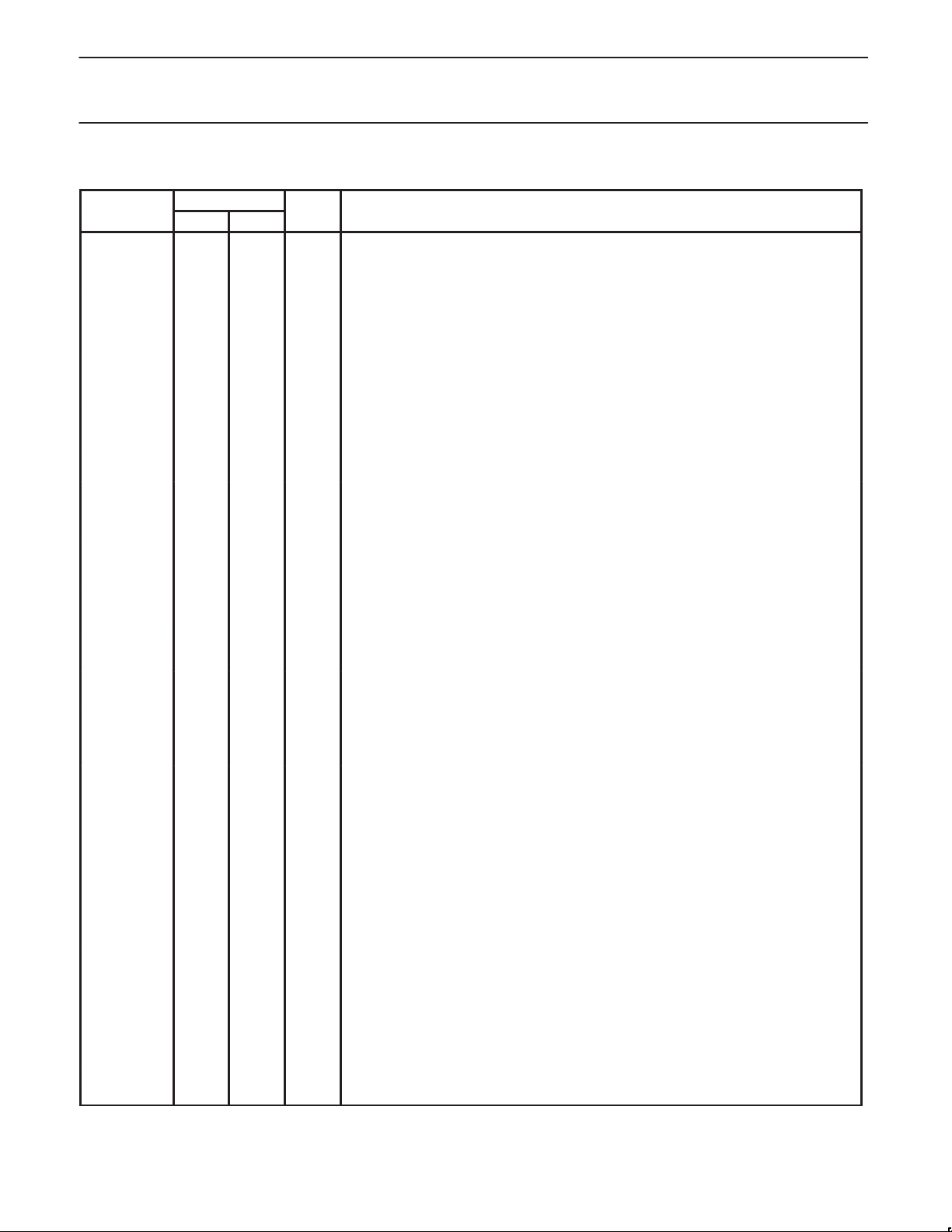

PIN DESCRIPTION

PIN NO.

DIP PLCC

D0–D7 22–15 27, 25,

CEN 14 17 I Chip Enable: Active-low input. When low, data transfers between the CPU and the UART

WRN 23 28 I Write Strobe: Active-low input. A low on this pin while CEN is low causes the contents of

RDN 1 2 I Read Strobe: Active-low input. A low on this pin while CEN is low causes the contents of

A0–A2 8–6 11–9 I Address Inputs: Active-high address inputs to select the UART registers for read/write

RESET 11 14 I Reset: Master reset. A high on this pin clears the status register (SR), the interrupt mask

INTRN 13 16 O Interrupt Request: This active-low output is asserted upon occurrence of one or more of

X1/CLK 9 12 I Crystal 1: Crystal connection or an external clock input. A crystal of a clock the appropriate

X2 10 13 I Crystal 2: Crystal connection. See Figure 7. If a crystal is not used it is best to keep this pin

RxD 2 3 I Receiver Serial Data Input: The least significant bit is received first. If external receiver

TxD 3 4 O Transmitter Serial Data Output: The least significant bit is transmitted first. This output is

MPO 4 5 O Multi-Purpose Output: One of the following functions can be selected for this output pin by

MPI 5 6 I Multi-Purpose Input: This pin can serve as an input for one of the following functions:

V

CC

GND 12 15 I Ground

24 1 I Power Supply: +5V supply input.

24,

22–18

I Data Bus: Active-high 8-bit bidirectional 3-State data bus. Bit 0 is the LSB and bit 7 is the

MSB. All data, command, and status transfers between the CPU and the UART take place

over this bus. The direction of the transfer is controlled by the WRN and RDN inputs when

the CEN input is low. When the CEN input is high, the data bus is in the 3-State condition.

are enabled on D0–D7 as controlled by the WRN, RDN and A0–A2 inputs. When CEN is

high, the UART is effectively isolated from the data bus and D0–D7 are placed in the 3-State

condition.

the data bus to be transferred to the register selected by A0–A2. The transfer occurs on the

trailing (rising) edge of the signal.

the register selected by A0–A2 to be placed on the data bus. The read cycle begins on the

leading (falling) edge of RDN.

operations.

register (IMR), and the interrupt status register (ISR), sets the mode register pointer to MR1,

and places the receiver and transmitter in the inactive state causing the TxD output to go to

the marking (high) state. Clears Test modes.

seven maskable interrupting conditions. The CPU can read the interrupt status register to

determine the interrupting condition(s). This open-drain output requires a pull-up resistor.

frequency (nominally 3.6864 MHz) must be supplied at all times. For crystal connections see

Figure 7, Clock Timing.

not connected although it is permissible to ground it.

clock is specified, this input is sampled on the rising edge of the clock.

held in the marking (high) condition when the transmitter is idle or disabled and when the

UART is operating in local loopback mode. If external transmitter is specified, the data is

shifted on the falling edge of the transmitter clock.

programming the auxiliary control register:

RTSN – Request to send active-low output. This output is asserted and negated via the

command register. By appropriate programming of the mode registers, RTSN can be programmed to be automatically reset after the character in the transmitter is completely shifted

or when the receiver FIFO and shift register are full.

C/TO – The counter/timer output.

TxC1X – The 1X clock for the transmitter.

TxC16X – The 16X clock for the transmitter.

RxC1X – The 1X clock for the receiver.

RxC16X – The 16X clock for the receiver.

TxRDY – The transmitter holding register empty signal. Active-low output. (Open drain)

RxRDY/FFULL – The receiver FIFO not empty/full signal. Active-low output. (Open drain)

GPI – General purpose input. The current state of the pin can be determined by reading the

ISR.

CTSN – Clear-to-send active-low input.

CTCLK – Counter/timer external clock input.

RTCLK – Receiver and/or transmitter external clock input. This may be a 1X or 16X clock as

programmed by CSR[3:0] or CSR[7:4].

Pin has an internal V

pull-up device supplying 1 to 4 A of current.

CC

1998 Sep 04

4

Philips Semiconductors Product specification

SYMBOL

PARAMETER

TEST CONDITIONS

UNIT

SCC2691Universal asynchronous receiver/transmitter (UART)

CC

1

PARAMETER RATING UNIT

to GND

2

3

3

Note 4 °C

–0.5 to + 7.0 V

–0.5 to V

+10% V

CC

ABSOLUTE MAXIMUM RATINGS

SYMBOL

T

V

V

P

T

A

STG

CC

S

D

Operating ambient temperature range

Storage temperature range –65 to +150 °C

Voltage from V

Voltage from any pin to ground

Power Dissipation 300 mW

NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any other condition above those indicated in the operation section of this specification is not

implied.

2. For operating at elevated temperature, the device must be derated based on +150°C maximum junction temperature.

3. This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static

charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

4. Parameters are valid over specified temperature range. See Ordering Information table for applicable operating temperature and V

range.

DC ELECTRICAL CHARACTERISTICS

1, 2, 3

CC

supply

LIMITS

Min Typ Max

V

V

V

V

I

IL

I

LL

I

OD

I

XIL

I

XIH

I

X2L

I

X2H

I

CCA

I

CCD

IL

IH

OL

OH

4

Input low voltage

Input high voltage

All except X1/CLK

X1/CLK

Output low voltage

Output high voltage

(except open drain outputs)

Input leakage current V

I

= 2.4mA

OL

IOH = –400µA

= 0 to V

IN

Data bus 3-State leakage current VO = 0.4 to V

Open-drain output leakage current VO = 0.4 to V

X1/CLK low input current V

X1/CLK high input current V

X2 low output current V

X2 high output current V

Power supply current, active

Power down current

5

= 0, X2 floated –100 –30 0 µA

IN

= VCC, X2 floated 0 30 100 µA

IN

= 0, X1/CLK = V

OUT

= VCC, X1/CLK = 0V 100 µA

OUT

0°C to +70°C

–40°C to +85°C

CC

CC

CC

CC

0.8 V

2

0.8V

CC

V

CC

0.4 V

2.4

–10 10 µA

–10 10 µA

–10 10

–100 µA

0.8

1.0

2.0

2.5

500

V

V

V

µA

mA

mA

µA

NOTES:

1. Parameters are valid over specified temperature range. See Ordering Information table for applicable operating temperature and V

range.

CC

supply

2. All voltage measurements are referenced to ground (GND). For testing, all input signals swing between 0V and 3.0V with a transition time of

20ns max. For X1/CLK, this swing is between 0.4V and 4.0V . All time measurements are referenced at input voltages of 0.8V and 2V and

output voltages of 0.8V and 2V as appropriate.

3. Typical values are at +25°C, typical supply voltages, and typical processing parameters.

4. Test condition for outputs: C

5. For power down current levels in the 1µA region see the UART application note.

= 150pF, except interrupt outputs. T est conditions for interrupt outputs: CL = 50pF, RL = 2.7kΩ to VCC.

L

1998 Sep 04

5

Philips Semiconductors Product specification

SYMBOL

PARAMETER

UNIT

SCC2691Universal asynchronous receiver/transmitter (UART)

AC ELECTRICAL CHARACTERISTICS

1, 2, 3, 4

LIMITS

Min Typ Max

Reset timing (Figure 3)

t

RES

Bus timing (Figure 4)

t

AS

t

AH

t

CS

t

CH

t

RW

t

DD

t

DF

t

DS

t

DH

t

RWD

MPI and MPO timing (Figure 5)

t

PS

t

PH

t

PD

Reset pulse width 100 ns

5

A0–A2 setup time to RDN, WRN low 10 ns

A0–A2 hold time from RDN, WRN low 100 ns

CEN setup time to RDN, WRN low 0 ns

CEN hold time from RDN, WRN high 0 ns

WRN, RDN pulse width 150 ns

Data valid after RDN low 125 ns

Data bus floating after RDN high 110 ns

Data setup time before WRN high 50 ns

Data hold time after WRN high 30 ns

Time between reads and/or writes

5

6, 7

150 ns

MPI input setup time before RDN low 30 ns

MI input hold time after RDN low 30 ns

MPO output valid after WRN high 370 ns

Interrupt timing (Figure 6)

t

IR

INTRN negated

Read RHR (RxRDY/FFULL interrupt) 370 ns

Write THR (TxRDY, TxEMT interrupt) 370 ns

Reset command (break change interrupt) 370 ns

Reset command (MPI change interrupt) 370 ns

Stop C/T command (counter interrupt) 370 ns

Write IMR (clear of interrupt mask bit) 270 ns

Clock timing (Figure 7)

t

CLK

f

CLK

t

CTC

f

CTC

t

RX

f

RX

t

TX

f

TX

9

8

8

8

X1/CLK high or low time 100 ns

X1/CLK frequency 0 4.0 MHz

Counter/timer clock high or low time 100 ns

Counter/timer clock frequency 0 4.0 MHz

RxC high or low time 220 ns

RxC frequency (16X)

RxC frequency (1X)

0

0

3.6864 2.0

1.0

MHz

MHz

TxC high or low time 220 ns

TxC frequency (16X)

TxC frequency (1X)

0

0

2.0

1.0

MHz

MHz

Transmitter timing (Figure 8)

t

TXD

t

TCS

TxD output delay from TxC external clock input on IP pin 350 ns

Output delay from TxC low at OP pin to TxD data output 0 150 ns

Receiver timing (Figure 9)

t

RXS

t

RXH

RxD data setup time before RxC high at external clock input on IP pin 100 ns

RxD data hold time after RxC high at external clock input on IP pin 100 ns

NOTES:

1. Parameters are valid over specified temp. range. See Ordering Information table for applicable operating temp. and V

2. All voltage measurements are referenced to ground (GND). For testing, all input signals swing between 0V and 3.0V with a transition time of

supply range.

CC

20ns max. For X1/CLK, this swing is between 0.4V and 4.0V . All time measurements are referenced at input voltages of 0.8V and 2V and

output voltages of 0.8V and 2V as appropriate.

3. Typical values are at +25°C, typical supply voltages, and typical processing parameters.

4. Test condition for outputs: C

5. Timing is illustrated and referenced to the WRN and RDN inputs. The device may also be operated with CEN as the ‘strobing’ input. In this

= 150pF, except interrupt outputs. T est conditions for interrupt outputs: CL = 50pF, RL = 2.7kΩ to VCC.

L

case, all timing specifications apply referenced to the falling and rising edges of CEN. CEN and RDN (also CEN and WRN) are ORed internally. As a consequence, this signal asserted last initiates the cycle and the signal negated first terminates the cycle.

6. If CEN is used as the ‘strobing’ input, this parameter defines the minimum high time between one CEN and the next. The RDN signal must

be negated for t

7. Consecutive write operations to the command register require at least three rising edges of the X1 clock between writes.

guarantee that any status register changes are valid.

RWD

8. These parameters are guaranteed by design, but are not 100% tested in production.

9. Operation to 0MHz is assured by design. Minimum test frequency is 2MHz.

1998 Sep 04

6

Philips Semiconductors Product specification

SCC2691Universal asynchronous receiver/transmitter (UART)

BLOCK DIAGRAM

As shown in the block diagram, the UART consists of: data bus buffer,

interrupt control, operation control, timing, receiver and transmitter.

Data Bus Buffer

The data bus buffer provides the interface between the external and

internal data busses. It is controlled by the operation control block to

allow read and write operations to take place between the controlling

CPU and UART.

Interrupt Control

A single interrupt output (INTRN) is provided which may be asserted

upon occurrence of any of the following internal events:

– Transmit holding register ready

– Transmit shift register empty

– Receive holding register ready or FIFO full

– Change in break received status

– Counter reached terminal count

– Change in MPI input

– Assertion of MPI input

Associated with the interrupt system are the interrupt mask register

(IMR) and the interrupt status register (ISR). The IMR can be

programmed to select only certain of the above conditions to cause

INTRN to be asserted. The ISR can be read by the CPU to

determine all currently active interrupting conditions. However, the

bits of the ISR are not masked by the IMR.

Operation Control

The operation control logic receives operation commands from the

CPU and generates appropriate signals to internal sections to

control device operation. It contains address decoding and read and

write circuits to permit communications with the microprocessor via

the data bus buffer. The functions performed by the CPU read and

write operations are shown in Table 1.

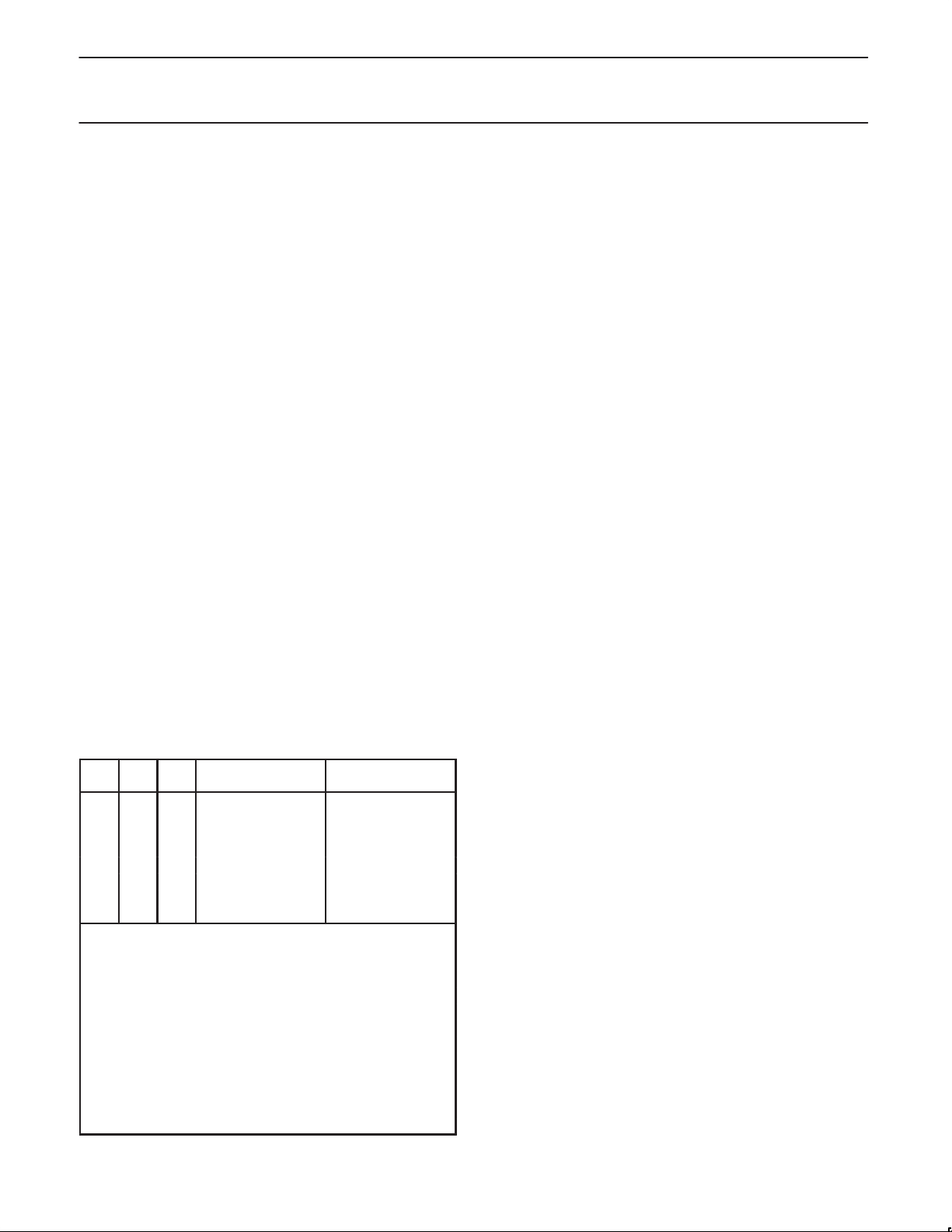

Table 1. Register Addressing

A2 A1 A0

0 0 0 MR1, MR2 MR1, MR2

0 0 1 SR CSR

0 1 0 BRG Test CR

0 1 1 RHR THR

1 0 0 1X/16X Test ACR

1 0 1 ISR IMR

1 1 0 CTU CTUR

1 1 1 CTL CTLR

NOTE;

*Reserved registers should never be read during operation since

they are reserved for internal diagnostics.

ACR = Auxiliary control register

CR = Command register

CSR = Clock select register

CTL = Counter/timer lower output register

CTLR = Counter/timer lower preset register

CTU = Counter/timer upper output register

CTUR = Counter/timer upper preset register

MR = Mode register A

SR = Status register

THR = Tx holding register

* See Table 6 for BRG Test frequencies in this data sheet, and

READ

(RDN = 0)

“Extended baud rates for SCN2681, SCN68681, SCC2691,

WRITE

(WRN = 0)

SCC2692, SCC68681 and SCC2698B”

for Data Communications, IC-19, 1994.

Mode registers 1 and 2 are accessed via an auxiliary pointer. The

pointer is set to MR1 by RESET or by issuing a reset pointer

command via the command register . Any read or write of the mode

register while the pointer is at MR1 switches the pointer to MR2. the

pointer then remains at MR2 so that subsequent accesses are to

MR2, unless the pointer is reset to MR1 as described above.

Philips Semiconductors ICs

Timing Circuits

The timing block consists of a crystal oscillator, a baud rate

generator, a programmable 16-bit counter/timer, and two clock

selectors.

The crystal oscillator operates directly from a 3.6864MHz crystal

connected across the X1/ CLK and X2 inputs with a minimum of

external components. If an external clock of the appropriate

frequency is available, it may be connected to X1/CLK. If an external

clock is used instead of a crystal, X1/CLK is driven using a

configuration similar to the one in Figure 7. In this case, the input

high-voltage must be capable of attaining the voltage specified in the

DC Electrical Characteristics. The clock serves as the basic timing

reference for the baud rate generator (BRG), the counter/timer, and

other internal circuits. A clock frequency, within the limits specified in

the electrical specifications, must be supplied if the internal BRG is

not used.

The baud rate generator operates from the oscillator or external

clock input and is capable of generating 18 commonly used data

communications baud rates ranging from 50 to 38.4K baud. Thirteen

of these are available simultaneously for use by the receiver and

transmitter. Eight are fixed, and one of two sets of five can be

selected by programming ACR[7]. The clock outputs from the BRG

are at 16X the actual baud rate. The counter/timer can be used as a

timer to produce a 16X clock for any other baud rate by counting

down the crystal clock or an external clock. The clock selectors

allow the independent selection by the receiver and transmitter of

any of these baud rates or an external timing signal.

Counter/Timer (C/T)

The C/T operation is programmed by ACR[6:4]. One of eight timing

sources can be used as the input to the C/T. The output of the C/T is

available to the clock selectors and can be programmed by

ACR[2:0} to be output on the MPO pin.

In the timer mode, the C/T generates a square wave whose period is

twice the number of clock periods loaded into the C/T upper and

lower registers. The counter ready bit in the ISR is set once each

cycle of the square wave. If the value in CTUR or CTLR is changed,

the current half-period will not be affected, but subsequent

half-periods will be affected. In this mode the C/T runs continuously

and does not recognize the stop counter command (the command

only resets the counter ready bit in the ISR). Receipt of a start C/T

command causes the counter to terminate the current timing cycle

and to begin a new cycle using the values in CTUR and CTLR.

In the counter mode, the C/T counts down the number of pulses

loaded into CTUR and CTLR. Counting begins upon receipt of a

start C/T command. Upon reaching terminal count, the counter

ready bit in the ISR is set. The counter continues counting past the

terminal count until stopped by the CPU. If MPO is programmed to

be the output of the C/T, the output remains high until terminal count

is reached, at which time it goes low. The output returns to the high

state and the counter ready bit is cleared when the counter is

stopped by a stop counter command. the CPU may change the

1998 Sep 04

7

Philips Semiconductors Product specification

SCC2691Universal asynchronous receiver/transmitter (UART)

values of CTUR and CTLR at any time, but the new count becomes

effective only on the next start counter command following a stop

counter command. If new values have not been loaded, the previous

count values are preserved and used for the next count cycle.

In the counter mode, the current value of the upper and lower eight

bits of the counter may be read by the CPU. It is recommended that

the counter be stopped when reading to prevent potential problems

which may occur if a carry from the lower eight bits to the upper

eight bits occurs between the times that both halves of the counter

are read. However, a subsequent start counter command causes

the counter to begin a new count cycle using the values in CTUR

and CTLR. See further description in CTUR/CTLR section.

Receiver and Transmitter

The UART is a full-duplex asynchronous receiver/transmitter. The

operating frequency for the receiver and transmitter can be selected

independently from the baud rate generator, the counter/timer, or

from an external input. Registers associated with the

communications channel are: the mode registers (MR1 and MR2),

the clock select register (CSR), the command register (CR), the

status register (SR), the transmit holding register (THR), and the

receive holding register (RHR).

Transmitter

The transmitter accepts parallel data from the CPU and converts it

to a serial bit stream on the TxD output pin. It automatically sends a

start bit followed by the programmed number of data bits, an

optional parity bit, and the programmed number of stop bits. The

least significant bit is sent first. Following the transmission of the

stop bits, if a new character is not available in the THR, the TxD

output remains high and the TxEMT bit in the SR will be set to 1.

Transmission resumes and the TxEMT bit is cleared when the CPU

loads a new character in the THR. In the 16X clock mode, this also

resynchronizes the internal 1X transmitter clock so that transmission

of the new character begins with minimum delay.

The transmitter can be forced to send a break (continuous low

condition) by issuing a start break command via the CR. The break

is terminated by a stop break command.

If the transmitter is disabled, it continues operating until the

character currently being transmitted and the character in the THR,

if any, are completely sent out. Characters cannot be loaded in the

THR while the transmitter is disabled.

Receiver

The receiver accepts serial data on the RxD pin, converts the serial

input to parallel format, checks for start bit, stop bit, parity bit (if any),

or break condition, and presents the assembled character to the

CPU. The receiver looks for a high-to-low (mark-to-space) transition

of the start bit on the RxD input pin. If a transition is detected, the

state of the RxD pin is sampled again each 16X clock for 7-1/2

clocks (16X clock mode) or at the next rising edge of the bit time

clock (1X clock mode). If RxD is sampled high, the start bit is invalid

and the search for a valid start bit begins again. If RxD is still low, a

valid start bit is assumed and the receiver continues to sample the

input at one bit time intervals at the theoretical center of the bit, until

the proper number of data bits and the parity bit (if any) have been

assembled, and one sop bit has been detected. The data is then

transferred to the RHR and the RxRDY bit in the SR is set to a 1. If

the character length is less than eight bits, the most significant

unused bits in the RHR are set to zero.

After the stop bit is detected, the receiver will immediately look for

the next start bit. However, if a non-zero character was received

without a stop bit (i.e. framing error) and RxD remains low for

one-half of the bit period after the stop bit was sampled, then the

receiver operates as if a new start bit transition had been detected at

that point(one-half bit time after the stop bit was sampled).

The parity error, framing error and overrun error (if any) are strobed

into the SR at the received character boundary, before the RxRDY

status bit is set.

If a break condition is detected (RxD is low for the entire character

including the stop bit), only one character consisting of all zeros will

be loaded in the FIFO and the received SR break bit is set to 1. The

RxD input must return to high for two (2) clock edges of the X1

crystal clock for the receiver to recognize the end of the break

condition and begin the search for a start bit. This will usually

require a high time of one X1 clock period or 3 X1 edges since

the clock of the controller is not synchronous to the X1 clock.

RECEIVER FIFO

The RHR consists of a first-in-first-out (FIFO) queue with a capacity

of three characters. Data is loaded from the receive shift register

into the top-most empty position of the FIFO. The RxRDY bit in the

status register (SR) is set whenever one or more characters are

available to be read, and a FFULL status bit is set if all three queue

positions are filled with data. Either of these bits can be selected to

cause an interrupt. A read of the RHR outputs the data at the top of

the FIFO. After the read cycle, the data FIFO and its associated

status bits are ‘popped’ thus emptying a FIFO position for new data.

Receiver Status Bits

In addition to the data word, three status bits (parity error, framing

error, and received break) are appended to each data character in

the FIFO. Status can be provided in two ways, as programmed by

the error mode control bit in mode register 1. In the character mode,

status is provided on a character-by-character basis: the status

applies only to the character at the top of the FIFO. In the block

mode, the status provided in the SR for these three bits is the

logical-OR of the status for all characters coming to the top of the

FIFO since the last reset error command was issued. In either

mode, reading the SR does not affect the FIFO. The FIFO is

‘popped’ only when the RHR is read. Therefore, the SR should be

read prior to reading the corresponding data character.

The receiver can control the deactivation of RTS. If programmed to

operate in this mode, the RTSN output will be negated when a valid

start bit was received and the FIFO is full. When a FIFO position

becomes available, the RTSN output will be re-asserted

automatically. This feature can be used to prevent an overrun, in

the receiver, by connecting the RTSN output to the CTSN input of

the transmitting device.

Receiver Reset and Disable

Receiver disable stops the receiver immediately – data being

assembled if the receiver shift register is lost. Data and status in the

FIFO is preserved and may be read. A re-enable of the receiver

after a disable will cause the receiver to begin assembling

characters at the next start bit detected. A receiver reset will discard

the present shift register data, reset the receiver ready bit (RxRDY),

clear the status of the byte at the top of the FIFO and re-align the

FIFO read/write pointers. This has the appearance of “clearing or

flushing” the receiver FIFO. In fact, the FIFO is NEVER cleared!

The data in the FIFO remains valid until overwritten by another

received character. Because of this, erroneous reading or extra

reads of the receiver FIFO will miss-align the FIFO pointers and

result in the reading of previously read data. A receiver reset will

re-align the pointers.

1998 Sep 04

8

Loading...

Loading...