Philips SC28C198A1A, SC28C198C1A, SC28L198A1A, SC28L198A1BE, SC28L198C1A Datasheet

Philips

Semiconductors

SC28L198

Octal UART for 3.3V and 5V supply

voltage

Product specification

Supersedes data of 1998 Nov 04

IC19 Data Handbook

1999 Jan 14

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

2

1999 Jan 14 853–2047 20654

Table of Contents

Description 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Uses 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Features 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pin Configurations

4. . . . . . . . . . . . . . . . . . . . . . . . .

Pinout 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pin Description 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Absolute Maximum Ratings 6. . . . . . . . . . . . . . . . .

Block Diagram

7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Description 7. . . . . . . . . . . . . . . . . . . . .

Conceptual Overview 7. . . . . . . . . . . . . . . . . . . . . . .

Host Interface 7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Asynchronous bus cycle 7. . . . . . . . . . . . . . . . . . . . . . . . . . .

Synchronous bus cycle 7. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timing Circuits 7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Crystal Oscillator 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sclk – System Clock 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baud Rate Generator BRG 8. . . . . . . . . . . . . . . . . . . . . . . .

BRG Counters (Used for random baud rate generation) 8

Channel Blocks 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Character Recognition 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Control 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Global Registers 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O Ports 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Detailed Descriptions 9. . . . . . . . . . . . . . . . . . . . . . .

Receiver and Transmitter

9. . . . . . . . . . . . . . . . . . .

Transmitter 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Status Bits 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmission of ”break” 10. . . . . . . . . . . . . . . . . . . . . . . . . . . .

1x and 16x modes, Transmitter 10. . . . . . . . . . . . . . . . . . . . .

Transmitter FIFO 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1x and 16x mode, Receiver 10. . . . . . . . . . . . . . . . . . . . . . . . .

Receiver Status Bits 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver FIFO 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RxFIFO Status: Status reporting modes 11. . . . . . . . . . . . . .

I/O ports 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

General Purpose Pins 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Global Registers 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Character Recognition 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Xon Xoff Characters 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Multi-drop or Wake up or 9 bit mode 12. . . . . . . . . . . . . . . . .

Character Stripping 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Arbitration and IRQN generation 12. . . . . . . . . . . . . . . .

IACKN Cycle, Update CIR 13. . . . . . . . . . . . . . . . . . . . . . . . . .

Polling 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Enabling and Activating Interrupt sources 13. . . . . . . . . . . . .

Setting Interrupt Priorities 13. . . . . . . . . . . . . . . . . . . . . . . . . .

Modes of Operation 14. . . . . . . . . . . . . . . . . . . . . . . .

Major Modes 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Minor Modes 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Watch-dog T imer Time–out Mode 15. . . . . . . . . . . . . . . . . . .

Wake Up Mode 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Xon/Xoff Operation 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

REGISTER DEFINITIONS 18. . . . . . . . . . . . . . . . . . . .

MR – Mode Registers 18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIR – Update CIR 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

General Purpose Output Pin Control 30. . . . . . . .

Register Maps 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Register Map Summary 31. . . . . . . . . . . . . . . . . . . . .

Register Map Detail 32. . . . . . . . . . . . . . . . . . . . . . . .

Reset Conditions 41. . . . . . . . . . . . . . . . . . . . . . . . . . .

Device Configuration after Hardware Reset or CRa cmd=x1F 41

Cleared registers: 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clears Modes for: 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Disables: 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Halts: 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Limitations: 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DC Electrical Specifications (5V) 42. . . . . . . . . . . .

AC Electrical Characteristic (5V)

43. . . . . . . . . . . .

DC Electrical Specifications (3.3V) 45. . . . . . . . . .

AC Electrical Characteristics (3.3V) 46. . . . . . . . . .

INDEX

52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DESCRIPTION

The Philips 28L198 Octal UART is a single chip CMOS–LSI

communications device that provides 8 full-duplex asynchronous

channels with significantly deeper 16 byte FIFOs, Automatic

in–band flow control using Xon/Xoff characters defined by the user

and address recognition in the wake up mode. Synchronous bus

interface is used for all communication between host and OCTAR T.

It is fabricated using Philips 1.0 micron CMOS technology that

combines the benefits of low cost, high density and low power

consumption.

The operating speed of each receiver and transmitter can be

selected independently from one of 22 fixed baud rates, a 16X clock

derived from one of two programmable baud rate counters or one of

three external 16X clocks (1 available at 1x clock rate). The baud

rate generator and counter can operate directly from a crystal or

from seven other external or internal clock inputs. The ability to

independently program the operating speed of the receiver and

transmitter makes the Octal UART particularly attractive for dual

speed full duplex channel applications such as clustered terminal

systems. The receivers and transmitters are buffered with FIFOs of

16 characters to minimize the potential for receiver overrun and to

reduce interrupt overhead. In addition, a handshaking capability and

in–band flow control are provided to disable a remote UART

transmitter when the receiver buffer is full or nearly so.

To minimize interrupt overhead an interrupt arbitration system is

included which reports the context of the interrupting UART via

direct access or through the modification of the interrupt vector. The

context of the interrupt is reported as channel number, type of

device interrupting ( receiver COS etc.) and, for transmitters or

receivers, the fill level of the FIFO.

The Octal UART provides a power down mode in which the

oscillator is stopped but the register contents are maintained. This

results in reduced power consumption of several orders of

magnitudes. The Octal UART is fully TTL compatible when

operating from a single +5V power supply. Operation at 3.3 volts is

maintained with CMOS interface levels.

The device also offered in a version which maintains TTL input and

output levels while operating with a 3.3 volt power supply.

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

3

Uses

Statistical Multiplexers

Data Concentrators

Packet–switching networks

Process Control

Building or Plant Control

Laboratory data gathering

ISDN front ends

Computer Networks

Point–of–Sale terminals

Automotive, cab and engine controls

Entertainment systems

MIDDI keyboard control music systems

Theater lighting control

Terminal Servers

Computer–Printer/Plotter links

FEA TURES

•Single 3.3V and 5V power supply

•Eight Philips industry standard full duplex UART channels

•Sixteen byte receiver FIFOs for each UART

•Sixteen byte transmit FIFOs for each UART

•In band flow control using programmable Xon/Xoff characters

•Flow control using CTSN RTSN hardware handshaking

•Automatic address detection in multi-drop mode

•Three byte general purpose character recognition

•Fast data bus, 30 ns data bus release time, 125 ns bus cycle time

•Programmable interrupt priorities

•Automatic identification of highest priority interrupt pending

•Global interrupt and control registers ease setup and interrupt

handling

•Vectored interrupts with programmable interrupt vector formats

– Interrupt vector modified with channel number

– Interrupt vector modified with channel number and channel type

– Interrupt vector not modified

•IACKN and DACKN signal pins

•Watch dog timer for each receiver (64 receive clock counts)

•Programmable Data Formats:

– 5 to 8 data bits plus parity

– Odd, even force or no parity

– 1, 1.5 or 2 stop bits

•Flexible baud rate selection for receivers and transmitters:

– 22 fixed rates; 50 – 230.4K baud or 100 to 460.8K baud

– Additional non–standard rates to 500K baud with internal

generators

– Two reload–counters provide additional programmable baud

rate generation

– External 1x or 16x clock inputs

– Simplified baud rate selection

•1 MHz 1x and 16x data rates full duplex all channels.

•Parity, framing and overrun error detection

•False start bit detection

•Line break detection and generation

•Programmable channel mode

– Normal(full duplex)

– Diagnostic modes

automatic echo

local loop back

emote loop back

•Four I/O ports per UART for modem controls, clocks, RTSN, I/O

etc.

– All I/O ports equipped with ”Change of State Detectors”

•Two global inputs and two global outputs for general purpose I/O

•Power down mode

•On chip crystal oscillator, 2–8 MHz

•TTL input levels. Outputs switch between full V

CC

and V

SS

•High speed CMOS technology

•84 pin PLCC

•100 pin LQFP

ORDERING CODE

VCC = 5V ±10%

PACKAGES

Industrial

1

DWG #

Industrial

-40°C to +85°C

84-Pin Plastic Leaded Chip Carrier (PLCC) SC28L198A1A SOT189-3

100-Pin Plastic Low–Profile Quad Flat Pack (LQFP) SC28L198A1BE SOT407–1

VCC = 3.3V ±10%

Industrial

1

-40°C to +85°C

84-Pin Plastic Leaded Chip Carrier (PLCC) SC28L198A1A SOT189-3

100-Pin Plastic Low–Profile Quad Flat Pack (LQFP) SC28L198A1BE SOT407–1

NOTES:

1. For availability , please contact factory.

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

4

PIN CONFIGURATIONS

11

1

75

12

32

33 53

54

74

84-PIN PLCC

TOP VIEW

84

PINOUT

Pin

Function

Pin

Function

Pin

Function

1

V

SS

29

I/O1d

57

I/O2g

2

V

CC

30

I/O2d

58

I/O1g

3

CEN

31

I/O3d

59

I/O0g

4

W_RN

32

RxDd

60

RxDg

5

A2

33

Vss

61

TxDg

6

A1

34

TxDd

62

V

SS

7

A0

35

RESETN

63

X1

8

DACKN

36

Gin0

64

X2

9

I/O0a

37

Gout0

65

TxDf

10

I/O1a

38

D0

66

I/O3f

11

RxDa

39

D1

67

I/O2f

12

RxDb

40

D2

68

I/O1f

13

I/O2a

41

D3

69

I/O0f

14

I/O3a

42

V

SS

70

TxDe

15

TxDa

43

V

CC

71

I/O3e

16

I/O0b

44

D4

72

I/O2e

17

I/O1b

45

D5

73

I/O1e

18

I/O2b

46

D6

74

RxDf

19

I/O3b

47

D7

75

RxDe

20

TxDb

48

Gin1

76

I/O0e

21

I/O0c

49

I/O3h

77

IRQN

22

Vss

50

I/O2h

78

A7

23

I/O1c

51

I/O1h

79

A6

24

I/O2c

52

I/O0h

80

A5

25

I/O3c

53

Vss

81

A4

26

TxDc

54

RxDh

82

A3

27

RxDc

55

TxDh

83

IACKN

28

I/O0d

56

I/O3g

84

SCLK

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

5

PIN CONFIGURATIONS

100

76

1

25

26 50

51

75

100–PIN LQFP

TOP VIEW

PINOUT

Pin

Function

Pin

Function

Pin

Function

БББББ

Pin

Function

1

N/C

26

V

SS

51

N/C

БББББ

76

N/C

2

RxDb

27

TxDd

52

N/C

БББББ

77

RxDe

3

I/02a

28

RESETN

53

RxDh

БББББ

78

I/O0e

4

I/03a

29

GIN0

54

TxDh

79

IRQN

5

TxDa

30

G

OUT

0

55

I/O3g

БББББ

80

A7

6

I/O0b

31

D0

56

I/O2g

БББББ

81

A6

7

I/O1b

32

D1

57

I/O1g

БББББ

82

A5

8

I/O2b

33

D2

58

I/O0g

БББББ

83

A4

9

I/O3b

34

D3

59

RxDg

БББББ

84

A3

10

TxDb

35

V

SS

60

TxDg

85

IACKN

11

I/O0c

36

V

SS

61

V

SS

БББББ

86

Sclk

12

V

SS

37

V

CC

62

V

SS

БББББ

87

V

SS

13

V

SS

38

V

CC

63

X1

БББББ

88

V

SS

14

I/O1c

39

D4

64

X2

БББББ

89

V

CC

15

I/O2c

40

D5

65

TxDf

90

V

CC

16

I/O3c

41

D6

66

I/O3f

БББББ

91

CEN

17

TxDc

42

D7

67

I/O2f

БББББ

92

W_RN

18

RxDc

43

GIN1

68

I/O1f

БББББ

93

A2

19

I/O0d

44

G

OUT

1

69

I/O0f

БББББ

94

A1

20

I/O1d

45

I/O3h

70

TxDe

95

JA0

21

I/O2d

46

I/O2h

71

I/O3e

БББББ

96

DACKN

22

I/O3d

47

I/O1h

72

I/O2e

БББББ

97

I/O0a

23

RxDd

48

I/O0h

73

I/O1e

БББББ

98

I/O1a

24

N/C

49

V

SS

74

RxDf

БББББ

99

RxDa

25

N/C

50

V

SS

75

N/C

БББББ

100

N/C

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

6

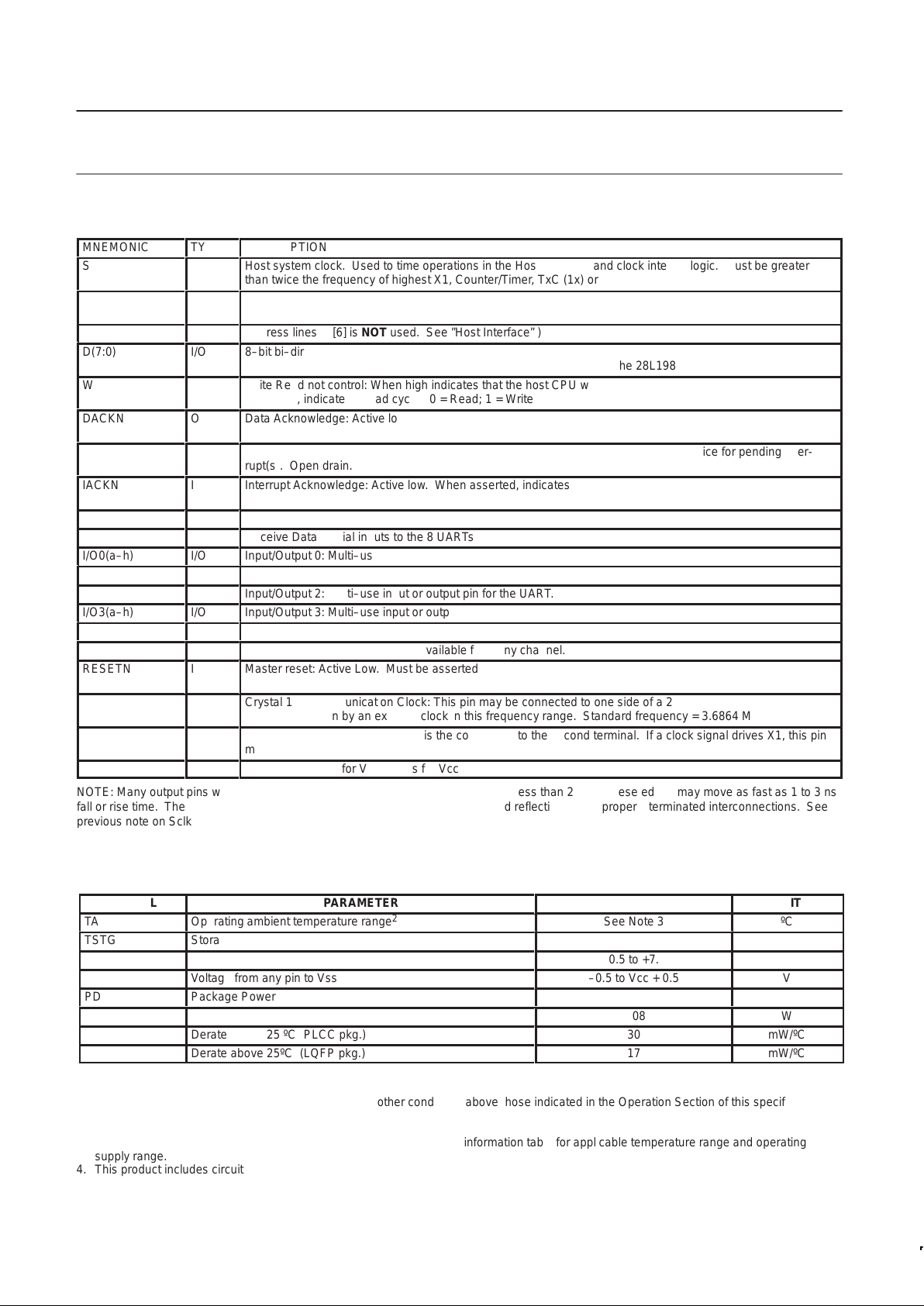

Pin Description

MNEMONIC

ÁÁÁ

TYPE

DESCRIPTION

ÁÁÁÁ

SClk

ÁÁÁ

ÁÁ

Á

I

БББББББББББББББББББББББББ

Á

Host system clock. Used to time operations in the Host Interface and clock internal logic. Must be greater

than twice the frequency of highest X1, Counter/Timer, TxC (1x) or RxC (1x) input frequency.

CEN

ÁÁÁ

I

Chip select: Active low. When asserted, allows I/O access to OCTART registers by host CPU. W_RN signal

indicates direction. (Must not be active in IACKN cycle)

A(7:0)

ÁÁÁ

I

Address lines (A[6] is NOT used. See ”Host Interface” )

D(7:0)

ÁÁÁ

I/O

8–bit bi–directional data bus. Carries command and status information between 28L198 and the host CPU.

Used to convey parallel data for serial I/O between the host CPU and the 28L198

ÁÁÁÁ

W_RN

ÁÁÁ

ÁÁ

Á

I

БББББББББББББББББББББББББ

Á

Write Read not control: When high indicates that the host CPU will write to a 28L198 register or transmit FIFO.

When low, indicates a read cycle. 0 = Read; 1 = W rite

DACKN

ÁÁÁ

O

Data Acknowledge: Active low. When asserted, it signals that the last transfer of the D lines is complete.

Open drain.

ÁÁÁÁ

IRQN

ÁÁÁ

ÁÁ

Á

O

БББББББББББББББББББББББББ

Á

Interrupt Request: Active low. When asserted, indicates that the 28L198 requires service for pending interrupt(s). Open drain.

IACKN

ÁÁÁ

I

Interrupt Acknowledge: Active low. When asserted, indicates that the host CPU has initiated an interrupt acknowledge cycle. (Do not use CEN in an IACKN cycle)

TD(a–h)

ÁÁÁ

O

Transmit Data: Serial outputs from the 8 UARTs.

RD(a–h)

ÁÁÁ

I

Receive Data: Serial inputs to the 8 UARTs

I/O0(a–h)

ÁÁÁ

I/O

Input/Output 0: Multi–use input or output pin for the UART.

I/O1(a–h)

I/O

Input/Output 1: Multi–use input or output pin for the UART.

I/O2(a–h)

ÁÁÁ

I/O

Input/Output 2: Multi–use input or output pin for the UART.

I/O3(a–h)

ÁÁÁ

I/O

Input/Output 3: Multi–use input or output pin for the UART.

GIN(1:0)

ÁÁÁ

I

Global general purpose inputs, available to any/all channels.

G

OUT

0

ÁÁÁ

O

Global general purpose outputs, available from any channel.

RESETN

ÁÁÁ

I

Master reset: Active Low. Must be asserted at power up and may be asserted at other times to reset and restart the system. See “Reset Conditions” at end of register map. Minimum width 10 SCLK.

X1/CCLK

ÁÁÁ

I

Crystal 1 or Communication Clock: This pin may be connected to one side of a 2–8 MHz crystal. It may alternatively be driven by an external clock in this frequency range. Standard frequency = 3.6864 MHz

ÁÁÁÁ

X2

ÁÁÁ

ÁÁ

Á

O

БББББББББББББББББББББББББ

Á

Crystal 2: If a crystal is used, this is the connection to the second terminal. If a clock signal drives X1, this pin

must be left unconnected.

Power Supplies

ÁÁÁ

I

8 pins total 6 pins for Vss, 2 pins for Vcc

NOTE: Many output pins will have very fast edges, especially when lightly loaded (less than 20 pf.) These edges may move as fast as 1 to 3 ns

fall or rise time. The user must be aware of the possible generation of ringing and reflections on improperly terminated interconnections. See

previous note on Sclk noise under pin assignments.

ABSOLUTE MAXIMUM RATINGS

1

SYMBOL

PARAMETER

RATING

UNIT

TA

ББББББББББББББББ

Operating ambient temperature range

2

See Note 3

ºC

TSTG

ББББББББББББББББ

Storage temperature range

–65 to +150

ºC

Vcc

ББББББББББББББББ

Voltage from VCC to Vss

4

–0.5 to +7.0

V

Vss

ББББББББББББББББ

Voltage from any pin to Vss

–0.5 to Vcc + 0.5

V

PD

ББББББББББББББББ

Package Power Dissipation (PLCC)

3.78

W

PD

Package Power Dissipation (LQFP)

2.08

W

ББББББББББББББББ

Derate above 25 ºC (PLCC pkg.)

30

mW/ºC

ББББББББББББББББ

Derate above 25ºC (LQFP pkg.)

17

mW/ºC

NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and

the functional operation of the device at these or any other conditions above those indicated in the Operation Section of this specification is

not implied.

2. For operating at elevated temperatures, the device must be derated based on +150C maximum junction temperature.

3. Parameters are valid over specified temperature range. See ordering information table for applicable temperature range and operating

supply range.

4. This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static

charge.

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

7

BLOCK DIAGRAM

Block Diagram SC28C/28L198

HOST INTERFACE

TIMING AND BAUD RATE

GENERATOR

INTERRUPT ARBITRATION

I/O PORT TIMING AND

INTERFACE

FULL DUPLEX UART CHANNEL

FULL DUPLEX UART CHANNEL

FULL DUPLEX UART CHANNEL

FULL DUPLEX UART CHANNEL

FULL DUPLEX UART CHANNEL

FULL DUPLEX UART CHANNEL

FULL DUPLEX UART CHANNEL

FULL DUPLEX UART CHANNEL

INPUT BUFFERS AND OUTPUT DRIVERS

DATA DRIVERS AND MODEM INTERFACE

SD00193

As shown in the block diagram, the Octal UART consists of: an

interrupt arbiter, host interface, timing blocks and eight UART

channel blocks. The eight channels blocks operate independently,

interacting only with the timing, host I/F and interrupt blocks.

FUNCTIONAL DESCRIPTION

The SC28L198 is composed of several functional blocks:

•Synchronous host interface block

•A timing block consisting of a common baud rate generator

making 22 industry standard baud rates and 2 16–bit counters

used for non–standard baud rate generation

•4 identical independent full duplex UART channel blocks

•Interrupt arbitration system evaluating 24 contenders

•I/O port control section and change of state detectors.

CONCEPTUAL OVERVIEW

Host Interface

The Host interface is comprised of the signal pins CEN, W/RN,

IACKN, DACKN, IRQN Sclk and provides all the control for data

transfer between the external and internal data buses of the host

and the OCTAR T. The host interface operates in a synchronous

mode with the system (Sclk) which has been designed for a nominal

operating frequency of 33 MHz. The interface operates in either of

two modes; synchronous or asynchronous to the Sclk However

the bus cycle within the OCTAR T always takes place in four Sclk

cycles after CEN is recognized. These four cycles are the C1, C2,

C3, C4 periods shown in the timing diagrams. DACKN always

occurs in the C4 time and occurs approximately 18 ns after the

rising edge of C4.

Addressing of the various functions of the OCTAR T is through the

address bus A(7:0). The 28L198 is compatible with the SC28L198

OCTAL UAR T in software and function. A[7], in a general sense, is

used to separate the data portion of the circuit from the control

portion.

Asynchronous bus cycle

The asynchronous mode requires one bus cycle of the chip select

(CEN) for each read or write to the chip. No more action will occur

on the bus after the C4 time until CEN is returned high.

Synchronous bus cycle

In the synchronous mode a read or write will be done every four

cycles of the Sclk. CEN does not require cycling but must remain

low to keep the synchronous accesses active. This provides a burst

mode of access to the chip.

In both cases each read or write operation(s) will be completed in

four (4) Sclk cycles. The difference in the two modes is only that the

asynchronous mode will not begin another bus cycle if the CEN

remains active after the four internal Sclk have completed. Internally

the asynchronous cycle will terminate after the four periods of Sclk

regardless of how long CEN is held active

In all cases the internal action will terminate at the withdrawal of

CEN. Synchronous CEN cycles shorter than multiples of four Sclk

cycles minus 1 Sclk and asynchronous CEN cycles shorter than four

Sclk cycles may cause short read or write cycles and produce

corrupted data transfers.

Timing Circuits

The timing block consists of a crystal oscillator, a fixed baud rate

generator (BRG), a pair of programmable 16 bit register based

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

8

counters. A buffer for the System Clock generates internal timing for

processes not directly concerned with serial data flow.

Crystal Oscillator

The crystal oscillator operates directly from a crystal, tuned between

1.0 and 8.0 MHz, connected across the X1/CCLK and X2 inputs with

a minimum of external components. BRG values listed for the clock

select registers correspond to a 3.6864 MHz crystal frequency. Use

of a 7.3728 MHz crystal will double the Communication Clock

frequencies.

An external clock in the 100 KHz to 10 MHz frequency range may

be connected to X1/CCLK. If an external clock is used instead of a

crystal, X1/CCLK must be driven and X2 left floating. The X1 clock

serves as the basic timing reference for the baud rate generator

(BRG) and is available to the BRG timers . The X1 oscillator input

may be left unused if the internal BRG is not used and the X1 signal

is not selected for any counter input.

Sclk – System Clock

A clock frequency, within the limits specified in the electrical

specifications, must be supplied for the system clock Sclk. To

ensure the proper operation of internal controllers, the Sclk

frequency provided, must be strictly greater than twice the frequency

of X1 crystal clock, or any external 1x data clock input. The system

clock serves as the basic timing reference for the host interface and

other internal circuits.

Baud Rate Generator BRG

The baud rate generator operates from the oscillator or external

X1/CCLK clock input and is capable of generating 22 commonly

used data communications baud rates ranging from 50 to 230.4K

baud. These common rates may be doubled (up to 460.8 and 500K

baud) when faster clocks are used on the X1/X2 clock inputs. (See

Receiver and Transmitter Clock Select Register descriptions.) All of

these are available simultaneously for use by any receiver or

transmitter. The clock outputs from the BRG are at 16X the actual

baud rate.

BRG Counters (Used for random baud rate generation)

The two BRG Timers are programmable 16 bit dividers that are used

for generating miscellaneous clocks. These clocks may be used by

any or all of the receivers and transmitters in the Octart or output on

the general purpose output pin GPO.

Each timer unit has eight different clock sources available to it as

described in the BRG Timer Control Register. (BRGTCR). Note

that the timer run and stop controls are also contained in this

register. The BRG Timers generate a symmetrical square wave

whose half period

is equal in time to the division of the selected

BRG Timer clock source by the number loaded to the BRG Timer

Reload Registers ( BRGTRU and BRGTRL). Thus, the output

frequency will be the clock source frequency divided by twice the

value loaded to the BRGTRU and BRGTRL registers. This is the

result of counting down once for the high portion of the output wave

and once for the low portion.

Whenever the these timers are selected via the receiver or

transmitter Clock Select register their output will be configured as a

16x clock for the respective receiver or transmitter. Therefore one

needs to program the timers to generate a clock 16 times faster than

the data rate. The formula for calculating ’n’, the number loaded to

the BRGTRU and BRGTRL registers, is shown below.

n

BRG Timer Input frequency

2 16 desired baud rate

–1

Note: ’n’ may assume values of 0 and 1. In previous Philips data

communications controllers these values were not allowed.

The BRG timer input frequency is controlled by the BRG Timer

control register (BRGTCR)

The frequency generated from the above formula will be at a rate 16

times faster than the desired baud rate. The transmitter and

receiver state machines include divide by 16 circuits which provide

the final frequency and provide various timing edges used in the

qualifying the serial data bit stream. Often this division will result in

a non–integer value; 26.3 for example. One may only program

integer numbers to a digital divider . There for 26 would be chosen.

If 26.7 was the result of the division then 27 would be chosen. This

gives a baud rate error of 0.3/26.3 or 0.3/26.7. which yields a

percentage error of 1.14% or 1.12% respectively; well within the

ability of the asynchronous mode of operation.

One should be cautious about the assumed benign effects of small

errors since the other receiver or transmitter with which one is

communicating may also have a small error in the precise baud rate.

In a ”clean” communications environment using one start bit, eight

data bits and one stop bit the total difference allowed between the

transmitter and receiver frequency is approximately 4.6%. Less

than eight data bits will increase this percentage.

Channel Blocks

There are eight channel blocks, each containing an I/O port control,

a data format control, and a single full duplex UART channel

consisting of a receiver and a transmitter with their associated 16

byte FIFOs. Each block has its own status register, interrupt status

and interrupt mask registers and their interface to the interrupt

arbitration system.

A highly programmable character recognition system is also

included in each block. This system is used for the Xon/Xoff flow

control and the multi-drop (”9 bit mode”) address character

recognition. It may also be used for general purpose character

recognition.

Four I/O pins are provided for each channel. These pins are

configured individually to be inputs or outputs. As inputs they may

be used to bring external data to the bus, as clocks for internal

functions or external control signals. Each I/O pin has a ”Change of

State” detector. The change detectors are used to signal a change

in the signal level at the pin (Either 0 to 1 or 1 to 0). The level

change on these pins must be stable for 25 to 50 Us (two edges of

the 38.4 KHz baud rate clock) before the detectors will signal a valid

change. These are typically used for interface signals from modems

to the OCTAR T and from there to the host. See the description of

the ”UART channel” under detailed descriptions below.

Character Recognition

Character recognition is specific to each of the eight UARTs. Three

programmable characters are provided for the character recognition

for each channel. The three are general purpose in nature and may

be set to only cause an interrupt or to initiate some rather complex

operations specific to ”Multi-drop” address recognition or in–band

Xon/Xoff flow control.

Character recognition is accomplished via CAM memory. The

Content Addressable Memory continually examines the incoming

data stream. Upon the recognition of a control character appropriate

bits are set in the Xon/Xoff Interrupt Status Register (XISR) and

Interrupt Status Register (ISR). The setting of these bit(s) will

initiate any of the automatic sequences or and/or an interrupt that

may have enabled via the MR0 register.

The characters of the recognition system are not controlled by the

software or hardware reset. They do not have a pre-defined “reset

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

9

value”. They may, however, be loaded by a “Gang White” or “Gang

Load” command as described in the “Xon Xoff Characters”

paragraph.

Note: Character recognition is further described in the

Minor Modes

of Operation.

Interrupt Control

The interrupt system determines when an interrupt should be

asserted thorough an arbitration (or bidding) system. This

arbitration is exercised over the several systems within the OCTAR T

that may generate an interrupt. These will be referred to as

”interrupt sources”. There are 64 in all. In general the arbitration is

based on the fill level of the receiver FIFO or the empty level of the

transmitter FIFO. The FIFO levels are encoded into a four bit

number which is concatenated to the channel number and source

identification code. All of this is compared (via the bidding or

arbitration process) to a user defined ”threshold”. When ever a

source exceeds the numerical value of the threshold the interrupt

will be generated.

At the time of interrupt acknowledge (IACKN) the source which has

the highest bid (not necessarily the source that caused the interrupt

to be generated) will be captured in a ”Current Interrupt Register”

(CIR). This register will contain the complete definition of the

interrupting source: channel, type of interrupt (receiver, transmitter,

change of state, etc.), and FIFO fill level. The value of the bits in the

CIR are used to drive the interrupt vector and global registers such

that controlling processor may be steered directly to the proper

service routine. A single read operation to the CIR provides all the

information needed to qualify and quantify the most common

interrupt sources.

The interrupt sources for each channel are listed below.

•Transmit FIFO empty level for each channel

•Receive FIFO Fill level for each channel

•Change in break received status for each channel

•Receiver with error for each channel

•Change of state on channel input pins

•Receiver Watch-dog Time out Event

•Xon/Xoff character recognition

•Address character recognition

Associated with the interrupt system are the interrupt mask register

(IMR) and the interrupt status register (ISR) resident in each UART.

Programming of the IMR selects which of the above sources may

enter the arbitration process. Only the bidders in the ISR whose

associated bit in the IMR is set to one (1) will be permitted to enter

the arbitration process. The ISR can be read by the host CPU to

determine all currently active interrupting conditions. For

convenience the bits of the ISR may be masked by the bits of the

IMR. Whether the ISR is read unmasked or masked is controlled by

the setting of bit 6 in MR1.

Global Registers

The ”Global Registers”, 19 in all, are driven by the interrupt system.

These are not real hardware devices. They are defined by the

content of the CIR (Current Interrupt Register) as a result of an

interrupt arbitration. In other words they are indirect registers

contained in the Current Interrupt Register (CIR) which the CIR uses

to point to the source and context of the OCTAR T sub circuit

presently causing an interrupt. The principle purpose of these

”registers” is improving the efficiency of the interrupt service.

The global registers and the CIR update procedure are further

described in the

Interrupt Arbitration

system

I/O Ports

Each of the eight UART blocks contains an I/O section of four ports.

These ports function as a general purpose post section which

services the particular UART they are associated with. External

clocks are input and internal clocks are output through these ports.

Each of the four pins has a change of state detector which will signal

a change (0 to 1 or 1 to 0) at the pin. The change of state detectors

are individually enabled and may be set to cause and interrupt.

These pins will normally be used for flow control hand–shaking and

the interface to a modem. Their control is further described in

I/O

Ports

section and the I/OPCR register.

DET AILED DESCRIPTIONS

RECEIVER AND TRANSMITTER

The Octal UART has eight full-duplex asynchronous

receiver/transmitters. The operating frequency for the receiver and

transmitter can be selected independently from the baud rate

generator, the counter , or from an external input. Registers that are

central to basic full-duplex operation are the mode registers (MR0,

MR1 and MR2), the clock select registers (RxCSR and TxCSR), the

command register (CR), the status register (SR), the transmit

holding register (TxFIFO), and the receive holding register

(RxFIFO).

Transmitter

The transmitter accepts parallel data from the CPU and converts it

to a serial bit stream on the TxD output pin. It automatically sends a

start bit followed by the programmed number of data bits, an

optional parity bit, and the programmed number of stop bits. The

least significant bit is sent first. Each character is always ”framed”

by a single start bit and a stop bit that is 9/16 bit time or longer. If a

new character is not available in the TxFIFO, the TxD output

remains high, the ”marking” position, and the TxEMT bit in the SR is

set to 1.

Transmitter Status Bits

The SR (Status Register, one per UART) contains two bits that show

the condition of the transmitter FIFO. These bits are TxRDY and

TxEMT. TxRDY means the TxFIFO has space available for one or

more bytes; TxEMT means The TxFIFO is completely empty and

the last stop bit has been completed. TxEMT can not be active

without TxRDY also being active. These two bits will go active upon

initial enabling of the transmitter. They will extinguish on the disable

or reset of the transmitter.

Transmission resumes and the TxEMT bit is cleared when the CPU

loads at least one new character into the TxFIFO. The TxRDY will

not extinguish until the TxFIFO is completely full. The TxRDY bit will

always be active when the transmitter is enabled and there is at

lease one open position in the TxFIFO.

The transmitter is disabled by reset or by a bit in the command

register (CR). The transmitter must be explicitly enabled via the CR

before transmission can begin. Note that characters cannot be

loaded into the TxFIFO while the transmitter is disabled, hence it is

necessary to enable the transmitter and then load the TxFIFO. It is

not possible to load the TxFIFO and then enable the transmission.

Note the difference between transmitter disable and transmitter

reset. The transmitter may by reset by a hardware or software. The

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

10

software reset is issued through command 3x of the Command

register (CR). The disable is done by setting the transmitter disable

bit also in the command register. If the transmitter is disabled, it

continues operating until the character currently being transmitted, if

any, is completely sent, including the stop bit. When reset the

transmitter stops immediately, drives the transmitter serial data out

put to a high level and discards any data in the TxFIFO.

Transmission of ”break”s

Transmission of a break character is often needed as a

synchronizing condition in a data stream. The ”break” is defined as

a start bit followed by all zero data bits by a zero parity bit (if parity is

enabled) and a zero in the stop bit position. The forgoing is the

minimum time to define a break. The transmitter can be forced to

send a break (continuous low condition) by issuing a start break

command via the CR. This command does not have any timing

associated with it. Once issued the TxD output will be driven low

(the spacing condition) and remain there until the host issues a

command to ”stop break” via the CR or the transmitter is issued a

software or hardware reset. In normal operation the break is usually

much longer than one character time.

1x and 16x modes, Transmitter

The transmitter clocking has two modes: 16x and 1x. Data is

always sent at the 1x rate. However the logic of the transmitter may

be operated with a clock that is 16 times faster than the data rate or

at the same rate as the data i.e. 1x. All clocks selected internally

for the transmitter (and the receiver) will be 16x clocks. Only when

an external clock is selected may the transmitter logic and state

machine operate in the 1x mode. The 1x or 16x clocking makes

little difference in transmitter operation. (this is not true in the

receiver) In the 16X clock mode the transmitter will recognize a byte

in the TxFIFO within 1/16 to 2/16 bit time and thus begin

transmission of the start bit; in the 1x mode this delay may be up to

2 bit times.

Transmitter FIFO

The transmitter buffer memory is a 16 byte by 8 bit ripple FIFO. The

host writes characters to this buffer. This buffer accepts data only

when the transmitter is enabled. The transmitter state machine

reads them out in the order they were received and presents them to

the transmitter shift register for serialization. The transmitter adds

the required start, parity and stop bits as required the MR2 register

programming. The start bit (always one bit time in length) is sent

first followed by the least significant bit (LSB) to the most significant

bit (MSB) of the character, the parity bit (if used) and the required

stop bit(s).

Logic associated with the FIFO encodes the number of empty

positions available in a four bit value. This value is concatenated

with the channel number and type interrupt type identifier and

presented to the interrupt arbitration system. The encoding of the

”positions empty” value is always 1 less than the number of

available positions. Thus, an empty TxFIFO will bid with the value

or 15; when full it will not bid at all; one position empty bids with the

value 0. A full FIFO will not bid since a character written to it will be

lost

Normally a TxFIFO will present a bid to the arbitration system when

ever it has one or more empty positions. The MR0[5:4] allow the

user to modify this characteristic so that bidding will not start until

one of four levels (empty, 3/4 empty, 1/2 empty, not full) have been

reached. As will be shown later this feature may be used to make

slight improvements in the interrupt service efficiency . A similar

system exists in the receiver.

Receiver

The receiver accepts serial data on the RxD pin, converts the serial

input to parallel format, checks for start bit, stop bit, parity bit (if

any),framing error or break condition, and presents the assembled

character and its status condition to the CPU via the RxFIFO. Three

status bits are FIFOed with each character received. The RxFIFO is

really 11 bits wide; eight data and 3 status. Unused FIFO bits for

character lengths less than 8 bits are set to zero. It is important to

note that receiver logic considers the entire message to be

contained within the start bit to the stop bit. It is not aware that a

message may contain many characters. The receiver returns to its

idle mode at the end of each stop bit! As described below it

immediately begins to search for another start bit which is normally,

of course, immediately forth coming.

1x and 16x mode, Receiver

The receiver operates in one of two modes; 1x and 16x. Of the two,

the 16x is more robust and the preferred mode. Although the 1x

mode may allow a faster data rate is does not provide for the

alignment of the receiver 1x data clock to that of the transmitter.

This strongly implies that the 1x clock of the remote transmitter is

available to the receiver; the two devices are physically close to

each other.

The 16x mode operates the receiver logic at a rate 16 times faster

than the 1x data rate. This allows for validation of the start bit,

validation of level changes at the receiver serial data input (RxD),

and a stop bit length as short as 9/16 bit time. Of most importance

in the 16x mode is the ability of the receiver logic to align the phase

of the receiver 1x data clock to that of the transmitter with an

accuracy of less than 1/16 bit time.

When the receiver is enabled ( via the CR register) it begins looking

for a high to low (mark to space) transition on the RxD input pin. If a

transition is detected, an internal counter running at 16 times the

data rate is reset to zero. If the RxD remains low and is still low

when the counter reaches a count of 7 the receiver will consider this

a valid start bit and begin assembling the character. If the RxD input

returns to a high state the receiver will reject the previous high to low

(mark to space) transition on the RxD input pin. This action is the

”validation” of the start bit and also establishes the phase of the

receiver 1x clock to that of the transmitter The counter operating at

16x the data rate is the generator for the 1x data rate clock. With

the phase of the receiver 1x clock aligned to the falling of the start

bit (and thus aligned to the transmitter clock) AND with a valid start

bit having been verified the receiver will continue receiving bits by

sampling the RxD input on the rising edge of the 1x clock that is

being generated by the above mentioned counter running 16 times

the data rate. Since the falling edge of the 1x clock was aligned to

falling edge of the start bit then the rising of the clock will be in the

”center” of the bit cell.

This action will continue until a full character has been assembled.

Parity , framing, and stop bit , and break status is then assembled

and the character and its status bits are loaded to the RxFIFO At

this point the receiver has finished its task for that character and will

immediately begin the search for another start bit.

Receiver Status Bits

There are five (5) status bits that are evaluated with each byte (or

character) received: received break, framing error, parity error,

overrun error, and change of break. The first three are appended to

each byte and stored in the RxFIFO. The last two are not

necessarily related to the a byte being received or a byte that is in

the RxFIFO. They are however developed by the receiver state

machine

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

11

. The ”received break” will always be associated with a zero byte in

the RxFIFO. It means that zero character was a break character

and not a zero data byte. The reception of a break condition will

always set the ”change of break” (see below) status bit in the

Interrupt Status Register(ISR).

A framing error occurs when a non zero character was seen and

that character has a zero in the stop bit position.

The parity error indicates that the receiver generated parity was not

the same as that sent by the transmitter.

The overrun error occurs when the RxFIFO is full, the receiver shift

register is full and another start bit is detected. At this moment the

receiver has 17 valid characters and the start bit of the 18th has

been seen. At this point the host has approximately 7/16 bit time to

read a byte from the RxFIFO or the overrun condition will be set and

the 18th character will overrun the 17th and the 19th the 18th and so

on until an open position in the RxFIFO is seen. The meaning of the

overrun is that data has been lost. Data in the RxFIFO remains

valid. The receiver will begin placing characters in the RxFIFO as

soon as a position becomes vacant.

Note: Precaution must be taken when reading an overrun FIFO.

There will be 16 valid characters. Data will begin loading as soon as

the first character is read. The 17

th.

character will have been

received as valid but it will not be known how many characters were

lost between the two characters of the 16

th.

and 17

th.

reads of the

RxFIFO

The ”Change of break” means that either a break has been detected

or that the break condition has been cleared. This bit is available in

the ISR. The beginning of a break will be signaled by the break

change bit being set in the ISR AND the received break bit being set

in the SR. At the termination of the break condition only the change

of break in the ISR will be set. After the break condition is detected

the termination of the break will only be recognized when the RxD

input has returned to the high state for two successive edges of the

1x clock; 1/2 to 1 bit time.

The receiver is disabled by reset or via CR commands. A disabled

receiver will not interrupt the host CPU under any circumstance in

the normal mode of operation. If the receiver is in the multi-drop or

special mode, it will be partially enabled and thus may cause an

interrupt. Refer to section on Wake–Up and minor modes and the

register description for MR1 for more information.

Receiver FIFO

The receiver buffer memory is a 16 byte ripple FIFO with three

status bits appended to each data byte. (The FIFO is then 16 11 bit

”words”). The receiver state machine gathers the bits from the

receiver shift register and the status bits from the receiver logic and

writes the assembled byte and status bits to the RxFIFO. Logic

associated with the FIFO encodes the number of filled positions for

presentation to the interrupt arbitration system. The encoding is

always 1 less than the number of filled positions. Thus, a full

RxFIFO will bid with the value or 15; when empty it will not bit at all;

one position occupied bids with the value 0. An empty FIFO will not

bid since no character is available. Normally RxFIFO will present a

bid to the arbitration system when ever it has one or more filled

positions. The MR2[3:2 bits allow the user to modify this

characteristic so that bidding will not start until one of four levels

(one or more filled, 1/2 filled, 3/4 filled, full) have been reached. As

will be shown later this feature may be used to make slight

improvements in the interrupt service efficiency . A similar system

exists in the transmitter.

RxFIFO Status: Status reporting modes

The description below applies to the upper three bits in the ”Status

Register” These three bits are not ”in the status register”; They are

part of the RxFIFO. The three status bits at the top of the RxFIFO

are presented as the upper three bits of the status register included

in each UART.

The error status of a character , as reported by a read of the SR

(status register upper three bits) can be provided in two ways, as

programmed by the error mode control bit in the mode register:

”Character mode ” or the ”Block Mode”. The block mode may be

further modified (via a CR command) to set the status bits as the

characters enter the FIFO or as they are read from the FIFO.

In the ’character’ mode, status is provided on a character by

character basis as the characters are read from the RxFIFO: the

”status” applies only to the character at the top of the RxFIFO – The

next character to be read

In the ’block’ mode, the status provided in the SR for these three bits

is the logical OR of the status for all characters coming to the top of

the RxFIFO, since the last reset error command was issued. In this

mode each of the status bits stored in the RxFIFO are passed

through a latch as they are sequentially read. If any of the

characters has an error bit set then that latch will set and remain set

until reset with an ”Reset Error” command from the command

register or a receiver reset. The purpose of this mode is indicating

an error in the data block as opposed to an error in a character

The latch used in the block mode to indicate ”problem data” is

usually set as the characters are read out of the RxFIFO. Via a

command in the CR the latch may be configured to set the latch as

the characters are pushed (loaded to) the RxFIFO. This gives the

advantage of indicating ”problem data” 16 characters earlier .

In either mode, reading the SR does not affect the RxFIFO. The

RxFIFO is ’popped’ only when the RxFIFO is read. Therefore, the

SR should be read prior to reading the corresponding data

character.

If the RxFIFO is full when a new character is received, that

character is held in the receive shift register until a RxFIFO position

is available. At this time there are 17 valid characters in the

RxFIFO. If an additional character is received while this state exists,

the contents of the RxFIFO are not affected: the character

previously in the shift register is lost and the overrun error status bit,

SR[4], will be set upon receipt of the start bit of the new

(overrunning) character.

I/O ports

Each of the eight UARTs includes four I/O ports equipped with

”change of state” detectors. The pins are individually programmable

for an input only function or one of three output functions. These

functions are controlled by the ”I/O Port Configuration Register

(I/OPCR)) They will normally be used for the RTSN–CTSN, DTR

hardware signals, RxD or TxD input or output clocks or switch inputs

as well as data out put from the I/OPIOR register.

It is important to note that the input circuits are always active. That

is the signal on a port, whether it is derived from an internal or

external source is always available to the internal circuits associated

with an input on that port.

The ”Change of State” (COS) detectors are sensitive to both a 1 to 0

or a 0 to 1 transition. The detectors are controlled by the internal

38.4 KHz baud rate and will signal a change when a transition has

been stable for two rising edges of this clock. Thus a level on the

I/O ports must be stable for 26 s to 52 s. Defining a port as an

output will disable the COS detector at that port. The condition of

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

12

the four I/O pins and their COS detectors is available at any time in

the IPR (Input Port Register)

The control of data and COS enable for these ports is through the

I/OPIOR register. This is a read/write register and gives individual

control to the enabling of the change of state detectors and also to

the level driven by I/O pins when programmed to drive the logic level

written to the four lower bits of the I/OPIOR. A read of this register

will indicate the data on the pin at the time of the read and the state

of the enabled COS detectors.

General Purpose Pins

In addition to the I/O ports for each UART four other ports are

provided which service the entire chip. Two are dedicated as inputs

and one as an output. The G

IN

1 and GIN0 are the input pins; G

OUT

0

the output. These ports are multiplexed to nearly every functional

unit in the chip. See the registers which describe the multitude of

connections available for these pins. The G

OUT

0 pin is highly

multiplexed output and is controlled by four (4) registers: GPOSR,

GPOR, GPOC and GPOD. The GIN0 and GIN1 pins are available to

the receivers and transmitters, BRG counters and the G

OUT

0 pin.

Global Registers

The ”Global Registers”, 19 in all, are driven by the interrupt system.

These are not real hardware devices. They are defined by the

content of the CIR (Current Interrupt Register) as a result of an

interrupt arbitration. In other words they are indirect registers

pointed to by the content of the CIR. The list of global register

follows:

GIBCR The byte count of the interrupting FIFO

GICR Channel number of the interrupting channel

GITR Type identification of interrupting channel

GRxFIFO Pointer to the interrupting receiver FIFO

GTxFIFO Pointer to the interrupting transmitter FIFO

A read of the GRxFIFO will give the content of the RxFIFO that

presently has the highest bid value. The purpose of this system is

to enhance the efficiency of the interrupt system. The global

registers and the CIR update procedure are further described in the

Interrupt Arbitration

system

Character Recognition

The character recognition circuits are basically designed to provide

general purpose character recognition. Additional control logic has

been added to allow for Xon/Xoff flow control and for recognition of

the address character in the multi-drop or ”wake–up” mode. This

logic also allows for the generation of an interrupts in either the

general purpose recognition mode or the specific conditions

mentioned above.

Xon Xoff Characters

The programming of these characters is usually done individually.

However a method has been provided to write to all of registers in

one operation. There are ”Gang Load” and a ”Gang Write”

commands provided in the channel A Command Register. When

these commands are executed all registers are programmed with

the same characters. The ”write” command loads a used defined

character; the ’load” command loads the standard Xon/Xoff

characters. Xon is x’11; Xoff x’13’. Any enabling of the Xon/Xof f

functions will use the contents of the Xon and Xoff character

registers as the basis on which recognition is predicated.

Multi-drop or Wake up or 9 bit mode

This mode is used to address a particular UART among a group

connected to the same serial data source. Normally it is

accomplished by redefining the meaning of the parity bit such that it

indicates a character as address or data. While this method is fully

supported in the SC28L198 it also supports recognition of the

character itself. Upon recognition of its address the receiver will be

enabled and data pushed onto the RxFIFO.

Further the Address recognition has the ability, if so programmed, to

disable (not reset) the receiver when an address is seen that is not

recognized as its own. The particular features of ”Auto Wake and

Auto Doze” are described in the detail descriptions below.

Note: Care should be taken in the programming of the character

recognition registers. Programming x’00, for example, may result in

a break condition being recognized as a control character. This will

be further complicated when binary data is being processed.

Character Stripping

The MR0 register provides for stripping the characters used for

character recognition. Recall that the character recognition may be

conditioned to control several aspects of the communication.

However this system is first a character recognition system. The

status of the various states of this system are reported in the XISR

and ISR registers. The character stripping of this system allows for

the removal of the specified control characters from the data stream:

two for the Xon /Xoff and one for the wake up. Via control in the

MR0 register these characters may be discarded (stripped) from the

data stream when the recognition system “sees” them or they may

be sent on the RxFIFO. Whether they are stripped or not the

recognition will process them according to the action requested: flow

control, wake up, interrupt generation, etc. Care should be

exercised in programming the stripping option if noisy environments

are encountered. If a normal character was corrupted to an Xoff

character turned off the transmitter and it was then stripped, then the

stripping action could make it difficult to determine the cause of

transmitter stopping.

Interrupt Arbitration and IRQN generation

Interrupt arbitration is the process used to determine that an

interrupt request should be presented to the host. The arbitration is

carried out between the ”Interrupt Threshold” and the ”sources”

whose interrupt bidding is enabled by the IMR. The interrupt

threshold is part of the ICR (Interrupt Control Register) and is a

value programmed by the user. The ”sources” present a value to

the interrupt arbiter. That value is derived from four fields: the

channel number, type of interrupt source, FIFO fill level, and

programmable value. . Only when one or more of these values

exceeds the threshold value in the interrupt control register will the

interrupt request (IRQN) be asserted.

Following assertion of the IRQN the host will either assert

IACKN(Interrupt Acknowledge) or will use the command to ”Update

the CIR”. At the time either action is taken the CIR will capture the

value of the source that is prevailing in the arbitration process. (Call

this value the winning bid)

The value in the CIR is the central quantity that results from the

arbitration. It contains the identity of the interrupting channel, the

type of interrupt in that channel (RxD, TxD, COS etc.) the fill levels

of the RxD or TxD FIFOs and , in the case of an RxD interrupt an

indicator of error data or good data. It also drives the Global

Registers associated with the interrupt. Most importantly it drives

the modification of the Interrupt Vector.

The arbitration process is driven by the Sclk. It scans the 10 bits of

the arbitration bus at the Sclk rate developing a value for the CIR

every 22 Sclk cycles. New arbitration values presented to the

arbitration block during an arbitration cycle will be evaluated in the

next arbitration cycle.

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

13

For sources other than receiver and transmitters the user may set

the high order bits of an interrupt source’s bid value, thus tailoring

the relative priority of the interrupt sources. The priority of the

receivers and transmitters is controlled by the fill level of their

respective FIFOs. The more filled spaces in the RxFIFO the higher

the bid value; the more empty spaces in the TxFIFO the higher its

priority. Channels whose programmable high order bits are set will

be given interrupt priority higher than those with zeros in their high

order bits , thus allowing increased flexibility. The transmitter and

receiver bid values contain the character counts of the associated

FIFOs as high order bits in the bid value. Thus, as a receiver’s

RxFIFO fills, it bids with a progressively higher priority for interrupt

service. Similarly, as empty space in a transmitter’s TxFIFO

increases, its interrupt arbitration priority increases.

IACKN Cycle, Update CIR

When the host CPU responds to the interrupt, it will usually assert

the IACKN signal low. This will cause the OCTART to generate an

IACKN cycle in which the condition of the interrupting device is

determined. When IACKN asserts, the last valid interrupt number is

captured in the CIR. The value captured presents most of the

important details of the highest priority interrupt at the moment the

IACKN (or the ”Update CIR” command) was asserted.

The Octal UART will respond to the IACKN cycle with an interrupt

vector. The interrupt vector may be a fixed value, the content of the

Interrupt Vector Register, or ,when ”Interrupt Vector Modification is

enabled via ICR, it may contain codes for the interrupt type and/or

interrupting channel. This allows the interrupt vector to steer the

interrupt service directly to the proper service routine. The interrupt

value captured in the CIR remains until another IACKN cycle occurs

or until an ”Update CIR” command is given to the OCTAR T. The

interrupting channel and interrupt type fields of the CIR set the

current ”interrupt context” of the OCTAR T. The channel component

of the interrupt context allows the use of Global Interrupt Information

registers that appear at fixed positions in the register address map.

For example, a read of the Global RxFIFO will read the channel B

RxFIFO if the CIR interrupt context is channel b receiver. At another

time read of the GRxFIFO may read the channel D RxFIFO (CIR

holds a channel D receiver interrupt) and so on. Global registers

exist to facilitate qualifying the interrupt parameters and for writing to

and reading from FIFOs without explicitly addressing them.

The CIR will load with x’00 if IACKN or Update CIR is asserted when

the arbitration circuit is NOT asserting and interrupt. In this

condition there is no arbitration value that exceeds the threshold

value.

Polling

Many users prefer polled to interrupt driven service where there are

a large number of fast data channels and/or the host CPU’s other

interrupt overhead is low. The Octal UART is functional in this

environment.

The most efficient method of polling is the use of the ”update CIR”

command (with the interrupt threshold set to zero) followed by a

read of the CIR. This dummy write cycle will perform the same CIR

capture function that an IACKN falling edge would accomplish in an

interrupt driven system. A subsequent read of the CIR, at the same

address, will give information about an interrupt, if any. If the CIR

contains 0s, no interrupt is awaiting service. If the value is

non–zero, the fields of the CIR may be decoded for type, channel

and character count information. Optionally, the global interrupt

registers may be read for particular information about the interrupt

status or use of the global RxD and TxD registers for data transfer

as appropriate. The interrupt context will remain in the CIR until

another update CIR command or an IACKN cycle is initiated by the

host CPU occurs. The CIR loads with x’00 if Update CIR is asserted

when the arbitration circuit has NOT detected arbitration value that

exceeds the threshold value.

Traditional methods of polling status registers may also be used.

They of course are less efficient but give the most variable and

quickest method of changing the order in which interrupt sources

are evaluated and interrogated.

Enabling and Activating Interrupt sources

An interrupt source becomes enabled when its interrupt capability is

set by writing to the Interrupt Mask Register, IMR. An interrupt

source can never generate an IRQN or have its ”bid” or interrupt

number appear in the CIR unless the source has been enabled by

the appropriate bit in an IMR.

An interrupt source is active if it is presenting its bid to the interrupt

arbiter for evaluation. Most sources have simple activation

requirements. The watch-dog timer, break received, Xon/Xoff or

Address Recognition and change of state interrupts become active

when the associated events occur and the arbitration value

generated thereby exceeds the threshold value programmed in the

ICR (Interrupt Control Register).

The transmitter and receiver functions have additional controls to

modify the condition upon which the initiation of interrupt ”bidding”

begins: the TxINT and RxINT fields of the MR0 and MR2 registers.

These fields can be used to start bidding or arbitration when the

RxFIFO is not empty, 50% full, 75% full or 100% full. For the

transmitter it is not full, 50% empty, 75% empty and empty.

Example: To increase the probability of transferring the contents of a

nearly full RxFIFO, do not allow it to start bidding until 50% or 75%

full. This will prevent its relatively high priority from winning the

arbitration process at low fill levels. A high threshold level could

accomplish the same thing, but may also mask out low priority

interrupt sources that must be serviced. Note that for fast channels

and/or long interrupt latency times using this feature should be used

with caution since it reduces the time the host CPU has to respond

to the interrupt request before receiver overrun occurs.

Setting Interrupt Priorities

The bid or interrupt number presented to the interrupt arbiter is

composed of character counts, channel codes, fixed and

programmable bit fields. The interrupt values are generated for

various interrupt sources as shown in the table below: The value

represented by the bits 9 to 3 in the table below are compared

against the value represented by the “Threshold. The “Threshold”

,bits 6 to 0 of the ICR (Interrupt Control Register), is aligned such

that bit 6 of the threshold is compared to bit 9 of the interrupt value

generated by any of the sources. When ever the value of the

interrupt source is greater than the threshold the interrupt will be

generated.

The channel number arbitrates only against other channels. The

threshold is not used for the channel arbitration. This results in

channel D having the highest arbitration number. The decreasing

order is H to A. If all other parts of an arbitration are equal then the

channel number will determine which channel will dominate in the

arbitration process

.

Philips Semiconductors Product specification

SC28L198Octal UART for 3.3V and 5V supply voltage

1999 Jan 14

14

Table 1. Interrupt Arbitration Priority

Type

B9

B8

B7

B6

B5

B4

B3

Bits 2:0

Receiver w/o error

RxFIFO Byte Count –1

0

0

1

Channel No

Receiver w/ error

RxFIFO Byte Count –1

1

0

1

Channel No

Transmitter

0

TxFIFO Byte Count –1

0

0

Channel No

Change of Break

Programmed Field

0

0

1

0

Channel No

Change of State

Programmed Field

0

1

1

0

Channel No

Xon/Xoff

Programmed Field

0

1

1

1

Channel No

Address Recognition

Programmed Field

0

0

1

1

Channel No

Receiver Watch-dog

RxFIFO Byte Count –1

As RxFIFO Above

Channel No

Threshold

Bits 6:0 of Interrupt Control Register

000

Note several characteristics of the above table in bits 6:3. These

bits contain the identification of the bidding source as indicated

below:

x001 Receiver without error

x101 Receiver with error

xx00 Transmitter

0010 Change of Break

0110 Change of State on I/O Ports

0111 Xon/Xoff Event

0011 Address Recognition

The codes form bits 6:3 drive part of the interrupt vector modification

and the Global Interrupt Type Register. The codes are unique to

each source type and Identify them completely. The channel

numbering progresses from ”a” to ”d” as the binary numbers 000 to

011 and identify the interrupting channel uniquely. As the channels

arbitrate ”d” will have the highest bidding value and ”a” the lowest

Note that the transmitter byte count is off–set from that of the

receiver by one bit. This is to give the receiver more authority in the

arbitration since and over–run receiver corrupts the message but an

under–run transmitter is not harmful. This puts some constraints on

how the threshold value is selected. If a threshold is chosen that

has its MSB set to one then a transmitter can never generate an

interrupt! Of course the counter point to this is the desire to set the

interrupt threshold high so interrupts occur only when a maximum or

near maximum number of characters may be transferred.

To give some control over this dilemma control bits have been

provided in the MR0 and MR2 registers of each channel to

individually control when a receiver or transmitter may interrupt. The

use of these bits will prevent a receiver or a transmitter from

entering the arbitration process even though its FIFO fill level is

above that indicated by the threshold value set. The bits in the MR0

and MR2 register are named TxINT (MR0[5:4]) and RxINT

(MR2[3:2])

The watch-dog is included in the table above to show that it affects

the arbitration. It does not have an identity of its own. A barking

watch-dog will prevent any other source type from entering the

arbitration process except enabled receivers. The threshold is

effectively set to zero when any watch-dog times out. The receivers

arbitrate among them selves and the one with the highest fill level

will win the process. Note that the receiver wining the bid may not

be the one that caused the watch-dog to bark.

The fields labeled ”Programmed Field” are the contents of the

Bidding Control Registers, BCRs, for these sources. Setting these

bits to high values can elevate the interrupt importance of the

sources they represent to values almost as high as a full receiver.

For example a COS event may be very important when it represents

the DSR (Data Set Ready) signal from the modem. In this case its

arbitration value should be high. Once the DSR is recognized then

its arbitration value could be reduced or turned off.

There is a single arbiter interrupt number that is not associated with

any of the UART channels. It is the ”Threshold V alue” and is

comprised of 7 bits from the Interrupt Control Register, ICR, and

three zeros in the channel field. It is only when one or more of

the enabled interrupt sources generates a arbitration value

larger than the threshold value that the IRQN will be asserted.

When the threshold bidding value is larger than any other bidding

value then the IRQN will be withdrawn. In this condition the CIR will

be loaded with if the IRQN or ”Update CIR” command is asserted.

Because the channels are numbered from 0 to 3 ( A to D) channel 3