Philips sad1009 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAD1009

Universal DAC (UDAC)

Preliminary specification

File under Integrated Circuits, IC02

January 1991

Philips Semiconductors Preliminary specification

Universal DAC (UDAC) SAD1009

GENERAL DESCRIPTION

The SAD1009 is intended as a peripheral to a microcontroller-based servo system in video cassette recorders.

The device relieves the microcontroller of some of the real time functions. These functions include; generation of

programmable pulse width signals (duty factor etc.) and accurate measurement of time period signals (tacho signal etc.).

The SAD1009 has nine programmable output ports. All functions of the UDAC are programmable. Commands and data

from the microcontroller are loaded via a bidirectional bus using a 16-bit format. Data from the time period measurement

is transferred to the microcontroller via the same bidirectional bus, also using a 16-bit format. The clock signal for this

device is provided by the quartz oscillator of the microcontroller.

Features

• Generation of programmable pulse width signals

• Measurement of time period signals

• All functions are programmable

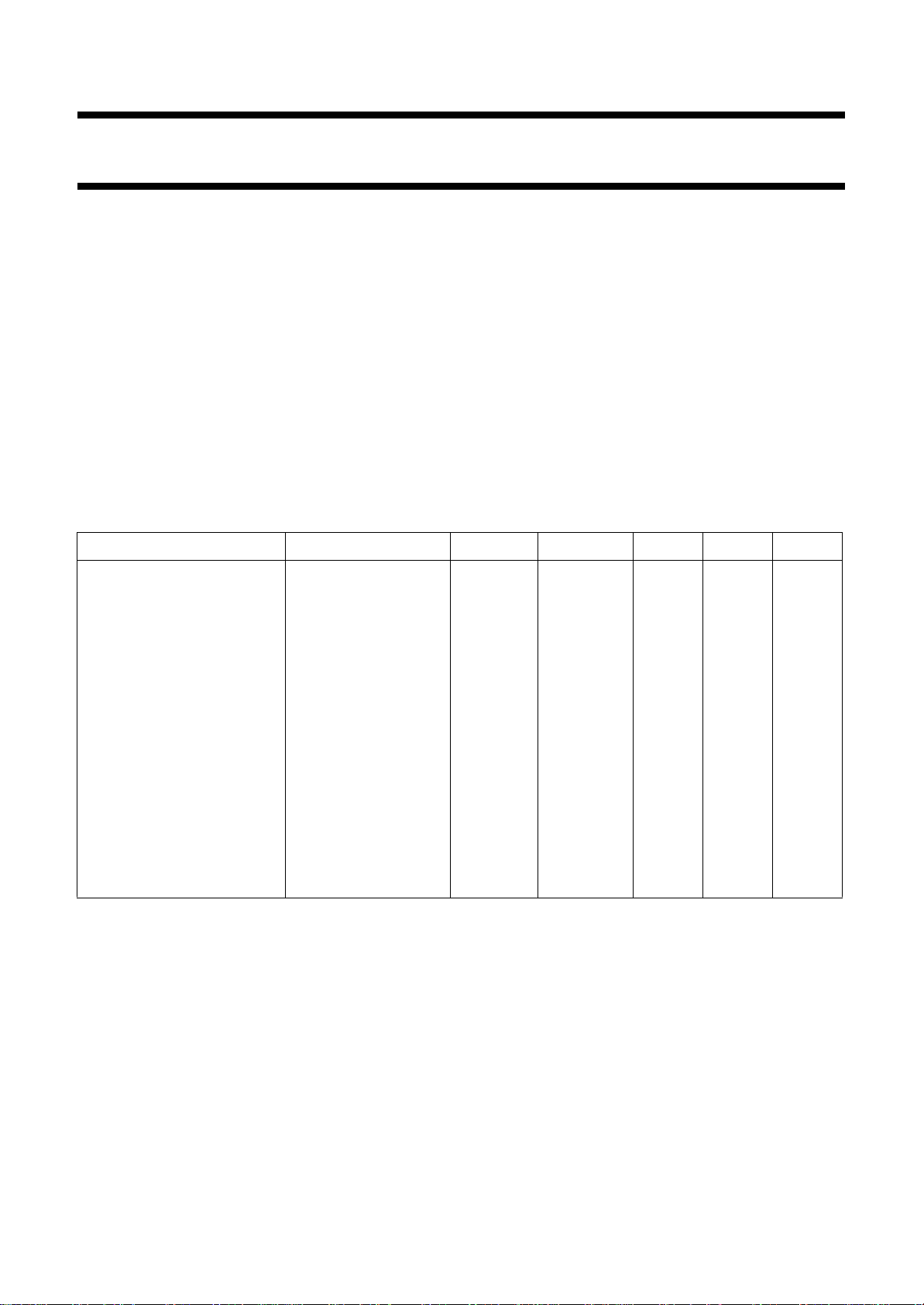

QUICK REFERENCE DATA

PARAMETER CONDITIONS SYMBOL MIN. TYP. MAX. UNIT

Supply

Supply voltage range V

DD

4,75 5,0 5,25 V

Inputs

Input voltage

LOW V

HIGH V

Input leakage current ± I

Input capacitance C

IL

IH

I

I

−−0,8 V

2,4 −−V

−−1µA

−−7,5 pF

Outputs

Output voltage

LOW I

HIGH I

= 1,6 mA V

OL

= − 1,0 mA V

OH

Output sink current I

Output source current − I

OL

OH

O

O

−−0,4 V

VDD−0,4 −−V

−−1,6 mA

−−1,0 mA

PACKAGE OUTLINES

SAD1009P: 24-lead DIL; plastic (SOT101A); SOT101-1; 1996 November 18.

SAD1009T: 24-lead mini-pack; plastic (SO24; SOT137A); SOT 137-1; 1996 November 18.

January 1991 2

Philips Semiconductors Preliminary specification

Universal DAC (UDAC) SAD1009

January 1991 3

Fig.1 Block diagram.

Philips Semiconductors Preliminary specification

Universal DAC (UDAC) SAD1009

PINNING

Fig.2 Pinning diagram.

Power supply

V

V

Inputs

S/L shift/latch input

FOSC oscillator input

TXD serial clock

Special inputs

TIM timer input

Outputs

Q0 to Q8 programmable output ports

PPW1 to PPW7 programmable pulse width outputs

Input/outputs

RXD serial data

R/

positive supply voltage (+5V)

DD

ground ( 0 V )

SS

O handshake

January 1991 4

Philips Semiconductors Preliminary specification

Universal DAC (UDAC) SAD1009

FUNCTIONAL DESCRIPTION

Loading data

All commands and data are loaded into the SAD1009 via the bidirectional bus (TXD, RXD). The bidirectional bus is

compatible with the serial interface of the ‘8051’ microcontroller, using mode 0.

A 16-bit word is used to program a function of the UDAC. The first 3-bits received from the RAM constitute the address

and the remaining 13-bits are data (LSB first, MSB last). None of the functions require all 13-bits of data, therefore, 16-bit

words contain a number of immaterial bits (x). The programming format is shown in Table 1.

To shift a program word into the input buffer of the UDAC the S/

input buffer are transferred to the appropriate RAM on the HIGH-to-LOW transition of the S/L signal. When S/L is LOW

the input buffer is disabled and cannot accept new incoming information. Fig.3 illustrates the program reception cycle.

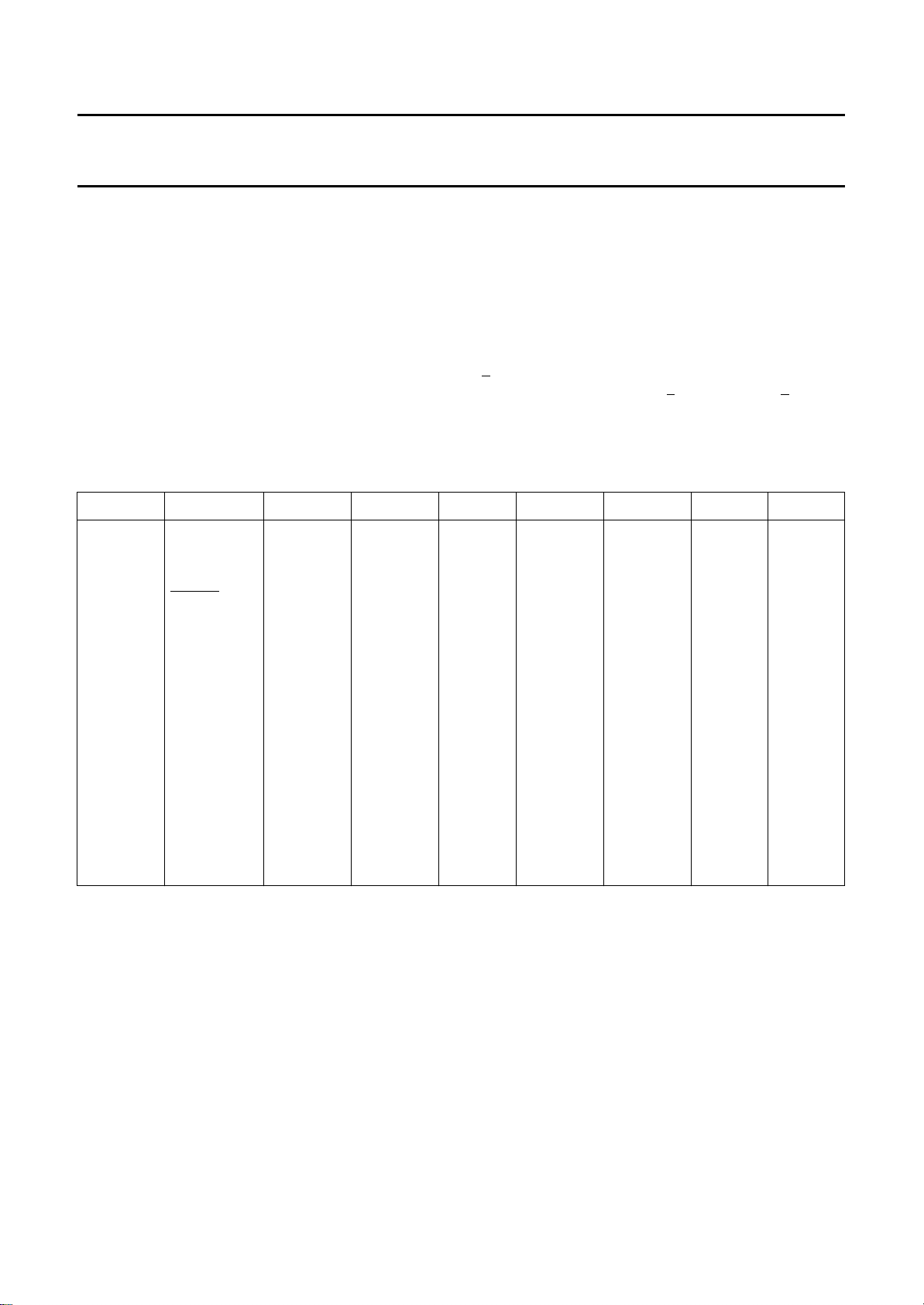

Table 1 Programming format

BIT STATUS PPW1 PPW2 PPW3 PPW4 PPW5 PPW6 PPW7

1L HLHLHLH

2L LHHLLHH

3L LLLHHHH

4

5X XXXXXQ5Q7

6X XXXXXXX

7X XXXXXXX

8X XXXXXXX

9 Q0 D8D8D8D8D8D8D8

10 Q1 D7 D7 D7 D7 D7 D7 D7

11 Q2 D6 D6 D6 D6 D6 D6 D6

12 Q3 D5 D5 D5 D5 D5 D5 D5

13X D4D4D4D4D4D4D4

14X D3D3D3D3D3D3D3

15 M1 D2 D2 D2 D2 D2 D2 D2

16 M2 D1 D1 D1 D1 D1 D1 D1

RESET Q8 X X X X Q4 Q6

L line (shift/latch not) must be HIGH. The contents of the

Where:

X : don’t care

D 1 to D8: data for programming pulse width, D1 = MSB and D8 = LSB

January 1991 5

‘

Philips Semiconductors Preliminary specification

Universal DAC (UDAC) SAD1009

Fig.3 Program reception cycle: a) normal reception cycle; b) no information is loaded into the input buffer,

the RAMs contents remain unchanged.

Pulse width modulated outputs

The UDAC has seven pulse width modulated outputs (PPW1 to PPW7). The output PPW1 is slightly different to outputs

PPW2 to PPW7, the difference is explained below. Each output produces a pulse width modulated signal with a duty

factor programmable in steps of 1/256 and has a repetition frequency of approximately 23 kHz. These pseudo analogue

signals are used to control the capstan and reel drives. Motor control can be performed in the following ways:

• convert the pulse width modulated signal into an analogue signal using filtering and analogue power amplification

• by feeding the pulse width modulated signal to the motor via a power switch and a switch mode filter

To conserve power use the second method for control of the capstain and reel motors. For the scanner control two

outputs are available, so that by weighted addition a higher resolution can be achieved.

PPW1 is also an 8-bit programmable output, with a repetition frequency of 23 kHz. The difference is the low frequency

contents of the signal are reduced by changing the distribution of the HIGH and LOW level portions. This redistribution

means that a filter with two poles; each at 43 µs, is sufficient to reduce the peak-to-peak ripple to less than 1 LSB.

This output is for use in applications where long filter delays are not tolerated.

January 1991 6

Loading...

Loading...