Philips sab9076h DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAB9076H

Picture-In-Picture (PIP) controller

Preliminary specification

File under Integrated Circuits, IC02

1996 Aug 13

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

FEATURES

Display

• Twin PIP in interlaced mode at 8-bit resolution

• Sub-title mode features built in

• Large display fine positioning area, both channels

independent

• Only 2 Mbit required as external VDRAM

(2 × 1 Mbit or 1 × 2 Mbit)

• Four 8-bit Analogue Digital Converters (ADCs; > 7-bit

performance) with clamp circuit

• Most PIP modes handle interlaced pictures without joint

line error

• Two PLLs which generate the line-locked clocks for the

acquisition channels

• Display PLL to generate line-locked clock for the display

• Three 8-bit Digital Analogue Converters (DACs)

• 4:1:1 data format

• Data reduction factors 1 to 1, 1 to 2, 1 to 3 and 1 to 4,

horizontal and vertical independent.

2

I

C-bus programmable

GENERAL DESCRIPTION

The SAB9076H is a picture-in-picture controller for NTSC

TV-sets. The circuit contains ADCs, reduction circuitry,

memory control, display control and DACs.

The device inserts one or two live video signals with

original or reduced sizes into a live video signal. All video

signals are expected to be analog baseband signals.

The conversion into the digital environment and back to

the analog environment is carried out on chip. Internal

clocks are generated by two acquisition PLLs and a

display PLL.

Due to the two PIP channels and a large external memory

a wide range of PIP modes are offered. The emphasis is

put on single-PIP, double-PIP, split-screen mode and a

many multi-PIP modes.

• Single and double PIP modes can be set

• Full field still mode available

• Several aspect ratios can be handled

• Reduction factors can be set freely

• Selection of vertical filtering type

• Freeze of live pictures

• Fine tuned display position, H (8-bit), V (8-bit),

both channels independent

• Fine tuned acquisition area, H (4-bit), V (8-bit),

both channels independent

• Eight main borders, sub-borders and background

colours selectable

• Border and background brightness adjustable, 30%,

50%, 70% and 100% IRE

• Several type of decoder input signals can be set.

1996 Aug 13 2

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

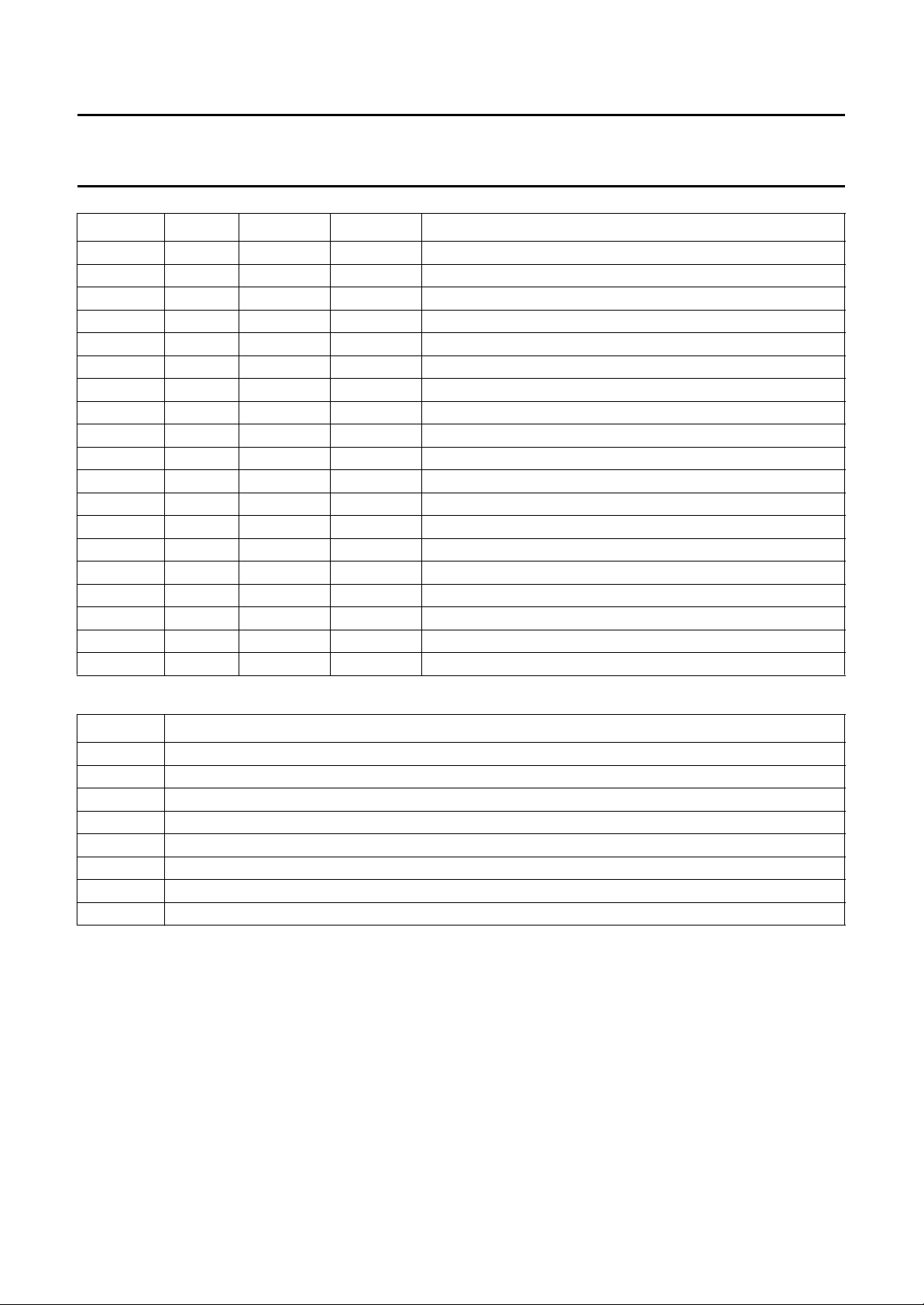

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD

I

DD

f

sys

f

loop

t

jitter

ς PLL damping factor − 0.7 −−

Note

1. The internal system frequency is 1728 times the H

ORDERING INFORMATION

supply voltage 4.5 5.0 5.5 V

supply current − 200 − mA

system frequency note 1 − 27 − MHz

PLL loop bandwidth frequency 4 −−kHz

PLL short term stability time jitter during 1 line (64 µs) −−4ns

input frequency for both the Acquisition and Display PLLs.

Sync

TYPE

NUMBER

NAME DESCRIPTION VERSION

SAB9076H QFP100

(1)

plastic quad flat package; 100 leads (lead length 1.95 mm);

PACKAGE

body 14 × 20 × 2.8 mm

Note

1. When using IR reflow soldering it is recommended that the Drypack instructions in the

(order number 9398 510 63011) are followed.

SOT317-2

“Quality Reference Handbook”

1996 Aug 13 3

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

BLOCK DIAGRAM

sync

bias

DPV

DV

sync

DPH

MGC962

DYDUDV

bias

DAV

refT

DAV

refB

DAV

DFB

andbook, full pagewidth

DDA

DAV

SSA

DAV

92 84 83

DDD

DAV

91

SSD

DAV

51, 53, 55,

AD0 to AD8

23, 25, 27,

DAI0 to DAI7

DAO0 to DAO7

31 40 32, 34, 36,

DT

47

WE SC

CAS

49 48

RAS

DDD

MV

SSD

MV

67 13 14

DDD

SV

68

SSD

SV

DDA

SAV

SSA

SAV

77 69 70

DDD

SAV

78

SSD

SAV

DDA

MAV

SSA

MAV

4 12 11

DDD

MAV

3

SSD

MAV

869088

57, 58, 56,

54, 52, 50

29, 30, 28,

26, 24

38, 39, 37,

35, 33

71

DAC

AND

AND

HORIZONTAL

CLAMP AND ADC

75

73

858789

BUFFER

VDRAM CONTROL AND (RE-) FORMATTING

FILTER

VERTICAL

767472

93

DISPLAY

CONTROL

LINE MEMORY

GENERATOR

PLL AND CLOCK

796480

1068

LINE MEMORYSAB9076H

AND

FILTER

VERTICAL

HORIZONTAL

CLAMP AND ADC

579

969495

GENERATOR

PLL AND CLOCK

C-BUS CONTROL

2

I

LINE MEMORY

GENERATOR

PLL AND CLOCK

2171

6318192221201516596061628281 4142434445466566979899

100

TDCLKTM2

TM0

SSD

MCV

SCL

POR

DDD

DCV

SSD

DV

DDD

V

DDD

SCV

SSA

SPV

DDA

DPV

SSA

MPV

TACLKTC

TM1

DDD

MCV

A0

SDA

SSD

DCV

DDD

DV

SSD

V

SSD

SCV

DDA

SPV

SSA

DPV

DDA

MPV

Fig.1 Block diagram.

SYSUSV

bias

SAV

refT

SAV

refB

SAV

syncSVsync

SPH

bias

SPV

1996 Aug 13 4

MYMUMV

bias

MAV

refT

MAV

refB

MAV

syncMVsync

MPH

bias

MPV

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

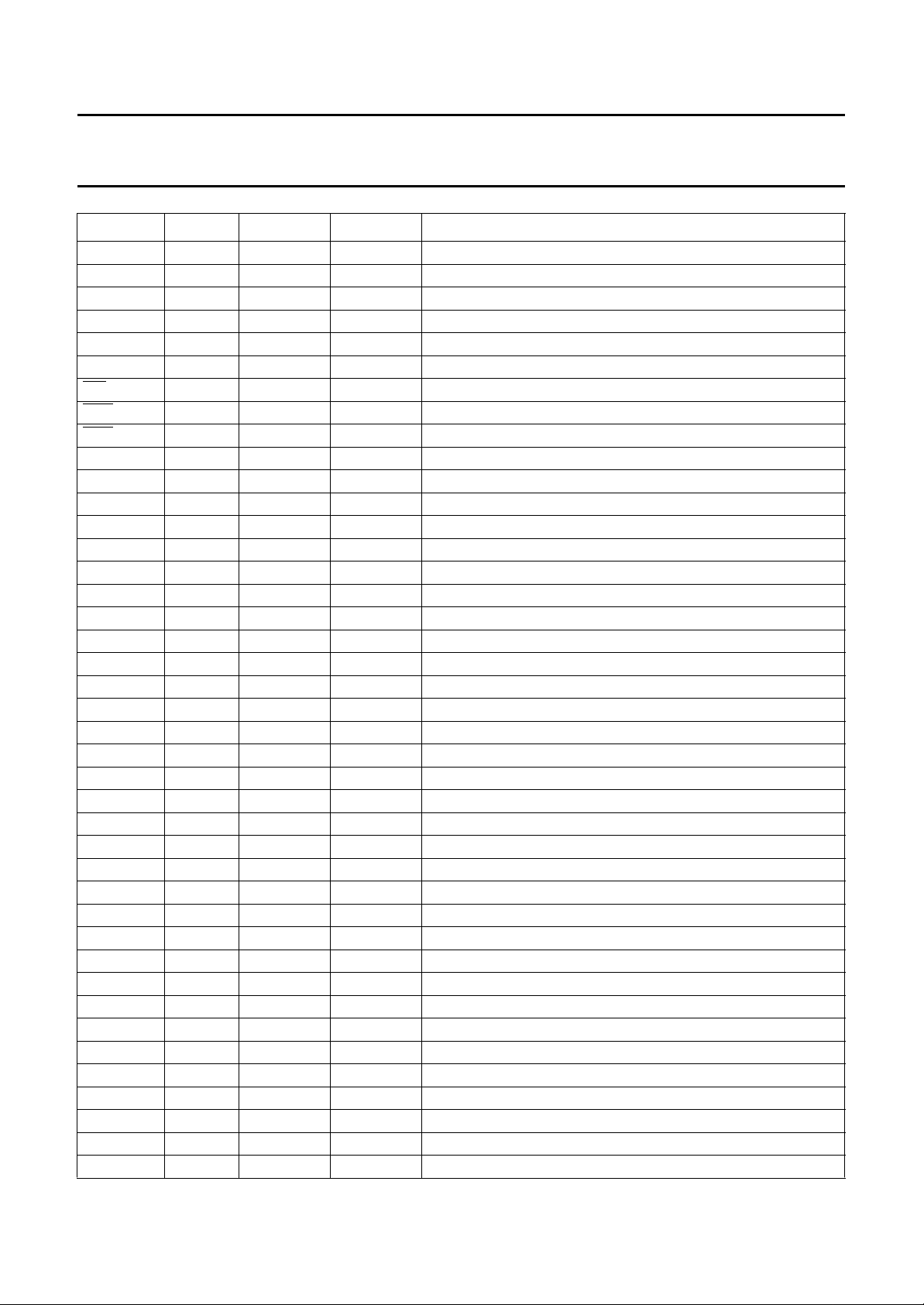

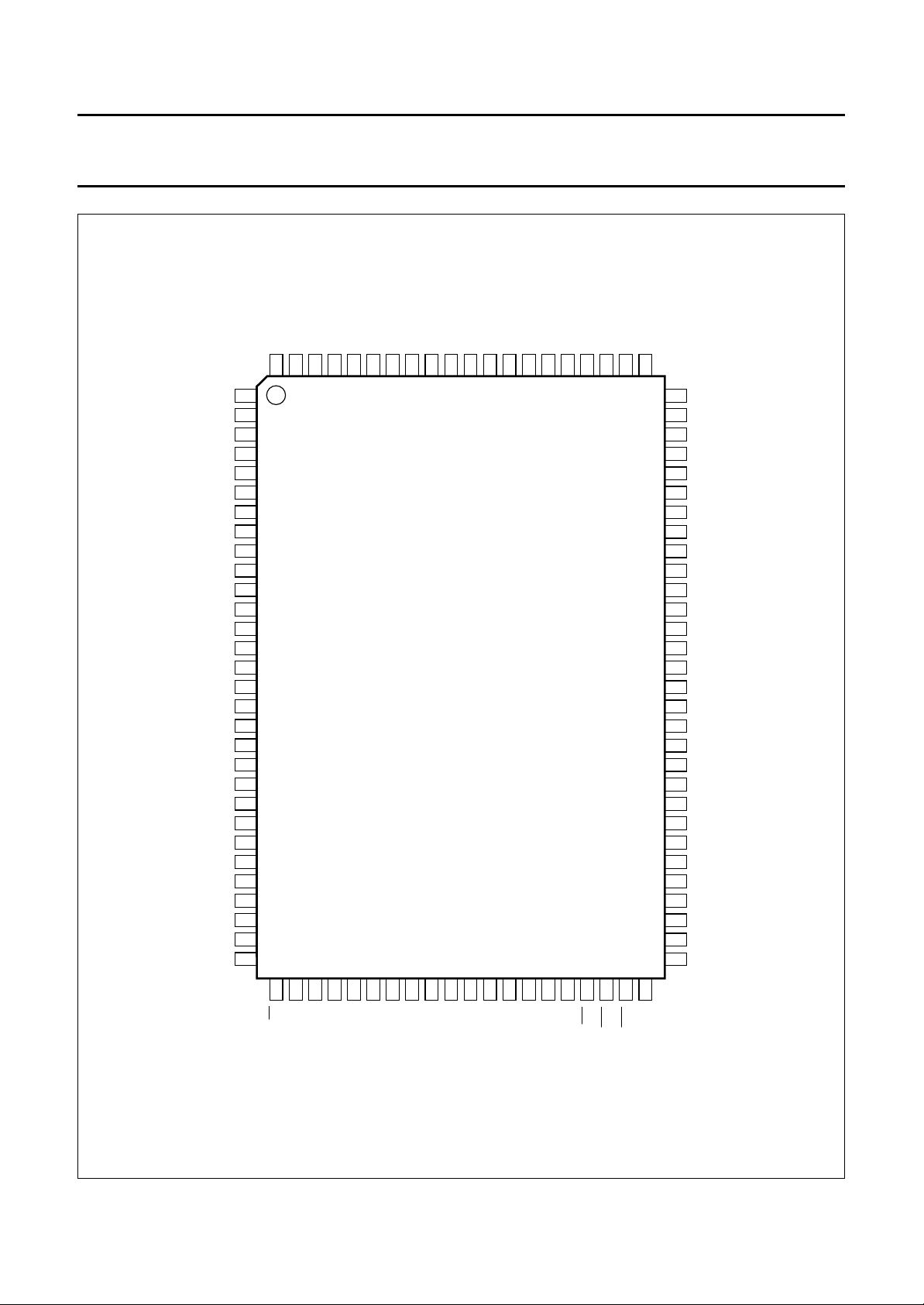

PINNING

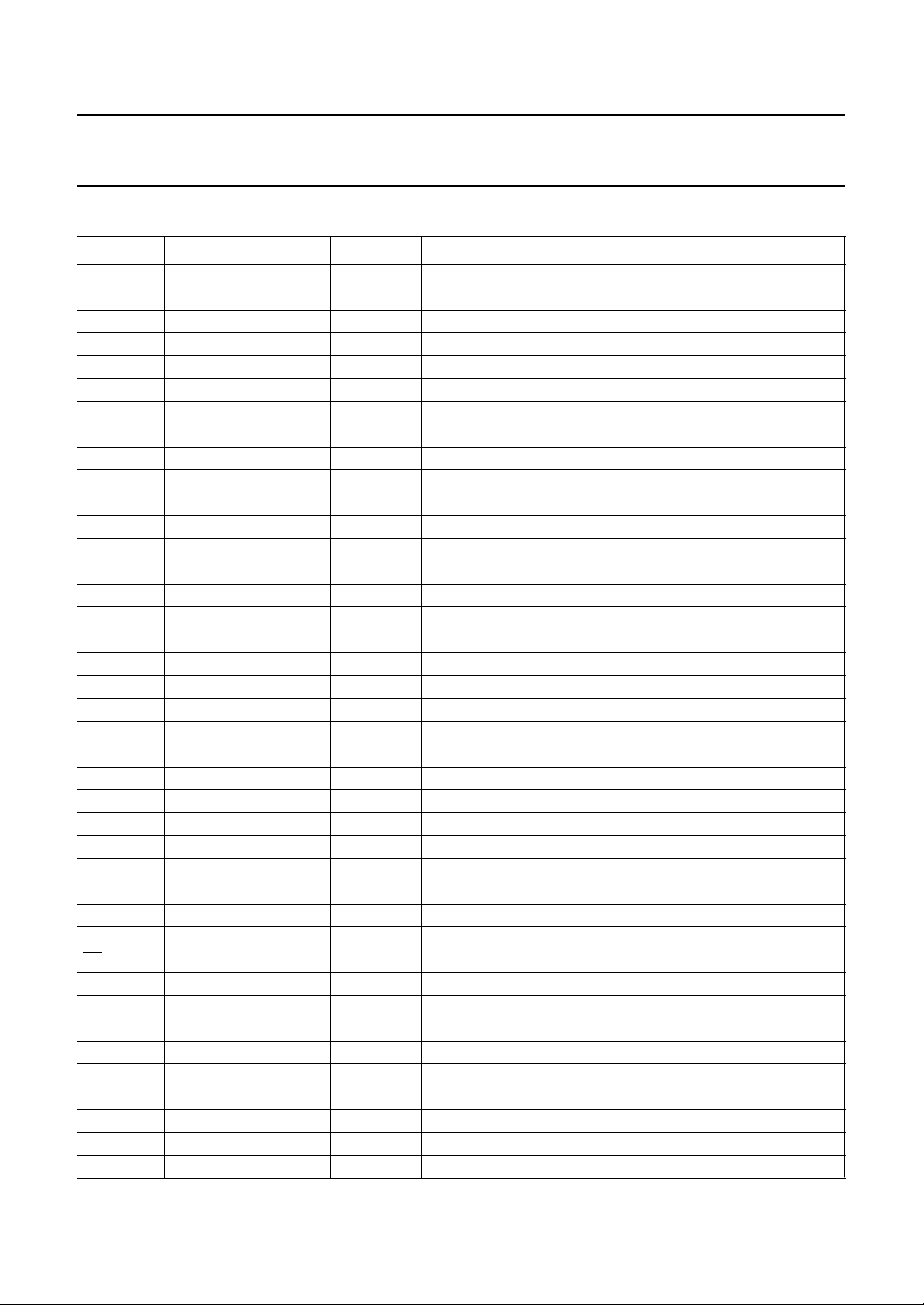

SYMBOL PIN I/O TYPE DESCRIPTION

MPV

bias

MPH

sync

MAV

SSD

MAV

DDD

MAV

bias

MU 6 I E027 analog U input for main channel

MAV

refT

MV 8 I E027 analog V input for main channel

MAV

refB

MY 10 I E027 analog Y input for main channel

MAV

DDA

MAV

SSA

MV

SSD

MV

DDD

MCV

DDD

MCV

SSD

MV

sync

TDCLK 18 I HPP01 test clock input for display

TC 19 I HPP01 test control input

TM0 20 I HPP01 test mode 0 input

TM1 21 I HPP01 test mode 1 input

n.c. 22 −−not connected

DAI0 23 I HPP01 data bus input from memory; bit 0

DAI7 24 I HPP01 data bus input from memory; bit 7

DAI1 25 I HPP01 data bus input from memory; bit 1

DAI6 26 I HPP01 data bus input from memory; bit 6

DAI2 27 I HPP01 data bus input from memory; bit 2

DAI5 28 I HPP01 data bus input from memory; bit 5

DAI3 29 I HPP01 data bus input from memory; bit 3

DAI4 30 I HPP01 data bus input from memory; bit 4

DT 31 O OPF20 memory data transfer output; active LOW

DAO0 32 O OPF20 data bus output to memory; bit 0

DAO7 33 O OPF20 data bus output to memory; bit 7

DAO1 34 O OPF20 data bus output to memory; bit 1

DAO6 35 O OPF20 data bus output to memory; bit 6

DAO2 36 O OPF20 data bus output to memory; bit 2

DAO5 37 O OPF20 data bus output to memory; bit 5

DAO3 38 O OPF20 data bus output to memory; bit 3

DAO4 39 O OPF20 data bus output to memory; bit 4

SC 40 O OPF20 memory shift clock output

1 I/O E027 analog bias reference for main channel

2 I HPP01 horizontal synchronization input for main channel

3 I/O E009 digital ground for main channel ADCs and PLLs

4 I/O E030 digital positive power supply for main channel ADCs and PLLs

5 I E027 analog bias reference input for main channel ADCs

7 I E027 analog top reference voltage input for main channel ADCs

9 I E027 analog bottom reference voltage input for main channel ADCs

11 I/O E030 analog positive power supply for main channel ADCs

12 I/O E009 analog ground for main channel ADCs

13 I/O E009 digital ground for main-channel core

14 I/O E030 digital positive power supply for main-channel core

15 I/O E030 digital positive power supply for main-clock buffer

16 I/O E009 digital ground for main-clock buffer

17 I HPP01 vertical synchronization input for main channel

1996 Aug 13 5

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

SYMBOL PIN I/O TYPE DESCRIPTION

DCV

SSD

DCV

DDD

DV

DDD

DV

SSD

V

SSD

V

DDD

WE 47 O OPF20 memory write enable output; active LOW

CAS 48 O OPF20 memory column address strobe output; active LOW

RAS 49 O OPF20 memory row address strobe output; active LOW

AD8 50 O OPF20 memory address bus output; bit 8

AD0 51 O OPF20 memory address bus output; bit 0

AD7 52 O OPF20 memory address bus output; bit 7

AD1 53 O OPF20 memory address bus output; bit 1

AD6 54 O OPF20 memory address bus output; bit 6

AD2 55 O OPF20 memory address bus output; bit 2

AD5 56 O OPF20 memory address bus output; bit 5

AD3 57 O OPF20 memory address bus output; bit 3

AD4 58 O OPF20 memory address bus output; bit 4

A0 59 I HPF01 I

SCL 60 I HPF01 shift clock input for I

SDA 61 I/O IOI41 shift I

POR 62 I HUP07 power-on reset input

TACLK 63 I HPP01 test clock input for acquisition

SV

sync

SCV

SSD

SCV

DDD

SV

DDD

SV

SSD

SAV

SSA

SAV

DDA

SY 71 I E027 analog Y input for sub-channel

SAV

refB

SV 73 I E027 analog V input for sub-channel

SAV

refT

SU 75 I E027 analog U input for sub-channel

SAV

bias

SAV

DDD

SAV

SSD

SPH

sync

SPV

bias

SPV

SSA

41 I/O E009 digital ground for display-clock buffer

42 I/O E030 digital positive power supply for display-clock buffer

43 I/O E030 digital positive power supply for display core

44 I/O E009 digital ground for display core

45 I/O E009 digital ground for peripherals

46 I/O E030 digital positive power supply for peripherals

2

C-bus address 0 selection input

2

C-bus

2

C-bus input data; acknowledge I2C-bus output data

64 I HPP01 vertical synchronization input for sub-channel

65 I/O E009 digital ground for sub-clock buffer

66 I/O E030 digital positive power supply for sub-clock buffer

67 I/O E030 digital positive power supply for sub-channel core

68 I/O E009 digital ground for sub-channel core

69 I/O E009 analog ground for sub-channel ADCs

70 I/O E030 analog positive power supply for sub-channel ADCs

72 I E027 analog bottom reference input voltage for sub-channel ADCs

74 I E027 analog top reference input voltage for sub-channel ADCs

76 I/O E027 analog bias reference input/output for sub-channel ADCs

77 I/O E030 digital positive power supply for sub-channel ADCs and PLLs

78 I/O E009 digital ground for sub-channel ADCs and PLLs

79 I HPP01 horizontal synchronization input for sub-channel

80 I/O E027 analog bias reference input/output for sub-channel

81 I/O E009 analog ground for sub-channel PLL

1996 Aug 13 6

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

SYMBOL PIN I/O TYPE DESCRIPTION

SPV

DDA

DAV

DDA

DAV

SSA

DAV

bias

DY 86 O E027 analog Y output of DAC

DAV

refT

DV 88 O E027 analog V output of DAC

DAV

refB

DU 90 O E027 analog U output of DAC

DAV

SSD

DAV

DDD

DFB 93 O OPF20 fast blanking control output signal

DV

sync

DPH

sync

DPV

bias

DPV

SSA

DPV

DDA

MPV

DDA

MPV

SSA

82 I/O E030 analog positive power supply for sub-channel PLL

83 I/O E030 analog positive power supply for DACs

84 I/O E009 analog ground for DACs

85 I E027 analog bias voltage reference input for DACs

87 I E027 analog top reference input voltage for DACs

89 I E027 analog bottom reference input voltage for DACs

91 I/O E009 digital ground for DACs

92 I/O E030 digital positive power supply for DACs

94 I HPP01 vertical synchronization input for display channel

95 I HPP01 horizontal synchronization input for display PLL

96 I/O E027 analog bias voltage reference input/output for display PLL

97 I/O E009 analog ground for display PLL

98 I/O E030 analog positive power supply for display PLL

99 I/O E030 analog positive power supply for main channel PLL

100 I/O E009 analog ground for main channel PLL

Table 1 Pin type explanation

PIN TYPE DESCRIPTION

E030 V

E009 VSSpin; diode to V

E027 analog input pin; diode to VDD and V

HPF01 digital input pin; CMOS levels, diode to V

HPP01 digital input pin; CMOS levels, diode to VDD and V

pin; diode to V

DD

SS

DD

SS

SS

SS

HUP07 digital input pin; CMOS levels with hysteresis, pull-up resistor to VDD, diode to VDD and V

IOI41 I2C-bus pull-down output stage; CMOS input levels, diode to V

SS

OPF20 digital output pin; CMOS levels

SS

1996 Aug 13 7

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

handbook, full pagewidth

MPV

MPH

MAV

MAV

MAV

MAV

MAV

MAV

MAV

MV

MV

MCV

MCV

MV

bias

sync

SSD

DDD

bias

MU

refT

MV

refB

MY

DDA

SSA

SSD

DDD

DDD

SSD

sync

TDCLK

TC

TM0

TM1

n.c.

DAI0

DAI7

DAI1

DAI6

DAI2

DAI5

DAI3

DAI4

SSA

DDA

DDA

MPV

MPV

DPV

99989796959493929190898887868584838281

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

SSA

DPV

bias

DPV

sync

DPH

sync

DV

DDD

SSD

DFB

DAV

DAV

SAB9076H

DU

refB

DAV

DV

refT

DAV

DY

bias

DAV

SSA

DAV

DDA

DAV

DDA

SPV

SSA

SPV

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

5130

SPV

bias

SPH

sync

SAV

SSD

SAV

DDD

SAV

bias

SU

SAV

refT

SV

SAV

refB

SY

SAV

DDA

SAV

SSA

SV

SSD

SV

DDD

SCV

DDD

SCV

SSD

SV

sync

TACLK

POR

SDA

SCL

A0

AD4

AD3

AD5

AD2

AD6

AD1

AD7

AD0

31323334353637383940414243444546474849

DT

DAO0

DAO7

DAO1

DAO6

DAO2

DAO5

DAO3

DAO4

Fig.2 Pin configuration.

1996 Aug 13 8

SC

SSD

DCV

DDD

DCV

DDD

DV

SSDVSSD

DV

DDD

V

WE

CAS

RAS

50

MGC963

AD8

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

FUNCTIONAL DESCRIPTION

Pixel rate

The internal chrominance format used is 4 : 1 : 1. It is

expected that the bandwidth of the input signals is limited

to 4.5 MHz for the Y input and 1.125 MHz for the U/V input.

The Y input is sampled with a 1728 × HS (≈27.0 MHz)

clock and is filtered and down sampled to the internal

864 × HS (≈13.5 MHz) pixel rate.

The U and V inputs are multiplexed and sampled with a

432 × HS clock and down sampled to the internal

216 × HS (≈3.375 MHz) pixel rate.

Acquisition area

Synchronisation is achieved via the acquisition H

V

pins. With the acquisition fine positioning added to a

sync

Sync

and

system constant the starting point of the acquisition can be

controlled.

The acquisition area is 672 pixels/line and 228 lines/field

for NTSC. Both main and sub-channels are equivalent in

handling the data.

Display mode

The internal display pixel rate is 864 × DPH

sync

which is

13.5 MHz. This pixel rate is up sampled by interpolation to

1728 × DPH

before the DAC stage.

sync

Display area

The display background is an area of 696 pixels and

238 lines. This can be put on/off by the BGON bit

independent of the PIPON bit. This area can be moved by

the display background fine positioning (BGHFP and

BGVFP registers). Its colour is determined by the BGCOL

and BGBRT registers.

Within this area PIPs are defined dependent on the PIP

mode. The PIP sizes are determined by the display

reduction factors as is shown in Table 2.

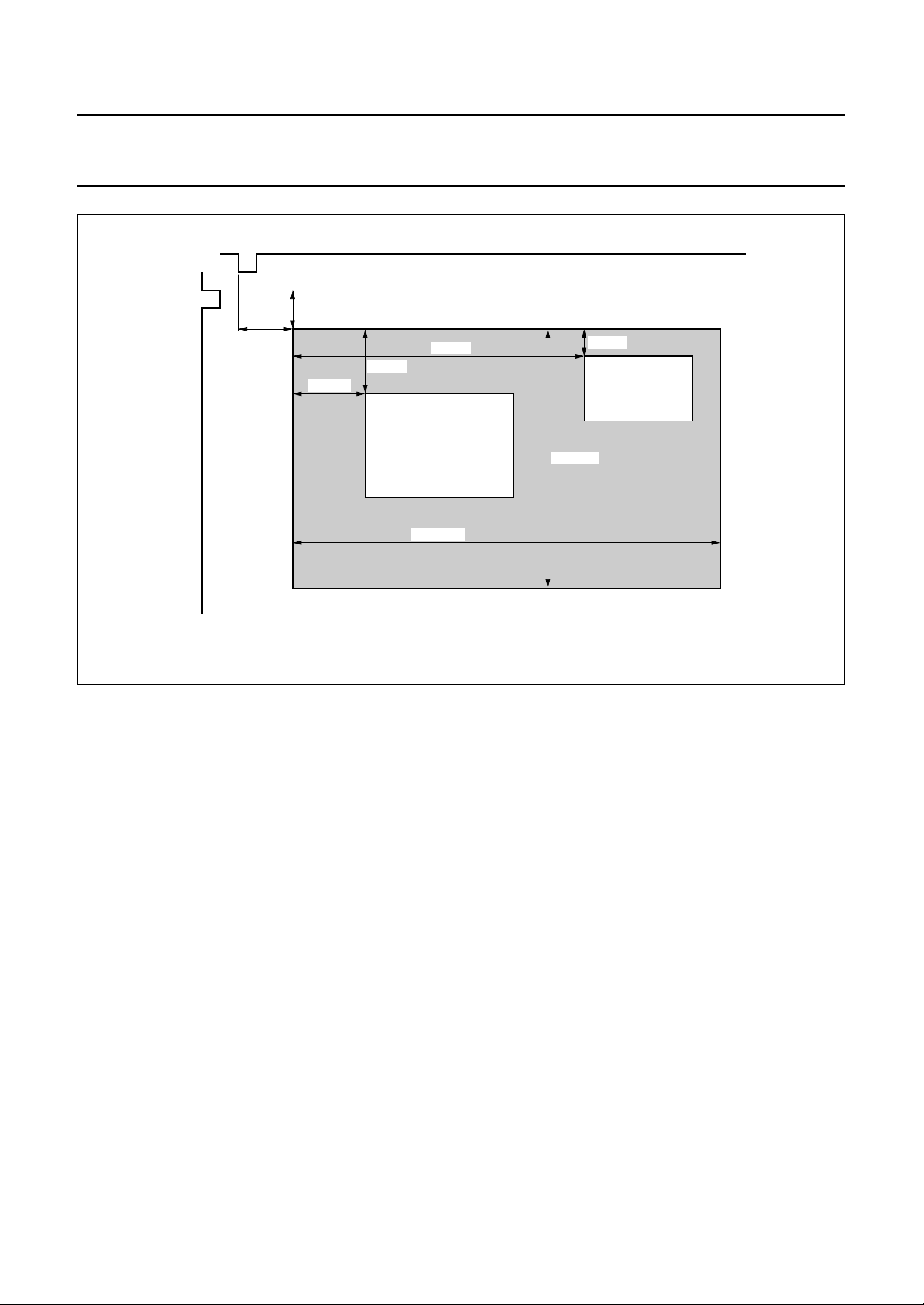

The display fine positioning determines the location of the

PIPs with respect to the background. Sub-channel and

main channel both have their independent PIP size and

location control, which is shown in Fig.3.

Table 2 PIP sizes

REDUCTION H/1 H/2 H/3 H/4 V/1 V/2 V/3 V/4

Pixels 672 336 224 168 −−−−

Lines −−−−228 114 76 57

1996 Aug 13 9

Philips Semiconductors Preliminary specification

Picture-In-Picture (PIP) controller SAB9076H

handbook, full pagewidth

BGHFP

BGVFP

SAHFP

MAVFP

MAHFP

MAIN CHANNEL

696 pixels

Fig.3 Display fine positioning.

PIP modes

The two independent acquisition channels can be

controlled independently on the display side. A wide

variety of modes is possible but a subset of 7 modes is

fixed and can be set easily by the I2C-bus. An overview of

the preconditioned modes is given in Table 3. For all PIP

modes the main and sub-display fine positioning must be

set to obtain a display configuration.

D

ATA TRANSFER

SAVFP

SUB CHANNEL

238 lines

MGC964

Approximately 800 8-bit words can be fetched from the

external VDRAM in one display line which is not enough to

display one complete display line with true 8-bit resolution.

Two methods of reducing data are available. One is simply

skipping the 8-bit to 6-bit (SKIP6, I

2

C-bus bit) and the other

is a small form of data reduction to come from 8-bit to 6-bit

(SMART6, I2C-bus bit). If both bits are set to logic 0 the

device is in true 8-bit resolution mode. For the twin PIP

mode the main channel is not placed in the VDRAM but in

an internal buffer, so still 8-bit resolution is achieved.

The internal data path has an 8-bit resolution and 4 :1:1

data format. The communication to the external VDRAM

takes place at 864 × H

(both display and acquisition).

sync

1996 Aug 13 10

Loading...

Loading...