Philips SAB6456, SAB6456T Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAB6456

SAB6456T

Sensitive 1 GHz

divide-by-64/divide-by-256

switchable prescaler

Product specification

File under Integrated Circuits, IC02

June 1986

Philips Semiconductors Product specification

Sensitive 1 GHz divide-by-64/divide-by-256

switchable prescaler

GENERAL DESCRIPTION

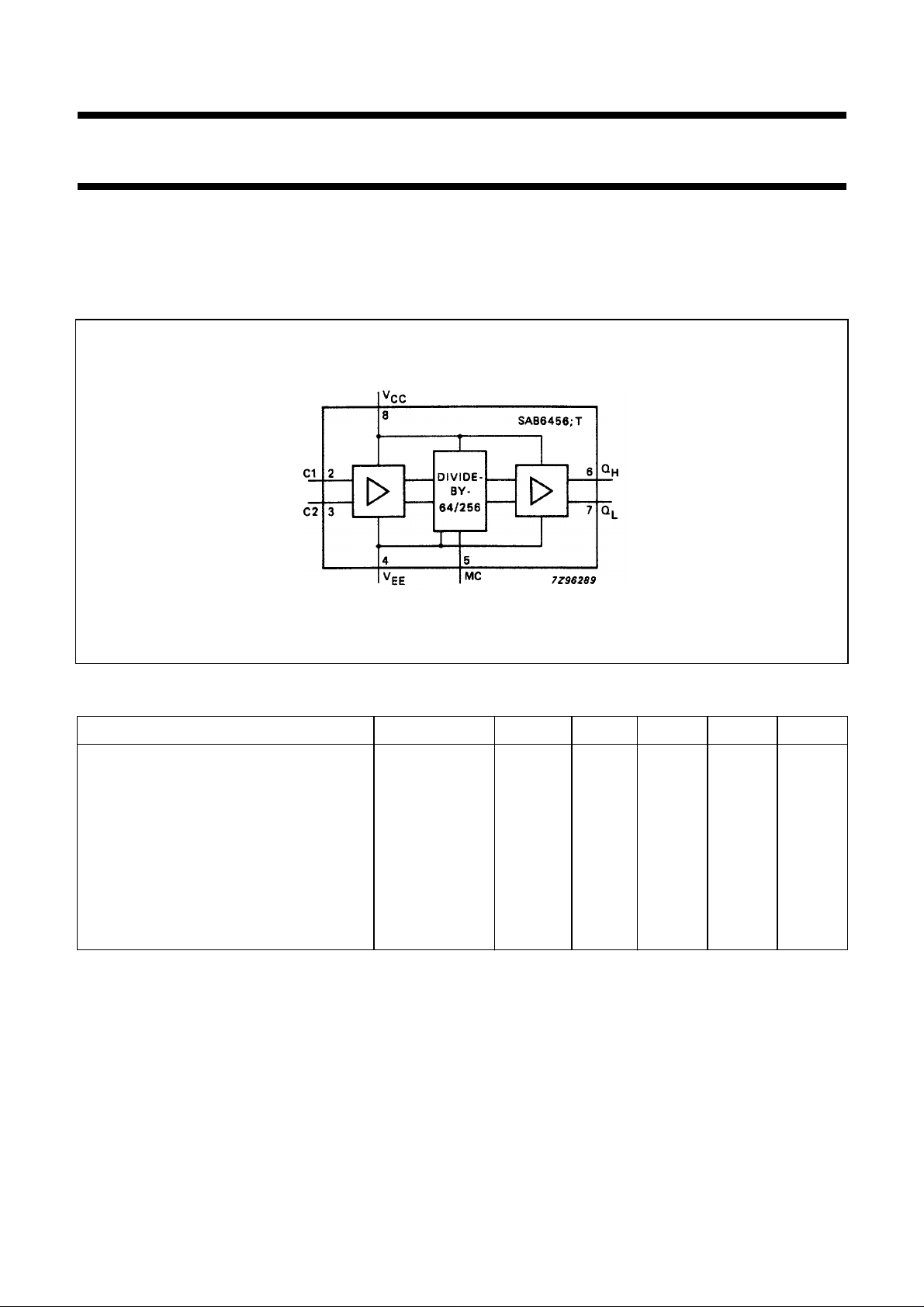

The SAB6456/SAB6456T is a prescaler for UHF/VHF tuners. It can be switched to divide-by-64 or divide-by-256 by the

mode-control (MC) pin. The circuit has an input frequency range of 70 MHz to 1 GHz, has high input sensitivity and good

harmonic suppression.

SAB6456

SAB6456T

Fig.1 Block diagram.

QUICK REFERENCE DATA

PARAMETER CONDITIONS SYMBOL MIN. TYP. MAX. UNIT

Supply voltage pin 8 to pin 4 V

Supply current pin 8 I

Input frequency range pins 2 and 3 f

Sensitivity to input voltage

(r.m.s. value) V

Output voltage

(peak-to-peak value) pins 6 and 7 V

Operating ambient

temperature range T

PACKAGE OUTLINES

SAB6456 : 8-lead DIL; plastic (SOT97); SOT97-1; 1996 November 18.

SAB6456T: 8-lead mini-pack (SO8; SOT96A); SOT96-1; 1996 November 18.

CC

CC

i

i(rms)

o(p-p)

amb

4,5 5,0 5,5 V

− 21 − mA

70 − 1000 MHz

−− 10 mV

− 1 − V

0 − 80 °C

June 1986 2

Philips Semiconductors Product specification

Sensitive 1 GHz divide-by-64/divide-by-256

switchable prescaler

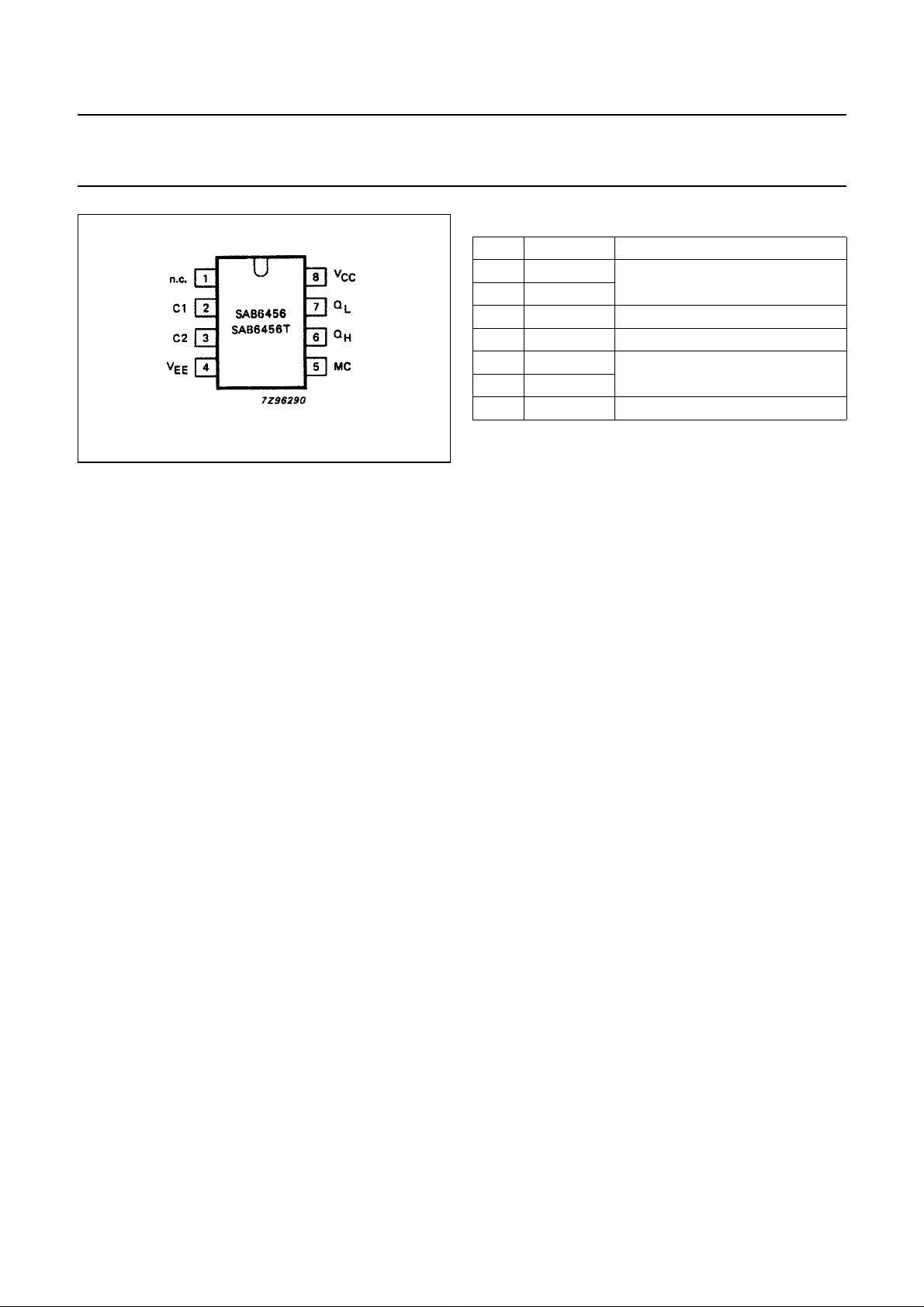

PINNING

1. n.c. not connected

2. C1

3. C2

4. V

5. MC mode control

6. Q

7. Q

8. V

Fig.2 Pinning diagram.

FUNCTIONAL DESCRIPTION

The circuit comprises an input amplifier, a divider stage with selectable division ratio and an output stage.

The input amplifier is driven by a sinusoidal signal from the local oscillator of a television tuner. The inputs (C1, C2) are

differential and are biased internally to permit capacitive coupling. When driven asymmetrically the unused input should

be connected to ground via a capacitor.

EE

H

L

CC

differential inputs

ground (0 V)

complementary outputs

positive supply voltage

SAB6456

SAB6456T

The mode-control (MC) input to the divider stage is intended for static control of the division ratio, selection is made as

follows:

divide-by-64: MC pin open-circuit

divide-by-256: MC pin connected to ground

The divider stage may oscillate during no-signal conditions but this oscillation is suppressed when input signals are

received.

Two complementary signals (Q

output signals are slowed internally to reduce harmonics in the television intermediate frequency band.

, QL) are provided by the output differential amplifier stage. The voltage-edges of the

H

June 1986 3

Loading...

Loading...