Philips saa7392 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

SAA7392

Channel encoder/decoder CDR60

Preliminary specification

File under Integrated Circuits, IC01

2000 Mar 21

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 QUICK REFERENCE DATA

4 ORDERING INFORMATION

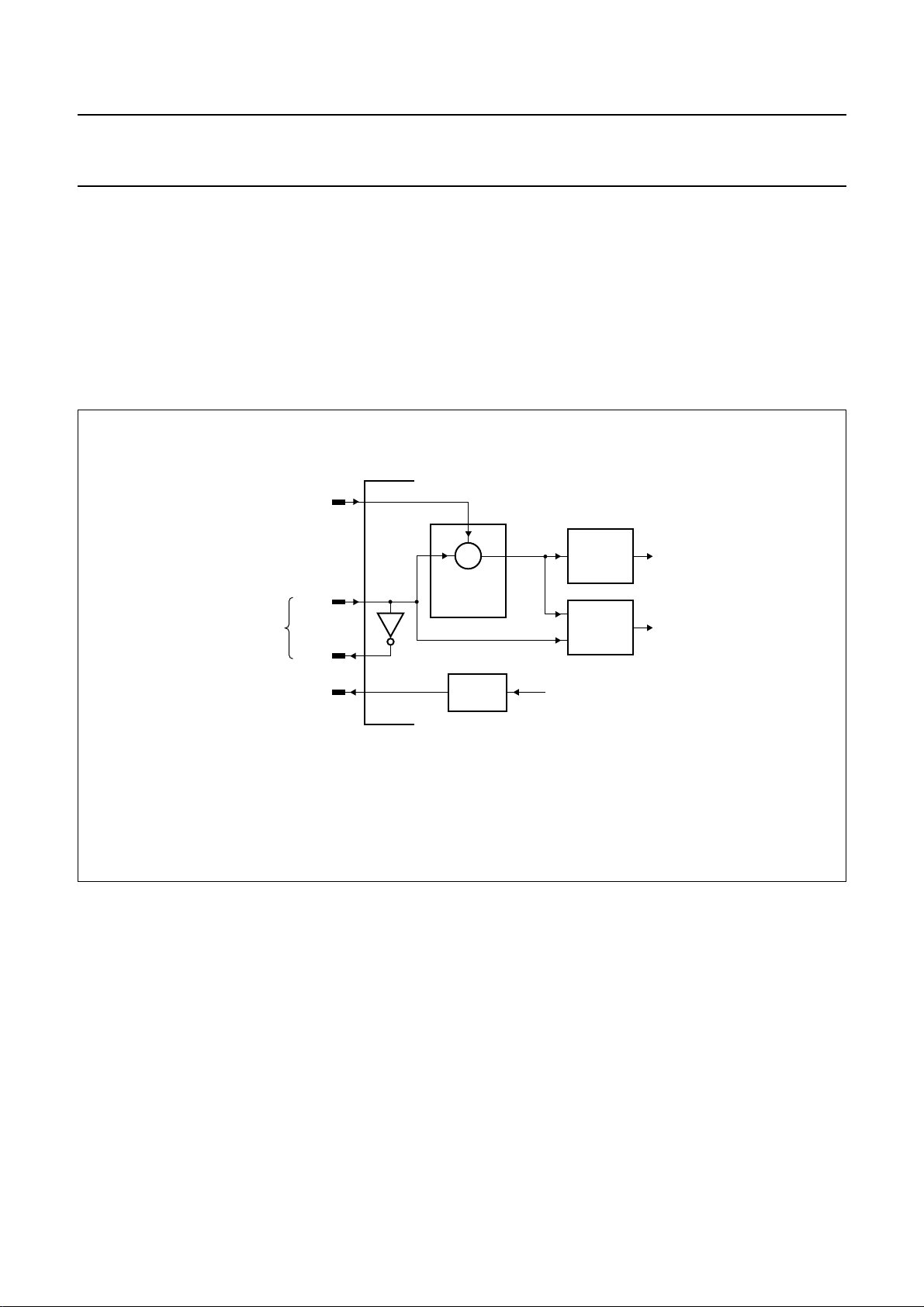

5 BLOCK DIAGRAM

6 PINNING INFORMATION

6.1 Pinning

6.2 Pin description

7 FUNCTIONAL DESCRIPTION

7.1 Microprocessor interfaces

7.2 Register map

7.3 System clocks

7.4 HF analog front-end

7.5 Bit recovery

7.6 Decoder function

7.7 Subcode interface

7.8 Digital output

7.9 Serial output interface

7.10 Motor control

7.11 The serial in function

7.12 The subcode insert function

7.13 The data encoder block

7.14 Encode control block

7.15 The EFM modulator

7.16 The EFM clock generator

7.17 The Wobble processor

8 LIMITING VALUES

9 OPERATING CHARACTERISTICS

9.1 ADC and AGC parameters

10 APPLICATION INFORMATION

10.1 Write startcontrol of encoder in CD-ROM mode

10.2 Write start control of encoder in Audio mode

10.3 Start-up of encode in flow-control operation

10.4 Start-up of encoder in synchronous stream

mode

10.5 Operating CDR60 in CAV mode, flow control

on input stream

10.6 Operating in CLV Mode, Flow Control on Input

Stream

10.7 Operating in CLV Mode, Synchronous Stream

Operation

11 PACKAGE OUTLINE

12 SOLDERING

12.1 Introduction to soldering surface mount

packages

12.2 Reflow soldering

12.3 Wave soldering

12.4 Manual soldering

12.5 Suitability of surface mount IC packages for

wave and reflow soldering methods

13 DEFINITIONS

14 LIFE SUPPORT APPLICATIONS

15 PURCHASE OF PHILIPS I2C COMPONENTS

2000 Mar 21 2

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

1 FEATURES

• Very high speed Compact Disc (CD) compatible

decoding and encoding device

• On-chip Analog-to-Digital Converter (ADC) and

Automatic Gain Control (AGC) for HF data capture

• Eight-to-Fourteen Modulation (EFM)

• Advanced motor control loop to allow CAV, CLV and

pseudo-CLV playback

• Integrated FIFO for de-coupling of mechanism speed

and application speed

• Versatile output interface allowing different I2S-bus and

Electronic Industries Association of Japan (EIAJ)

formats

• Device is fully compatible with ELM, PLUM and Sanyo

CD-ROM block decoders

• Quad-pass CIRC correction for CD mode

(C1-C2-C1-C2)

• Subcode/header processing for CD format

• Frequency multiplier allows use of a 8 MHz crystal.

The bit detector recovers the individual bits from the

incoming signal, correcting asymmetry, performing noise

filtering and equalisation, and recovering the channel bit

clock using a digital PLL. The demodulator converts the

EFM bits to byte-wide data symbols, before passing them

onto the decoder for subcode extraction, de-interleaving

and error correction. The decoded data is then made

available via the multi-function serial output interface.

The encode datapath takes data symbols from the block

encoder/decoder via the serial data and subcode input

functions, encoding them via the encoder block. The

encoded data stream is passed to the EFM modulator,

which generates the required EFM signal, output as a

digital bitstream. Theencode process iscontrolled viathe

Wobble processor, encode control and EFM clock

generator functions.

2 GENERAL DESCRIPTION

As well as these two data processing sections, three

further blocks support overall device operation. The

CDR60 is a channel encoder/decoder for

CD/CD-R/CD-RW/CD Audio Recorder systems. It

incorporates all logic and RAM required for the complete

encoding and decoding processes.

There aretwo main datapathsthrough the CDR60 device.

system clockgenerator provides all digitalclocks required

by the CDR60. The motor servo allows the CDR60 to

control the spindle motor and is controlled by the

microprocessor interface. This interface can be accessed

either via a parallel (80C51) or a serial (I2C-bus) interface.

The decode datapath captures the incoming EFM data

stream via the HF ADC and AGC functions.

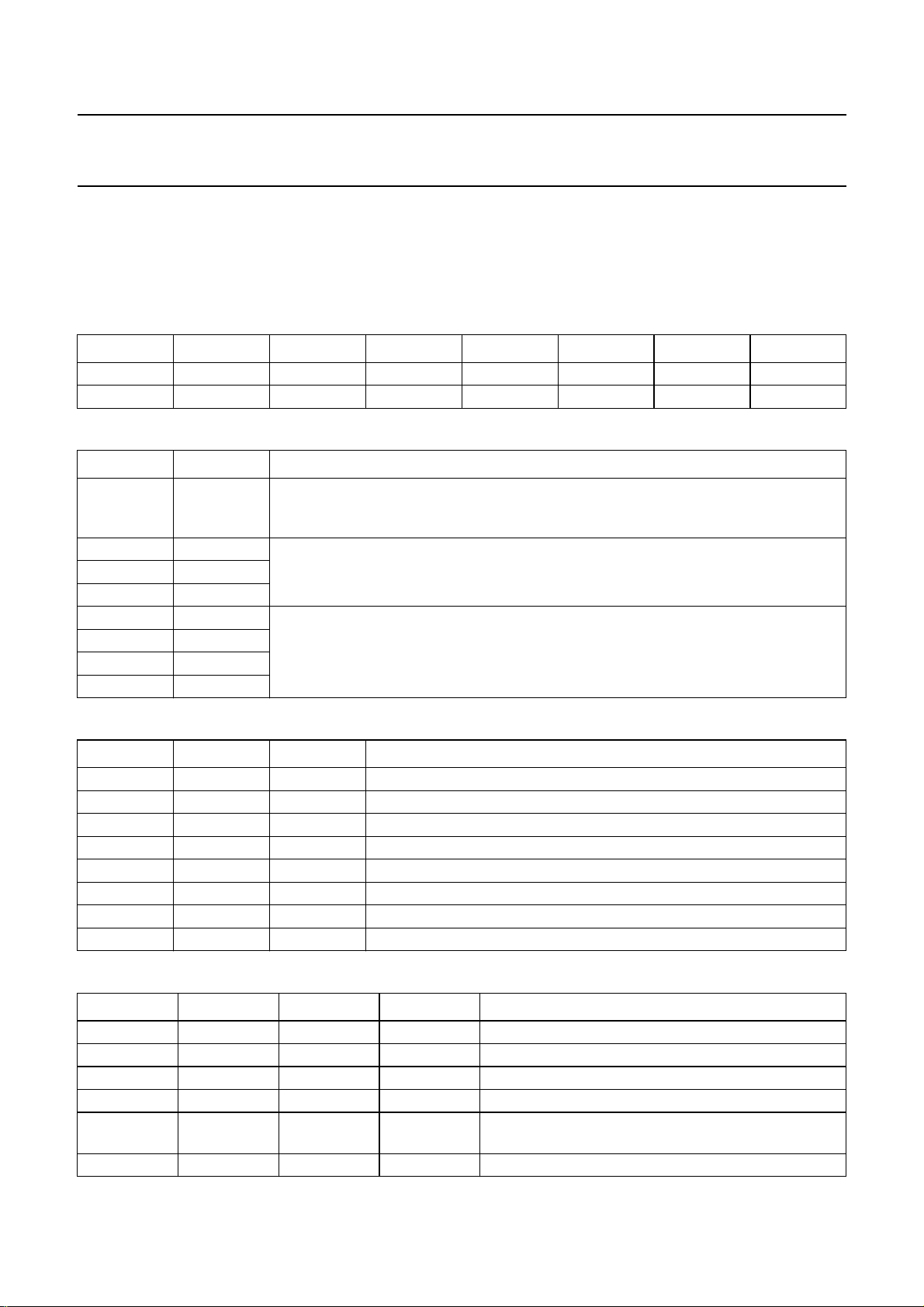

3 QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

V

V

I

f

T

T

DDD

DDA

DDE

DD

xtal

amb

stg

supply voltage (core and pad ring) 3.0 3.3 3.6 V

supply voltage (analog) 3.0 3.3 3.6 V

supply voltage (output drivers) 3.0 3.3 3.6 V

supply current − 200 − mA

crystal frequency 8 8.4672 33 MHz

operating ambient temperature 0 − 70 °C

storage temperature −55 − +125 °C

4 ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

SAA7392HL LQFP80 plastic low profile quad flat package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

2000 Mar 21 3

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

d

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsingthrough the pdf inthe Acrobat reader. white to force landscape pages to be ...

2000 Mar 21 4

book, full pagewidth

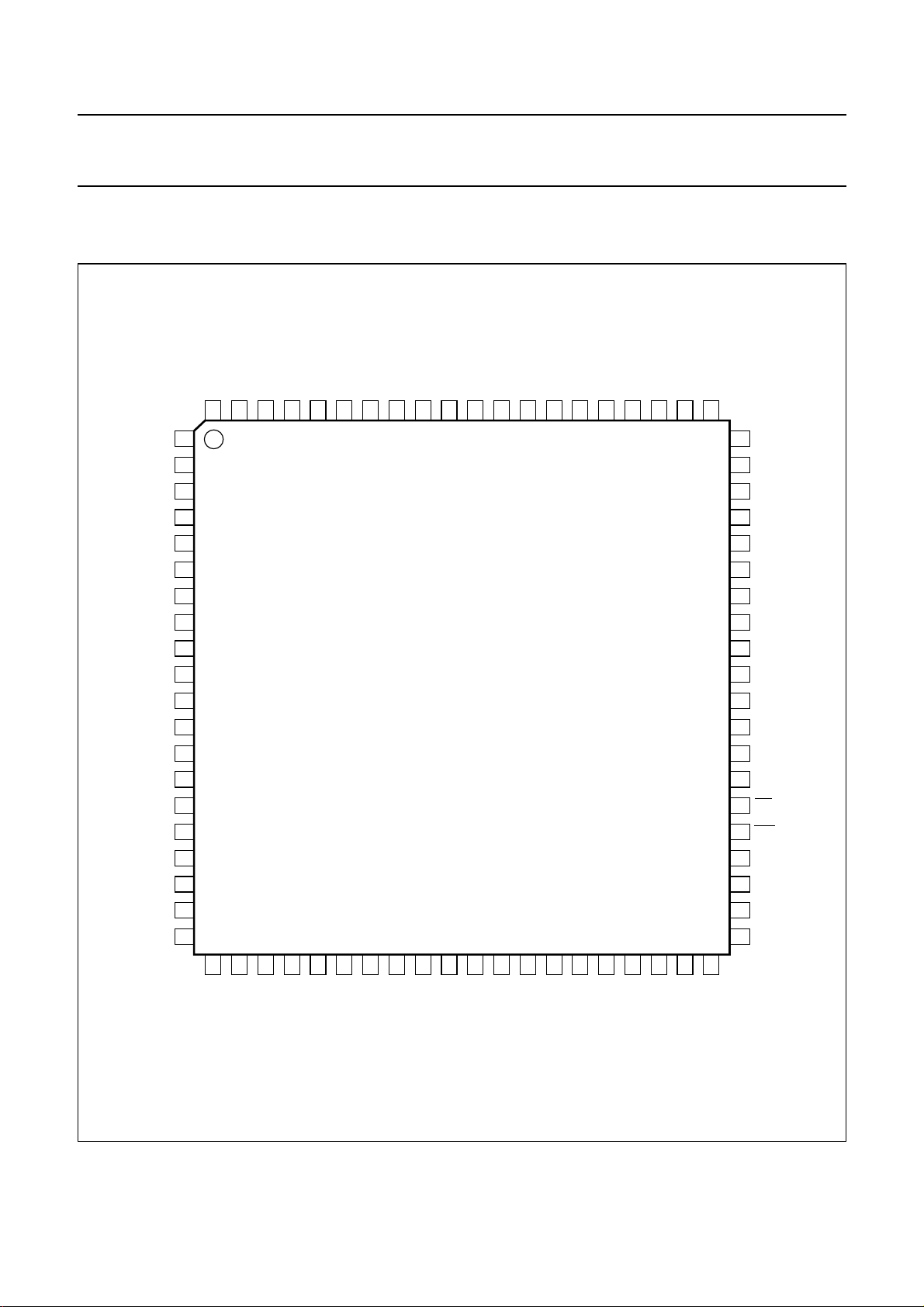

5 BLOCK DIAGRAM

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

IREF

VREF

OTD

T1

T2

MOTO2/T3

MOTO1

V

SSA1

V

DDA1

V

DDA2

V

SSA2

V

DDD

V

SSD

V

DDE

8

IREF

7

GENERATOR

23

70

69

73

74

4

5

15

16

30, 49, 53, 76

19, 31, 43, 48,

52, 62, 71, 75

20, 44, 63, 72

WREFLO

HF DATA

CAPTURE

ATIPSYC

26

6

W441

25

WREFMID

WREFHI

3

1

PROCESSOR

WIN

2

WOBBLE

MOTOR/TACHO

INTERFACE

SAA7392

BIT DETECTOR DE-MODULATOR

SYSTEM CLOCK

GENERATOR

XEFM

78

EFM CLOCK

GENERATOR

RESET

EFMDATA

MODULATOR

TEST

CONTROL

PANIC

LASERON

79

EFM

ERROR CORRECTOR

AND

MEMORY PROCESSOR

77

ENCODE

CONTROL

SUB-CPU INTERFACE

27

SUBCODE

INSERT

SERIAL IN

SERIAL OUT

65

SUB

67

SFSY

66

RCK

64

DATAI

60

WCLK

61

BCLK

57

SYNC

55

V4

56

EBUOUT

59

DATAO

54

STOPCK

58

FLAG

51

PCAin

11

HREFLO

HREFMID

14

HREFHI

10

13

AGCREF

HIN

12

MEAS1

80

29

CL1

MUXSWI

24

XTLO

21

22

XTLI

28

PORE

Fig.1 Block diagram.

TEST2

18

17

TEST1

CFLG

35

to

42

DA7

to

DA0

47

ALE

68

RDi

45

46

WRi

CSi

32

50

SCL

SDA

34

33

MGR791

INT

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

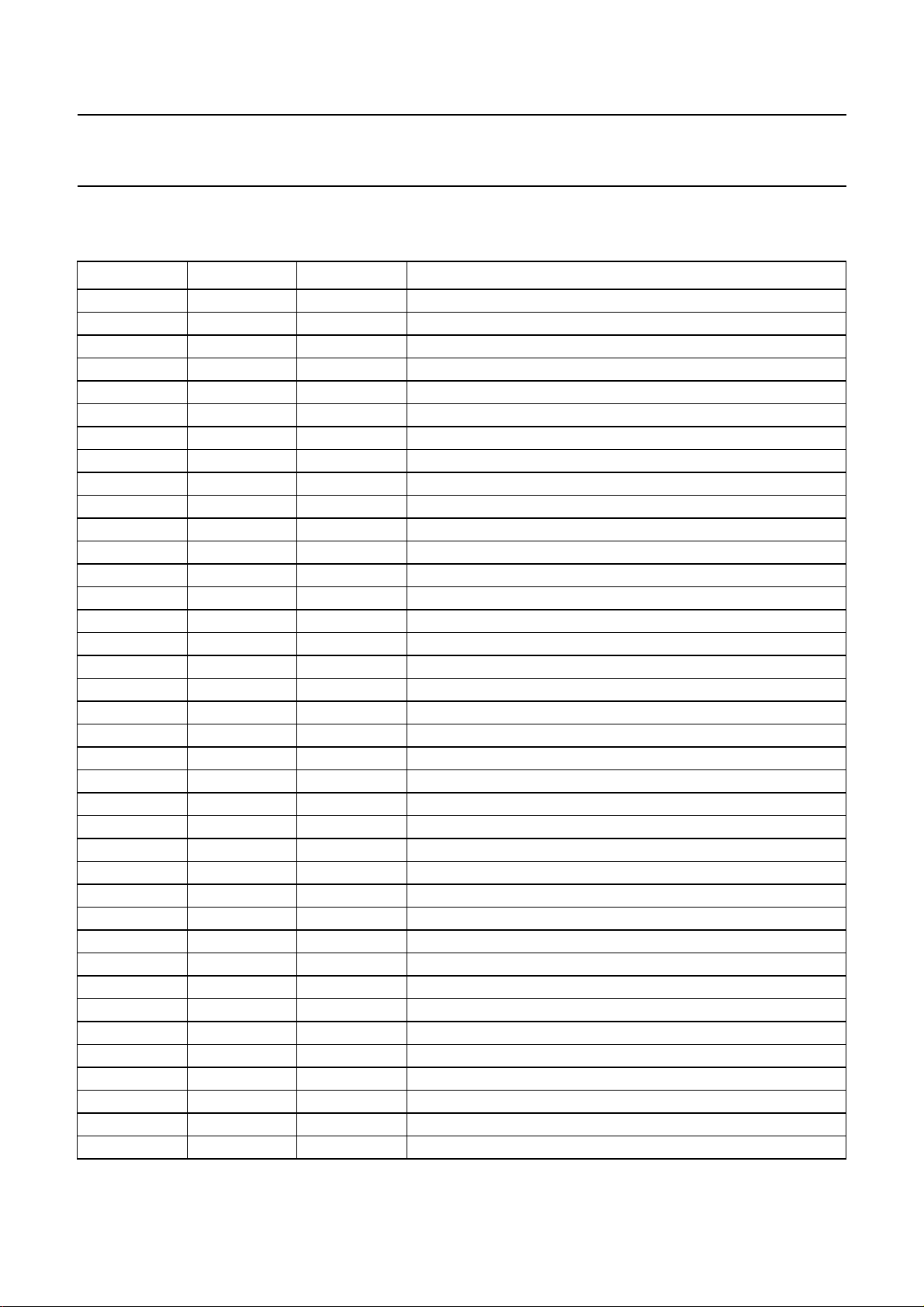

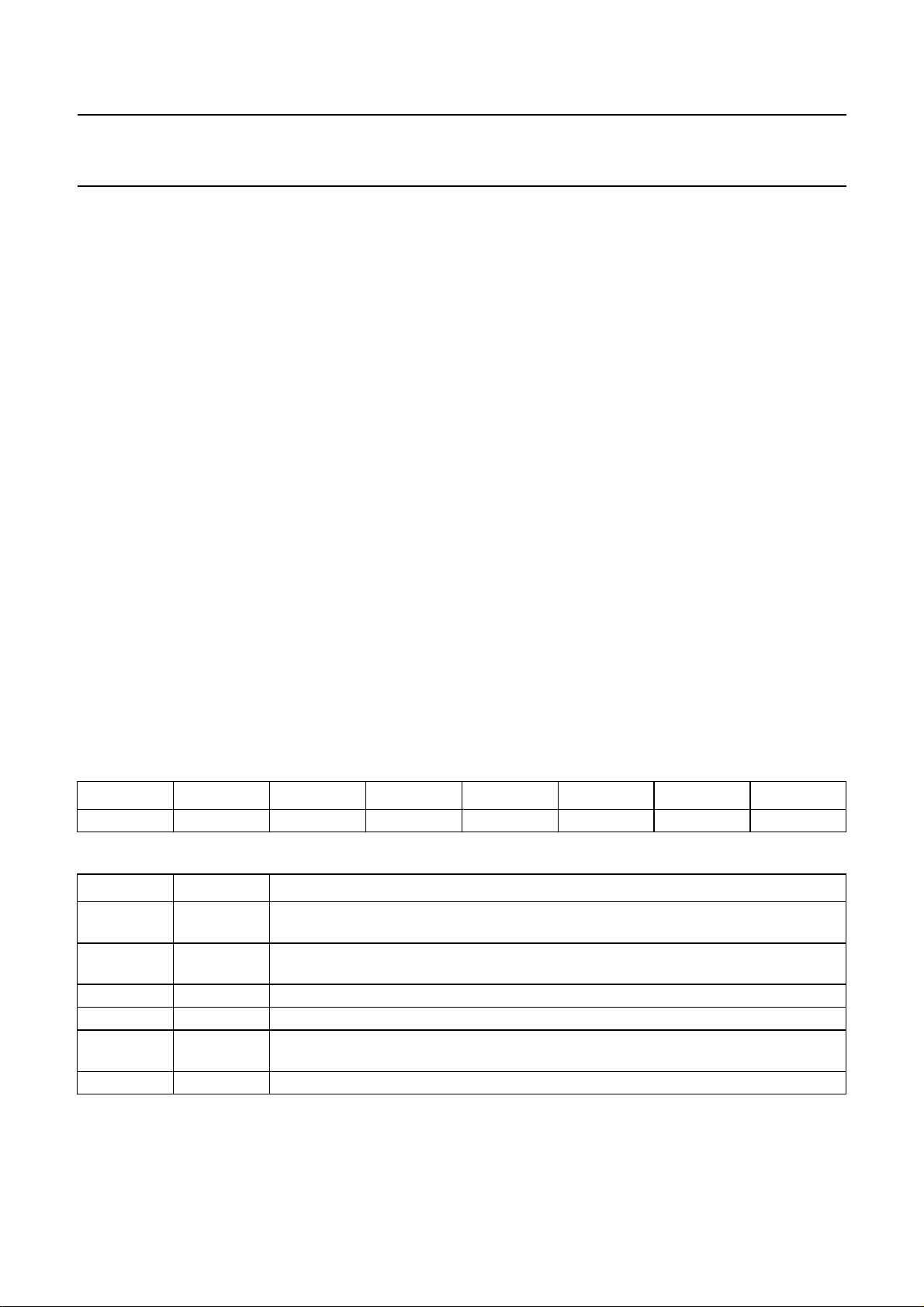

6 PINNING INFORMATION

6.1 Pinning

handbook, full pagewidth

WREFLO

WREFHI

WREFMID

V

SSA1

V

DDA1

WIN

VREF

IREF

n.c.

HREFHI

HREFLO

AGCREF

HIN

HREFMID

V

DDA2

V

SSA2

TEST1

TEST2

V

SSD

V

DDE

MEAS1

EFMDATA

XEFM

80

79

78

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

DDDVSSD

LASERON

V

77

76

75

MOTO1

74

MOTO2/T3

73

DDEVSSD

V

72

71

SAA7392

T1

70

T2

69

CFLG

68

SFSY

67

RCK

66

SUB

65

DATAI

64

DDEVSSD

V

63

62

BCLK

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

WCLK

DATAO

FLAG

SYNC

EBUOUT

V4

STOPCK

V

DDD

V

SSD

PCAin

CSi

V

DDD

V

SSD

ALE

RDi

WRi

V

DDE

V

SSD

DA0

DA1

21

22

23

24

25

26

27

28

29

30

XTLI

XTLO

OTD

W441

MUXSWI

PANIC

ATIPSYC

PORE

CL1

V

Fig.2 Pin configuration.

2000 Mar 21 5

DDD

31

SSD

V

32

SCL

33

SDA

34

INT

35

DA7

36

DA6

37

DA5

38

DA4

39

DA3

40

MGR792

DA2

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

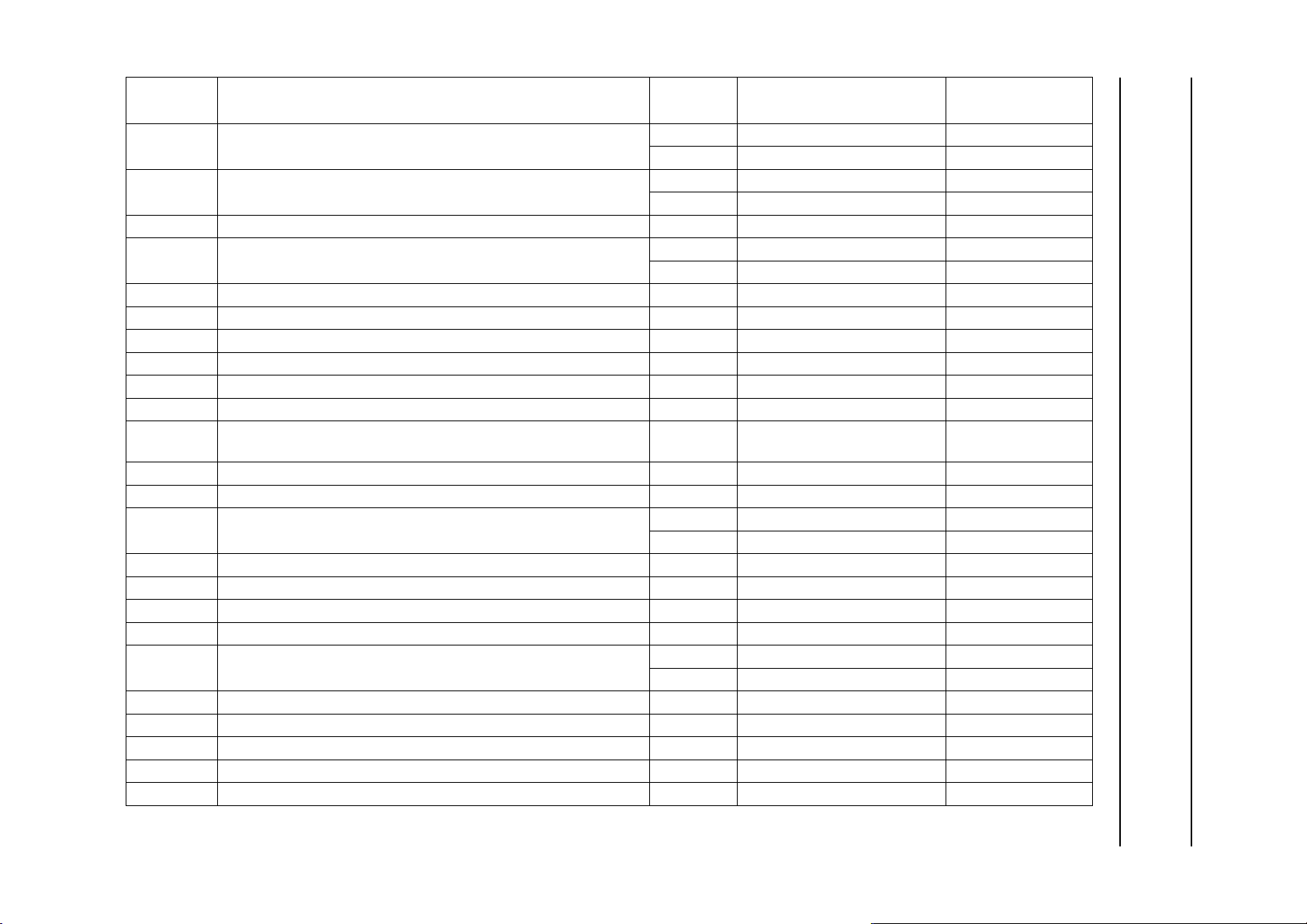

6.2 Pin description Table 1 LQFP80 package; note 1

SYMBOL PIN TYPE DESCRIPTION

WREFLO 1 O wobble ADC analog reference voltage

WREFHI 2 O wobble ADC analog reference voltage

WREFMID 3 O wobble ADC analog reference voltage

V

SSA1

V

DDA1

WIN 6 I wobble analog input

VREF 7 O analog voltage reference

IREF 8 O analog current reference

n.c. 9 − not connected

HREFHI 10 O HFADC analog reference voltage

HREFLO 11 O HF ADC analog reference voltage

AGCREF 12 I AGC analog reference voltage

HIN 13 I HF analog data input

HREFMID 14 O HFADC analog reference voltage

V

DDA2

V

SSA2

TEST1 17 I test input 1

TEST2 18 I test input 2

V

SSD

V

DDE

XTLI 21 I crystal oscillator input

XTLO 22 O crystal oscillator output

OTD 23 I off track detect input

MUXSWI 24 I clock multiplier enable

W441 25 O wobble 44.1 kHz clock output

ATIPSYC 26 O ATIPSync output

PANIC 27 I laser low power (LLP)

PORE 28 I power-on reset

CL1 29 O divided clock output

V

DDD

V

SSD

SCL 32 I sub-CPU clock

SDA 33 I/O bidirectional sub-CPU data

INT 34 O sub-CPU interrupt

DA7 35 I/O bidirectional sub-CPU parallel data bus

DA6 36 I/O bidirectional sub-CPU parallel data bus

DA5 37 I/O bidirectional sub-CPU parallel data bus

DA4 38 I/O bidirectional sub-CPU parallel data bus

4 supply analog ground

5 supply 3 V analog supply voltage 1; note 2

15 supply 3 V analog supply voltage 2; note 2

16 supply analog ground

19, 43, 62, 71 supply output driver ground

20 supply output driver 3 V supply voltage

30, 49, 53, 76 supply core and pad ring 3 V supply voltage; note 2

31, 48, 52, 75 supply core and pad ring ground

2000 Mar 21 6

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

SYMBOL PIN TYPE DESCRIPTION

DA3 39 I/O bidirectional sub-CPU parallel data bus

DA2 40 I/O bidirectional sub-CPU parallel data bus

DA1 41 I/O bidirectional sub-CPU parallel data bus

DA0 42 I/O bidirectional sub-CPU parallel data bus

V

DDE

WRi 45 I sub-CPU write enable; active LOW

RDi 46 I sub-CPU read enable; active LOW

ALE 47 I sub-CPU address latch enable

CSi 50 I sub-CPU chip select

PCAin 51 I PCA input

STOPCK 54 O stop clock output

V4 55 O serial subcode output

EBUOUT 56 O digital output

SYNC 57 O I

FLAG 58 O I

DATAO 59 O I

WCLK 60 I/O bidirectional I

BCLK 61 I/O bidirectional I

V

DDE

DATAI 64 I I

SUB 65 I EIAJ subcode data

RCK 66 O EIAJ subcode clock

SFSY 67 I EIAJ subcode sync

CFLG 68 O correction statistics; open-drain

T2 69 I tacho control input 2

T1 70 I tacho control input 1

V

DDE

MOTO2/T3 73 I/O motor output 2/tacho input 3

MOTO1 74 O motor control output 1

LASERON 77 O laser write control

XEFM 78 O EFM clock output

EFMDATA 79 O EFM data output

MEAS1 80 O front end telemetry; open-drain

44 supply output driver 3 V supply voltage

2

S sector sync output

2

S correction flag

2

S data output

2

S word clock

2

S bit clock

63 supply output driver 3 V supply voltage

2

S data input

72 supply output driver 3 V supply voltage

Notes

1. No signal may be applied to this device when it is not powered.

2. The analog and digital supply pins (V

DDA

and V

) must be connected to the same external supply.

DDD

2000 Mar 21 7

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7 FUNCTIONAL DESCRIPTION

7.1 Microprocessor interfaces

The SAA7392 is programmed via two independent

microprocessor interfaces:

• Serial I2C-bus

– SDA=I2C-bus data

– SCL = I2C-bus clock

–I2C-bus write address = 3EH

–I2C-bus read address = 3FH.

• Parallel 80C51 compatible

– DA(7:0) = address/data bus

– ALE = address latch enable; latches the address

information on the bus

– WRi = active LOW write signal; write to SAA7392

– RDi = active LOW read signal; read from SAA7392

– CSi = chip select signal; gates the RDi and WRi

signals.

7.1.1 S

ERIAL I

C-BUS INTERFACE

2

Data is transferred over the interface in single bytes, via

write data or read data commands.

The sequence for a write data command is as follows:

1. Send START condition

2. Send address 3EH (write)

3. Write register address byte

4. Write data byte

5. Send STOP condition.

The sequence for a read data command is as follows:

1. Send START condition

2. Send address 3EH (write)

3. Write status register address byte

4. Send STOP condition

5. Send address 3FH (read)

6. Read data byte

7. Send STOP condition.

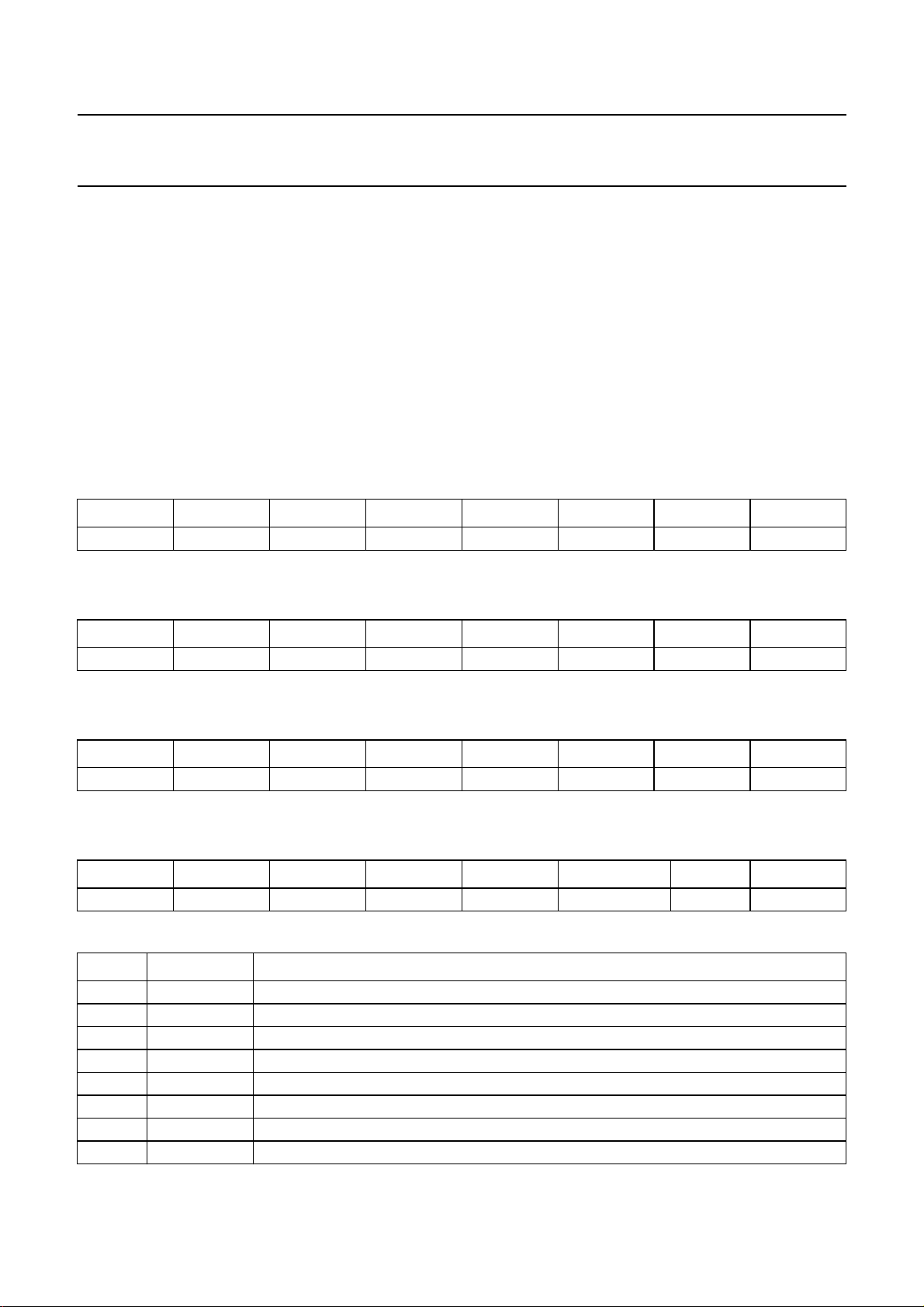

7.1.2 P

ARALLEL INTERFACE

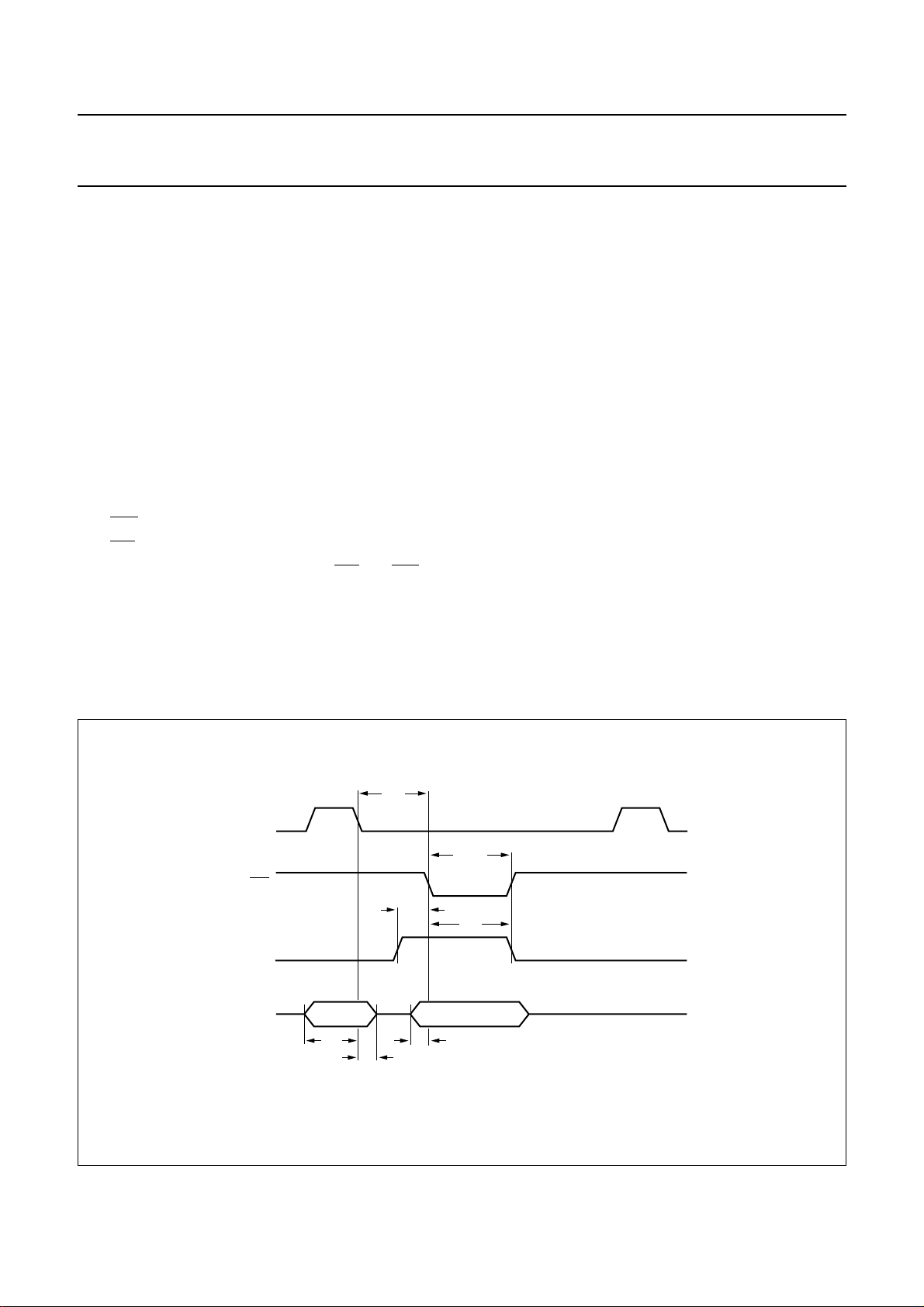

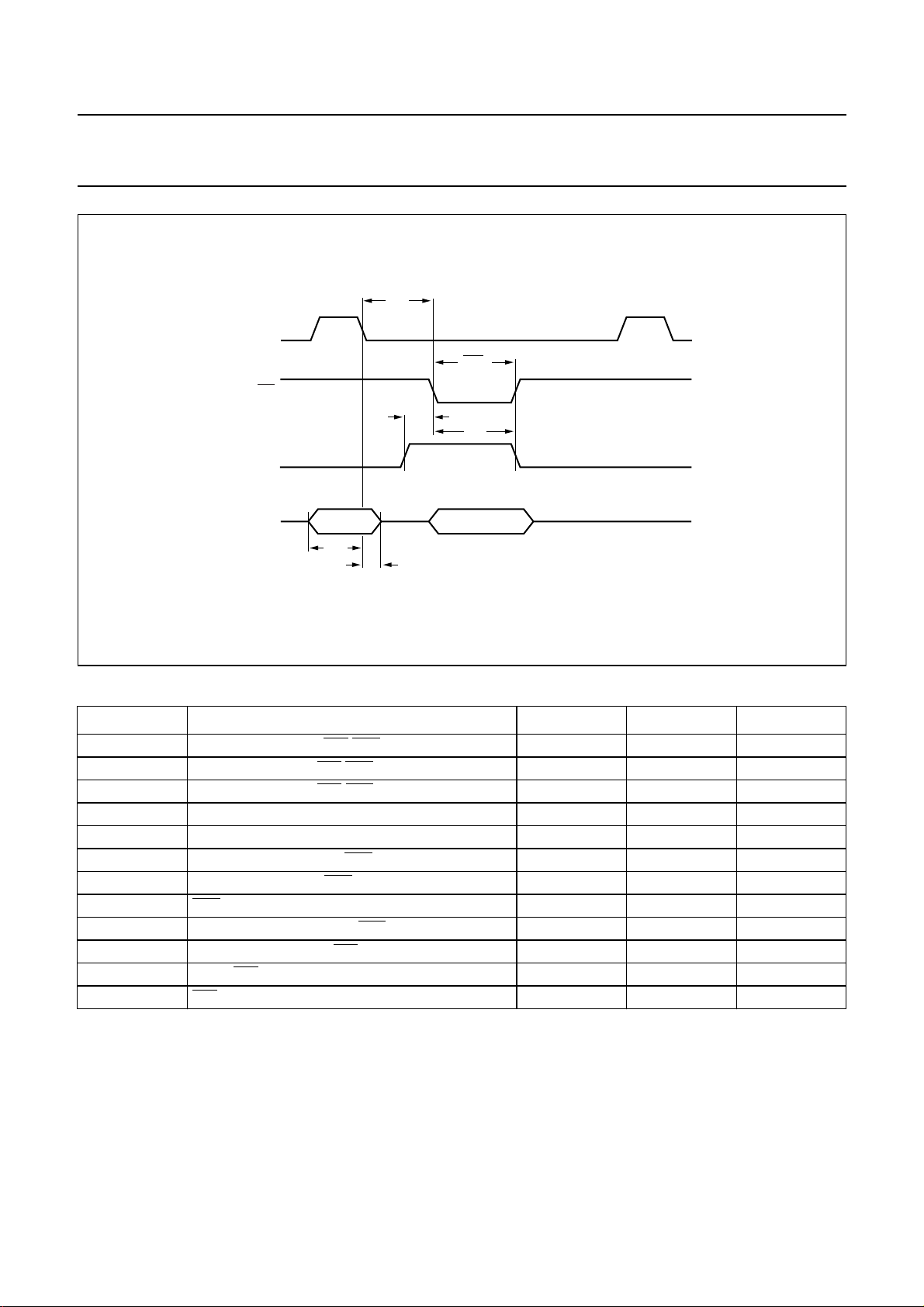

The parallelinterface hasa multiplexed address/databus.

Information can be written to or read from the SAA7392

using the protocols shown inFigs 3 and 4; specific timings

are shownin Table 2. Notethat only thelower six address

bits are decoded; so writing to address 40H would have

the same effect as writing to address 00H.

t

handbook, full pagewidth

ALE

WRi

CSi

DA0 to DA7

address (0:7)

IN

t

su1

d1

t

d2

data (0:7)

t

t

h2

su2

Fig.3 Microprocessor write protocol.

2000 Mar 21 8

t

WRiL

t

IN

h1

MGR793

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

t

handbook, full pagewidth

ALE

RDi

CSi

d1

RDi

L

t

d2

t

h1

DA0 to DA7

address (0:7)

IN

t

su1

t

h2

data (0:7)

OUT

Fig.4 Microprocessor read protocol.

Table 2 Parallel interface timing

SYMBOL DESCRIPTION MIN.

t

d1

t

d2

t

h1

t

su1

t

h2

t

su2

t

h3

t

WRiL

t

h4

t

d3

t

d4

t

RDiL

Delay ALE falling to RDi/WRi falling. 17 − ns

Delay CSi rising to RDi/WRi falling. 17 − ns

CSi hold time after RDi/WRi falling. 2T

Address setup time before ALE falling. 17 − ns

Address hold time after ALE falling. 17 − ns

Data setup time before WRi falling. 0 − ns

Data hold time after WRi falling. 2T

WRi LOW time. 1T

ALE LOW hold time after WRi LOW. 3T

Delay data valid after RDi LOW. − 3T

Delay RDi HIGH to data out high-impedance. − 17 ns

RDi LOW time. 3T

MGR794

(1)

+17 − ns

clk

+17 − ns

clk

+17 − ns

clk

+17 − ns

clk

+ 128 − ns

clk

(1)

MAX.

+17 ns

clk

UNIT

Note

1. T

is the system clock period.

clk

2000 Mar 21 9

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsingthrough the pdf inthe Acrobat reader. white to force landscape pages to be ...

2000 Mar 21 10

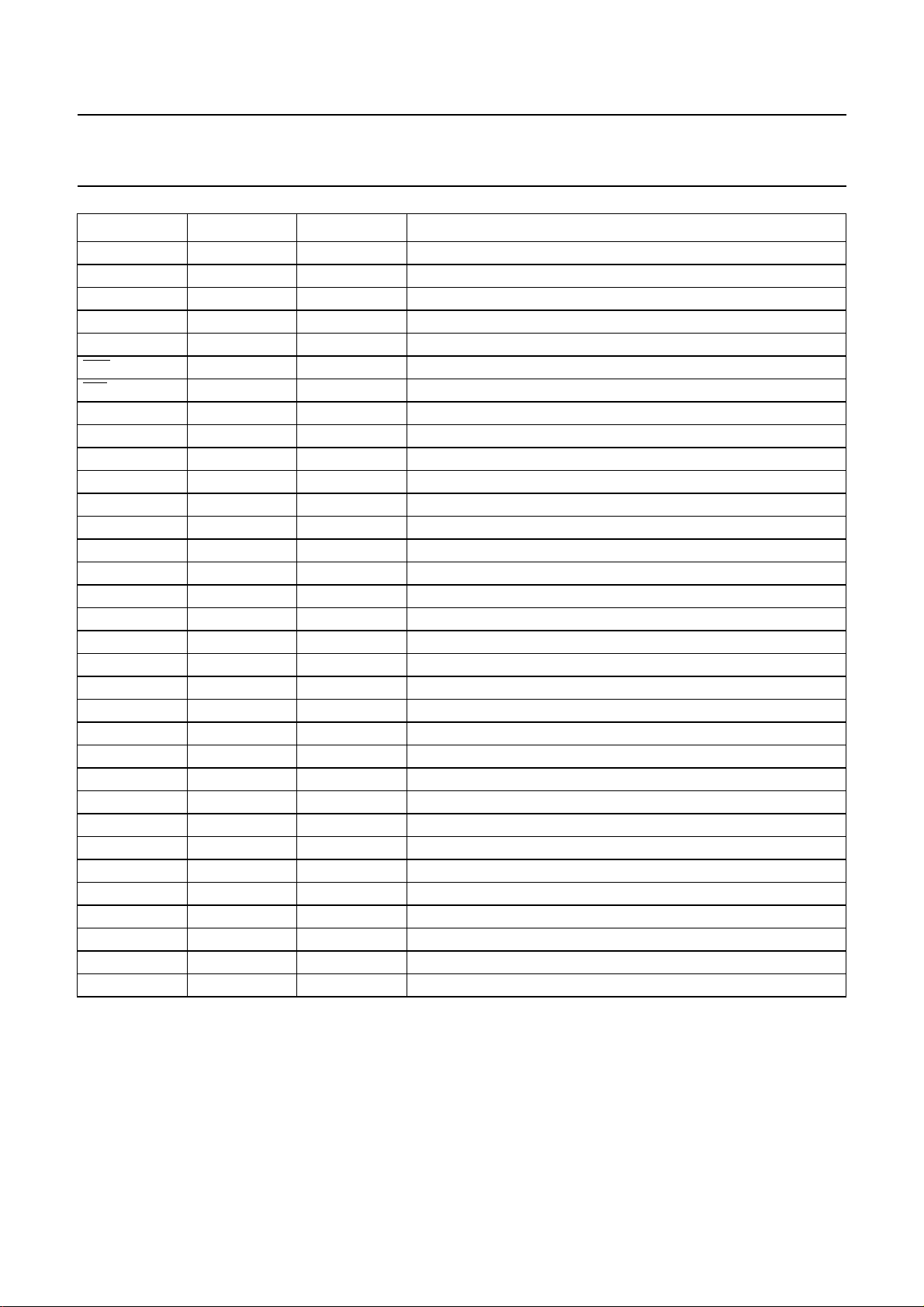

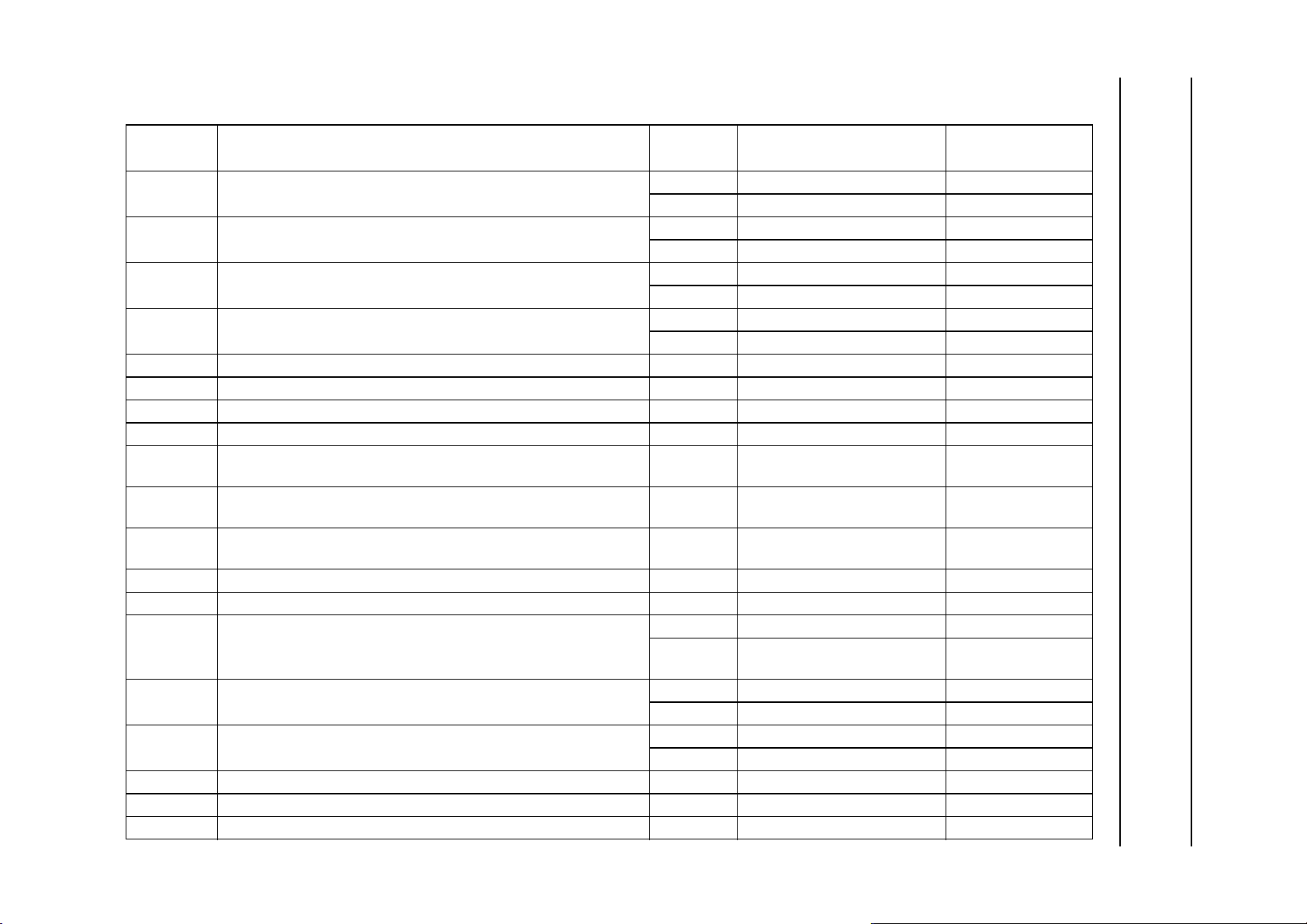

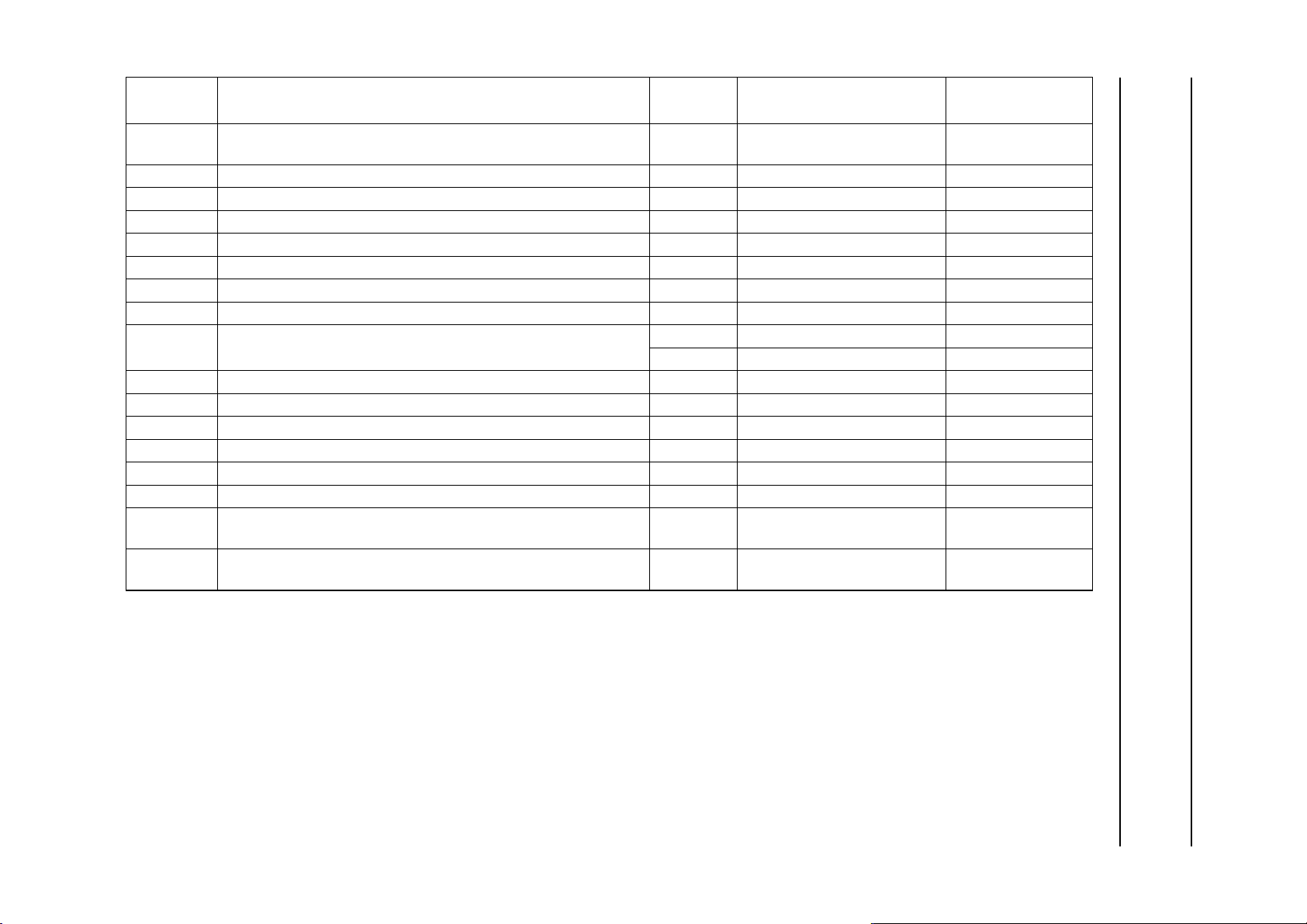

7.2 Register map Table 3 Register map

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

ADDRESS

(HEX)

00 PLL Lock Select Register (PLLLock) Write PLL lock select bit detector

01 PLL Bandwidth Select Register (PLLSet) Write PLL bandwidth select bit detector

02 PLL Frequency Preset Register (PLLFreq) Write PLL frequency preset bit detector

03 PLL Equalizer Preset Register (PLLEqu) Write PLL equalizer preset bit detector

04 PLL Lock Aid2 Preset Register (PLLFMeas) Write PLL lock aid 2 preset bit detector

05 I2S Output Register 1 (Output1) Write I2S output 1 serial out

06 I

07 I

08 Semaphore Register 1 (Sema1) Write/Read Inter-microprocessor

09 Semaphore Register 2 (Sema2) Write/Read Inter-microprocessor

0A Semaphore Register 3 (Sema3) Write/Read Inter-microprocessor

0B Interrupt Enable Register (IntEn) Write Enable interrupts sub-CPU

0B Status Register (Status) Read Interrupt status sub-CPU

0C Motor Control Register1 (Motor1) Write Frequency set-point motor/tacho

0D Motor Mode Select Register2 (Motor2) Write Motor coefficient preset motor/tacho

0E Motor Control Register 3 (Motor3) Write Motor integrator preset motor/tacho

0F Motor Control Register 4 (Motor4) Write Motor control motor/tacho

10 Motor Control Register 5 (Motor5) Read/Write Motor integrator value motor/tacho

11 Motor Control Register 6 (Motor6) Read/Write Motor integrator value motor/tacho

2

S Output Register 2 (Output2) Write I2S output 2 serial out

2

S Output Register 3 (Output3) Write I2S output 3 serial out

REGISTER NAME TYPE FUNCTION

Read 8-bit PLL frequency bit detector

Read 8-bit asymmetry signal bit detector

Read 8-bit jitter signal bit detector

Read Observe internal lock flags bit detector

communication

communication

communication

Read 8-bit slicer compensation

value

Read Opening of eye pattern bit detector

Read Read back of motor frequency motor/tacho

sub-CPU

sub-CPU

sub-CPU

bit detector

BLOCK

RESPONSIBLE

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsingthrough the pdf inthe Acrobat reader. white to force landscape pages to be ...

2000 Mar 21 11

ADDRESS

(HEX)

12 Clock Preset Register (ClockPre) Write Clock control clock generator

13 Decoder Mode Select Register (DecoMode) Write Decoder mode select encoder/decoder

14 Subcode Read End Register (SubReadEnd) Read Subcode data read finished encoder/decoder

15 Analog Settings Register 1 (AnaSet1) Write Analog control analog

16 Viterbi Detector Settings Register (VitSet) Write Viterbi detector control bit detector

17 Tacho Gain Setting Register (Tacho1) Write Tacho gain setting motor/tacho

18 Tacho Trip Setting Register (Tacho2) Write Tacho trip setting motor/tacho

19 Tacho Control Register (Tacho3) Write Tacho control settings motor/tacho

1B Soft Reset Register (SoftReset) Write Sub-block reset sub-CPU

1D Motor Control Register7 (Motor7) Write Control coefficients select motor/tacho

1E Input Configuration Register (InputConfig) Write EBU clock frequency and

20 Status Register 2 (Status2) Read/Write Interrupt status sub-CPU

21 Interrupt Enable Register 2 (IntEn2) Write Enable interrupts sub-CPU

22 Subcode Preset Count Register (SubPresetCount) Write Preset count field subcode insert

23 Subcode Configuration Register 1 (SubConfig1) Write Subcode control subcode insert

24 Subcode Configuration Register 2 (SubConfig2) Read/Write Subcode control subcode insert

25 Subcode Start Data Register (SubStartData) Write Subcode control subcode insert

26 Subcode Data Register (SubData) Read/Write Subcode data subcode insert

27 Wobble Configuration Register 1 (WobbleConfig1) Integrator and loop bandwidth Wobble processor

28 Wobble Configuration Register 2 (WobbleConfig2) Write Wobble PLL control Wobble processor

29 ATIP Status Register (ATIPStatus) Read ATIP status Wobble processor

2A Wobble Frequency Register 1 (WobbleFreq1) Read/Write 8 MSBs of PLL frequency Wobble processor

2B Wobble Frequency Register 2 (WobbleFreq2) Read/Write 8 LSBs of PLL frequency Wobble processor

2C ATIP Data Register (ATIPData) Read ATIP data Wobble processor

REGISTER NAME TYPE FUNCTION

Read Status of Q-channel subcode encoder/decoder

Read Q-channel subcode data encoder/decoder

Read C1 frames in FIFO + offset encoder/decoder

input format

Read Current count field subcode insert

Window width ATIP syncs Wobble processor

BLOCK

RESPONSIBLE

serial input

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsingthrough the pdf inthe Acrobat reader. white to force landscape pages to be ...

2000 Mar 21 12

ADDRESS

(HEX)

2D ATIP Data End Register (ATIPDataEnd) Read Least significant byte ATIP

2E Wobble Peak Status Register (WobbleStatus) Read Peak value of wobble signal Wobble processor

30 Encode WriteOn Control Register (EncodeWContr) Read/Write Laser and data flow control encode control

31 Encode Start Offset Register (EncodeStartOffset) Write Start WriteOn flags delay encode control

32 Encode Stop Offset Register (EncodeStopOffset) Write Stop WriteOn flags delay encode control

33 Encode Offset Register (EncodeXOffset) Write 10-bit value for Xoffset encode control

34 EFM Clock Configuration Register 1 (EFMClockConf1) Write EFM clock control EFM clock generator

35 EFM Clock Configuration Register 2 (EFMClockConf2) Write EFM clock control EFM clock generator

36 EFM Clock Configuration Register 3 (EFMClockConf3) Write EFM clock control EFM clock generator

37 EFM PLL Frequency Register (EFMPLLFreq) Read EFM PLL frequency EFM clock generator

37 EFM Clock Configuration Register 4 (EFMClockConf4) Write EFM clock control EFM clock generator

38 ATIP Error Register (ATER) Read Counter for ATIP CRC errors sub-CPU

39 C1 Block Error Register (C1BLER) Read Counter for C1 errors sub-CPU

3A C2 Block Error Register (C2BLER) Read Counter for C2 errors sub-CPU

3C EFM Preset Count Register (EFMPresetCount) Write EFM frame position for output EFM modulator

3D EFM Modulator Configuration Register (EFMModConfig) Write XEFM control and output data

3E EFM Modulator Configuration Register 2 (EFMModConfig2) Write XEFM control and output data

REGISTER NAME TYPE FUNCTION

data

Read Integrator value EFM clock generator

format

format

BLOCK

RESPONSIBLE

Wobble processor

EFM modulator

EFM modulator

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7.2.1 INTERRUPT PIN

The interrupt pin (INT) is the AND-OR-INVERT of the Status and Interrupt Enable Registers, i.e. INT will become active

when corresponding bits are set at the same time in the Status and Interrupt Enable Registers.

7.2.2 THE SEMAPHORE REGISTERS (SEMA1, SEMA2 AND SEMA3)

The Semaphore Registers are intended for inter-microprocessor communications. For example, microcontroller 1 can

writedata tomicrocontroller 2 viaSema1 andmicrocontroller 2 can writedata tomicrocontroller 1 viaSema2. TheStatus

Register ofthe SAA7392offers a mechanismso that both microcontrollers cansee when newdata hasbeen written and

whenit hasbeen readby lookingat thecontents ofthe Semaphore Registers. Version M3of theCDR60 canbe identified

by writingand reading register Sema3. In version M3,bit 1 of Sema3is always read as logic 0, whereas inother CDR60

versions this bit reads the same value as what was written to it before.

7.2.2.1 Semaphore Register 1 (Sema1)

Table 4 Semaphore Register 1 (address 08H) - READ/WRITE

76543210

Sema1.7 Sema1.6 Sema1.5 Sema1.4 Sema1.3 Sema1.2 Sema1.1 Sema1.0

7.2.2.2 Semaphore Register 2 (Sema2)

Table 5 Semaphore Register 2 (address 09H) - READ/WRITE

76543210

Sema2.7 Sema2.6 Sema2.5 Sema2.4 Sema2.3 Sema2.2 Sema2.1 Sema2.0

7.2.2.3 Semaphore Register 3 (Sema3)

Table 6 Semaphore Register 3 (address 0AH) - READ/WRITE

76543210

Sema3.7 Sema3.6 Sema3.5 Sema3.4 Sema3.3 Sema3.2 Sema3.1 Sema3.0

7.2.3 S

Table 7 Status Register (address 0BH) - READ

Table 8 Description of Status bits

TATUS REGISTER (STATUS)

76543 210

Sema1 Sema2 Sema3 LockIn HeaderVal MotorOverflow FIFOOv −

BIT SYMBOL DESCRIPTION

7 Sema1 If Sema1 = 1, change in register Sema1 has been detected. Reset if register Sema1 read.

6 Sema2 If Sema2 = 1, change in register Sema2 has been detected. Reset if register Sema2 read.

5 Sema3 If Sema3 = 1, change in register Sema3 has been detected. Reset if register Sema3 read.

4 LockIn If LockIn = 1, then channel data PLL in lock (not latched).

3 HeaderVal HeaderVal is set when new header/subcode is available; reset on reading SubReadEnd.

2 MotorOverflow If MotorOverflow = 1, then a motor overflow is occurring (not latched).

1 FIFOOv If FIFOOv = 1, then the FIFO has overflowed.

0 − This bit is reserved.

2000 Mar 21 13

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7.2.4 INTERRUPT ENABLE REGISTER (INTEN)

Table 9 Interrupt Enable Register (address 0BH) - WRITE

76543 2 10

Sema1En Sema2En Sema3En LockInEn HeaderValen MotorOverflowEn FIFOOvEn −

Table 10 Description of IntEn bits

BIT SYMBOL DESCRIPTION

7 Sema1En If Sema1En = 1, then Semaphore Register 1 interrupt is enabled.

6 Sema2En If Sema2En = 1, then Semaphore Register 2 interrupt is enabled.

5 Sema3En If Sema3En = 1, then Semaphore Register 3 interrupt is enabled.

4 LockInEn If LockinEn = 1, then channel data PLL in lock interrupt is enabled.

3 HeaderValEn If HeaderValEn = 1, then new header/subcode available interrupt is enabled.

2 MotorOverflowEn If MotorOverflowEn = 1, then motor overflow interrupt is enabled.

1 FIFOOvEn If FIFOOvEn = 1, then FIFO overflow interrupt is enabled.

0 − This bit is reserved.

7.2.5 S

Table 11 Status Register 2 (address 20H) - READ/WRITE

BankSwitch SyncError DataNotValid QSync ATIPSync LaserOn LaserOff XErrorLarge

Table 12 Description of Status2 bits

BIT SYMBOL DESCRIPTION

TATUS REGISTER 2(STATUS2)

76 543210

7 BankSwitch When set a ‘Bank switch’in the subcode insert blockhas occurred; reset when a logic 1

is written to this bit.

6 SyncError When set synchronisation with PLUM on subcode transfer has failed; reset when a

logic 1 is written to this bit.

5 DataNotValid When set an under-run on subcode transfer with PLUM has occurred; reset when a

logic 1 is written to this bit.

4 QSync When set a Q-channel subcode sync has been written to disc; reset when a logic 1 is

written to this bit.

3 ATIPSync When set sync has been found in the ATIP channel; reset when a logic 1 is written to

this bit.

2 LaserOn When set a rising edge of the internal LaserOn signal has occurred; reset when a

logic 1 is written to this bit.

1 LaserOff When set a falling edge of the internal LaserOn signal has occurred; reset when a

logic 1 is written to this bit.

0 XErrorLarge Whenset the offset between QSync and ATIPSync is more than 2 EFM frames different

from the programmed value.

2000 Mar 21 14

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7.2.6 INTERRUPT ENABLE REGISTER 2(INTEN2)

Table 13 Interrupt Enable Register 2 (address 21H) - WRITE

76 543210

BankSwitchEnSyncErrorEn DataNotValidEnQSyncEn ATIPSyncEn LaserOnEn LaserOffEn XErrorLarge

En

Table 14 Description of IntEn2 bits

BIT SYMBOL DESCRIPTION

7 BankSwitchEnIf BankSwitchEn = 1, then BankSwitch interrupt is enabled.

6 SyncErrorEn If SyncErrorEn = 1, then SyncError interrupt is enabled.

5 DataNotVali

dEn

4 QSyncEn If QSyncEn = 1, then QSync interrupt is enabled.

3 ATIPSyncEn If ATIPSyncEn = 1, then ATIPSync interrupt is enabled.

2 LaserOnEn If LaserOnEn = 1, then LaserOn interrupt is enabled.

1 LaserOffEn If LaserOffEn = 1, then LaserOff interrupt is enabled.

0 XErrorLargeEnIf XerrorLarge = 1, then XErrorLarge interrupt is enabled.

If DataNotValidEn= 1, then DataNotValid interrupt is enabled.

7.2.7 S

Table 15 Soft Reset Register (address 1BH) - WRITE

Table 16 Description of SoftReset bits

OFT RESET REGISTER (SOFTRESET)

76543210

−−−−−−−SReset1

BIT SYMBOL DESCRIPTION

7to1 − These 7 bits are reserved.

0 SReset1 When set, synchronisation with PLUM on subcode transfer has failed; reset when

a logic 1 is written to this bit (Status2).

This bit is an active HIGH reset to the following blocks: Encoder/decoder, EFM

modulator, Encode control block, Serial input/output block and Encode subcode insert

block. The clock control, EFM PLL, tacho, motor interface and wobble interface remain

running.

Soft reset will reset the following registers: EFMPresetCount, EFMModulateConfig,

EFMModulateConfig2, EncodeXOffset, EncodeWriteControl, EncodeStartOffset,

EncodeStopOffset, SubPresetCount, SubConfig1, Subconfig2,SubStartData, SubData,

InputConfig, DecoMode, Output1, Output2 and Output3.

A soft reset is mandatory in the following cases:

1. After programming the BCLK clock

2. When switching from encode to decode

3. When switching from decode to encode.

2000 Mar 21 15

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

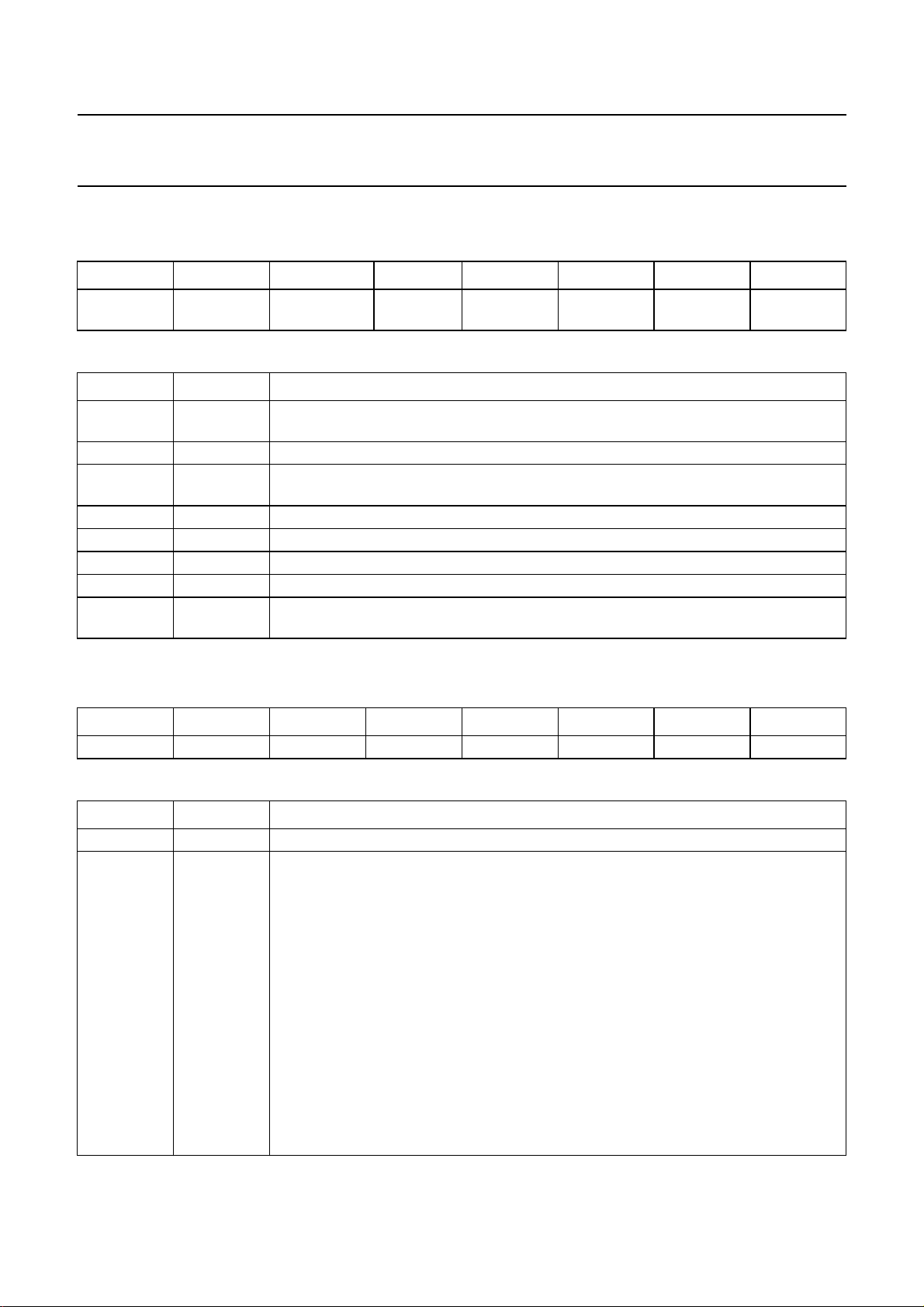

7.3 System clocks

The principleclocks used inthe SAA7392 are derived from the crystaloscillator input pinXTLI (alternatively, anexternal

clock can be connected to this pin). These clocks are the system clock (also used as the ADC clock) and the I2S output

bit clock (BCLK).

The system clock (f

) defines the maximumoperational channel rate for the device. The maximum EFM channel clock

clk

is twice the system clock, for CD it is equivalent tosystem clock/(4.3 × 106) which is approximately 11.5 × CDROM for a

25 MHz system clock.

The other clock in the system is the channel data clock, this is recovered by the front-end bit recovery PLL.

handbook, full pagewidth

crystal

oscillator

MUXSWI

XTLI

XTLO

CL1

×

(1)

CLOCK

MULTIPLIER

CL1

DIVIDER

M × XTLI

XTLI

SYSTEM

CLOCK

DIVIDER

BIT

CLOCK

DIVIDER

system clock

system clock

BCLK

MGR795

(1) M = 1 if MUXSWI is LOW; M = 8 if MUXSWI is HIGH.

Fig.5 System clock generator.

2000 Mar 21 16

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7.3.1 CLOCK PRESET REGISTER (CLOCKPRE)

Table 17 Clock Preset Register (address 12H) - WRITE

76543210

CL1Div GateBClk Div.1 Div.0 Mux2 Div2.2 Div2.1 Div2.0

Table 18 Description of ClockPre bits

BIT SYMBOL DESCRIPTION

1

⁄3f

7 CL1Div If CL1Div = 0, then CL1 output frequency is

frequency is1⁄2f

6 GateBClk If GateBClk = 0, then I

clk

.

2

S output bit clock gating is disabled. If GateBClk = 1, then I2S

output bit clock gating enabled, BCLK is output, clock is automatically stopped if FIFO

underflows (this is known as Flow control mode).

5 Div.1 These 2 bits select the system clock frequency (f

4 Div.0

should be programmed for the expected disc channel rate (e.g. 4.33 MHz for 1 × CD)

within the following constraints:

. If CL1Div = 1, then CL1 output

clk

); see Table 19. This frequency

clk

Channel rate

---------------------------------2

4 Channel rate×<<

f

clk

In this clock range, reliable bit detection is possible. All data found will be written to the

FIFO. It is the responsibility of the user to select system clock values so that the FIFO

performance is controlled.

3 Mux2 If Mux2 = 0, then N (bit clock divider pre-scaler) = 1. If Mux2 = 1, then N = M.

2 to 0 Div2<2:0> These 3 bits select the BCLK frequency (f

); see Table 20. It is the responsibility of

BCLK

the user to select BCLK values so that the FIFO performance is controlled.

Table 19 Selection of system clock frequency

Div.1 Div.0 SYSTEM CLOCK FREQUENCY (f

00M×f

0 1 0.5 × M × f

1 0 0.25 × M × f

1 1 0.125 × M × f

XTLI

XTLI

XTLI

XTLI

clk

Table 20 Selection of BCLK frequency

Div2.1 Div2.1 Div2.0 BCLK FREQUENCY (f

000N×f

001N×f

010

011

100

101

110

111

XTLI

XTLI

1

/

(N × f

2

1

/

(N × f

3

1

/

(N × f

4

1

/

(N × f

6

1

/

(N × f

8

1

/

(N × f

12

XTLI

XTLI

XTLI

XTLI

XTLI

XTLI

)

)

)

)

)

)

BCLK

)

)

2000 Mar 21 17

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7.4 HF analog front-end

The HF ADC in the SAA7392 encodes the EFM high

frequency signal from the disc light pen assembly. These

signals are pre-processed, externally to the SAA7392, by

either AEGER-2 or a DALAS equivalent. The dynamic

range of the ADC is optimized by the inclusion of an

AC coupled AGC function under digital control.

In order to make use of the whole digital front-end

resolution, the output of the gain control amplifier should

constantly deliver 1.4 V

ofthe ADC isapproximately14 dB, with32 steps. Thegain

control for the variable gain amplifier is controlled by an

on-chip digital gaincontrol block (AGC). This blockallows

for both automatic and microprocessor gain control. The

gain control block will detect ADC extreme conditions

(00H or FFH outputs); on these values the gain control

block will decrement the gain. If no extreme codes occur

the gain is incremented.

7.4.1 FIXED GAIN

Control of the gain is as follows:

1. Writing XX1X XXXX to the Anaset1 register

(address 15H) increases the AGC gain by 1.1 dB

2. Writing XX0X XXXX to the AnaSet1 register

(address 15H) decreases the AGC gain by 1.1 dB

output signal. The gain range

(p-p)

3. Instructions to increment/decrement gain are ignored

when the AGC gain limits of −4/+12 dB are reached.

7.4.2 AUTOMATIC GAIN CONTROL (AGC)

The gain of theAGC cellis adjusteduntil the analog signal

at the ADC input extends over the complete range of

the ADC.Detection ofthis conditionis in thedigital domain

where the maximum and minimum ADC codes are

measured. The dynamics of the AGC system are as

follows.

1. If the ADC output codes are not full scale (i.e.

000 0000 and 111 11111) the AGC gain is

incremented in 1.1 dB steps with a time constant of

1000/n µs, where n is the over-speed factor i.e. n = 1

for basic audio CD.

2. When full scale is detected at the output of the ADC

the AGC gain is fixed provided that full scale is

maintained and clipping does not occur for greater

than 20% of the time.

3. If clipping occurs for more than 20% of the time, then

the AGC gain is reduced in 1.1 dB steps with a time

constant of 60/n µs.

The ADC and AGC electrical characteristics are specified

in Chapter 9.

7.4.3 ANALOG SETTINGS REGISTER 1(ANASET1)

Table 21 Analog Settings Register 1 (address 15H) - WRITE

76543210

GainControl MaxGain StepUp StepDown PowerDown −−−

Table 22 Description of AnaSet1 bits

BIT SYMBOL DESCRIPTION

7 GainControl If GainControl = 0, then gain control is in Hold mode. If GainControl = 1, then automatic

gain control is on.

6 MaxGain If MaxGain = 0, then there is no gain limit. If MaxGain = 1, then the maximum gain is

7.66 dB.

5 StepUp If StepUp = 1, then step up gain by one LSB.

4 StepDown If StepDown = 1, then step down gain by one LSB.

3 PowerDown If PowerDown = 0, then analog blocks are powered up. If PowerDown = 1, then analog

blocks are powered down.

2to0 − These 3 bits are reserved and must be set to a logic 0s.

2000 Mar 21 18

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7.5 Bit recovery

The bit recovery block (shown in Fig.6) contains the slice

levelcircuitry, anoise filtertolimit theHF-EFMsignal noise

contribution, an adaptive slicer circuit and a digital PLL.

These blocks can be controlled via the microprocessor.

The channel rate should always obey the following

constraints:

• It should be less than 2 × the system clock

• It should be greater than 0.25 × the system clock.

In this clock range reliable bit clock detection is possible.

All data found will be written to the FIFO. It is the

responsibility ofthe user toselect BCLK and system clock

values so that the FIFO operation is controlled.

The digital noise filter runs on the PLL bit clock and limits

the bandwidthof the incomingsignal to 0.25 ofthe PLL bit

clock frequency. The characteristics of the filter are:

• Passband: 0 to 0.22 f

• Stopband: 0.28 fb to (f

b

− 0.28 fb)

clk

• Rejection: −28 dB.

The slice level determination circuit compensates the

incoming signalasymmetry component. Thebandwidth of

this circuit is programmable via register PLLSet.

A programmable (one tap presetable, asymmetrical)

equaliser is used in the bit detection circuit. The first and

last tap settings are different. Possible tap values are

settable via register PLLEqu.

The advanced detector has two extra detection circuits

(adaptive slicer and run length 2 push-back) which are

controlled via the VitSet register, that allow improved

margin in the bit detector.

The adaptive slicer does a second stage slice operation;

thebandwidth ishigherthan thefirst slicer. Itcan beturned

on/off via the VitSet register.

If the advanced detector is switched on all run length 2

symbols are pushed back to run length 3. The circuit will

determine thetransition that was most likely to bein error,

and shift the transition on that edge.

GAIN CONTROLLED

handbook, full pagewidth

AMPLIFIER

HIN

GAIN CONTROL

BLOCK

ADC

+

+

−

NOISE

FILTER

SLICE LEVEL

DETERMINE

DIGITAL

EQUALIZER

clocked on PLL clock

DIGITAL

PLL

RMS JITTER

MEASUREMENT

Fig.6 Block diagram of bit recovery block.

VITERBI

DETECTOR

ZERO TRANS

DETECTOR

PLL frequency

jitter value

slice level

MULTIPLEXER

MEAS1

MGR796

2000 Mar 21 19

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

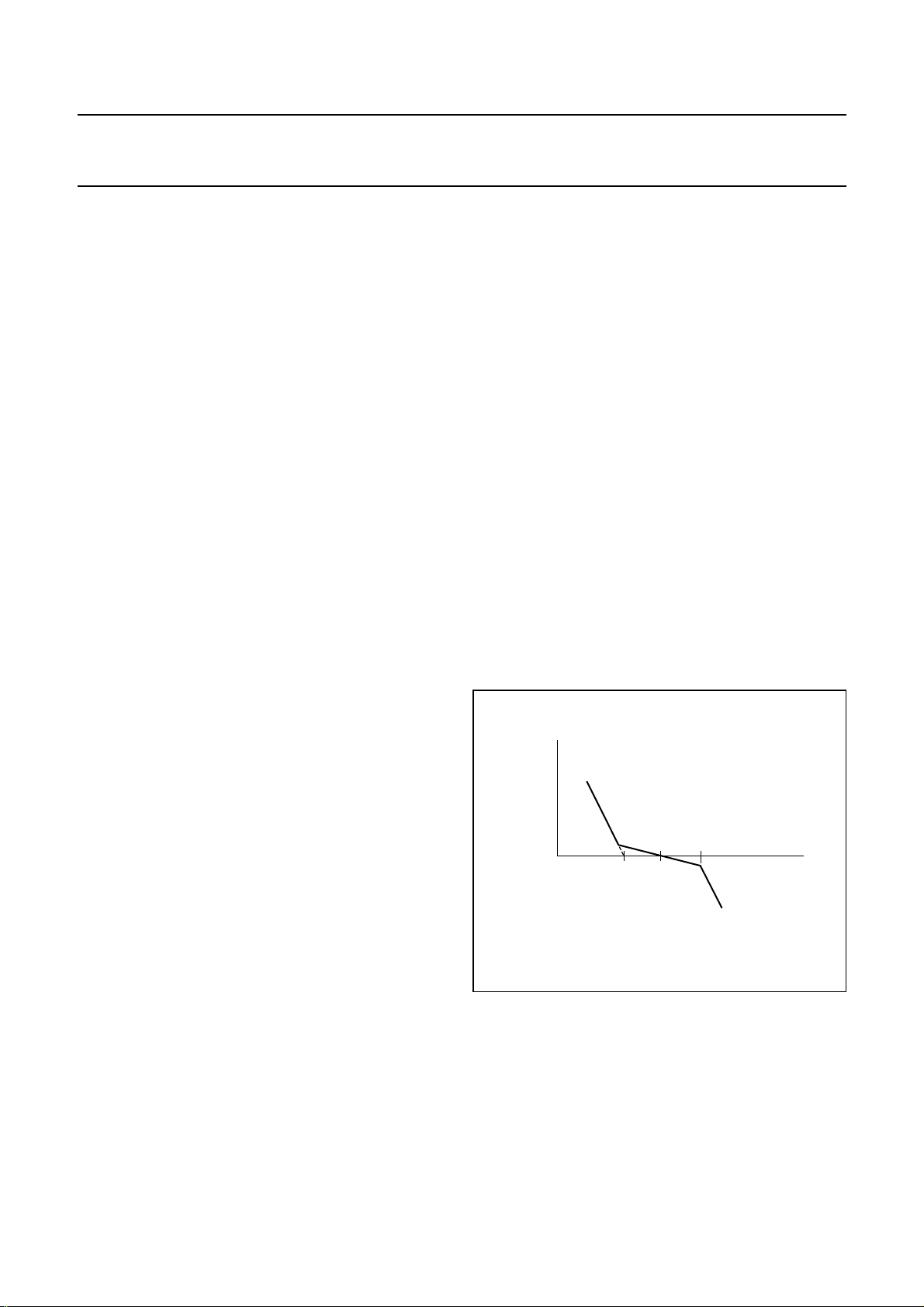

7.5.1 DIGITAL PLL

The digital PLL will recover the channel bit clock. As the

capturerange ofthe PLLitselfis limited,lockdetectors and

2 capture aids are present. In total three different PLL

operation modes exist: In-lock, Inner-lock aid and

Outer-lock aid.

The PLL behaviour during in-lock (the normal on-track

situation) can be best explained in the frequency domain.

The PLL operation is completely linear during in-lock

situations. The open-loop response of the PLL is given in

Fig.7. The three frequencies, f0(integrator cross-over

frequency), f1(PLL bandwidth) and f2(low-pass

bandwidth) are programmable via register PLLSet.

To extend the PLL capture range two lock aids are used:

• Inner lock aid: has a capture range of ±10% and will

bring the PLL frequency to the lock point

• Outer lock range: has no limitation on capture range,

and will bring the PLL within the range of the inner lock

range.

Two outer lock aids can be used:

• Run length 3 deviation detector: this circuit is known to

be sensitive to systematic over/under equalization; this

over/under equalizationcan becounter-acted by writing

a non-zero phase offset value to register PLLLock.

• Frequency measurement detector: this circuit regulates

the PLL frequency so that the average number of EFM

transitions is a fixed fraction of the PLL bit clock; the

transition frequency is settable via register PLLFMeas.

• PLL frequency signal: the most significant 8 bits are

available via register PLLLock

• Asymmetry signal: the 8-bit signal in 2’s complement

form is available via register PLLSet

• Jitter signal: the most significant 8 bits are available via

register PLLFreq. This gives an impression of the

detection jitter after all processing is done.

jitter<9:0> = average ((jitter individual

transition)2× 8192)

To obtain the jitter in the bit clocks the jitter<9:0> value

must be divided by 8192 and square routed. Note that

the jitter<9:0> overestimates thejitter (byapproximately

rms jitter increase of 0.03 bit clock), because the

quantization of the zero transitions is in 4 intervals.

Note the jitter is measured before the bit detection and

contains contributions due to various imperfections in

the complete signal path; i.e. disc, preamplifier, ADC,

limited bitwidths, PLL performance, internal filter noise,

asymmetry compensation, equalizer.

• Internal lock flags: The internally generated inner-lock

signal (f_lock_in), lock signal (lock_in) and flag that

indicates when a run length 14 is detected

(long_symbol) are available via register PLLEqu.

handbook, halfpage

amplitude

(dB)

Programmability/observability is built into the PLL. Its

operation can be influenced in two ways:

• It is possible to select the state the PLL is in (in-lock,

near-lock, outer-lock) via register PLLLock

• It is possible to preset the PLL frequency to a certain

value via registers PLLEqu and PLLFreq.

The operation of the bit detector can be monitored by the

microprocessor and via the MEAS1 pin. Four signals are

available for measurement:

2000 Mar 21 20

f

2

f

0f1

frequency (Hz)

Fig.7 PLL bode diagram.

MGR797

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

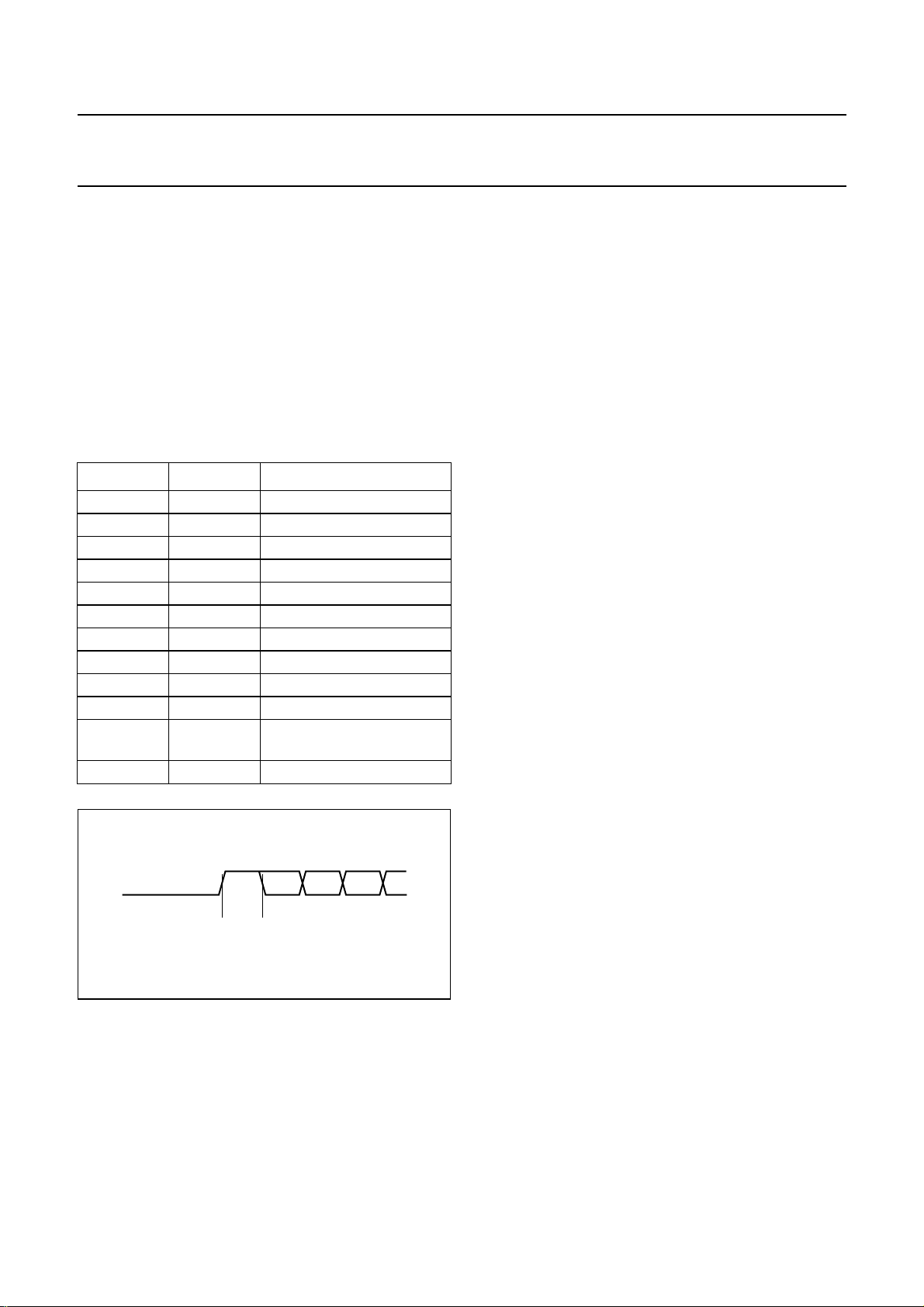

7.5.2 MEAS1 PIN

The MEAS1 pin carries the 3 measurement signals: jitter

(sampled twice), PLL frequency, and asymmetry. Each

frame consists of 64 bits (each 4 system clock periods

long), beginning with a start bit, then data bits then pause

bits (see Fig.8). The start bit is always preceded by

17 pause bits; and the intermediate start bits at

locations 12, 24 and 36 guarantee that no other ‘1’ bit is

preceded by 17 ‘0’ bits, making the start detection easy.

The structure of the frame is described in Table 23 and

shown in Fig.8.

Table 23 Frame structure

BIT VALUE FUNCTION

0 logic 1 start bit

1 to 10 jitter<9:0> jitter word

11 logic 0

12 logic 1 intermediate start bit

13 to 22 pllfreq<9:0> PLL frequency word

23 logic 0

24 logic 1 intermediate start bit

25 to 32 assym<7:0> asymmetry word

33 logic 0

34 logic 1 intermediate start bit

37 to 46 jitter<9:0> second sample of jitter

word

47 to 63 logic 0 pause

handbook, halfpage

pause data bits

bit 0 bit 1

start

bit

bit 2 bit 3

MGR798

Fig.8 Format on MEAS1 pin.

2000 Mar 21 21

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

7.5.3 PLL LOCK SELECT REGISTER (PLLLOCK)

The behaviour of this register is dependent upon whether its being read or written. The behaviour for the write operation

is described in Tables 24 to 27. When read the 8 MSBs of the PLL frequency counter are returned; this is described in

Tables 24 and 28.

Table 24 PLL Lock Select Register (address 00H) - WRITE/READ

76543210

LockOride PhaOset.2 PhaOset.1 PhaOset.0 PLLForceL.3 PLLForceL.2 PLLForceL.1 PLLForceL.0

PLLFreq.7 PLLFreq.6 PLLFreq.5 PLLFreq.4 PLLFreq.3 PLLFreq.2 PLLFreq.1 PLLFreq.0

Table 25 Description of PLLLock bits for write operation

BIT SYMBOL DESCRIPTION

7 LockOride When LockOride = 0, then automatic lock behaviourselected, PLLForceL<3:0>must be

set to ‘0000’. When LockOride = 1, then PLL manual override, PLLForceL<3:0> must

also be programmed.

6 PhaOset.2 These 3 bits are used to select the phase override settings; see Table 26.

5 PhaOset.1

4 PhaOset.0

3 PLLForceL.3 These 4 bits are used to select the PLL lock; see Table 27.

2 PLLForceL.2

1 PLLForceL.1

0 PLLForceL.0

Table 26 Selection of phase override setting

PhaOset.2 PhaOset.1 PhaOset.0 PHASE OVERRIDE

0 0 0 reserved

001

010

011

3

/

×PLL clock over-equalized T3

8

2

/

×PLL clock over-equalized T3

8

1

/

×PLL clock over-equalized T3

8

1 0 0 correct equalisation

101

110

111

1

/

×PLL clock under-equalized T3

8

2

/

×PLL clock under-equalized T3

8

3

/

×PLL clock under-equalized T3

8

Table 27 Selection of PLL lock

PLLForceL.3 PLLForceL.2 PLLForceL.1 PLLForceL.0 PLL LOCK

0000automatic lock behaviour

0001force PLL in-lock

0100force PLL into outer-lock

0110force PLL into inner-lock

1000force PLL into Hold mode (PLL frequency can be

forced using preset value in register PLLFreq)

XXXXall other combinations are reserved

2000 Mar 21 22

Philips Semiconductors Preliminary specification

Channel encoder/decoder CDR60 SAA7392

Table 28 Description of PLLock bits for read operation

BIT SYMBOL DESCRIPTION

7 to 0 PLLFreq<7:0> This register holds the 8 MSBs of the PLL frequency counter. The PLL frequency is

calculated as shown below:

f

(Hz)

PLL

7.5.4 PLL B

The function of this register is dependent upon whether its being read or written. The function for the write operation is

described in Tables 29 to 34. Note the measurement conditions are: system clock = 2.15 MHz, bit clock = 4.3 MHz,

bandwidth is proportional to the system clock.

When read this register returns the 8-bit PLL asymmetry value, see Table 29.

Table 29 PLL Bandwidth Select Register (address 01H) - WRITE/READ

76543210

SliceBW.1 SliceBW.0 IntegF0.1 IntegF0.0 PLLBWF1.1 PLLBWF1.0 LPBWF2.1 LPBWF2.0

PLLAsym.7 PLLAsym.6 PLLAsym.5 PLLAsym.4 PLLAsym.3 PLLAsym.2 PLLAsym.1 PLLAsym.0

Table 30 Description of PLLSet bits for write operation

BIT SYMBOL DESCRIPTION

7 SliceBW.1 These 2 bits select the Slicer bandwidth; see Table 31.

6 SliceBW.0

5 IntegF0.1 These 2 bits select the integrator crossover frequency; see Table 32.

4 IntegF0.0

3 PLLBWF1.1 These 2 bits select the PLL bandwidth; see Table 33.

2 PLLBWF1.0

1 LPBWF2.1 These 2 bits select the low-pass bandwidth; see Table 34.

0 LPBWF2.0

ANDWIDTH SELECT REGISTER (PLLSET)

PLLFreq<7:0> ADC clock (Hz)×()

=

-----------------------------------------------------------------------------------------128

Table 31 Selection of Slicer bandwidth

SliceBW.1 SliceBW.0 SLICER BANDWIDTH

0 0 12 Hz

0 1 50 Hz

1 0 200 Hz

1 1 This value is reserved.

Table 32 Selection of integrator crossover frequency

IntegFO.1 IntegFO.0 INTEGRATOR CROSSOVER FREQUENCY

0 0 3780 Hz

0 1 1890 Hz

1 0 945 Hz

1 1 This value is reserved.

2000 Mar 21 23

Loading...

Loading...