Philips SAA7367 Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAA7367

Bitstream conversion ADC for

digital audio systems

Product specification

Supersedes data of 1996 Jun 17

File under Integrated Circuits, IC01

1998 Nov 17

Philips Semiconductors Product specification

Bitstream conversion ADC for

digital audio systems

FEATURES

• Total Harmonic Distortion plus Noise

(THD + N) = −88 dB (0.004%); DR = 93 dB;

S/N = 97 dB

• Simple interfacing to analog inputs

• Small, non-critical PCB layout

• Low pin-out SO24 package (pin-compatible to

SAA7366)

• 4 flexible serial interface modes

• 4.5 to 5.5 V operation

• Standby mode

• Detection of digital signal ≥−1 dB amplitude

• Up to 18 significant bits serial output

• Selectable high-pass filter.

APPLICATIONS

The device is designed for the digital acquisition of analog

audio signals for digital audio systems such as:

• Compact Disc-Recordable (CD-R)

• Audio digital signal processing systems for hi-fi and

musical instrument applications

• Digital Audio Tape (DAT).

SAA7367

GENERAL DESCRIPTION

The SAA7367 is a CMOS low-cost stereo

Analog-to-Digital Converter (ADC) using the Philips

bitstream conversion technique.

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DDD

I

DDD

V

DDA

I

DDA

f

BCK

f

s

THD + N total harmonic distortion plus

digital supply voltage 4.5 5.0 5.5 V

digital supply current − 17 − mA

analog supply voltage 4.5 5.0 5.5 V

analog supply current − 13 − mA

clock input frequency 4.60 12.288 12.8 MHz

sample rate 18 48 50 kHz

at 0 dB input −−88 −80 dB

noise

DR dynamic range at −60 dB 90 93 − dB

S/N signal-to-noise ratio − 97 − dB

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

SAA7367 SO24 plastic small outline package; 24 leads; body width 7.5 mm SOT137-1

1998 Nov 17 2

Philips Semiconductors Product specification

Bitstream conversion ADC for

digital audio systems

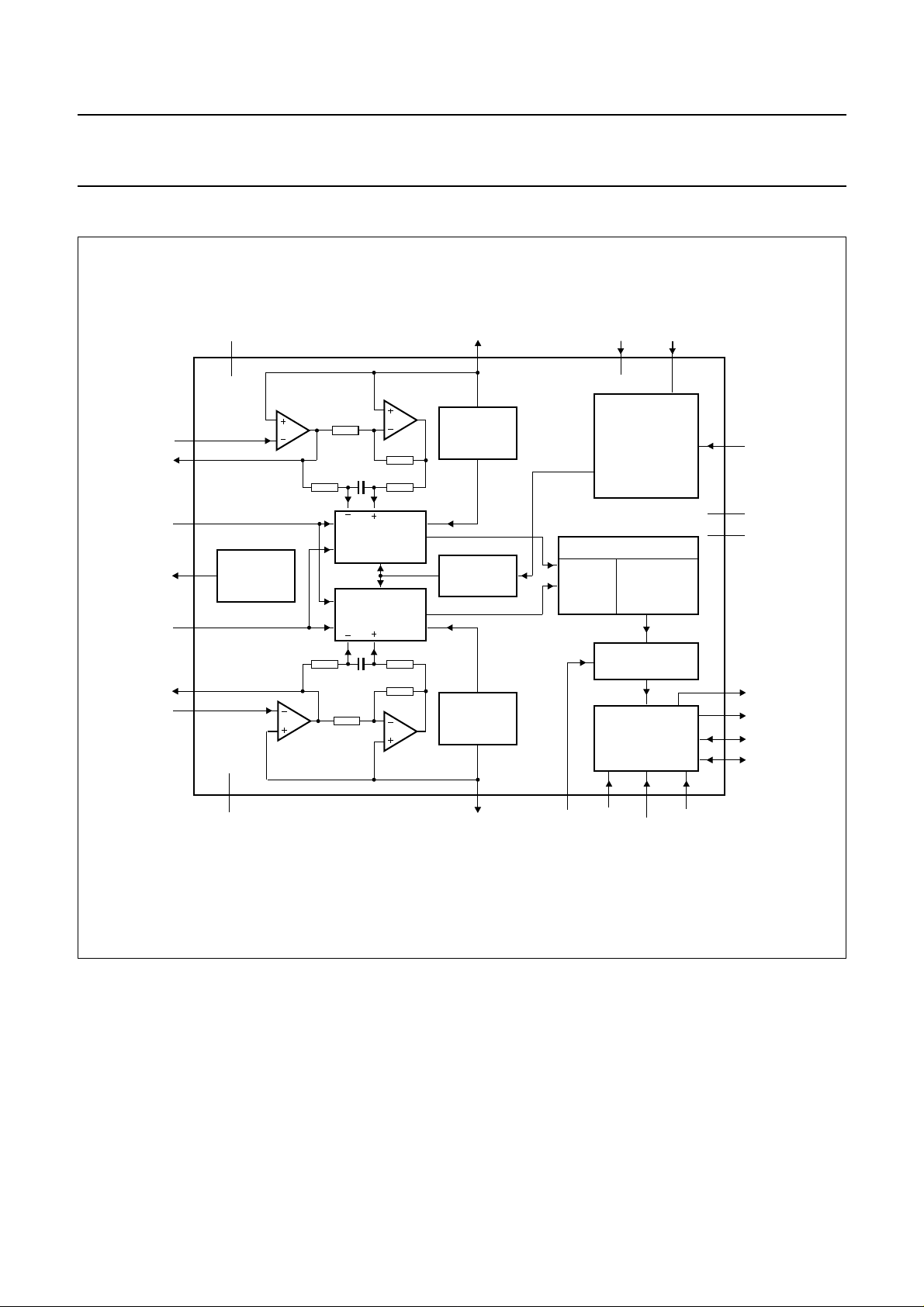

BLOCK DIAGRAM

V

16

17

19

REFERENCE

14

GENERATOR

18

20

21

SSA

operational

amplifier

CURRENT

operational

amplifier

23

handbook, full pagewidth

BIR

BOR

V

DACP

I

ref

V

DACN

BOL

BIL

operational

amplifier

SIGMA-

DELTA

MODULATOR

SIGMA-

DELTA

MODULATOR

operational

amplifier

V

refR

REFERENCE

VOLT AGE

GENERATOR

TIMING

GENERATOR

REFERENCE

VOLT AGE

GENERATOR

22

SAA7367

TESTB

DECIMATION FILTER

STAGE 1

COMB

FILTER

SERIAL OUTPUT

11 1

STDB

CLOCK

GENERATION

AND

CONTROL

STAGE 2

3 HALF-BAND

FILTERS

HIGH-PASS

FILTER

INTERFACE

24

10

SAA7367

2121513

4

CKIN

5

V

DDD

6

V

SSD

3

OVLD

7

SDO

8

SWS

9

SCK

V

DDA

Fig.1 Block diagram.

1998 Nov 17 3

HPEN

V

refL

TEST1

SLAVE

SFOR

MGE645

Philips Semiconductors Product specification

Bitstream conversion ADC for

SAA7367

digital audio systems

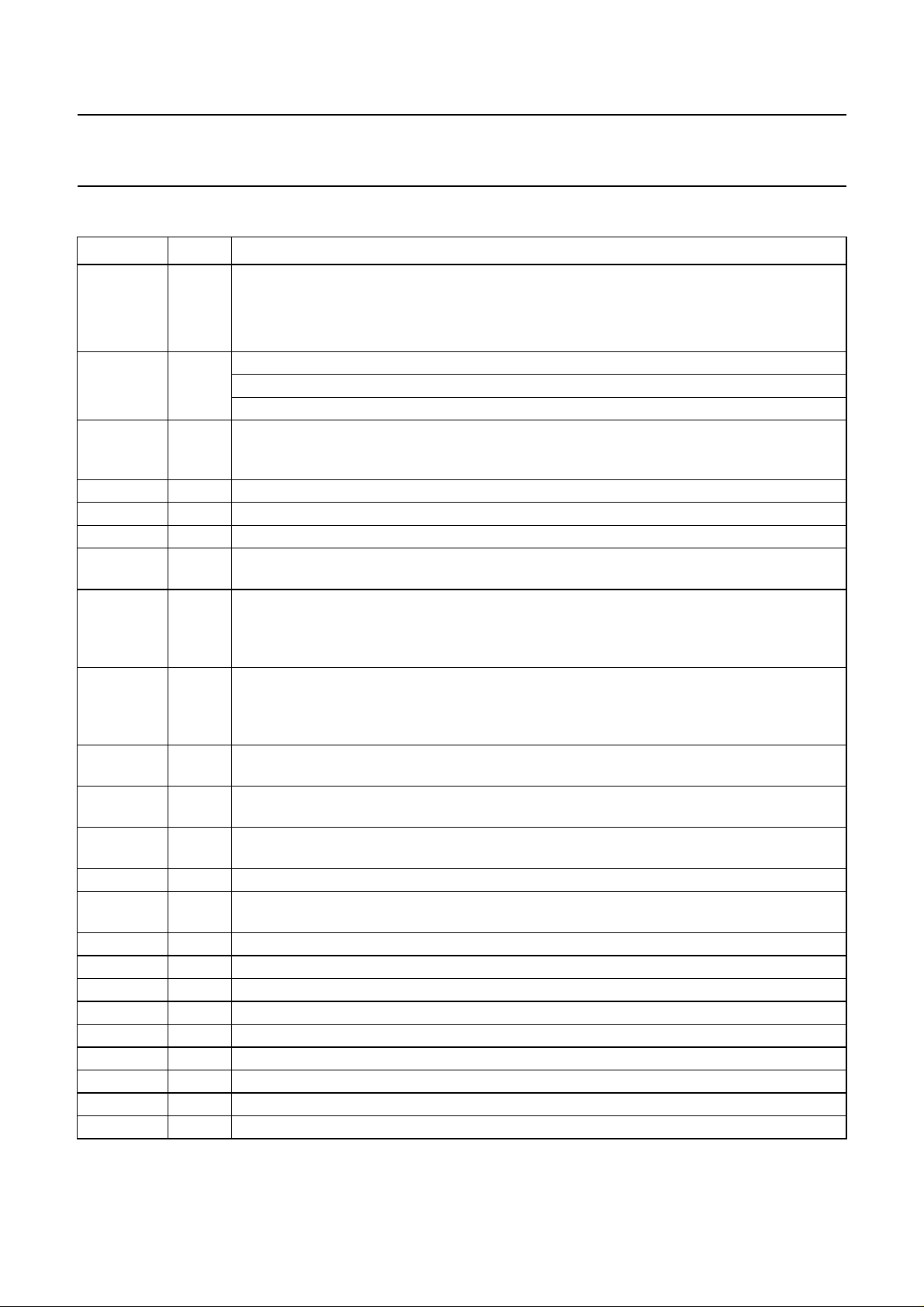

PINNING

SYMBOL PIN DESCRIPTION

SFOR 1 TTL level input; in normal mode this input selects the serial interface output format; output

format is selected as follows:

SFOR = HIGH selects Format 1

SFOR = LOW selects Format 2 (similar to I

STDB 2 schmitt-trigger input; in normal mode, this input is used to select standby mode:

STDB = HIGH selects normal operation

STDB = LOW selects standby mode (low power consumption)

OVLD 3 TTL level output; in normal mode this output indicates whether the internal digital signal is

within 1 dB of maximum; if so, the output will go HIGH for 131072 clock cycles (approximately

11 ms); in standby mode this output is forced LOW

CKIN 4 CMOS level input; system clock input; nominally clocked at 256f

V

V

DDD

SSD

5 digital supply voltage (4.5 to 5.5 V)

6 digital ground

SDO 7 TTL level output (3-state); in normal mode this pin outputs data from the serial interface; in

standby mode, this output is high impedance

SWS 8 TTL level input/output; serial interface word select signal; in master mode (SLAVE = LOW),

this pin outputs the serial interface word select signal; in slave mode (SLAVE = HIGH), this pin

is the word select input to the serial interface; in standby mode (STDB = LOW) this pin is

always an input (high impedance); for polarity: see Table 1

SCK 9 TTL level input/output; in master mode (SLAVE = LOW) the pin outputs the serial interface bit

clock; in slave mode (SLAVE = HIGH) this pin is the input for the external bit clock; data on

SDO is clocked out on the HIGH-to-LOW transition of SCK; the data is valid on the

LOW-to-HIGH transition

TEST1 10 Test1; TTL level input with internal pull-down; in slave mode (slave = HIGH), this pin is used

to select extra serial interface formats (see Table 2)

HPEN 11 TTL level input; this input is used to enable the internal high-pass filter when HIGH; in

scan-test mode (TESTB = LOW and TEST1 = LOW) this pin functions as ‘scan chain c’ input

TESTB 12 TestB; CMOS level input with internal pull-up; in normal applications, this input should be left

HIGH

V

I

V

SSA

ref

refR

13 analog ground; this pin is internally connected to VSS via the on-chip substrate contacts

14 current reference generator output; 33 kΩ in parallel with 22 nF is connected from this pin to

V

SSA

15 right channel analog reference output voltage (1⁄2V

BIR 16 buffer operational amplifier inverting input for right channel

BOR 17 buffer operational amplifier output for right channel

V

DACN

V

DACP

18 negative 1-bit DAC reference voltage input, connected to 0 V

19 positive 1-bit DAC reference voltage input, connected to +5 V

BOL 20 buffer operational amplifier output for left channel

BIL 21 buffer operational amplifier inverting input for left channel

V

V

refL

DDA

22 left channel analog reference output voltage (1⁄2V

23 analog supply voltage (4.5 to 5.5 V)

2

S)

s

)

DDA

)

DDA

1998 Nov 17 4

Philips Semiconductors Product specification

Bitstream conversion ADC for

digital audio systems

SYMBOL PIN DESCRIPTION

SLAVE 24 TTL level input; used to select the serial interface operating mode:

SLAVE = HIGH selects slave mode

SLAVE = LOW selects master mode

Table 1 SWS polarity

CONDITIONS

SLAVE AND TEST1 SWS SFOR

SLAVE = LOW or TEST1 = LOW LOW LOW left data

LOW HIGH right data

SLAVE = HIGH and TEST1 = HIGH LOW LOW right data

LOW HIGH left data

Table 2 Selection of serial interface formats via TEST1

CONDITIONS

SELECTED FORMAT

SFOR TEST1

HIGH LOW format 1

HIGH format 3

LOW LOW format 2

HIGH format 4

SAA7367

POLARITY

handbook, halfpage

SFOR

1

STDB

2

OVLD

3

CKIN

4

V

5

DDD

V

6

SSD

SDO

SWS

SCK

TEST1

HPEN

TESTB

7

8

9

10

11

12

SAA7367

MGE644

Fig.2 Pin configuration.

FUNCTIONAL DESCRIPTION

General

SLAVE

24

V

23

DDA

V

22

refL

BIL

21

BOL

20

The SAA7367 is a bitstream conversion CMOS ADC for

digital audio systems. The conversion is achieved using a

third-order Sigma-Delta Modulator (SDM), running at

128 times the output sample frequency (f

). The high

s

oversampling ratio greatly simplifies the design of the

analog input anti-alias filter. In most events, the internal

buffer operational amplifier, configured as a low-pass filter,

19

V

DACP

V

18

DACN

17

BOR

BIR

16

V

15

refR

I

14

ref

V

13

SSA

will suffice. The 1-bit code from the SDM is filtered and

down-sampled (decimated) to 1fs by Finite Impulse

Response (FIR) filters. An optional I2R high-pass filter is

provided to remove DC, if required. The device has been

designed with ease of use, low board area and low

application costs in mind.

Clock frequency

The external clock input on pin CKIN runs at 256f

, which

s

can range from 18 to 50 kHz.

1998 Nov 17 5

Philips Semiconductors Product specification

Bitstream conversion ADC for

digital audio systems

Input buffer

Two input buffers are provided, one for each channel, for

signal amplitude matching, signal buffering and anti-alias

filter purposes. These are configured for inverting use.

Access is provided by pins BIL, BIR (inverting inputs) and

BOL, BOR (outputs), for left and right channels

respectively. By the choice of feedback component values,

the application signal amplitude can be matched to the

requirements of the ADC.

Typically, the operational amplifiers are configured as

low-pass filters with a gain of 1 and a pole at

approximately 5f

Remark: the complete ADC is non-inverting. Hence, a

positive DC input (referenced to V

digital output.

Input level

The overall system gain is proportional V

accurately the potential difference between the DAC

reference voltages (V

convenience, the ADC input signal amplitude is defined as

that amplitude seen on BOL or BOR, the operational

amplifier outputs (i.e. the input to the SDM). Also, the 0 dB

input level is defined as that which gives a −1 dB (actually

−1.12 dB) digital output, relative to full-scale swing. This

reduced gain provides headroom to accommodate small

random DC offsets, without causing the digital output to

clip.

Hence:

V

0dB()

I

.

s

) and (V

VDACP

V

=

-------------------------------------------------------

–()

VDACPVVDACN

5V(RMS)

) will yield a positive

ref

, or more

DDA

). For

VDACN

SAA7367

Input signals in the range 0 to 1 dB may or may not be

clipped, depending on the values of DC dither and small

random offsets in the analog circuitry.

When using the recommended application circuitry,

clipping will initially be observed on negative peaks, due to

the use of negative DC dither.

The maximum level of overload that can be safely

tolerated is application circuit dependent. In the case of the

recommended circuit, the following applies: the inverting

operational amplifier inputs BIL and BIR are protected

from excessive voltages (currents) by diodes to V

V

. These have absolute maximum ratings of

SSA

Id= ±20 mA, with a safe practical limit of ±2 mA.

Given the input resistor of 10 kΩ, ±2 mA diode current and

the operation of the operational amplifier, a maximum

signal (applied to the input resistor) of ±30 V can be

handled safely. This level represents an overload of 26 dB.

During overload, the in-band portion of the waveform will

be correctly converted. The out-of-band portion will be

limited as previously detailed.

Sigma-Delta Modulator (SDM)

The SAA7367 uses two third-order SDMs with a

quantization noise floor of approximately −104 dB. The

scaling of the feedback has been optimized for stable

operation, even during overload. Thus, with a maximum

signal swing of 0 V to V

on the input, the digital output

DDA

remains well-behaved, i.e. it does not burst into random

oscillation. During overload, the output is simply a clipped

version of the input. The gain of this stage is −4.64 dB.

Decimation filter

DDA

and

The user of the IC should ensure that, when all sources of

signal amplitude variation are taken into account, the

maximum input signal should conform to the 0 dB level.

In the event that the maximum signal level cannot be

pre-determined, e.g. live microphone input, the average

signal level should be set at −10 to −20 dB down. The

exact value will depend on the application and the balance

between headroom and operating Signal-to-Noise Ratio

(SNR).

Behaviour during overload

As previously defined, the maximum input level for normal

operation is 0 dB. If the input level exceeds this value,

clipping may occur. Within the system, excessive

amplitudes are detected after the high-pass filter.

Infringements are limited to the maximum permitted

positive or negative values 217− 1 or −217 respectively.

1998 Nov 17 6

Decimation from 128f

is performed in two stages. The first

s

stage, a comb filter, uses 64 symmetrical coefficients to

implement a 3rd sinx⁄x characteristic. This filter decimates

from 128 to 8fs. The second stage, an FIR filter, consists of

three half-band filters, each decimating by a factor of 2.

The overall characteristics are given in Table 3.

Loading...

Loading...