Philips SAA7360GP Datasheet

INTEGRATED CIRCUITS

DATA SH EET

SAA7360

Bitstream conversion ADC

for digital audio systems

Product specification

Supersedes data of July 1993

File under Integrated Circuits, IC01

Philips Semiconductors

1995 Apr 24

Philips Semiconductors Product specification

Bitstream conversion ADC

for digital audio systems

FEATURES

• Stereo input

• Single-ended input

• Uncommitted input buffer for filtering and pre-scaling

• Fully differential analog-to-digital converter (ADC) using

3rd order Sigma-Delta modulation

• 128 times oversampling

• Four stage digital decimation filter

• Switchable high-pass filter to remove DC offsets

• 16-bit or 18-bit selectable output in a multiple of formats

• Sampling rates between 18 and 53 kHz supported

• Master or slave operation

• Choice of 2 crystal frequencies

• Single power supply operation (+5 V).

QUICK REFERENCE DATA

SAA7360

GENERAL DESCRIPTION

The SAA7360 is a CMOS ADC using Philips bitstream

conversion technique. The device is designed for digital

audio playback systems, such as digital amplifiers,

CD-recordable and Digital Compact Cassette (DCC). The

device is a complementary device to the SAA7350

bitstream conversion digital-to-analog converter (DAC).

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD

f

xtal

THD + N total harmonic distortion + noise −−90 −85 dB

ORDERING INFORMATION

TYPE

NUMBER

SAA7360GP QFP44

Note

1. When using IR reflow soldering it is recommended that the Drypack instructions in the

Pocketbook”

supply voltage 4.5 5.0 5.5 V

crystal frequency 256f

NAME DESCRIPTION VERSION

(1)

plastic quad flat package; 44 leads (lead length 2.35 mm);

body 14 × 14 × 2.2 mm

512f

s

s

PACKAGE

− 11.2896 − MHz

− 22.5792 − MHz

SOT205-1

“Quality Reference

(order number 9398 510 34011) are followed.

1995 Apr 24 2

1995 Apr 24 3

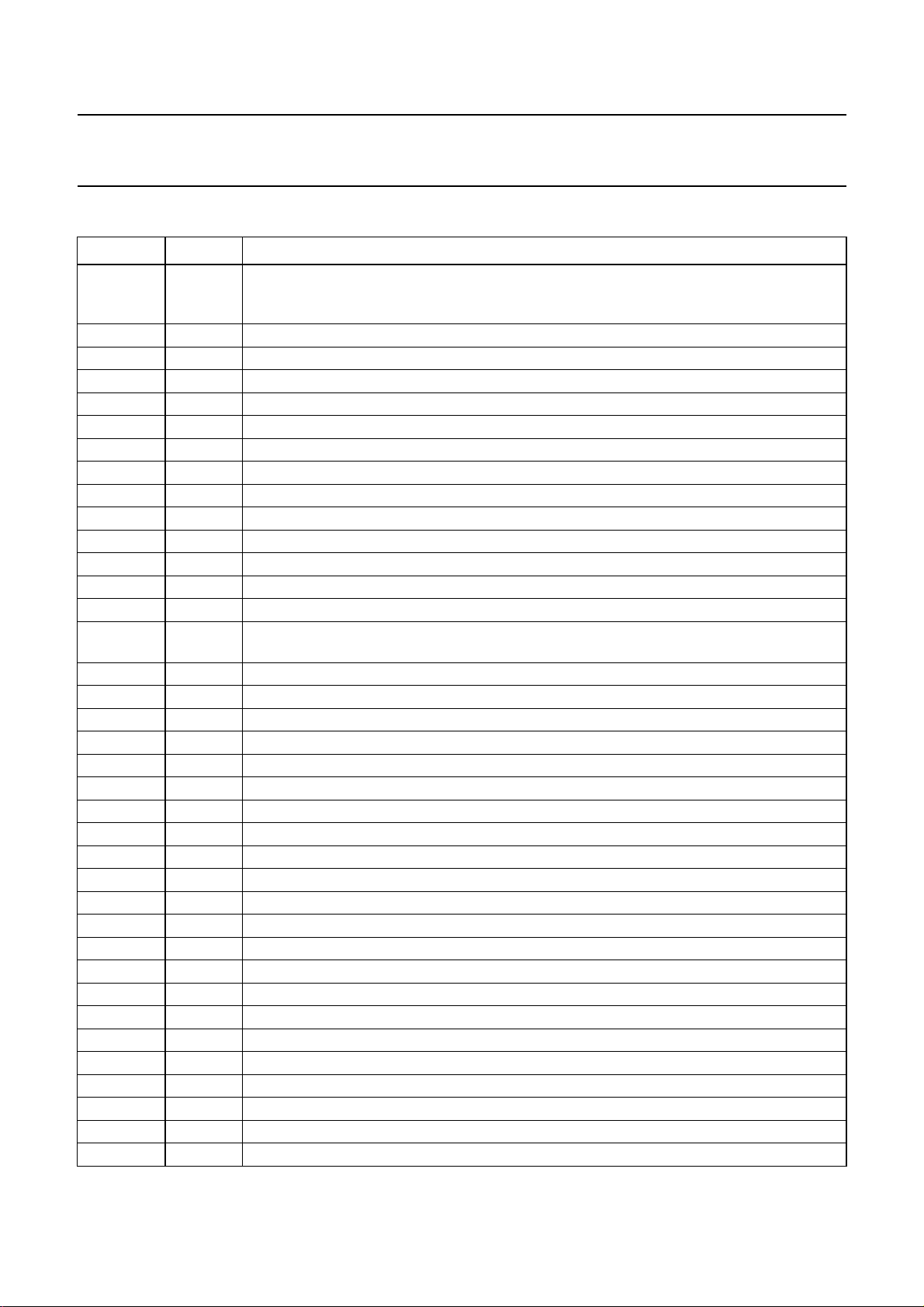

BLOCK DIAGRAM

for digital audio systems

BAOL BBOL NINL PINL DIOL DCKO XIN XOUT XSYS1 XSYS2

Philips Semiconductors Product specification

Bitstream conversion ADC

V

DACN

V

DACP

V

DDAT

V

SSAT

V

V

V

V

BAIL

refL

refR

I

ref

BAIR

SSA

DDA

31 34 32 33

30

SDM

V

refL

27

29

20

19

35

21

28

26

V

refR

37

36

V

refL

TIMING

V

ref

I

ref

V

refR

25 22

BBORBAOR

SDM

24 23

NINR PINR

128f

128f

15

18

s

MUX

1st

DECIMATION

FILTER

STAGE

MUX

s

17

8f

16

2nd

DECIMATION

FILTER

STAGE

SAA7360

TIMING

CONTROL

f

ss

AND

HIGHPASS

FILTER

9876

1

FSEL

40

WSEL

39

TSEL

42

ODF1

41

OUTPUT

INTER-

FACE

38

V

TEST1HPENDIORDSEL

DDDVSSD

452

14

11

12

13

10

44

43

3

ODF2

SWSO

SCKO

SDO

SWSI

SCKI

CEN

RESET

TEST2

MLA714 - 1

handbook, full pagewidth

Fig.1 Block diagram.

SAA7360

Philips Semiconductors Product specification

Bitstream conversion ADC

SAA7360

for digital audio systems

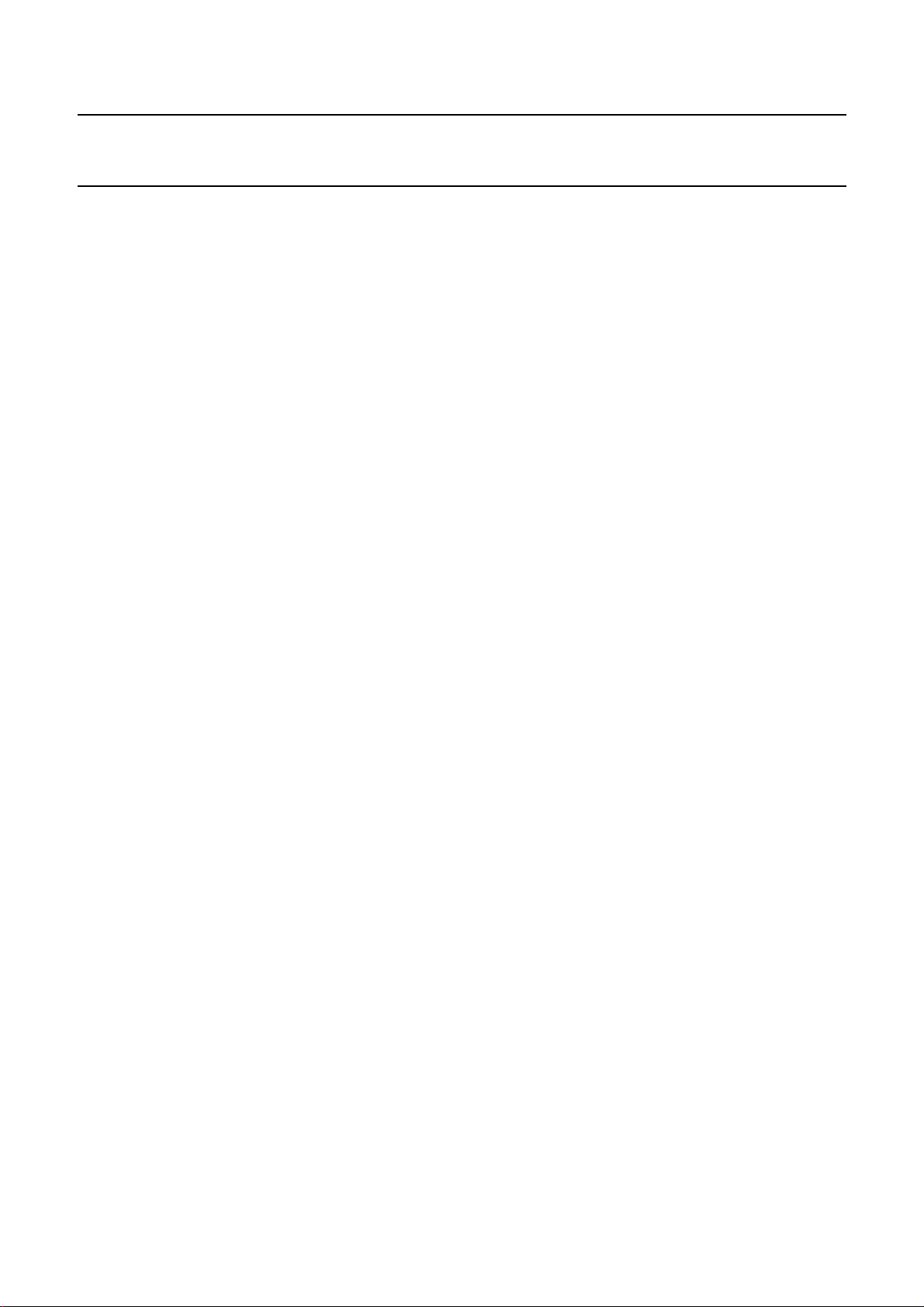

PINNING

SYMBOL PIN DESCRIPTION

FSEL 1 Crystal frequency select input. This pin is used to select the master crystal frequency as

follows: FSEL = HIGH = 256f

HIGH.

TEST1 2 test input 1; this pin should be left open-circuit

TEST2 3 test input 2; this pin should be left open-circuit

V

V

SSD

DDD

4 supply ground for the digital section

5 supply voltage for the digital section (+5 V)

XIN 6 crystal oscillator input

XOUT 7 crystal oscillator output

XSYS1 8 system clock output

XSYS2 9 output clock at a frequency half the system clock frequency

SCKI 10 serial interface clock input

SCKO 11 serial interface clock output

SDO 12 serial interface data output

SWSI 13 serial interface word select input

SWSO 14 serial interface word select output

DSEL 15 input for selecting between the internally generated 1-bit code (DSEL = HIGH) or an

externally generated 1-bit code (DSEL = LOW); if unconnected this pin defaults HIGH

DCKO 16 1-bit code clock output

DIOR 17 1-bit code input/output (right channel)

DIOL 18 1-bit code input/output (left channel)

V

V

V

SSAT

DDAT

refR

19 supply ground for the analog timing section

20 supply voltage for the analog timing section (+5 V)

21 voltage reference generator for the right channel analog section

BBOR 22 output of right channel buffer operational amplifier ‘B’

PINR 23 positive input to right channel Sigma-Delta modulator

NINR 24 negative input to right channel Sigma-Delta modulator

BAOR 25 output of right channel buffer operational amplifier ‘A’

BAIR 26 input of right channel buffer operational amplifier ‘A’

V

DACN

I

ref

V

DACP

27 negative voltage reference level input for the DACs

28 current reference output

29 positive voltage reference level input for the DACs

BAIL 30 input of left channel buffer operational amplifier ‘A’

BAOL 31 output of left channel buffer operational amplifier ‘A’

NINL 32 negative input to left channel Sigma-Delta modulator

PINL 33 positive input to left channel Sigma-Delta modulator

BBOL 34 output of left channel buffer operational amplifier ‘B’

V

V

V

refL

DDA

SSA

35 voltage reference generator for the left channel analog section

36 supply voltage for the analog section (+5 V)

37 supply ground for the analog section

; FSEL = LOW = 512fs; if unconnected the pin will default

s

1995 Apr 24 4

Philips Semiconductors Product specification

Bitstream conversion ADC

SAA7360

for digital audio systems

SYMBOL PIN DESCRIPTION

HPEN 38 high-pass filter enable input (HPEN = HIGH = enabled); if unconnected this pin defaults

HIGH

TSEL 39 input to select master (TSEL = LOW) or slave (TSEL = HIGH) operation of the serial

interface; if unconnected this pin defaults HIGH

WSEL 40 input to indicate 16-bit (WSEL = HIGH) or 18-bit (WSEL = LOW) output data word length of

the serial interface; if unconnected this pin defaults HIGH

ODF2 and

ODF1

RESET 43 Power-On Reset (POR) input (active LOW) to mute the digital output during power on

CEN 44 Chip enable input; this pin, when LOW, disables the operation of the device and 3-states the

41 and 42 serial interface format inputs; these 2 pins determine the interface format in which the device

will operate (see Chapter “Functional Description”); if unconnected these pins will default

2

HIGH (I

S format)

outputs of the serial interface bus. This enables the connection of one of more devices to the

output bus; if unconnected this pin defaults HIGH.

handbook, full pagewidth

FSEL

TEST1

TEST2

V

SSD

V

DDD

XIN

XOUT

XSYS1

XSYS2

SCKI

SCKO

refL

DDA

WSEL

40

16

DCKO

TSEL

39

17

DIOR

HPEN

38

18

DIOL

37

19

SSAT

V

V

ODF2

ODF1

RESET

CEN

44

1

2

3

4

5

6

7

8

9

10

11

12

SDO

43

13

SWSI

42

14

SWSO

41

SAA7360

15

DSEL

SSA

V

V

36

20

DDAT

V

V

35

21

refR

BBOL

34

22

BBOR

33

32

31

30

29

28

27

26

25

24

23

MLA715 - 2

PINL

NINL

BAOL

BAIL

V

DACP

I

ref

V

DACN

BAIR

BAOR

NINR

PINR

Fig.2 Pin configuration.

1995 Apr 24 5

Philips Semiconductors Product specification

Bitstream conversion ADC

for digital audio systems

FUNCTIONAL DESCRIPTION

General

The SAA7360 is a bitstream conversion CMOS ADC for

digital audio systems. The device consists of a input buffer

which can be configured by the user for pre-scaling and

anti-aliasing, a third order Sigma- Delta modulator with a

performance of better than 90 dB THD + Noise, and

decimation filters with anti-aliasing suppression of >93 dB

and in band ripple of less than 0.0002 dB. The device

outputs data in a number of formats compatible with a

range of manufacturers.

Clock frequency

The SAA7360 can operate in either master or slave mode

(CMOS input drive levels). The clock can be either 256f

512fs (where fs is the sampling frequency) indicated via pin

FSEL. System clock outputs equal to the input frequency

(XSYS1) and half the input frequency (XSYS2) are

provided to drive other ICs in the system. All performance

parameters track with fs which can vary between

18 and 53 kHz without degradation of performance.

Input buffer

The input buffer stage consists of an uncommitted input

operational amplifier (‘A’) and a committed unity gain

operational amplifier (‘B’) to perform a single-to-double

ended conversion for the differential ADC. The input buffer

can be configured for pre-scaling and second order

anti-aliasing filtering. The scaling should be performed so

as to provide a maximum of 1 V RMS value at the output

of the operational amplifier.

Sigma-Delta modulator

The analog-to-digital conversion is performed by a third

order Sigma-Delta modulator, which outputs a 1-bit code

at 128fs with a distortion plus noise figure of >90 dB. The

modulator is scaled so that a 0 dB input results in an output

of −3 dB, at the 1-bit outputs.

Digital decimation filter

The left and right channel 1-bit codes from the ADC are

decimated from 128f

first filter stage decimates by a factor of 16fsto 8fs using a

4th order combination type filter. The other three filter

stages consist of three cascaded half-band filters each

decimating by a factor of two. The half-band filter

decimating from 8fsto 4fs has a gain of +2 dB to

compensate for the −3 dB through the analog part and

to 1fs in four stages of filtering. The

s

or

s

SAA7360

allow a headroom of 1 dB to prevent clipping with DC

offsets.

The overall response of the digital decimation filter is a

pass band from 0f

with a ripple of <0.0002 dB and a transition band of

0.454fsto 0.544fs. All frequencies between

0.544fsand 64fs which could result in aliasing into the

base band are attenuated by >−93 dB.

High-pass filter

The operational amplifiers in the Sigma-Delta modulator

can cause a small DC offset to be present in the 1-bit code

passed to the digital section. This can result in the

possibility of clicks when switching between devices and

the recording of DC offsets which can upset offsets

introduced in filters and noise shaping DACs in the

playback path. A switchable high-pass filter is included on

the IC after the decimation filter stage to allow the user to

remove these DC offsets (selectable via pin HPEN). The

filter does not affect the decimation process. The filter is

1st order high pass with following specifications:

• Corner frequency (−3 dB): 1.7 Hz

• Ripple: none

• Above 100 Hz: <0.00002 dB; <1 degree

• At 20 Hz: −0.03 dB, 5 degree phase deviation

• Noise floor: −116 dB.

Output interface

The output interface can operate in master or slave mode

selectable by pin TSEL. Master mode drives pins SWSO

(word select), SCKO (bit clock) and SDO (data output).

Slave mode receives the word clock on pin SWSI and the

bit clock on pin SCKI. In slave mode the internal circuitry

runs on the incoming bit clock and therefore cannot

operate with burst clocks. Slave mode causes the pins

SWSO and SCKO to be 3-stated allowing systems to

connect SWSO and SCKO to pins SWSI and SCKI

respectively for applications where the device has to

operate in master and slave modes. The bit clock in master

mode is at 32f

In slave mode the bit clock is a minimum of 32fs and a

maximum of 64fs.

Three output formats are supported, I2S and two pseudo

I2S modes common in digital audio ADC systems. These

formats are shown in Fig.3. Selection of the three formats

is given in Table 1. 16-bit or 18-bit output words can be

chosen (via pin WSEL).

to 0.454fs (20 kHz at fs= 44.1 kHz)

s

for 16-bit output, and 64fs for 18-bit output.

s

1995 Apr 24 6

Loading...

Loading...