Philips SAA7126H-V1 Datasheet

DATA SH EET

Product specification

File under Integrated Circuits, IC22

1999 May 31

INTEGRATED CIRCUITS

SAA7126H; SAA7127H

Digital video encoder

1999 May 31 2

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

FEATURES

• Monolithic CMOS 3.3 V device, 5 V I2C-bus optionally

• Digital PAL/NTSC encoder

• System pixel frequency 13.5 MHz

• 54 MHz double-speed multiplexed D1 interface capable

of splitting data into two separate channels (encoded

and baseband)

• Four Digital-to-Analog Converters (DACs) for CVBS

(CSYNC, VBS), RED (Cr, C), GREEN (Y, VBS) and

BLUE (Cb, CVBS) two times oversampled (signals in

parenthesis are optionally). RED (Cr), GREEN (Y) and

BLUE (Cb) signal outputs with 9-bit resolution, whereas

all other signal outputs have 10-bit resolution; CSYNC is

an advanced composite sync on the CVBS output for

RGB display centring.

• Real-time control of subcarrier

• Cross-colour reduction filter

• Closed captioning encoding and World Standard

Teletext (WST) and North-American Broadcast Text

System (NABTS) teletext encoding including sequencer

and filter

• Copy Generation Management System (CGMS)

encoding (CGMS described by standard CPR-1204 of

EIAJ); 20 bits in lines 20/283 (NTSC) can be loaded via

the I

2

C-bus

• Fast I2C-bus control port (400 kHz)

• Line 23 Wide Screen Signalling (WSS) encoding

• Video Programming System (VPS) data encoding in

line 16 (CCIR line count)

• Encoder can be master or slave

• Programmable horizontal and vertical input

synchronization phase

• Programmable horizontal sync output phase

• Internal Colour Bar Generator (CBG)

• Macrovision Pay-per-View copy protection system

rev. 7.01 and rev. 6.1 as option; ‘handsfree’ Macrovision

pulse support through on-chip timer for pulse amplitude

modulation; this applies to SAA7126H only. The device

is protected by USA patent numbers 4631603, 4577216

and 4819098 and other intellectual property rights.

Use of the Macrovision anti-copy process in the device

is licensed for non-commercial home use only. Reverse

engineering or disassembly is prohibited. Please

contact your nearest Philips Semiconductors sales

office for more information.

• Controlled rise/fall times of output syncs and blanking

• On-chip crystal oscillator (3rd-harmonic or fundamental

crystal)

• Down mode (low output voltage) or power-save mode of

DACs

• QFP44 package.

GENERAL DESCRIPTION

The SAA7126H; SAA7127H encodes digital Cb-Y-Cr

video data to an NTSC or PAL CVBS or S-video signal.

Simultaneously, RGB or bypassed but interpolated

Cb-Y-Cr signals are available via three additional

Digital-to-Analog Converters (DACs). The circuit at a

54 MHz multiplexed digital D1 input port accepts two CCIR

compatible Cb-Y-Cr data streams with 720 active pixels

per line in 4 :2:2multiplexed formats, for example MPEG

decoded data with overlay and MPEG decoded data

without overlay, whereas one data stream is latched at the

rising, the other one at the falling clock edge.

It includes a sync/clock generator and on-chip DACs.

ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

SAA7126H QFP44 plastic quad flat package; 44 leads (lead length 1.3 mm);

body 10 × 10 × 1.75 mm

SOT307-2

SAA7127H

1999 May 31 3

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

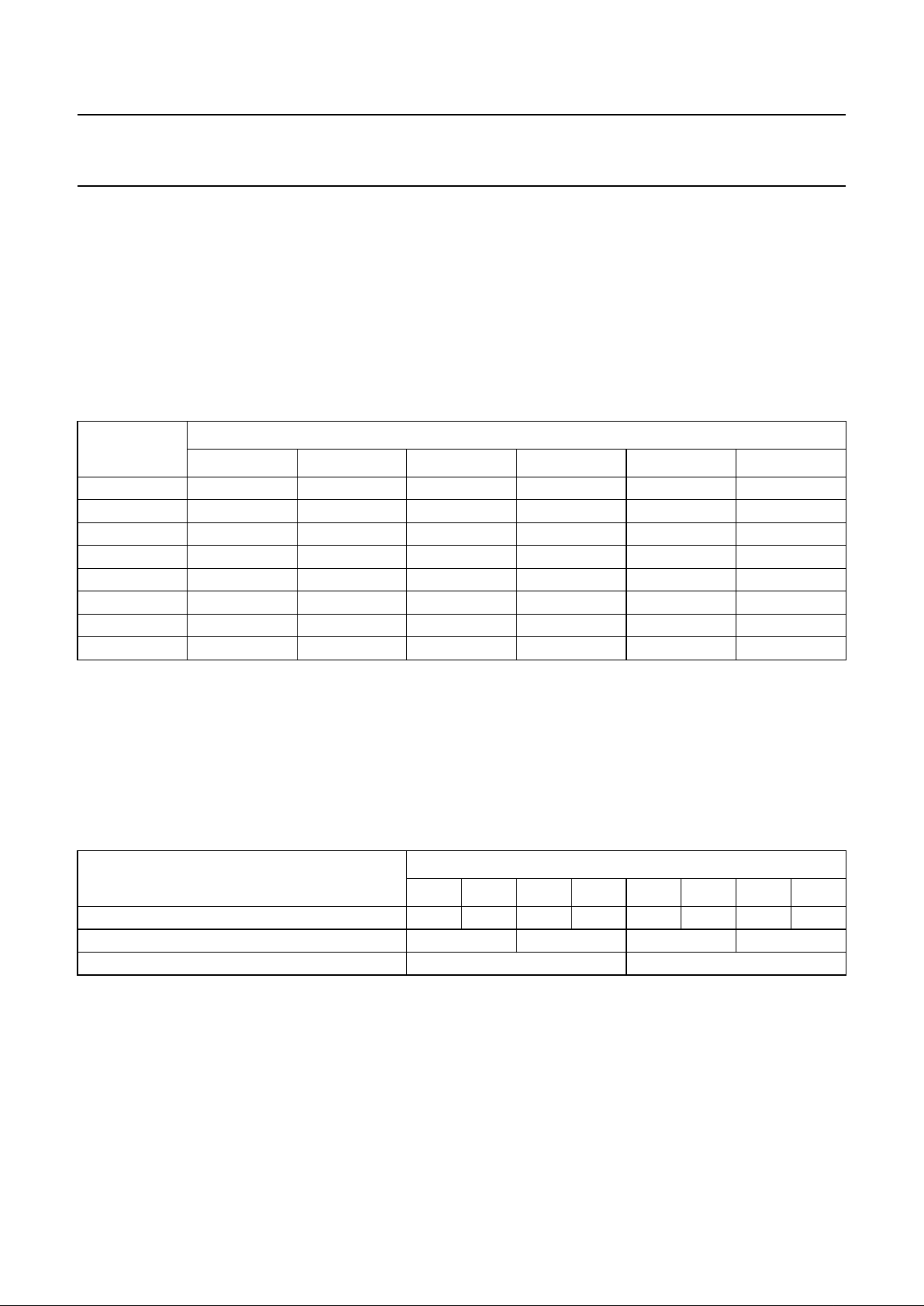

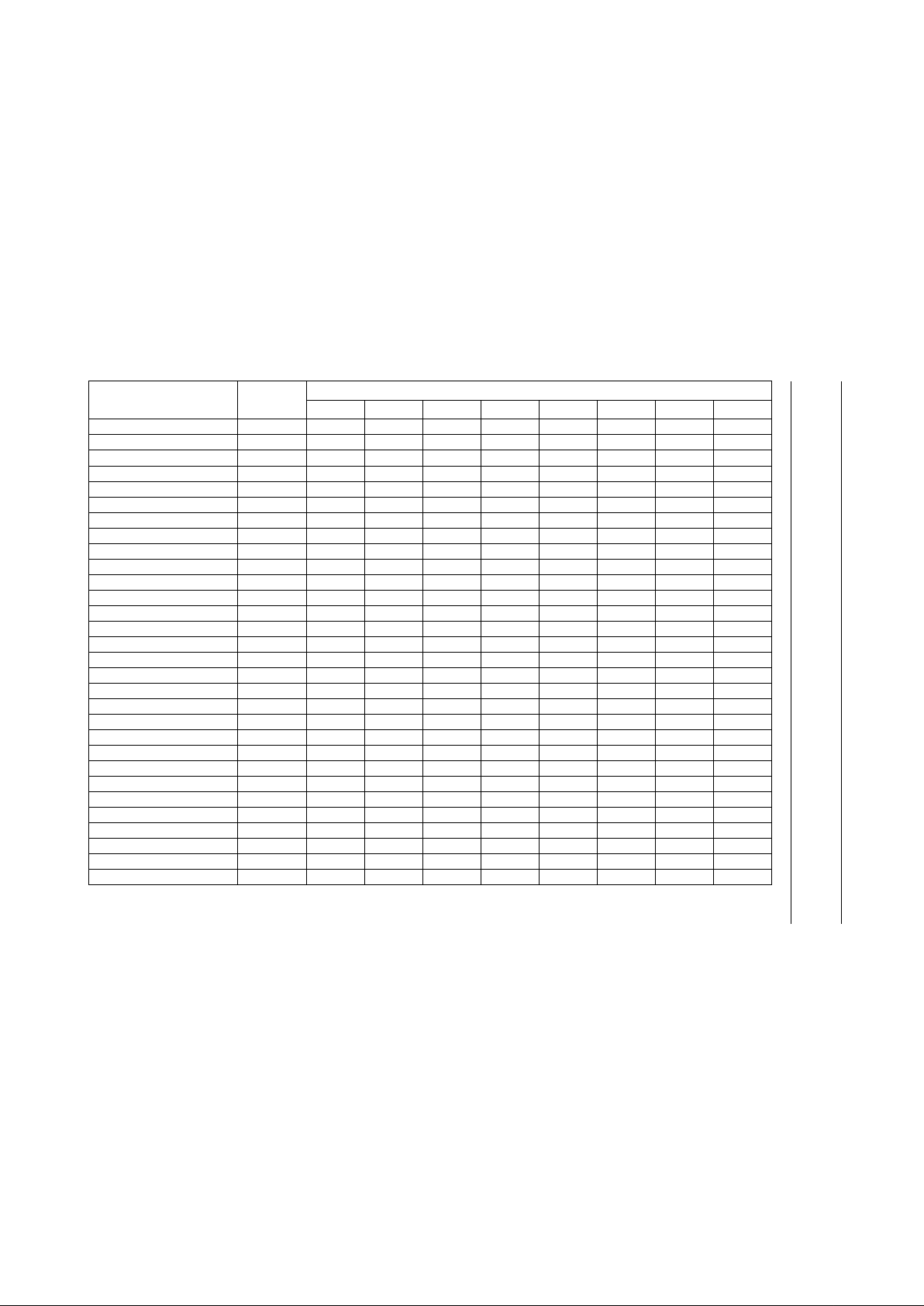

QUICK REFERENCE DATA

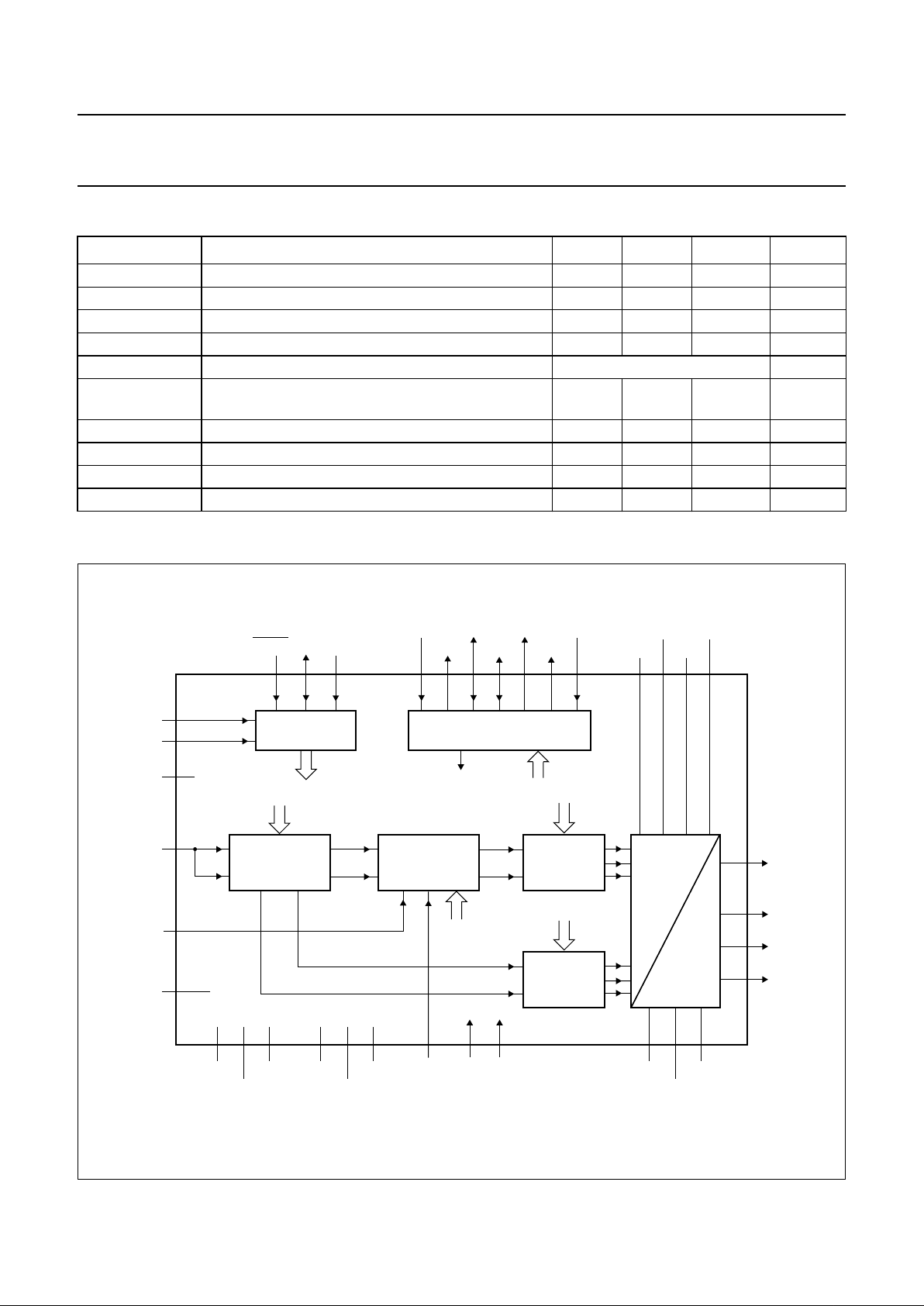

BLOCK DIAGRAM

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DDA

analog supply voltage 3.15 3.3 3.45 V

V

DDD

digital supply voltage 3.0 3.3 3.6 V

I

DDA

analog supply current − 77 100 mA

I

DDD

digital supply current − 37 46 mA

V

i

input signal voltage levels TTL compatible

V

o(p-p)

analog output signal voltages Y, C and CVBS

without load (peak-to-peak value)

1.30 1.45 1.55 V

R

L

load resistance 75 − 300 Ω

LE

lf(i)

low frequency integral linearity error −−±3 LSB

LE

lf(d)

low frequency differential linearity error −−±1 LSB

T

amb

ambient temperature 0 − 70 °C

Fig.1 Block diagram.

handbook, full pagewidth

I2C-BUS

INTERFACE

DATA

MANAGER

ENCODER

SYNC/CLOCK

OUTPUT

INTERFACE

D

A

40 42 41

7

8433734

35 4

MP7

to

MP0

TTX

V

DD(I2C)

19

30

23

26

RESET SDA SCL

RCV1

RCV2

TTXRQ

XCLK

XTAL

XTALI

LLC1

CVBS

RED

GREEN

29

BLUE

I2C-bus

control

I2C-bus

control

I2C-bus

control

I

2

C-bus

control

I

2

C-bus

control

5

V

SSD1

18

V

SSD2

38

V

SSD3

6

V

DDD1

17

V

DDD2

39

V

DDD3

22

V

SSA1

32

V

SSA2

33

V

SSA3

25

V

DDA1

28

V

DDA2

31

V

DDA3

36

V

DDA4

RTCI

23

SP AP

clock

and timing

Y

Y

C

RGB

PROCESSOR

I2C-bus

control

Y

CbCr

CbCr

44

20

SA

21

RES

1

n.c.

24, 27

9 to 16

MP1

MP2

MHB498

SAA7126H

SAA7127H

1999 May 31 4

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

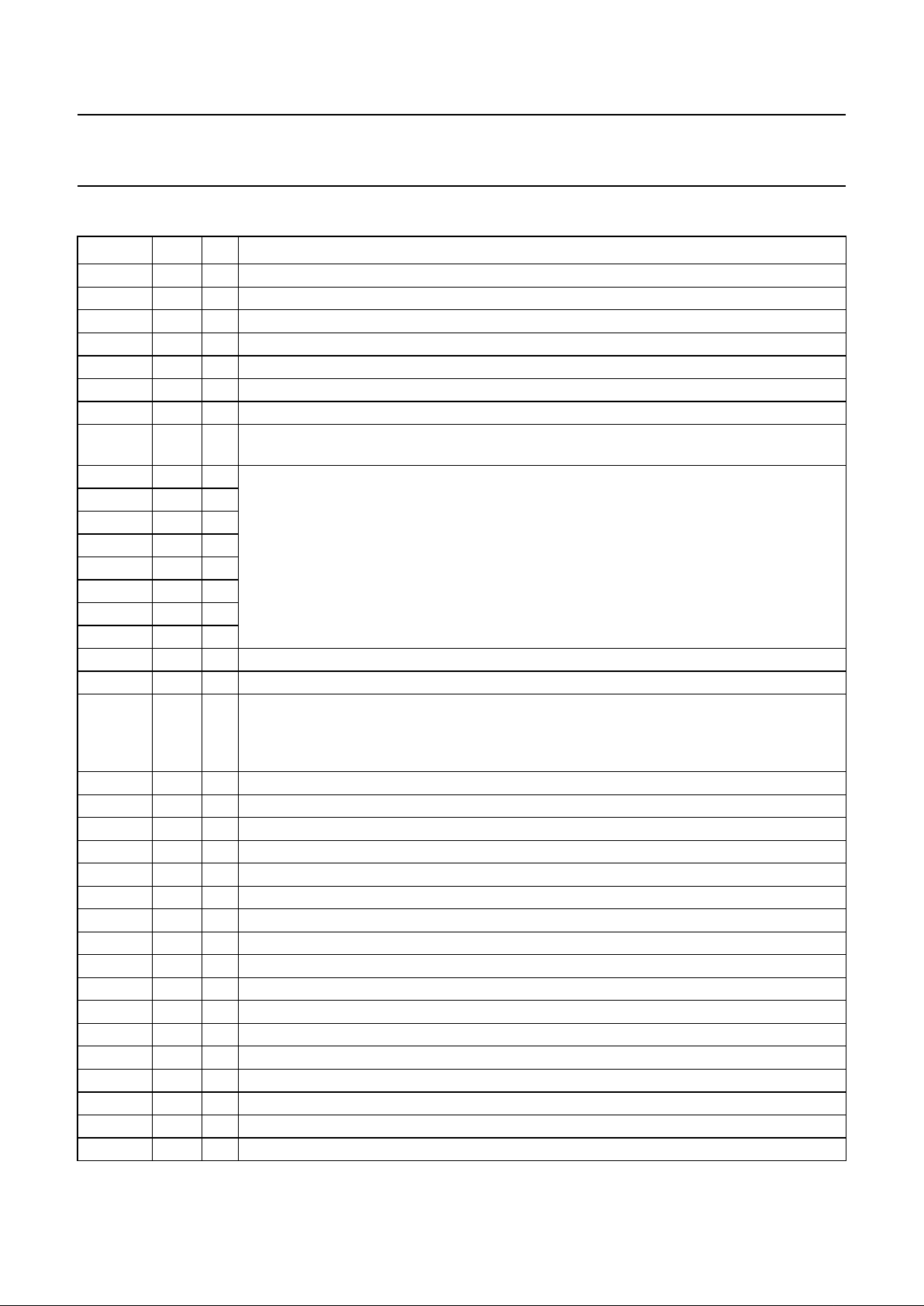

PINNING

SYMBOL TYPE PIN DESCRIPTION

RES − 1 reserved pin; do not connect

SP I 2 test pin; connected to digital ground for normal operation

AP I 3 test pin; connected to digital ground for normal operation

LLC1 I 4 line-locked clock input; this is the 27 MHz master clock

V

SSD1

− 5 digital ground 1

V

DDD1

− 6 digital supply voltage 1

RCV1 I/O 7 raster control 1 for video port; this pin receives/provides a VS/FS/FSEQ signal

RCV2 I/O 8 raster control 2 for video port; this pin provides an HS pulse of programmable length or

receives an HS pulse

MP7 I 9 double-speed 54 MHz MPEG port; it is an input for

“CCIR 656”

style multiplexed Cb-Y-Cr

data; data is sampled on the rising and falling clock edge; data sampled on the rising edge is

then sent to the encoding part of the device; data sampled on the falling edge is sent to the

RGB part of the device (or vice versa, depending on programming)

MP6 I 10

MP5 I 11

MP4 I 12

MP3 I 13

MP2 I 14

MP1 I 15

MP0 I 16

V

DDD2

− 17 digital supply voltage 2

V

SSD2

− 18 digital ground 2

RTCI I 19 real-time control input (I

2

C-bus register SRES = 0): if the LLC1 clock is provided by an

SAA7111 or SAA7151B, RTCI should be connected to the RTCO pin of the respective

decoder to improve the signal quality. Sync reset input (I2C-bus register SRES = 1): a HIGH

impulse resets synchronization of the encoder (first field, first line).

V

DD(I2C)

− 20 sense input for I2C-bus voltage; connect to I2C-bus supply

SA I 21 select I

2

C-bus address; LOW selects slave address 88H, HIGH selects slave address 8CH

V

SSA1

− 22 analog ground 1 for RED (Cr) (C) and GREEN (Y) (VBS) outputs

RED O 23 analog output of RED (Cr) or (C) signal

n.c. − 24 not connected

V

DDA1

− 25 analog supply voltage 1 for RED (Cr) (C) output

GREEN O 26 analog output of GREEN (Y) or (VBS) signal

n.c. − 27 not connected

V

DDA2

− 28 analog supply voltage 2 for GREEN (Y) (VBS) output

BLUE O 29 analog output of BLUE (Cb) or (CVBS) signal

CVBS O 30 analog output of CVBS (CSYNC) or (VBS) signal

V

DDA3

− 31 analog supply voltage 3 for BLUE (Cb) (CVBS) and CVBS (CSYNC) (VBS) outputs

V

SSA2

− 32 analog ground 2 for BLUE (Cb) (CVBS) and CVBS (CSYNC) (VBS) outputs

V

SSA3

− 33 analog ground 3 for the DAC reference ladder and the oscillator

XTAL O 34 crystal oscillator output

XTALI I 35 crystal oscillator input; if the oscillator is not used, this pin should be connected to ground

V

DDA4

− 36 analog supply voltage 4 for the DAC reference ladder and the oscillator

1999 May 31 5

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

XCLK O 37 clock output of the crystal oscillator

V

SSD3

− 38 digital ground 3

V

DDD3

− 39 digital supply voltage 3

RESET I 40 reset input, active LOW. After reset is applied, all digital I/Os are in input mode; PAL black

burst on CVBS, VBS and C; RGB outputs set to lowest voltage. The I2C-bus receiver waits

for the START condition.

SCL I 41 I

2

C-bus serial clock input

SDA I/O 42 I

2

C-bus serial data input/output

TTXRQ O 43 teletext request output, indicating when text bits are requested

TTX I 44 teletext bit stream input

SYMBOL TYPE PIN DESCRIPTION

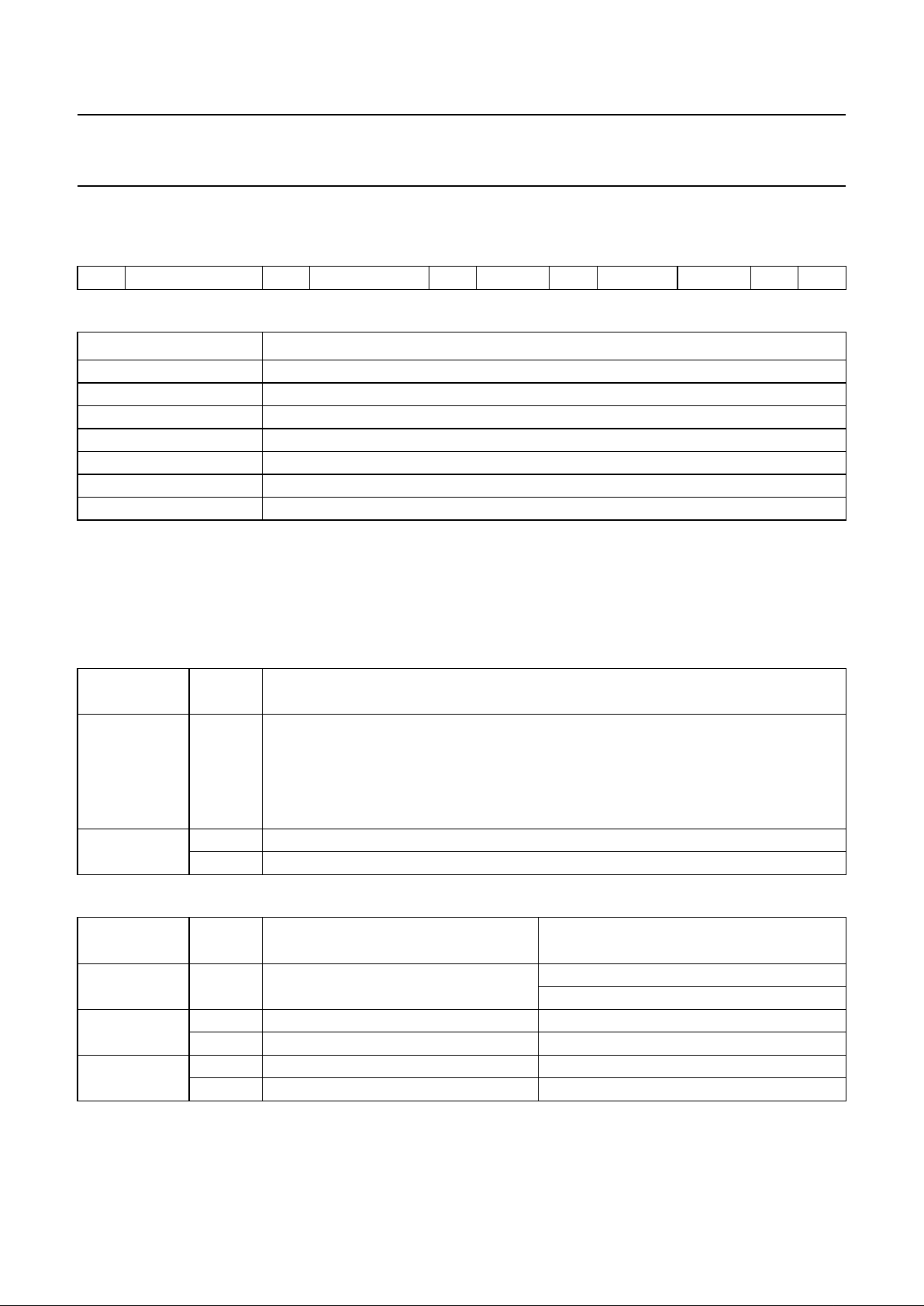

Fig.2 Pin configuration.

handbook, full pagewidth

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

SAA7126H

SAA7127H

MHB499

V

SSA3

V

SSA2

V

DDA3

CVBS

V

DDA2

n.c.

GREEN

V

DDA1

n.c.

RED

RES

SP

AP

LLC1

V

SSD1

V

DDD1

RCV2

MP7

MP5

BLUE

TTXRQ

SDA

SCL

RESET

V

DDD3

V

SSD3

V

DDA4

XTALI

XTAL

TTX

XCLK

MP3

MP2

MP1

MP0

V

DDD2

V

SSD2

V

DD(I2C)

SA

V

SSA1

MP4

RTCI

RCV1

MP6

1999 May 31 6

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

FUNCTIONAL DESCRIPTION

The digital video encoder encodes digital luminance and

colour difference signals into analog CVBS, S-video and

simultaneously RGB or Cr-Y-Cb signals. NTSC-M, PAL

B/G and sub-standards are supported.

Both interlaced and non-interlaced operation is possible

for all standards.

The basic encoder function consists of subcarrier

generation, colour modulation and insertion of

synchronization signals. Luminance and chrominance

signals are filtered in accordance with the standard

requirements of

“RS-170-A”

and

“ITU-R BT.470-3”

.

For ease of analog post filtering the signals are twice

oversampled with respect to the pixel clock before

digital-to-analog conversion.

The total filter transfer characteristics are illustrated in

Figs 3 to 8. The DACs for Y, C and CVBS are realized with

full 10-bit resolution; 9-bit resolution for RGB output.

The Cr-Y-Cb to RGB dematrix can be bypassed optionally

in order to provide the upsampled Cr-Y-Cb input signals.

The 8-bit multiplexed Cb-Y-Cr formats are

“CCIR 656”

(D1 format) compatible, but the SAV and EAV codes can

be decoded optionally; when the device is operated in

slave mode. Two independent data streams can be

processed, one latched by the rising edge of LLC1, the

other latched by the falling edge of LLC1. The purpose of

that is e.g. to forward one of the data streams containing

both video and On Screen Display (OSD) information to

the RGB outputs, and the other stream containing video

only to the encoded outputs CVBS and S-video.

For optimum display of RGB signals through a

euro-connector TV set, an early composite sync pulse (up

to 31LLC1 clock periods) can be provided optionally on the

CVBS output.

It is also possible to connect a Philips digital video decoder

(SAA7111, SAA7711A, SAA7112 or SAA7151B) to the

SAA7126H; SAA7127H. Information concerning the actual

subcarrier, PAL-ID and (with SAA7111 and newer types)

definite subcarrier phase can be inserted via the RTCI pin,

connected to the RTCO pin of a decoder.

The SAA7126H; SAA7127H synthesizes all necessary

internal signals, colour subcarrier frequency and

synchronization signals from that clock.

Wide screen signalling data can be loaded via the I2C-bus

and is inserted into line 23 for standards using a 50 Hz

field rate.

VPS data for program dependent automatic start and stop

of such featured VCR’s is loadable via the I

2

C-bus.

The IC also contains closed caption and extended data

services encoding (line 21), and supports anti-taping

signal generation in accordance with Macrovision. It is also

possible to load data for copy generation management

system into line 20 of every field (525/60 line counting).

A number of possibilities are provided for setting different

video parameters such as:

• Black and blanking level control

• Colour subcarrier frequency

• Variable burst amplitude etc.

During reset (RESET = LOW) and after reset is released,

all digital I/O stages are set to the input mode and the

encoder is set to PAL mode and outputs a ‘black burst’

signal on CVBS and S-video outputs, while RGB outputs

are set to their lowest output voltages. A reset forces the

I2C-bus interface to abort any running bus transfer.

Data manager

In the data manager, alternatively to the external video

data, a pre-defined colour look-up table located in this

block can be read out in a pre-defined sequence (8 steps

per active video line), achieving a colour bar test pattern

generator without need for an external data source.

Encoder

V

IDEO PATH

The encoder generates out of Y, U and V baseband

signals luminance and colour subcarrier output signals,

suitable for use as CVBS or separate Y and C signals.

Luminance is modified in gain and in offset (latter

programmable in a certain range to enable different black

level set-ups). After insertion of a fixed synchronization

pulse tip level, in accordance with standard composite

synchronization schemes, a blanking level can be set.

Other manipulations used for the Macrovision anti-taping

process such as additional insertion of AGC super-white

pulses (programmable in height) are supported by

SAA7126H only.

In order to enable easy analog post filtering, luminance is

interpolated from 13.5 MHz data rate to 27 MHz data rate,

providing luminance in 10-bit resolution. The transfer

characteristic of the luminance interpolation filter are

illustrated in Figs 5 and 6. Appropriate transients at

start/end of active video and for synchronization pulses

are ensured.

1999 May 31 7

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

Chrominance is modified in gain (programmable

separately for U and V), standard dependent burst is

inserted, before baseband colour signals are interpolated

from a 6.75 MHz data rate to a 27 MHz data rate. One of

the interpolation stages can be bypassed, thus providing a

higher colour bandwidth, which can be made use of for

Y and C output. The transfer characteristics of the

chrominance interpolation filter are illustrated in

Figs 3 and 4.

The amplitude, beginning and ending of the inserted burst,

is programmable in a certain range that is suitable for

standard signals and for special effects. Behind the

succeeding quadrature modulator, colour in 10-bit

resolution is provided on the subcarrier.

The numeric ratio between the Y and C outputs is in

accordance with set standards.

T

ELETEXT INSERTION AND ENCODING

Pin TTX receives a WST or NABTS teletext bitstream

sampled at the LLC clock. Two protocols are provided: at

each rising edge of output signal (TTXRQ) a single teletext

bit has to be provided after a programmable delay at input

pin TTX. Or: the signal TTXRQ performs only a single

LOW-to-HIGH transition and remains at HIGH level for

360, 296 or 288 teletext bits, depending on the chosen

standard.

Phase variant interpolation is achieved on this bitstream in

the internal teletext encoder, providing sufficient small

phase jitter on the output text lines.

TTXRQ provides a fully programmable request signal to

the teletext source, indicating the insertion period of

bitstream at lines which are selectable independently for

both fields. The internal insertion window for text is set

to 360 (PAL-WST), 296 (NTSC-WST) or 288 (NABTS)

teletext bits including clock run-in bits. The protocol and

timing are illustrated in Fig.14.

V

IDEO PROGRAMMING SYSTEM (VPS) ENCODING

Five bytes of VPS information can be loaded via the

I2C-bus and will be encoded in the appropriate format into

line 16.

C

LOSED CAPTION ENCODER

Using this circuit, data in accordance with the specification

of closed caption or extended data service, delivered by

the control interface, can be encoded (line 21).

Two dedicated pairs of bytes (two bytes per field), each

pair preceded by run-in clocks and framing code, are

possible.

The actual line number where data is to be encoded in, can

be modified in a certain range.

The data clock frequency is in accordance with the

definition for NTSC-M standard 32 times horizontal line

frequency.

Data LOW at the output of the DACs corresponds to 0 IRE,

data HIGH at the output of the DACs corresponds to

approximately 50 IRE.

It is also possible to encode closed caption data for 50 Hz

field frequencies at 32 times the horizontal line frequency.

ANTI-TAPING (SAA7126H ONLY)

For more information contact your nearest Philips

Semiconductors sales office.

RGB processor

This block contains a dematrix in order to produce red,

green and blue signals to be fed to a SCART plug.

Before Y, Cb and Cr signals are de-matrixed, individual

gain adjustment for Y and colour difference signals and

2 times oversampling for luminance and 4 times

oversampling for colour difference signals is performed.

The transfer curves of luminance and colour difference

components of RGB are illustrated in Figs 7 and 8.

Output interface/DACs

In the output interface, encoded Y and C signals are

converted from digital-to-analog in a 10-bit resolution.

Y and C signals are also combined to a 10-bit CVBS

signal.

The CVBS output occurs with the same processing delay

(equal to 51 LLC clock periods, measured from MP input

to the analog outputs) as the Y, C and RGB outputs.

Absolute amplitude at the input of the DAC for CVBS is

reduced by

15

⁄16 with respect to Y and C DACs to make

maximum use of conversion ranges.

Red, green and blue signals are also converted from

digital-to-analog, each providing a 9-bit resolution.

Outputs of the DACs can be set together via software

control to minimum output voltage (approximately 0.2 V

DC) for either purpose. Alternatively, the buffers can be

switched into 3-state output condition; this allows for ‘wired

AND’ing with other 3-state outputs and can also be used

as a power-save mode.

1999 May 31 8

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

Synchronization

The synchronization of the SAA7126H; SAA7127H is able

to operate in two modes; slave mode and master mode.

In master mode (see Fig.10), the circuit generates all

necessary timings in the video signal itself, and it can

provide timing signals at the RCV1 and RCV2 ports.

In slave mode, it accepts timing information either from the

RCV pins or from the embedded timing data of the

CCIR 656 data stream.

For the SAA7126H; SAA7127H, the only difference

between master and slave mode is that it ignores the

timing information at its inputs in master mode. Thus, if in

slave mode, any timing information is missing, the IC will

continue running free without a visible effect. But there

must not be any additional pulses (with wrong phase)

because the circuit will not ignore them.

In slave mode (see Fig.9), an interface circuit decides,

which signal is expected at the RCV1 port and which

information is taken from its active slope. The polarity can

be chosen, if PRCV1 is logic 0 the rising slope will be

active.

The signal can be:

• A Vertical Sync (VS) pulse; the active slope sets the

vertical phase

• An odd/even signal; the active slope sets the vertical

phase, the internal field flag to odd and optionally sets

the horizontal phase

• A Field Sequence (FSEQ) signal; it marks the first field

of the 4 (NTSC) or 8 (PAL) field sequence. In addition to

the odd/even signal, it also sets the PAL phase and

optionally defines the subcarrier phase.

On the RCV2 port, the IC can provide a horizontal pulse

with programmable start and stop phase; this pulse can be

inhibited in the vertical blanking period to build up, for

example, a composite blanking signal.

The horizontal phase can be set via a separate input

RCV2. In the event of VS pulses at RCV1, this is

mandatory. It is also possible to set the signal path to blank

via this input.

From the CCIR 656 data stream, the SAA7126H;

SAA7127H decodes only the start of the first line in the odd

field. All other information is ignored and may miss. If this

kind of slave mode is active, the RCV pins may be

switched to output mode.

In slave mode, the horizontal trigger phase can be

programmed to any point in the line, the vertical phase

from line 0 to line 15 counted from the first serration pulse

in half line steps.

Whenever a synchronization information cannot be

derived directly from the inputs, the SAA7126H;

SAA7127H will calculate it from the internal horizontal,

vertical and PAL phase. This gives good flexibility with

respect to external synchronization but the circuit does not

suppress illegal settings. In such an event, e.g the

odd/even information may vanish as it does in the

non-interlaced modes.

In master mode, the line lengths are fixed to 1728 clocks

at 50 Hz and 1716 clocks at 60 Hz. To allow

non-interlaced frames, the field lengths can be varied by

±0.5 lines. In the event of non-interlace, the SAA7126H;

SAA7127H does not provide odd/even information and the

output signal does not contain the PAL ‘Bruch sequence’.

At the RCV1 pin the IC can provide:

• A Vertical Sync (VS) signal with 2.5 (50 Hz) or 3 (60 Hz)

lines duration

• An odd/even signal which is LOW in odd fields

• A Field Sequence (FSEQ) signal which is HIGH in the

first field of the 4 or 8 field sequence.

At the RCV2 pin, there is a horizontal pulse of

programmable phase and duration available. This pulse

can be suppressed in the programmable inactive part of a

field giving a composite blank signal.

The directions and polarities of the RCV ports can be

chosen independently. Timing references can be found in

Tables 29 and 37.

Clock

The input at LLC1 can either be an external clock source

or the buffered on-chip clock XCLK. The internal crystal

oscillator can be run with either a 3rd-harmonic or a

fundamental crystal.

I

2

C-bus interface

The I2C-bus interface is a standard slave transceiver,

supporting 7-bit slave addresses and 400 kbits/s

guaranteed transfer rate. It uses 8-bit subaddressing with

an auto-increment function. All registers are write and

readable, except one read only status byte.

The I2C-bus slave address is defined as 88H with pin 21

(SA) tied LOW and as 8CH with pin 21 (SA) tied HIGH.

1999 May 31 9

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

Input levels and formats

The SAA7126H; SAA7127H expects digital Y, Cb, Cr data

with levels (digital codes) in accordance with

“CCIR 601”

.

For C and CVBS outputs, deviating amplitudes of the

colour difference signals can be compensated by

independent gain control setting, while gain for luminance

is set to predefined values, distinguishable for 7.5 IRE

set-up or without set-up.

The RGB, respectively Cr-Y-Cb path features a gain

setting individually for luminance (GY) and colour

difference signals (GCD).

Reference levels are measured with a colour bar,

100% white, 100% amplitude and 100% saturation.

Table 1

“CCIR 601”

signal component levels

Notes

1. Transformation:

a) R = Y + 1.3707 × (Cr − 128)

b) G = Y − 0.3365 × (Cb − 128) − 0.6982 × (Cr − 128)

c) B = Y + 1.7324 × (Cb − 128).

2. Representation of R, G and B (or Cr, Y and Cb) at the output is 9 bits at 27 MHz.

Table 2 8-bit multiplexed format (similar to

“CCIR 601”

)

COLOUR

SIGNALS

(1)

YCbCrR

(2)

G

(2)

B

(2)

White 235 128 128 235 235 235

Yellow 210 16 146 235 235 16

Cyan 170 166 16 16 235 235

Green 145 54 34 16 235 16

Magenta 106 202 222 235 16 235

Red 81 90 240 235 16 16

Blue 41 240 110 16 16 235

Black 16 128 128 16 16 16

TIME

BITS

01234567

Sample Cb

0

Y

0

Cr

0

Y

1

Cb

2

Y

2

Cr

2

Y

3

Luminance pixel number 0123

Colour pixel number 0 2

1999 May 31 10

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

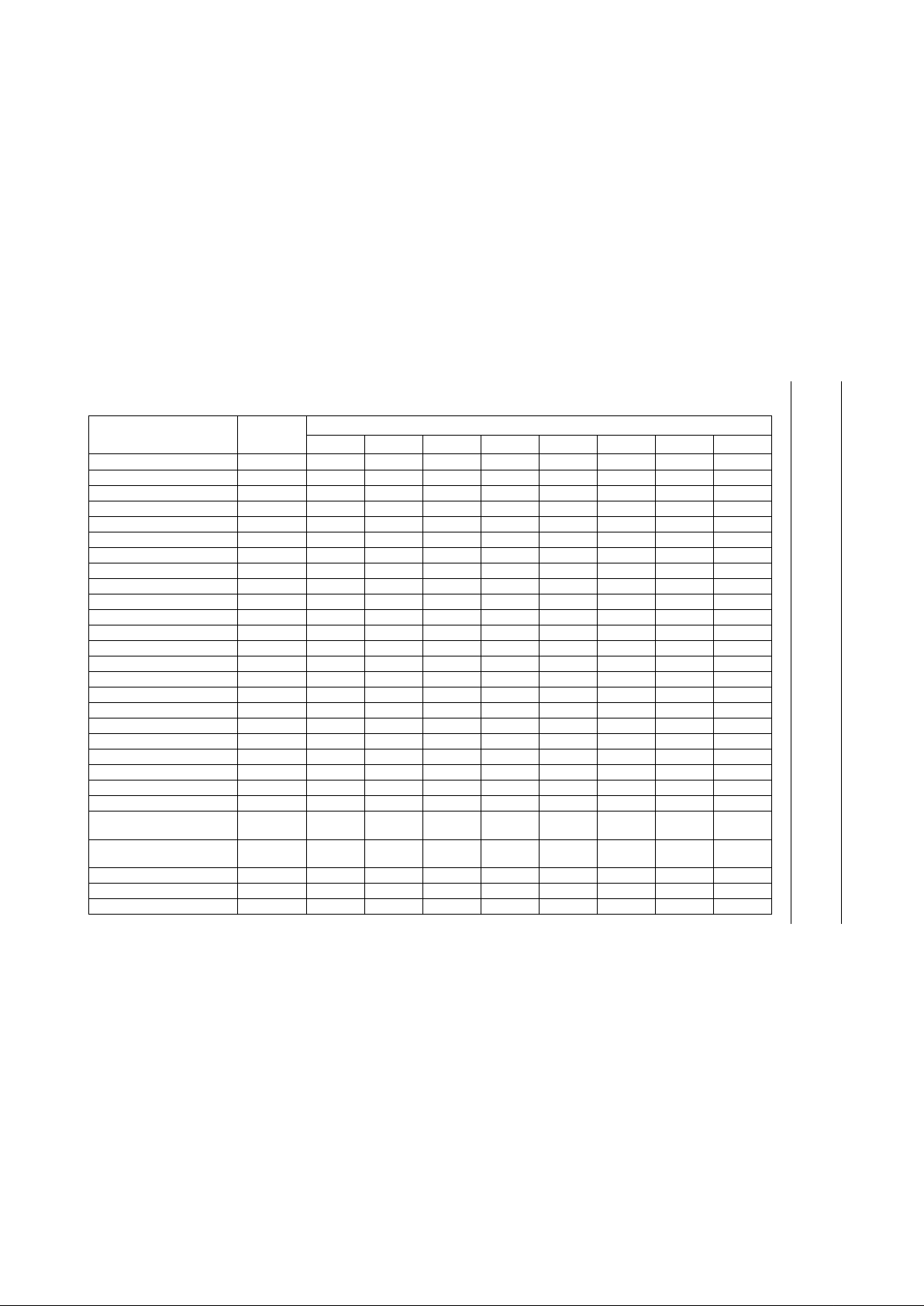

Bit allocation map

Table 3 Slave receiver (slave address 88H)

REGISTER FUNCTION

SUB ADDR

(HEX)

DATA BYTE

(1)

D7 D6 D5 D4 D3 D2 D1 D0

Status byte (read only) 00H VER2 VER1 VER0 CCRDO CCRDE 0 FSEQ O_E

Null 01H to 25H 00000000

Wide screen signal 26H WSS7 WSS6 WSS5 WSS4 WSS3 WSS2 WSS1 WSS0

Wide screen signal 27H WSSON 0 WSS13 WSS12 WSS11 WSS10 WSS9 WSS8

Real-time control, burst start 28H DECCOL DECFIS BS5 BS4 BS3 BS2 BS1 BS0

Sync reset enable, burst end 29H SRES 0 BE5 BE4 BE3 BE2 BE1 BE0

Copy generation 0 2AH CG07 CG06 CG05 CG04 CG03 CG02 CG01 CG00

Copy generation 1 2BH CG15 CG14 CG13 CG12 CG11 CG10 CG09 CG08

CG enable, copy generation 2 2CH CGEN 0 0 0 CG19 CG18 CG17 CG16

Output port control 2DH VBSEN1 VBSEN0 CVBSEN CEN CVBSTRI RTRI GTRI BTRI

Null 2EH to 37H 00000000

Gain luminance for RGB 38H 0 0 0 GY4 GY3 GY2 GY1 GY0

Gain colour difference for RGB 39H 0 0 0 GCD4 GCD3 GCD2 GCD1 GCD0

Input port control 1 3AH CBENB 0 0 SYMP DEMOFF CSYNC MP2C2 MP2C1

VPS enable, input control 2 54H VPSEN CCIRS 0000EDGE2 EDGE1

VPS byte 5 55H VPS57 VPS56 VPS55 VPS54 VPS53 VPS52 VPS51 VPS50

VPS byte 11 56H VPS117 VPS116 VPS115 VPS114 VPS113 VPS112 VPS111 VPS110

VPS byte 12 57H VPS127 VPS126 VPS125 VPS124 VPS123 VPS122 VPS121 VPS120

VPS byte 13 58H VPS137 VPS136 VPS135 VPS134 VPS133 VPS132 VPS131 VPS130

VPS byte 14 59H VPS147 VPS146 VPS145 VPS144 VPS143 VPS142 VPS141 VPS140

Chrominance phase 5AH CHPS7 CHPS6 CHPS5 CHPS4 CHPS3 CHPS2 CHPS1 CHPS0

Gain U 5BH GAINU7 GAINU6 GAINU5 GAINU4 GAINU3 GAINU2 GAINU1 GAINU0

Gain V 5CH GAINV7 GAINV6 GAINV5 GAINV4 GAINV3 GAINV2 GAINV1 GAINV0

Gain U MSB, real-time control,

black level

5DH GAINU8 DECOE BLCKL5 BLCKL4 BLCKL3 BLCKL2 BLCKL1 BLCKL0

Gain V MSB, real-time

control, blanking level

5EH GAINV8 DECPH BLNNL5 BLNNL4 BLNNL3 BLNNL2 BLNNL1 BLNNL0

CCR, blanking level VBI 5FH CCRS1 CCRS0 BLNVB5 BLNVB4 BLNVB3 BLNVB2 BLNVB1 BLNVB0

Null 60H 00000000

Standard control 61H DOWNB DOWNA INPI YGS 0 SCBW PAL FISE

1999 May 31 11

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

Note

1. All bits labelled ‘0’ are reserved. They must be programmed with logic 0.

RTC enable, burst amplitude 62H RTCE BSTA6 BSTA5 BSTA4 BSTA3 BSTA2 BSTA1 BSTA0

Subcarrier 0 63H FSC07 FSC06 FSC05 FSC04 FSC03 FSC02 FSC01 FSC00

Subcarrier 1 64H FSC15 FSC14 FSC13 FSC12 FSC11 FSC10 FSC09 FSC08

Subcarrier 2 65H FSC23 FSC22 FSC21 FSC20 FSC19 FSC18 FSC17 FSC16

Subcarrier 3 66H FSC31 FSC30 FSC29 FSC28 FSC27 FSC26 FSC25 FSC24

Line 21 odd 0 67H L21O07 L21O06 L21O05 L21O04 L21O03 L21O02 L21O01 L21O00

Line 21 odd 1 68H L21O17 L21O16 L21O15 L21O14 L21O13 L21O12 L21O11 L21O10

Line 21 even 0 69H L21E07 L21E06 L21E05 L21E04 L21E03 L21E02 L21E01 L21E00

Line 21 even 1 6AH L21E17 L21E16 L21E15 L21E14 L21E13 L21E12 L21E11 L21E10

RCV port control 6BH SRCV11 SRCV10 TRCV2 ORCV1 PRCV1 CBLF ORCV2 PRCV2

Trigger control 6CH HTRIG7 HTRIG6 HTRIG5 HTRIG4 HTRIG3 HTRIG2 HTRIG1 HTRIG0

Trigger control 6DH HTRIG10 HTRIG9 HTRIG8 VTRIG4 VTRIG3 VTRIG2 VTRIG1 VTRIG0

Multi control 6EH SBLBN BLCKON PHRES1 PHRES0 LDEL1 LDEL0 FLC1 FLCO

Closed caption, teletext enable 6FH CCEN1 CCEN0 TTXEN SCCLN4 SCCLN3 SCCLN2 SCCLN1 SCCLN0

RCV2 output start 70H RCV2S7 RCV2S6 RCV2S5 RCV2S4 RCV2S3 RCV2S2 RCV2S1 RCV2S0

RCV2 output end 71H RCV2E7 RCV2E6 RCV2E5 RCV2E4 RCV2E3 RCV2E2 RCV2E1 RCV2E0

MSBs RCV2 output 72H 0 RCV2E10 RCV2E9 RCV2E8 0 RCV2S10 RCV2S9 RCV2S8

TTX request H start 73H TTXHS7 TTXHS6 TTXHS5 TTXHS4 TTXHS3 TTXHS2 TTXHS1 TTXHS0

TTX request H delay, length 74H TTXHL3 TTXHL2 TTXHL1 TTXHL0 TTXHD3 TTXHD2 TTXHD1 TTXHD0

CSYNC advance, Vsync shift 75H CSYNCA4 CSYNCA3 CSYNCA2 CSYNCA1 CSYNCA0 VS_S2 VS_S1 VS_S0

TTX odd request vertical start 76H TTXOVS7 TTXOVS6 TTXOVS5 TTXOVS4 TTXOVS3 TTXOVS2 TTXOVS1 TTXOVS0

TTX odd request vertical end 77H TTXOVE7 TTXOVE6 TTXOVE5 TTXOVE4 TTXOVE3 TTXOVE2 TTXOVE1 TTXOVE0

TTX even request vertical start 78H TTXEVS7 TTXEVS6 TTXEVS5 TTXEVS4 TTXEVS3 TTXEVS2 TTXEVS1 TTXEVS0

TTX even request vertical end 79H TTXEVE7 TTXEVE6 TTXEVE5 TTXEVE4 TTXEVE3 TTXEVE2 TTXEVE1 TTXEVE0

First active line 7AH FAL7 FAL6 FAL5 FAL4 FAL3 FAL2 FAL1 FAL0

Last active line 7BH LAL7 LAL6 LAL5 LAL4 LAL3 LAL2 LAL1 LAL0

TTX mode, MSB vertical 7CH TTX60 LAL8 TTXO FAL8 TTXEVE8 TTXOVE8 TTXEVS8 TTXOVS8

Null 7DH 00000000

Disable TTX line 7EH LINE12 LINE11 LINE10 LINE9 LINE8 LINE7 LINE6 LINE5

Disable TTX line 7FH LINE20 LINE19 LINE18 LINE17 LINE16 LINE15 LINE14 LINE13

REGISTER FUNCTION

SUB ADDR

(HEX)

DATA BYTE

(1)

D7 D6 D5 D4 D3 D2 D1 D0

1999 May 31 12

Philips Semiconductors Product specification

Digital video encoder SAA7126H; SAA7127H

I2C-bus format

Table 4 I

2

C-bus address; see Table 5

Table 5 Explanation of Table 4

Notes

1. X is the read/write control bit; X = logic 0 is order to write; X = logic 1 is order to read.

2. If more than 1 byte of DATA is transmitted, then auto-increment of the subaddress is performed.

Slave receiver

Table 6 Subaddresses 26H and 27H

Table 7 Subaddress 28H

S SLAVE ADDRESS ACK SUBADDRESS ACK DATA 0 ACK -------- DATA n ACK P

PART DESCRIPTION

S START condition

Slave address 1000100X or 1 0 0 0 1 1 0 X; note 1

ACK acknowledge, generated by the slave

Subaddress; note 2 subaddress byte

DATA data byte

-------- continued data bytes and ACKs

P STOP condition

DATA BYTE

LOGIC

LEVEL

DESCRIPTION

WSS − wide screen signalling bits

3 to 0 = aspect ratio

7 to 4 = enhanced services

10 to 8 = subtitles

13 to 11 = reserved

WSSON 0 wide screen signalling output is disabled; default after reset

1 wide screen signalling output is enabled

DATA BYTE

LOGIC

LEVEL

DESCRIPTION REMARKS

BS − starting point of burst in clock cycles PAL: BS= 33 (21H); default after reset

NTSC: BS = 25 (19H)

DECCOL 0 disable colour detection bit of RTCI input

1 enable colour detection bit of RTCI input bit RTCE must be set to logic 1 (see Fig.13)

DECFIS 0 field sequence as FISE in subaddress 61

1 field sequence as FISE bit in RTCI input bit RTCE must be set to logic 1 (see Fig.13)

Loading...

Loading...