DATA SH EET

Preliminary specification

File under Integrated Circuits, IC02

1997 Jun 10

INTEGRATED CIRCUITS

SAA4945H

LIne MEmory noise Reduction IC

(LIMERIC)

1997 Jun 10 2

Philips Semiconductors Preliminary specification

LIne MEmory noise Reduction IC

(LIMERIC)

SAA4945H

FEATURES

• 2-D adaptive vertically recursive noise reduction

• Noise reduction for Y, U and V signals in 4 : 1 : 1 format

• Single 5 V ±10% power supply

• Communication by means of serial communication

protocol 83C654 (SNERT bus)

• Via SNERT bus, 10 different types of noise reduction

selectable; the noise reduction function can also be

disabled

• Phase relation write enable input/output signal

simultaneously switchable over one clock period w.r.t.

input/output samples

• 8-bit wide data processing for Y, U and V; in unsigned

format (Y signal) and in 2’s complement (U and V

signals)

• One fixed line locked clock operation frequency up to

16 MHz (typical)

• Exactly one line delay.

GENERAL DESCRIPTION

The SAA4945H, LIMERIC (LIne MEmory noise Reduction

IC) is a 2-D recursive noise reduction filter for both

luminance and colour difference signals. The noise

reduction is automatically adapted to the global noise level

in the image. Ten different preferences of noise reduction

can be set using a synchronous receiver transmitter bus;

SNERT (Synchronous No parity Eight bit Receive

Transmit) bus. Alternatively, the noise reduction can be

switched off. The LIMERIC is generally placed directly

after the ADC in the feature box and works fully in the 1f

h

(50/60 Hz) domain.

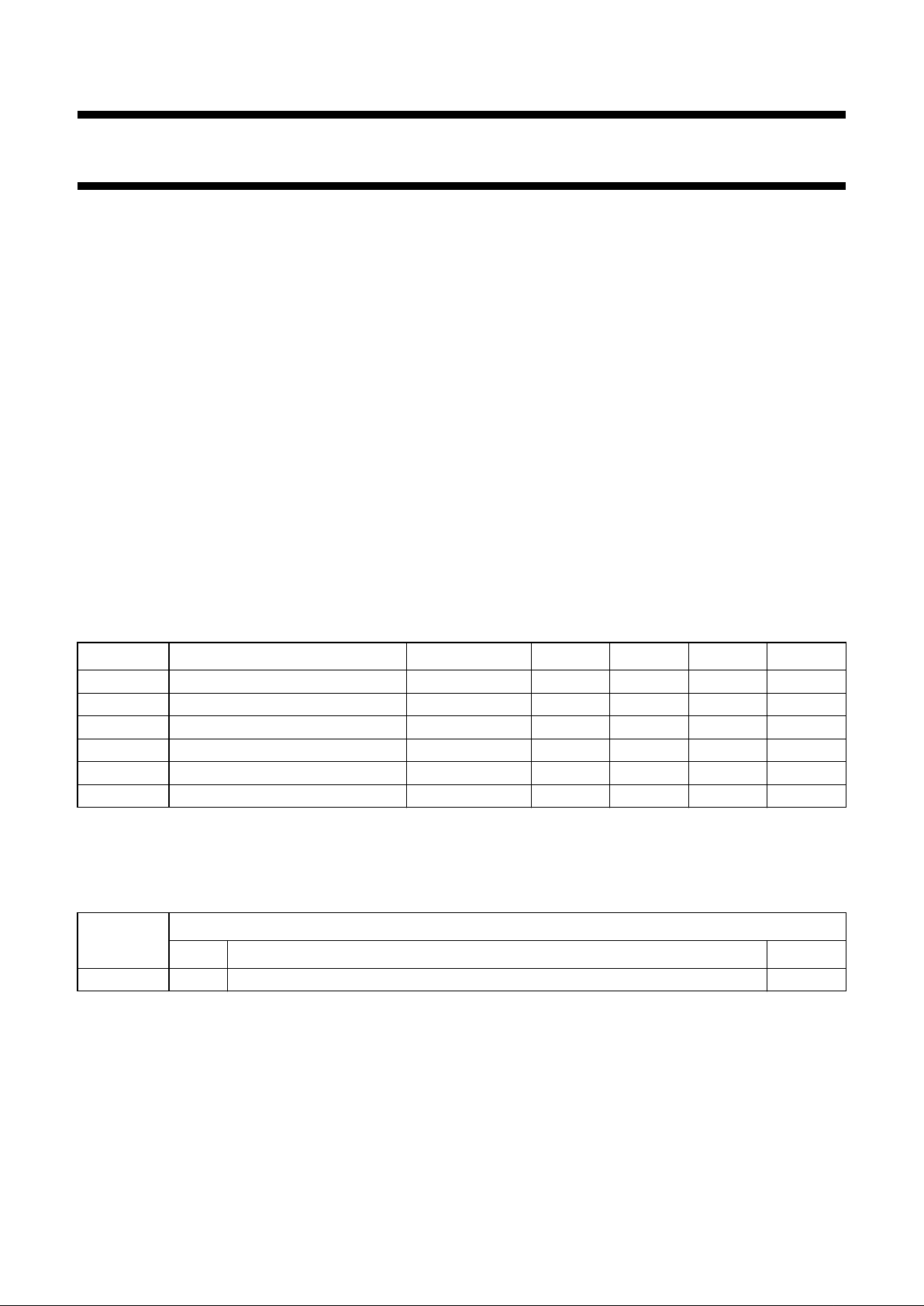

QUICK REFERENCE DATA

Note

1. Maximum number of clocks per line is 1024.

ORDERING INFORMATION

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD

supply voltage (pins 5, 29 and 30) 4.5 5.0 5.5 V

I

DD

supply current − 70 − mA

P power dissipation − 350 − mW

f

CLK

clock frequency ±7%; note 1 10 16 17.1 MHz

f

SNERT

bus clock frequency −−1 MHz

T

amb

operating ambient temperature 0 − 70 °C

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

SAA4945H QFP44 plastic quad flat package; 44 leads (lead length 1.3 mm); body 10 × 10 × 1.75 mm SOT307-2

1997 Jun 10 3

Philips Semiconductors Preliminary specification

LIne MEmory noise Reduction IC

(LIMERIC)

SAA4945H

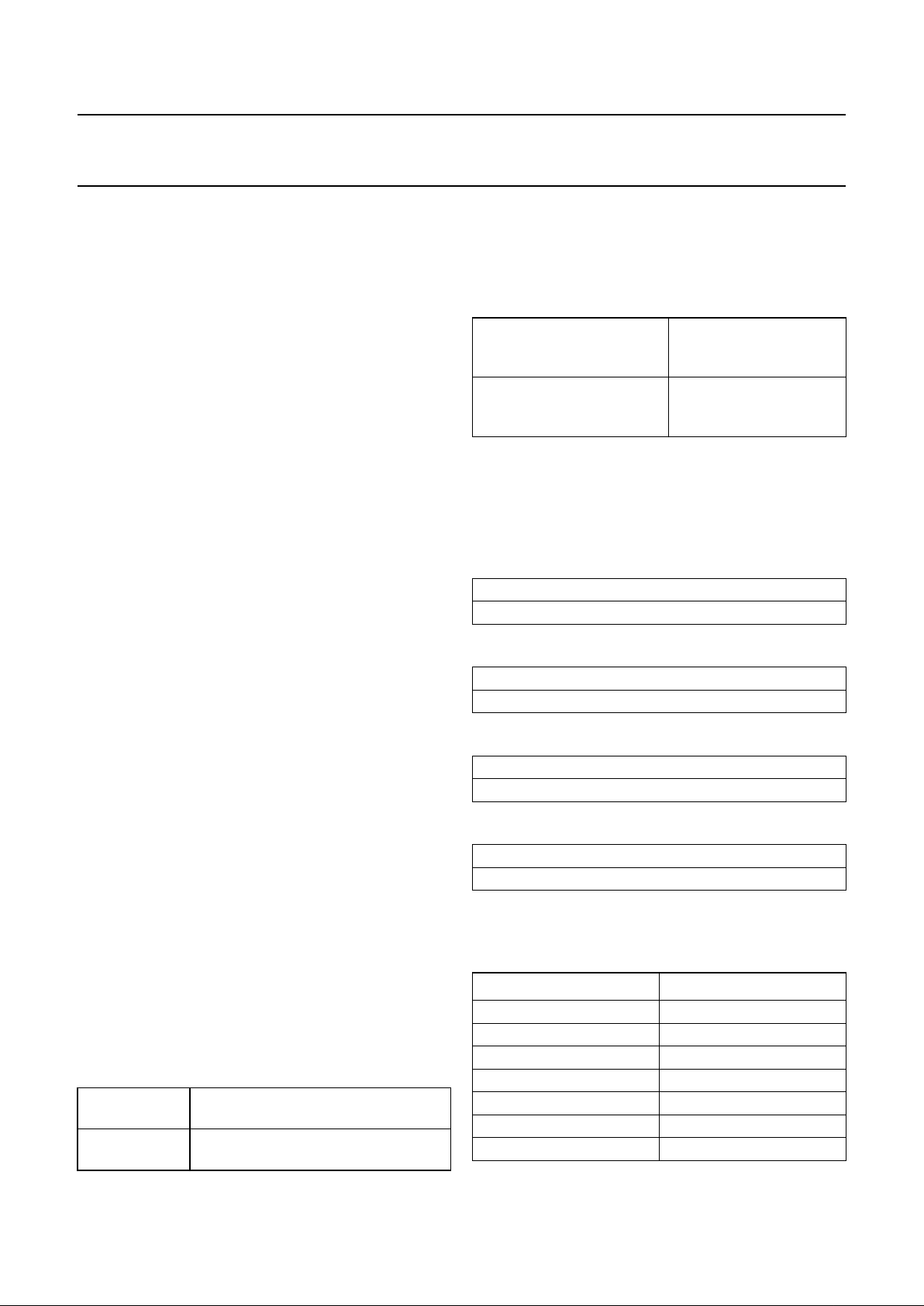

BLOCK DIAGRAM

Fig.1 Block diagram.

handbook, full pagewidth

MGK170

NOISE

REDUCTION

FILTER

NOISE

REDUCTION

FILTER

(MULTIPLEXED)

NOISE

ESTIMATOR

SNERT

INTERFACE

TST0

432

26

38 to 44, 1

36, 37

REFORMATTER

FORMATTER

TEST

CONTROL

TST1

25

TST2

24

31

RAM_Y

N_thr_UV

N_thr_Y

N_thr_UV

TASTE

W

val

YpScale

CONTROL

GND1WE

I

VaCLK

VRST

SNCL

SDNA

internal

control

signals

2221

33

6

GND2

20

GND3

23

GND4

27

GND5

28

GND6

32

19

NTHR

RAM_UV ∆t

8

814 to 7

5

V

DD1

29

V

DD2

30

V

DD3

UO0, U

O1

34, 35

VO0, V

O1

16, 15

UI0, U

I1

18, 17

VI0, V

I1

Y

I0

to Y

I7

Y

O0

to

YO6, Y

O7

WE

O

n.c.

SAA4945H

1997 Jun 10 4

Philips Semiconductors Preliminary specification

LIne MEmory noise Reduction IC

(LIMERIC)

SAA4945H

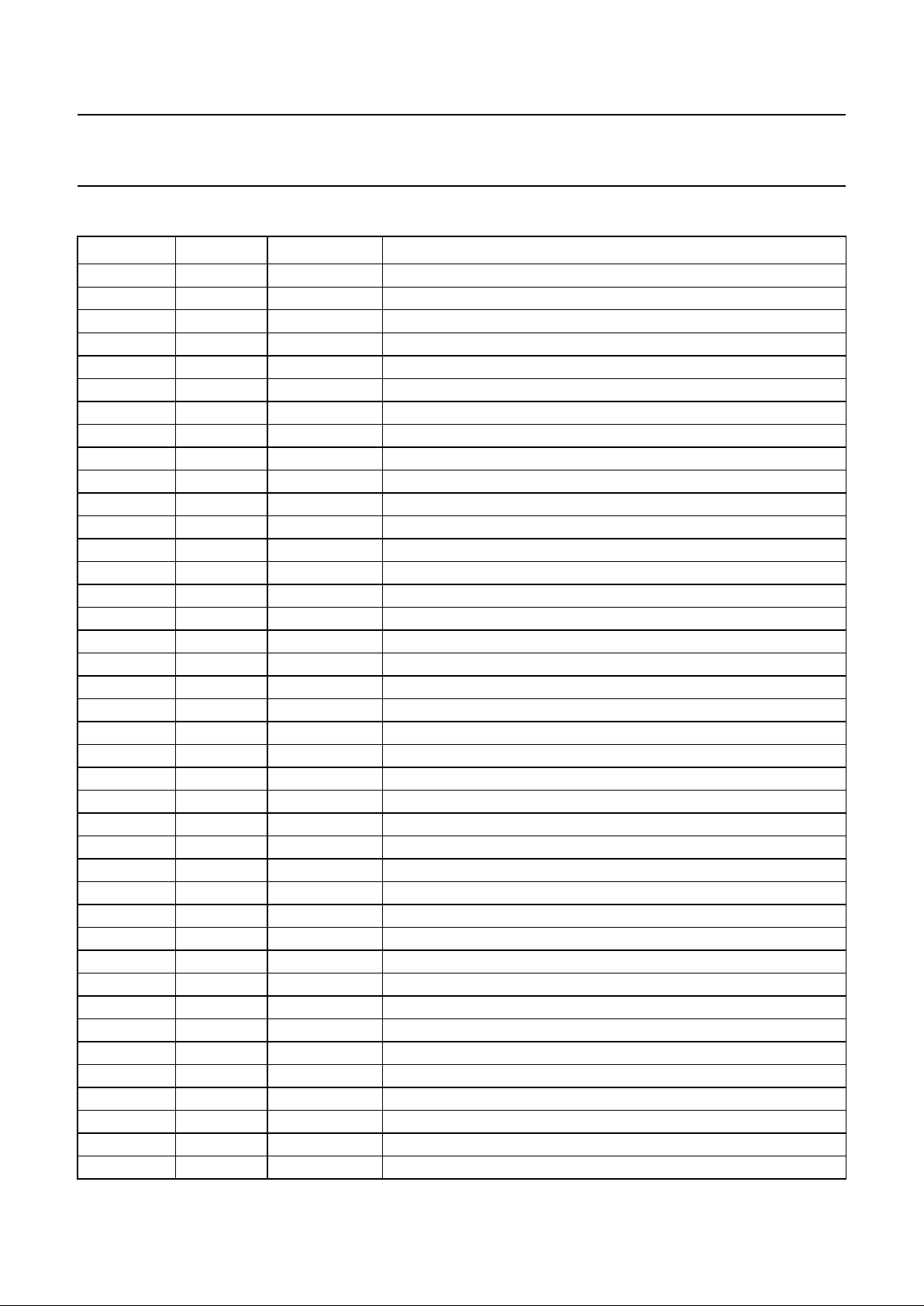

PINNING

SYMBOL PIN TYPE DESCRIPTION

Y

O7

1 output luminance output bit 7

SNDA 2 input/output data from interface SNERT bus

SNCL 3 input clock from interface SNERT bus

VRST 4 input reset in the vertical blanking interval

V

DD1

5 supply supply voltage 1

GND1 6 ground ground 1

Y

I7

7 input luminance input bit 7 from analog-to-digital converter

Y

I6

8 input luminance input bit 6 from analog-to-digital converter

Y

I5

9 input luminance input bit 5 from analog-to-digital converter

Y

I4

10 input luminance input bit 4 from analog-to-digital converter

Y

I3

11 input luminance input bit 3 from analog-to-digital converter

Y

I2

12 input luminance input bit 2 from analog-to-digital converter

Y

I1

13 input luminance input bit 1 from analog-to-digital converter

Y

I0

14 input luminance input bit 0 from analog-to-digital converter

U

I1

15 input U input bit 1 from analog-to-digital converter

U

I0

16 input U input bit 0 from analog-to-digital converter

V

I1

17 input V input bit 1 from analog-to-digital converter

V

I0

18 input V input bit 0 from analog-to-digital converter

CLK 19 input master clock

GND2 20 ground ground 2

WE

I

21 input write enable input

Va 22 input vertical blanking pulse

GND3 23 ground ground 3

TST2 24 input test pin 2

TST1 25 input test pin 1

TST0 26 input test pin 0

GND4 27 ground ground 4

GND5 28 ground ground 5

V

DD2

29 supply supply voltage 2

V

DD3

30 supply supply voltage 3

WE

O

31 output write enable output

GND6 32 ground ground 6

n.c. 33 − not connected

V

O0

34 output V output bit 0

V

O1

35 output V output bit 1

U

O0

36 output U output bit 0

U

O1

37 output U output bit 1

Y

O0

38 output luminance output bit 0

Y

O1

39 output luminance output bit 1

Y

O2

40 output luminance output bit 2

1997 Jun 10 5

Philips Semiconductors Preliminary specification

LIne MEmory noise Reduction IC

(LIMERIC)

SAA4945H

Y

O3

41 output luminance output bit 3

Y

O4

42 output luminance output bit 4

Y

O5

43 output luminance output bit 5

Y

O6

44 output luminance output bit 6

SYMBOL PIN TYPE DESCRIPTION

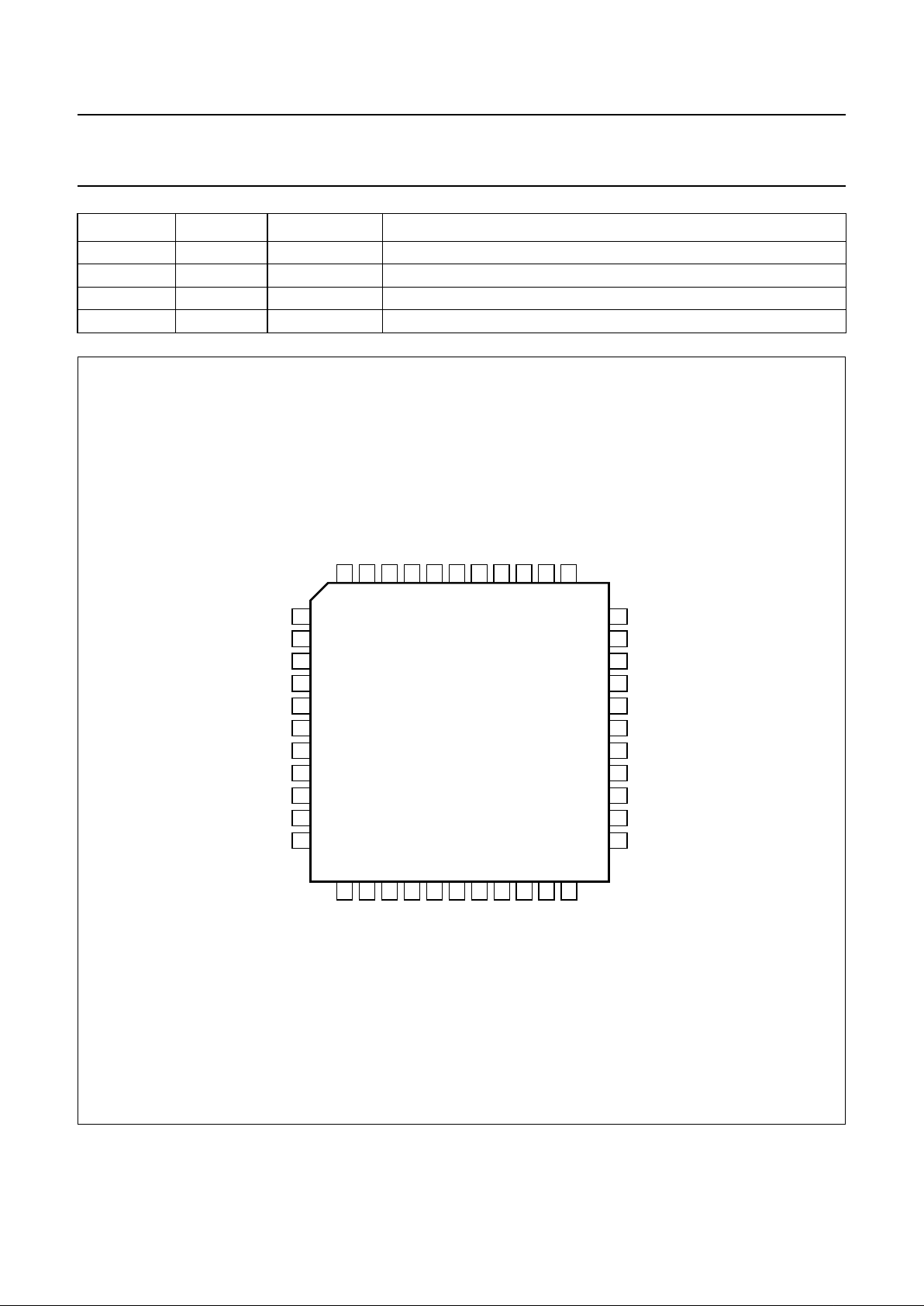

Fig.2 Pin configuration.

handbook, full pagewidth

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

SAA4945H

MGK169

n.c.

GND6

WE

O

V

DD3

GND5

GND4

TST0

TST1

TST2

GND3

Y

O7

SNDA

SNCL

VRST

V

DD1

GND1

Y

I6

Y

I5

Y

I3

V

DD2

YO5YO4YO3YO2YO1Y

O0

UO0VO1V

O0

Y

O6

U

O1

Y

I1

Y

I0

U

I1

U

I0

V

I1

V

I0

GND2

WE

I

Va

Y

I2

CLK

Y

I7

Y

I4

1997 Jun 10 6

Philips Semiconductors Preliminary specification

LIne MEmory noise Reduction IC

(LIMERIC)

SAA4945H

FUNCTIONAL DESCRIPTION

The digital LIMERIC is an effective low noise reduction IC

for luminance and colour difference signals. Noise filtering

is automatically adapted to the global noise level which is

measured within the picture content. The two dimensional

non-linear noise reduction (one for luminance, one for

chrominance) uses only line memory to function.

Furthermore, up to 10 different preferences can be set by

the user.

As shown in Fig.1, the main components of the device are

the noise reduction filter with the line memories (RAM) and

the noise estimator. Other components shown are the

reformatter, formatter, controller and a SNERT bus

transceiver.

Noise reduction filter

Both luminance and chrominance signals are filtered with

vertical recursion. This is produced as the filter receives

both filtered samples from the previous line, and unfiltered

samples from the current line. A new replacement value is

calculated for each sample read from the line memory.

This in turn, is the filtered response value for the reference

input pixel. The reference pixel is then placed at the centre

of the delay-line into which the current (unfiltered) video

line is shifted. Tables 1 to 6 show this as an ‘O’.

Both luminance and colour difference signals are filtered

using the so-called Discriminating AveragingFilter (DAF),

in which filter coefficients are related to the Absolute

Difference (AD) between samples. The filter uses samples

from both present and previous line (using the line delay)

and the result of the filter is stored back in the line memory.

In this way a vertical recursive structure is realized.

The filter coefficients are set depending on the noise

measured by the noise estimator or the NTHR (SNERT

register F9).

C

HROMINANCE FILTER

The basic signal processing for either U or V is via the

same filter. It is used to process both V and U using a

multiplexed operation.

The taps structure of the chrominance filter is as shown in

Table 1.

Table 1 Chrominance processing

X X X X X ← 5 adjacent R − Y samples from the

filtered line

o O o ← 3 adjacent R − Y samples from the

incoming line

LUMINANCE FILTER

The taps structure of the luminance filter is as shown in

Table 2.

Table 2 Luminance processing

A ‘weave’ function is used to reduce any smearing effect

that could occur at edges. As shown in Tables 3 to 6, the

‘weave’ calculates over 4 consecutive lines. The relative

position of the actual pixel changes one position every line.

Table 3 For line 2n

Table 4 For line 2n + 1

Table 5 For line 2n + 2

Table 6 For line 2n + 3

Table 7 Weave configuration

Depending on even and odd fields the ‘weave’ has the

following configuration:

X . . . . X . . . X . . . X . . . . X ← 5 Y samples from the

filtered line (distance 4 / 5

pixel)

o . O . o ← 3 Y samples from the

incoming line (distance 2

pixels)

X . . . . X . . . X . . . X . . . . X

o . O . o

X . . . . X . . . X . . . X . . . . X

. . o . O . o

X . . . . X . . . X . . . X . . . . X

o . O . o

X . . . . X . . . X . . . X . . . . X

o . O . o . .

ODD FIELDS EVEN FIELDS

XX

XX

XX

XX

XX

XX

XX

Loading...

Loading...