Philips sa5214 DATASHEETS

INTEGRATED CIRCUITS

SA5214

Postamplifier with link status indicator

Product specification

Replaces datasheet NE/SA5214 of 1995 Apr 26

IC19 Data Handbook

1998 Oct 07

Philips Semiconductors Product specification

SA5214Postamplifier with link status indicator

DESCRIPTION

The SA5214 is a 75MHz postamplifier system designed to accept

low level high-speed signals. These signals are converted into a

TTL level at the output. The SA5214 can be DC coupled with the

previous transimpedance stage using SA5210, SA5211 or SA5212

transimpedance amplifiers. This “system on a chip” features an

auto-zeroed first stage with noise shaping, a symmetrical limiting

second stage, and a matched rise/fall time TTL output buffer. The

system is user-configurable to provide noise filtering, adjustable

input thresholds and hysteresis. The threshold capability allows the

user to maximize signal-to-noise ratio, insuring a low Bit Error Rate

(BER). An Auto-Zero loop can be used to minimize the number of

external coupling capacitors to one. A signal absent flag indicates

when signals are below threshold. Additionally, the low signal

condition forces the overall TTL output to a logical Low level. User

interaction with this “jamming” system is available. The SA5214 is

packaged in a standard 20-pin surface-mount package and typically

consumes 42mA from a standard 5V supply. The SA5214 is

designed as a companion to the SA5211/5212 transimpedance

amplifiers. These differential preamplifiers may be directly coupled

to the post-amplifier inputs. The SA5212/5214 or SA5211/5214

combinations convert nanoamps of photodetector current into

standard digital TTL levels.

APPLICATIONS

•Fiber optics

•Communication links in Industrial and/or Telecom environment

with high EMI/RFI

•Local Area Networks (LAN)

•Metropolitan Area Networks (MAN)

•Synchronous Optical Networks (SONET)

•RF limiter

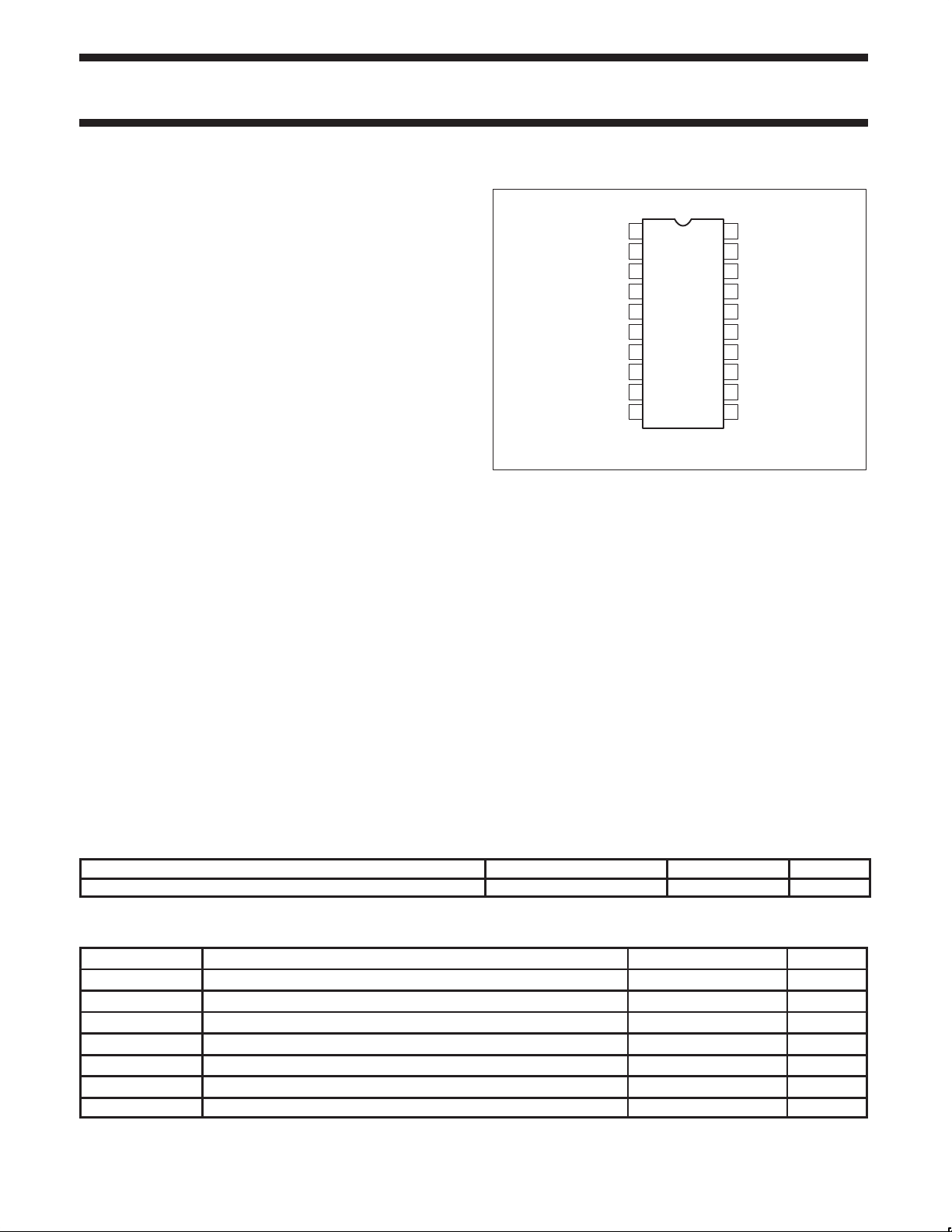

PIN CONFIGURATION

D1 Package

1

LED

PKDET

THRESH

GND

FLAG

JAM

V

CCD

V

CCA

GND

V

OUT

2

3

4

A

5

6

7

8

9

D

10

TOP VIEW

C

NOTE:

1. SOL – Released in large SO package only.

20

19

18

17

16

15

14

13

12

11

IN

1B

IN

1A

C

AZP

C

AZN

OUT

1B

IN

2B

OUT

1A

IN

2A

R

HYST

R

PKDET

SD00349

Figure 1. Pin Configuration

FEATURES

•Postamp for the SA5211/5212 preamplifier family

•Wideband operation: typical 75MHz (100MBaud NRZ)

•Interstage filtering/equalization possible

•Single 5V supply

•Low signal flag

•Low signal output disable

•Link status threshold and hysteresis programmable

•LED driver (normally ON with above threshold signal)

•Fully differential for excellent PSRR

•Auto-zero loop for DC offset cancellation

•2kV ElectroStatic Discharge (ESD) protection

ORDERING INFORMATION

DESCRIPTION TEMPERATURE RANGE ORDER CODE DWG #

20-Pin Plastic Small Outline Large (SOL) Package -40°C to +85°C SA5214D SOT163-1

ABSOLUTE MAXIMUM RATINGS

SYMBOL PARAMETER RATING UNIT

V

CCA

V

CCD

T

A

T

J

T

STG

P

D

V

IJ

1998 Oct 07 853-1657 20142

Power supply +6 V

Power supply +6 V

Operating ambient temperature range -40 to +85 °C

Operating junction temperature range -55 to +150 °C

Storage temperature range -65 to +150 °C

Power dissipation 300 mW

Jam input voltage -0.5 to 5.5 V

2

Philips Semiconductors Product specification

SA5214Postamplifier with link status indicator

PIN DESCRIPTIONS

PIN

SYMBOL DESCRIPTION

NO.

1 LED Output for the LED driver. Open collector output transistor with 125Ω series limiting resistor. An above threshold signal

turns this transistor ON.

2 C

PKDET

3 THRESH Peak detector threshold resistor. The value of this resistor determines the threshold level of the peak detector.

4 GND

5 FLAG Peak detector digital output. When this output is LOW, there is data present above the threshold. This pin is normally

6 JAM Input to inhibit data flow. Sending the pin HIGH forces TTL DATA OUT ON, Pin 10, LOW. This pin is normally connected

7 V

CCD

8 V

CCA

9 GND

10 V

OUT

11 R

PKDET

12 R

HYST

13 IN

2A

14 OUT

15 IN

2B

16 OUT

17 C

AZN

18 C

AZP

19 IN

1A

20 IN

1B

Capacitor for the peak detector. The value of this capacitor determines the detector response time to the signal,

supplementing the internal 10pF capacitor.

Device analog ground pin.

A

connected to the JAM pin and has a TTL fanout of two.

to the FLAG pin and is TTL-compatible.

Power supply pin for the digital portion of the chip.

Power supply pin for the analog portion of the chip.

Device digital ground pin.

D

TTL output pin with a fanout of five.

Peak detector current resistor. The value of this resistor determines the amount of discharge current available to the

peak detector capacitor, C

PKDET

.

Peak detector hysteresis resistor. The value of this resistor determines the amount of hysteresis in the peak detector.

Non-inverting input to amplifier A2.

Non-inverting output of amplifier A1.

1A

Inverting input to amplifier A2.

Inverting output of amplifier A1.

1B

Auto-Zero capacitor pin (Negative terminal). The value of this capacitor determines the low-end frequency response of

the preamp A1.

Auto-Zero capacitor pin (Positive terminal). The value of this capacitor determines the low-end frequency response of the

preamp A1.

Non-inverting input of the preamp A1.

Inverting input of the preamp A1.

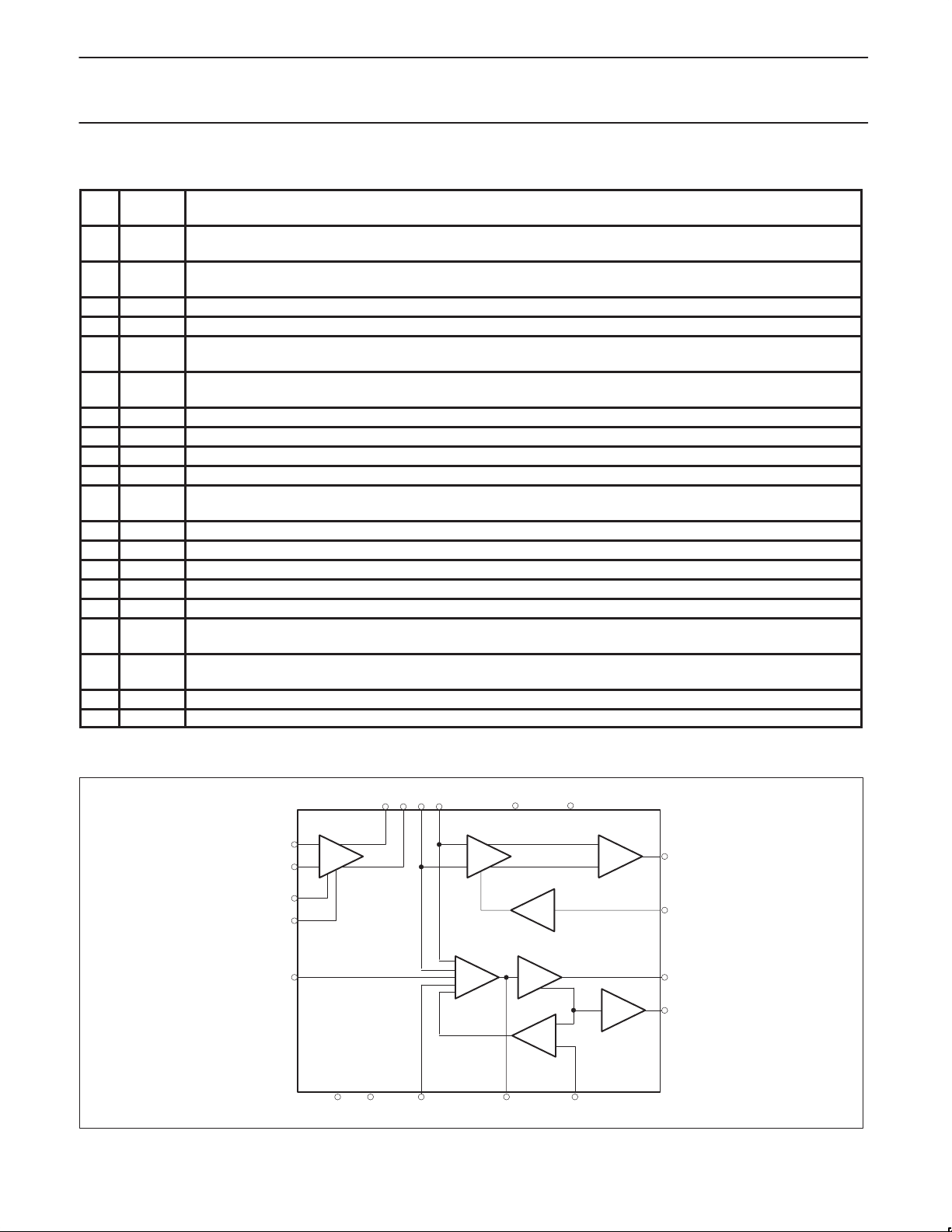

BLOCK DIAGRAM

1998 Oct 07

C

C

R

PKDET

IN

IN

AZP

AZN

1B

1A

OUT

IN

1B

D

2B

16 1514 13

THRESH

OUT

1A

20

A1 A2

19

18

17

11

9

43

GNDAGND

Figure 2. Block Diagram

IN

2A

GATED AMP

PEAK DETECT

A3

C

PKDET

3

V

CCD

A4

HYSTERESIS

2

V

CCA

87

OUTPUT BUFFER

OUTPUT DISABLE

A6

A7

12

R

HYST

A8

A5

LED DRIVER

10

6

5

1

SD00350

V

OUT

JAM

FLAG

LED

Loading...

Loading...