Philips PHC2300 Datasheet

DISCRETE SEMICONDUCTORS

DATA SH EET

PHC2300

Complementary enhancement

mode MOS transistors

Product specification

Supersedes data of 1997 Jun 19

File under Discrete Semiconductors, SC13b

1997 Oct 24

Philips Semiconductors Product specification

Complementary enhancement mode

MOS transistors

FEATURES

• High-speed switching

• No secondary breakdown.

APPLICATIONS

• Universal line interface in telephone sets

• Relay, high-speed and line transformer drivers.

DESCRIPTION

One N-channel and one P-channel enhancement mode

MOS transistor in an 8-pin plastic SOT96-1 (SO8)

package.

CAUTION

The device is supplied in an antistatic package.

The gate-source input must be protected against static

discharge during transport or handling.

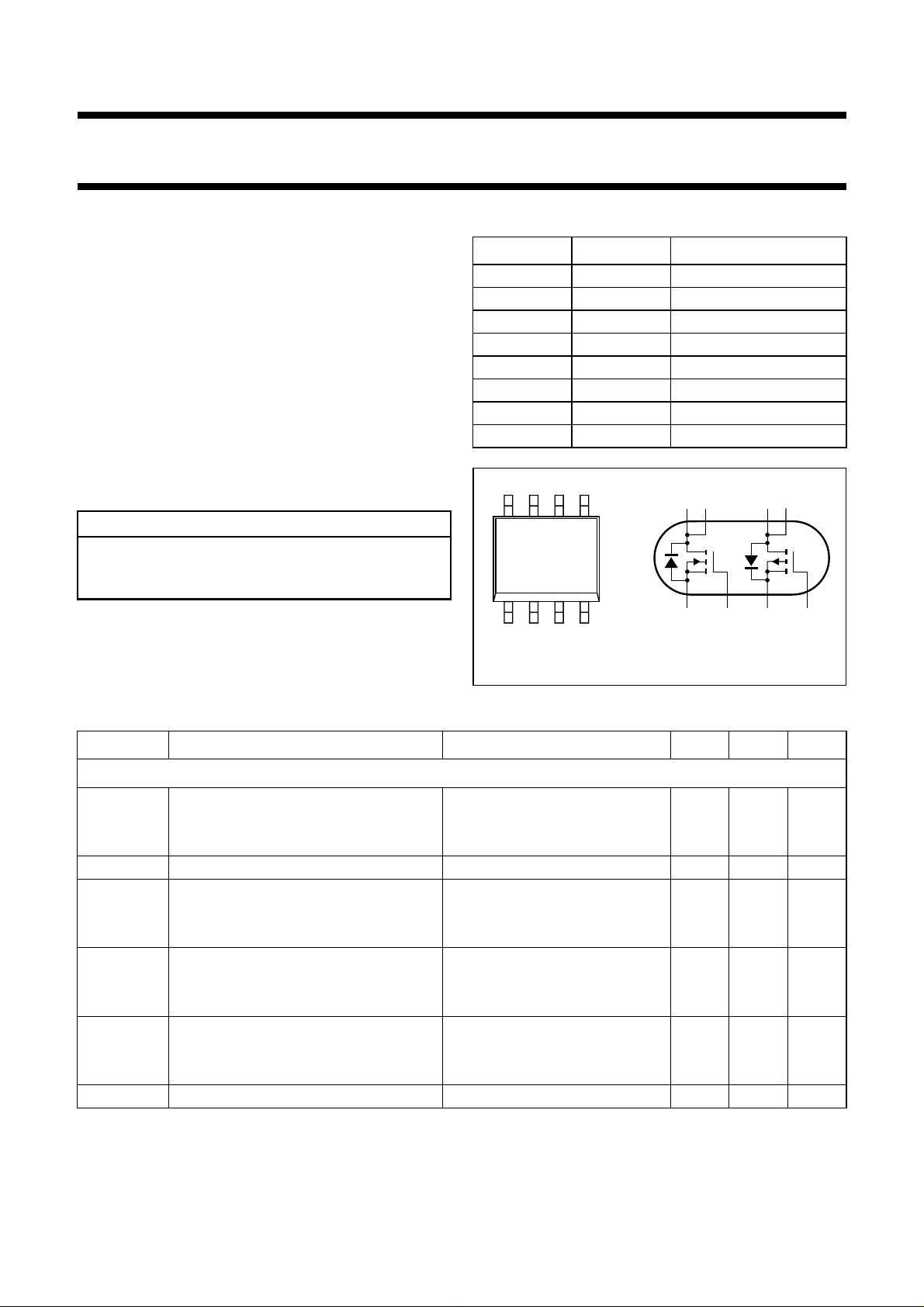

PINNING - SOT96-1 (SO8)

PIN SYMBOL DESCRIPTION

1s

2g

3s

4g

5d

6d

7d

8d

handbook, halfpage

58

1

4

1

1

2

2

2

2

1

1

source 1

gate 1

source 2

gate 2

drain 2

drain 2

drain 1

drain 1

d

d

1

1

PHC2300

d

d

2

2

MAM118

s

1

2

1

s

g

Fig.1 Simplified outline and symbol.

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

Per FET

V

DS

drain-source voltage (DC)

N-channel − 300 V

P-channel −−300 V

V

GS

V

GSth

I

D

gate-source voltage (DC) −±20 V

gate-source threshold voltage V

N-channel V

P-channel V

DS=VGS;ID

DS=VGS

= 1 mA 0.8 2 V

; ID= −1mA −0.8 −2V

drain current (DC) Ts=80°C

N-channel − 340 mA

P-channel −−235 mA

R

P

DSon

tot

drain-source on-state resistance

N-channel V

P-channel V

= 10 V; ID= 170 mA − 8 Ω

GS

= −10 V; ID= −115 mA − 17 Ω

GS

total power dissipation Ts=80°C − 1.6 W

g

2

1997 Oct 24 2

Philips Semiconductors Product specification

Complementary enhancement mode

PHC2300

MOS transistors

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

Per FET

V

V

I

I

P

T

T

DS

GS

D

DM

tot

stg

j

drain-source voltage (DC)

N-channel − 300 V

P-channel −−300 V

gate-source voltage (DC) −±20 V

drain current (DC) Ts=80°C; note 1

N-channel − 340 mA

P-channel −−235 mA

peak drain current note 2

N-channel − 1.4 A

P-channel −−0.9 A

total power dissipation Ts=80°C; note 3 − 1.6 W

T

=25°C; note 4 − 1.8 W

amb

T

=25°C; note 5 − 0.9 W

amb

T

=25°C; note 6 − 1.2 W

amb

storage temperature −55 +150 °C

operating junction temperature −55 +150 °C

Notes

1. T

is the temperature at the soldering point of the drain leads.

s

2. Pulse width and duty cycle limited by maximum junction temperature.

3. Maximum permissible dissipation per MOS transistor. (So both devices may be loaded up to 1.6 W at the same time).

4. Maximum permissible dissipation per MOS transistor. Value based on a printed-circuit board with an R

th a-tp

(ambient

to tie-point) of 27.5 K/W.

5. Maximum permissible dissipation per MOS transistor. Value based on a printed-circuit board with an R

th a-tp

(ambient

to tie-point) of 90 K/W.

6. Maximum permissible dissipation if only one MOS transistor dissipates. Value based on a printed-circuit board with

an R

(ambient to tie-point) of 90 K/W.

th a-tp

1997 Oct 24 3

Philips Semiconductors Product specification

Complementary enhancement mode

MOS transistors

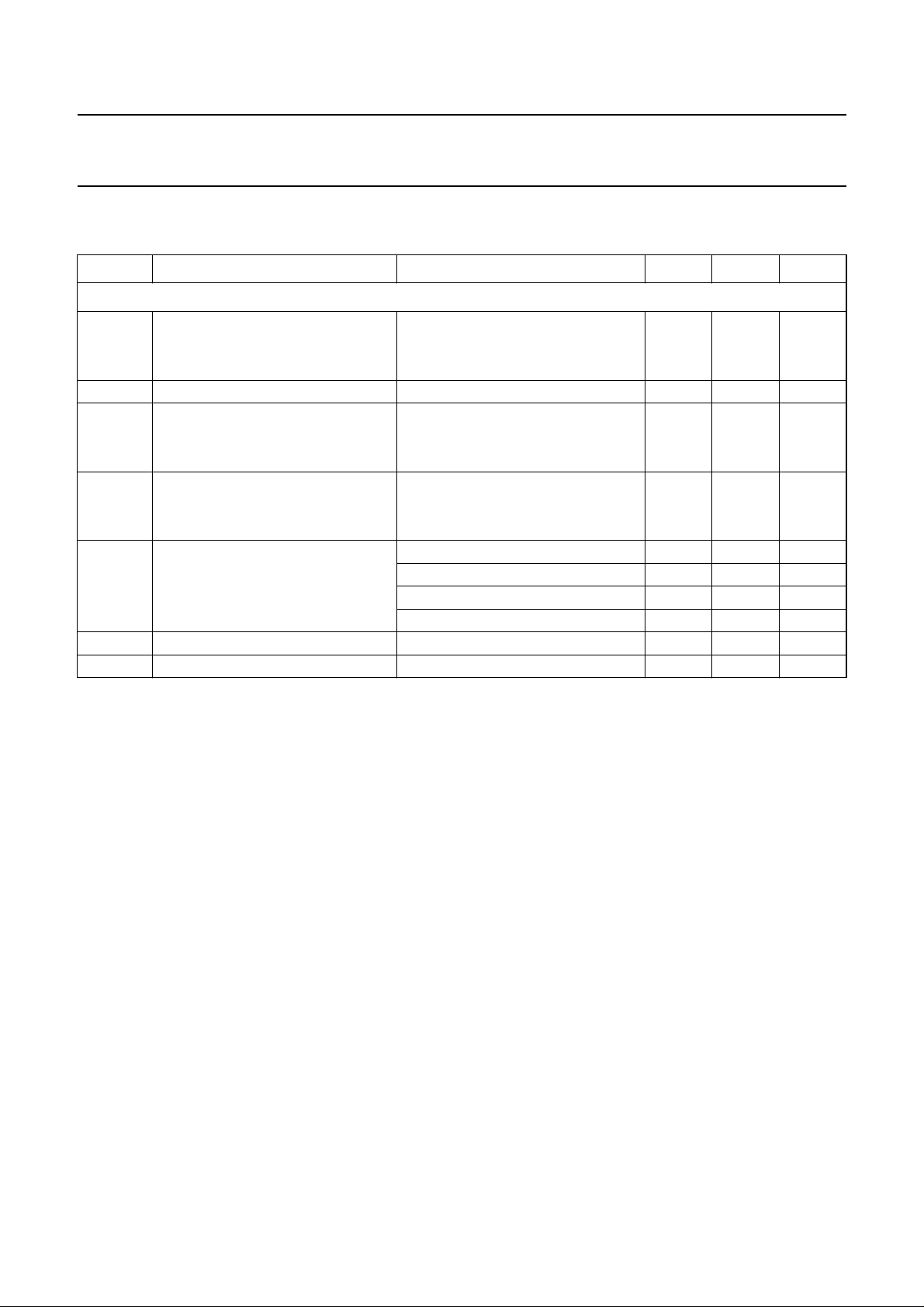

120

MDA235

Ts (°C)

handbook, halfpage

2

P

tot

(W)

1.6

1.2

0.8

0.4

0

0 40 80 160

10

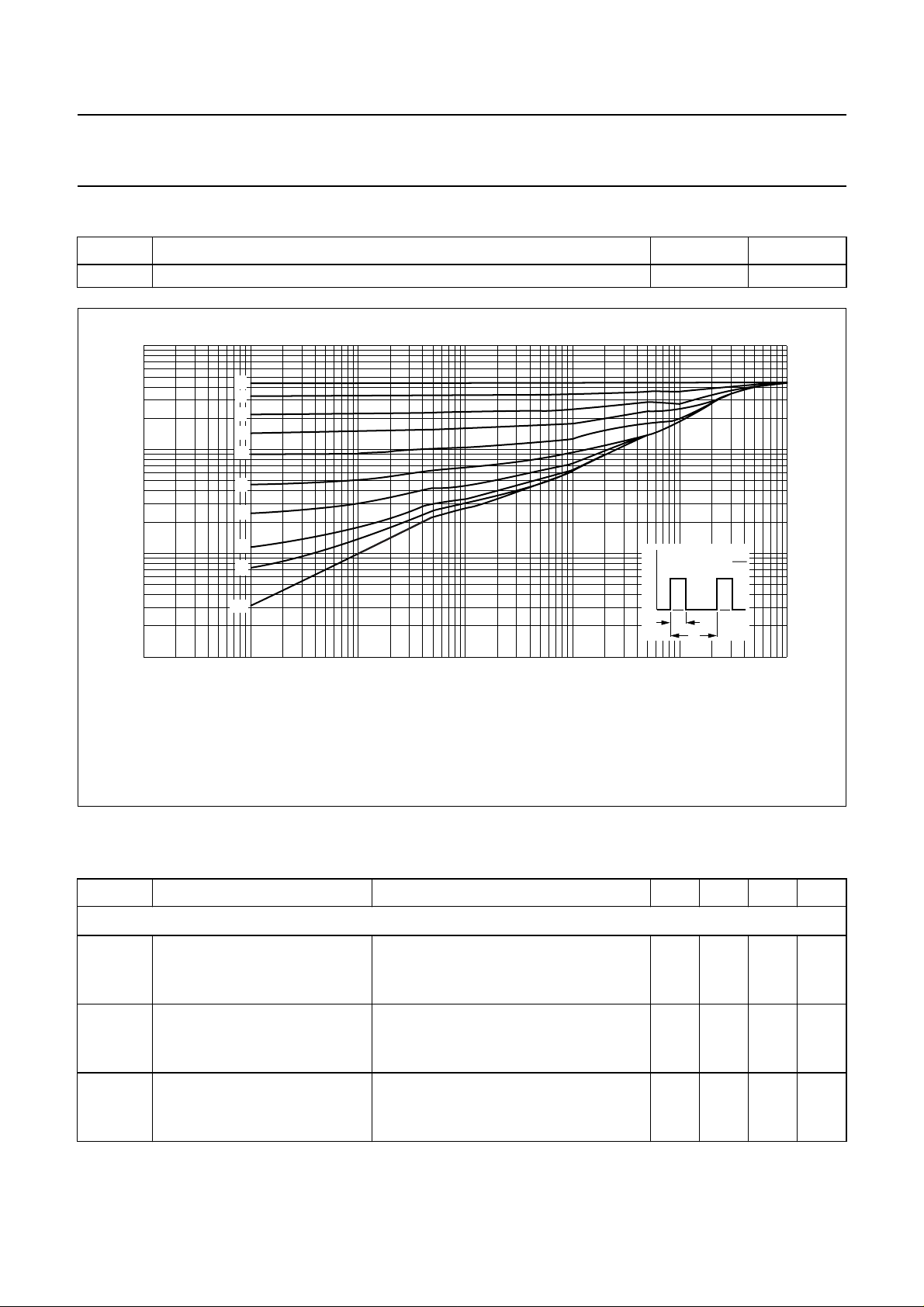

handbook, halfpage

ID

(A)

1

1

−

10

2

−

10

3

−

10

1

PHC2300

MDA240

(1)

t

P

t

p

T

p

=

δ

T

DC

t

10 10

2

VDS (V)

3

10

−10

handbook, halfpage

ID

(A)

−1

1

−

−10

2

−

−10

3

−

−10

−1

Fig.2 Power derating curve.

(1)

t

P

t

p

T

p

=

δ

T

DC

t

−10 −10

2

VDS (V)

MGL245

−10

δ = 0.01; Ts=80°C.

(1) R

DSon

limitation.

Fig.3 SOAR; N-channel.

3

δ = 0.01; Ts=80°C.

(1) R

DSon

limitation.

Fig.4 SOAR; P-channel.

1997 Oct 24 4

Philips Semiconductors Product specification

Complementary enhancement mode

PHC2300

MOS transistors

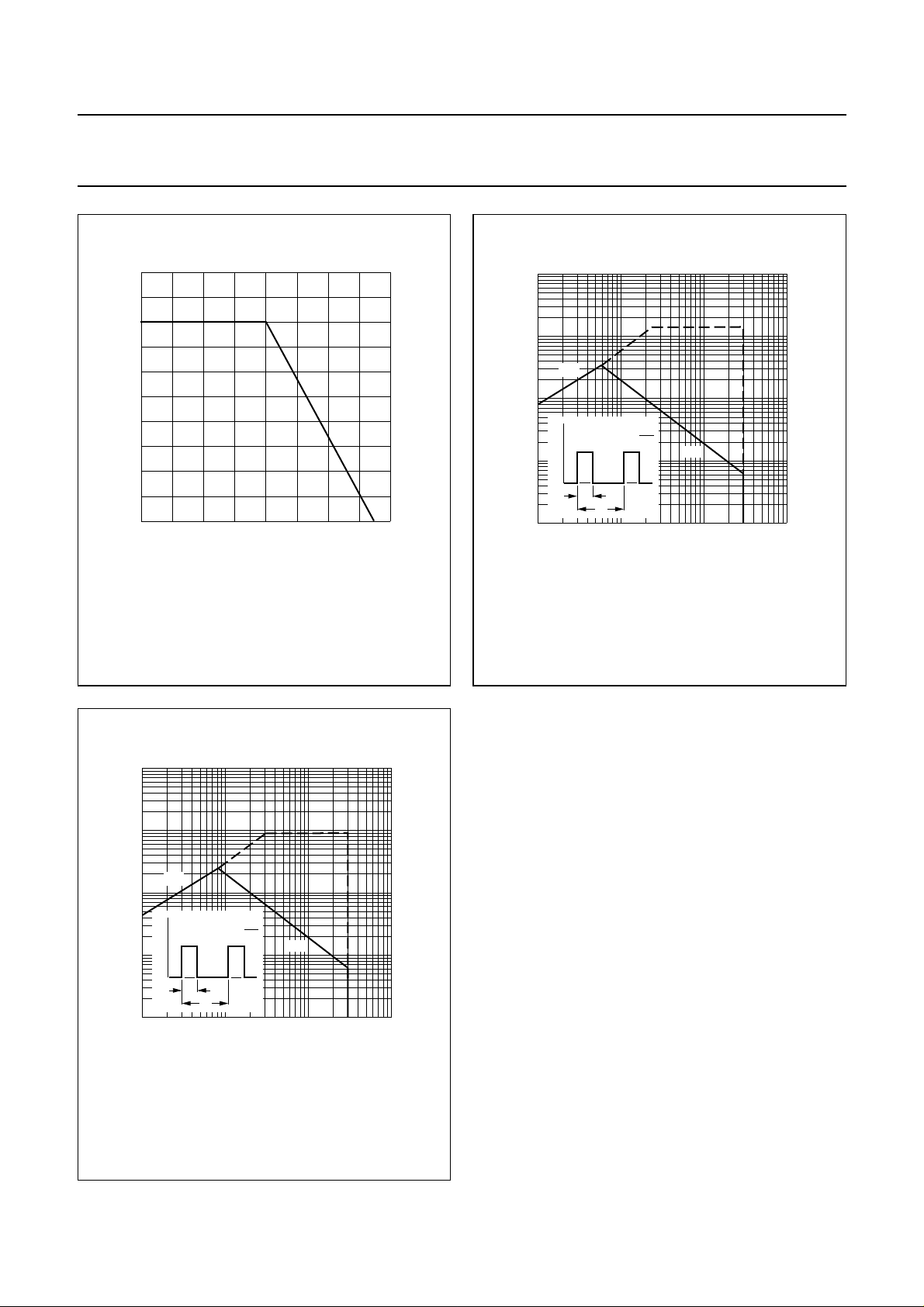

THERMAL CHARACTERISTICS

SYMBOL PARAMETER VALUE UNIT

R

th j-s

handbook, full pagewidth

R

(K/W)

thermal resistance from junction to soldering point 43 K/W

2

10

th js

10

1

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

P

δ =

t

T

MDA244

p

(10)

−1

10

−6

10

(1) δ = 1.00. (2) δ = 0.75. (3) δ = 0.5. (4) δ = 0.33. (5) δ = 0.2.

(6) δ = 0.1. (7) δ = 0.05. (8) δ = 0.02. (9) δ = 0.01. (10) δ =0.

−5

10

−4

10

−3

10

t

p

T

−2

10

−1

10

tp (s)

t

1

Fig.5 Transient thermal resistance from junction to soldering point as a function of pulse time

for N- and P-channels; typical values.

CHARACTERISTICS

T

=25°C unless otherwise specified.

j

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Per FET

V

(BR)DSS

V

GSth

I

DSS

drain-source breakdown voltage

N-channel V

P-channel V

gate-source threshold voltage

N-channel V

P-channel V

drain-source leakage current

N-channel V

P-channel V

= 0; ID=10µA 300 −−V

GS

= 0; ID= −10 µA −300 −−V

GS

GS=VDS

GS=VDS

GS

GS

; ID= 1 mA 0.8 − 2V

; ID= −1mA −0.8 −−2V

= 0; VDS= 240 V −−100 nA

= 0; VDS= −240 V −−−100 nA

1997 Oct 24 5

Loading...

Loading...